芯片管理设计主要包括电源管理设计、时钟管理设计和复位管理设计。

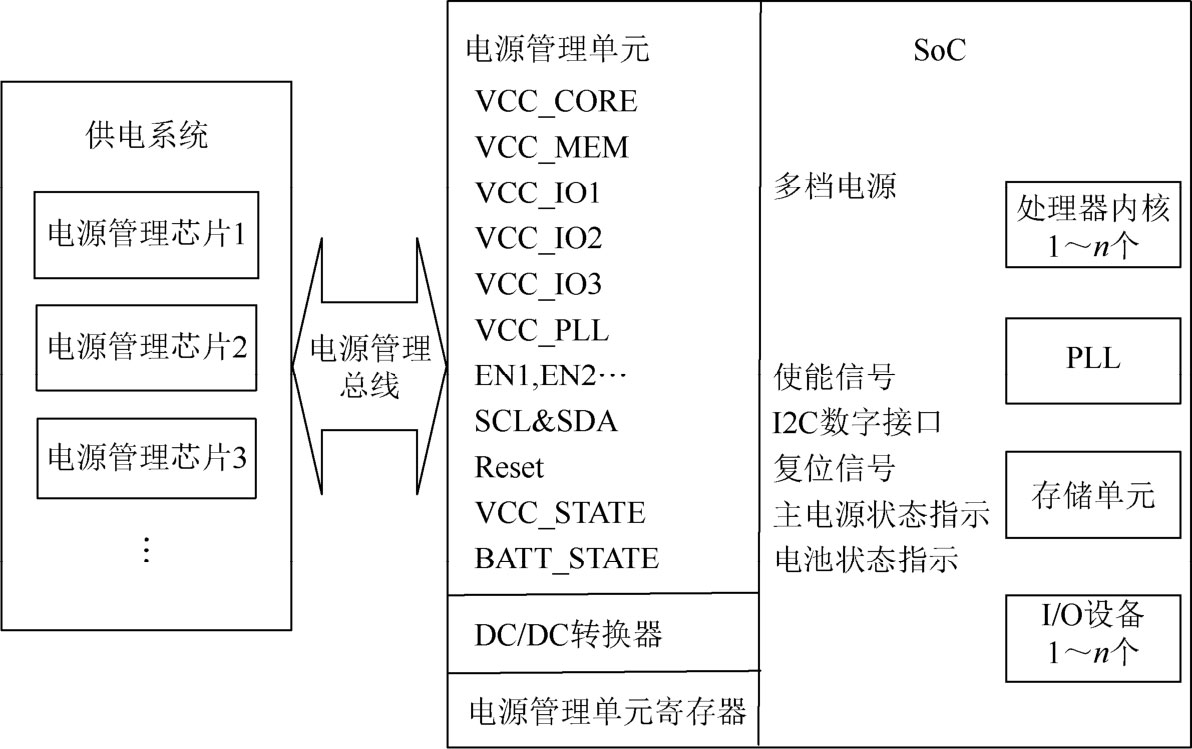

单个SoC的功能越来越复杂,包含的IP也越来越多,如处理器、射频模块、音/视频模块、内存控制器和外设等。不同功能和不同IP带来了多档电源的需求。为了满足低功耗的需求,SoC通常被分为多个电源域,不同的电源域可以独立供电和进行上电/断电控制,需要根据芯片工作场景确定供电电压。

电源信号可由外部直接输入,或者由片内电路产生。其中,SoC外部的电源管理模块称为电源管理芯片(Power Management IC,PMIC);SoC内部的电源管理模块则称为电源管理单元(Power Management Unit,PMU)。

电源管理芯片具有高集成度,其将传统的多路输出电源封装在一个芯片内,使得多电源应用场景的效率更高,体积更小。电源管理单元将传统分立的若干类电源管理芯片,如直流/直流(DC/DC)转换器,集成到片上的电源管理单元中,从而实现更高的电源转换效率和更低的功耗,以及更少的组件数量。典型的SoC供电系统和内部电源管理单元如图1.46所示。

图1.46 典型的SoC供电系统和内部电源管理单元

SoC通常使用两种电压调节器,即低压差线性稳压器和开关稳压器,两种电压调节器的比较如图1.47所示。

图1.47 两种电压调节器的比较

低压差线性稳压器可提供非常低的噪声和极其稳定的输出电压,其输入电压与输出电压之间仅有微小电压降,可以在极低的输入电压下工作,如图1.48所示。

图1.48 低压差线性稳压器

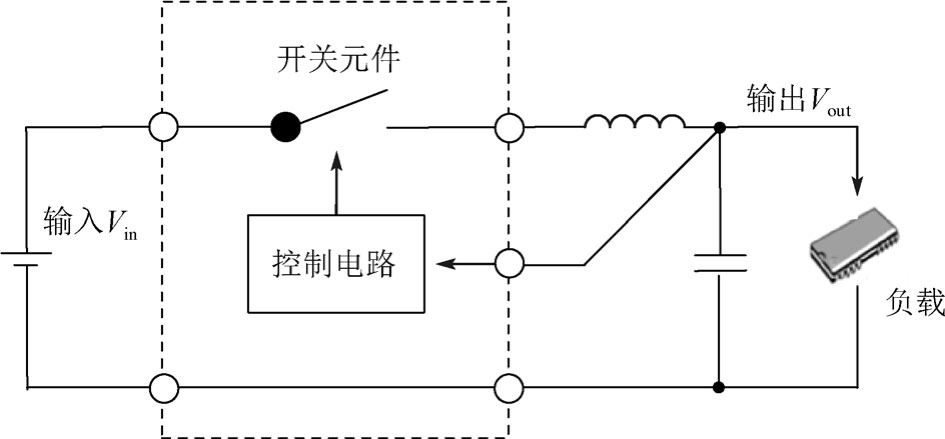

开关稳压器是将一个直流电压转换为另一个直流电压的有效器件,通过控制开关元件的关断/打开时间来得到稳定的输出电压,如图1.49所示。

图1.49 开关稳压器

根据芯片工作场景需要,确定所需时钟及频率等。

时钟源信号可由外部直接输入,也可由外接晶体/陶瓷振荡器和内部时钟发生器产生。内部RC振荡器能够产生精度较差的系统时钟,而内部锁相环(PLL)可以产生高频、高精度的系统时钟。在实际设计时,可以灵活选择一个或多个时钟源。

芯片中使用的PLL需要提供所有必要的频率,如果可能,应减少其数量以节省面积。

时钟源信号经过片上时钟管理模块(包括分频电路、多路选择电路和门控电路)处理后,提供给片上的模块或器件。芯片内部有很多时钟域,可以按照功能要求对其实施开闭。

时钟树是常见的时钟分布网络,由许多缓冲单元或反相器对平衡搭建而成。

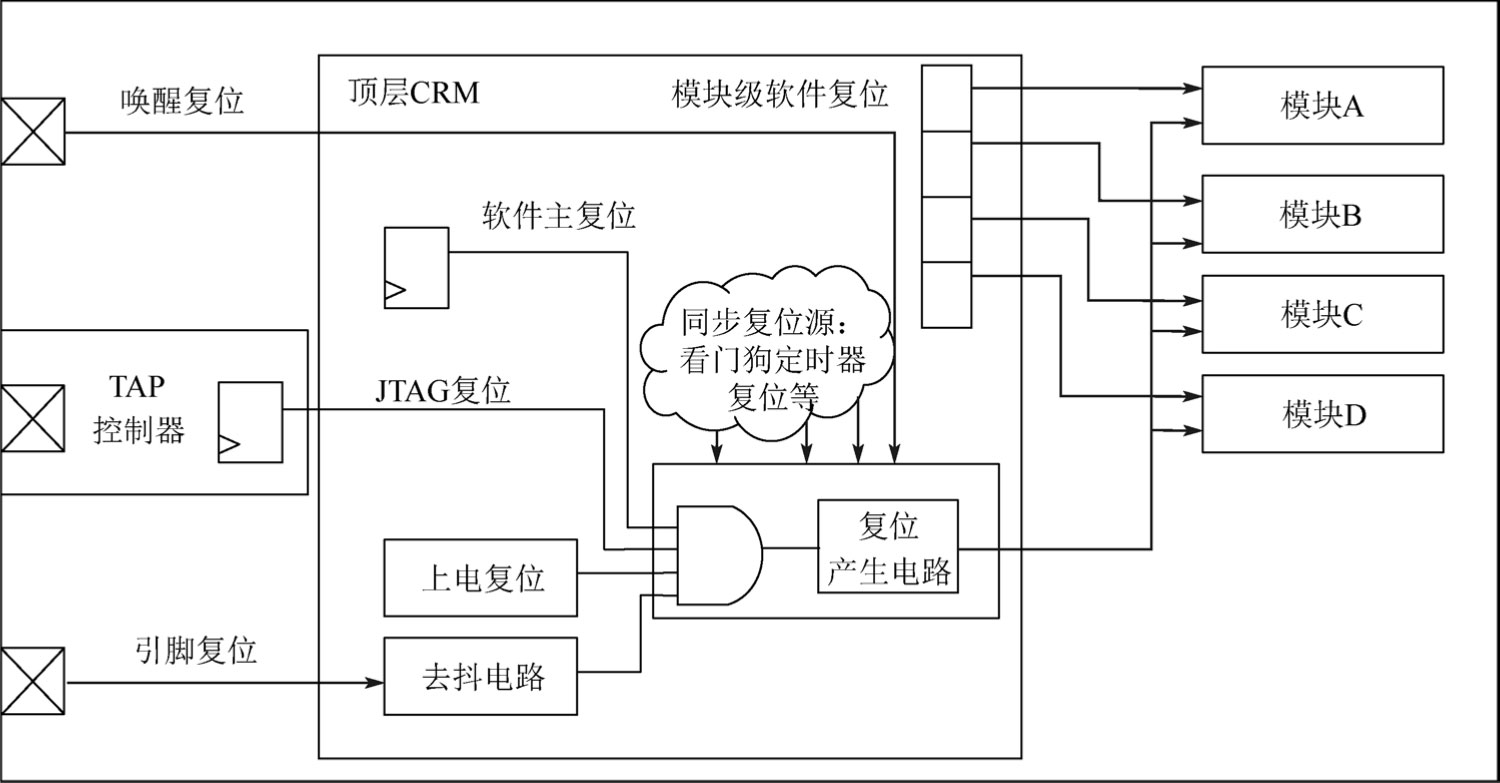

复位源可以分为片外复位源和片内复位源。片外复位源一般有来自系统板上的上电复位、手动复位,以及电源管理芯片的电源复位、调试口复位、唤醒复位等,有时还可能有特定的功能复位,如PCIe总线提供的PERST#等。片内复位源有上电复位、看门狗定时器复位、软件复位及其他硬件机制产生的复位等。

两级同步触发器可以有效消除由异步复位信号释放沿与时钟上升沿过于接近导致的亚稳态问题。

SoC的复位管理模块产生相应的芯片级和模块级复位信号。图1.50所示为典型的SoC复位结构,芯片级硬件复位信号与上电复位信号、手动复位信号、软件复位信号、调试口复位信号等有关,其与模块级软件复位信号一起被传送至各个模块。

图1.50 典型的SoC复位结构

在芯片内部,复位信号往往使用复位网络来驱动众多触发器。图1.51所示为复位网络。

图1.51 复位网络