功耗已成为SoC的重要指标与约束。低功耗设计的总原则是根据芯片的应用场景,选择适当的低功耗设计策略和实现方法,降低芯片的运行功耗。

功耗目标的确定需要考量芯片应用场景中功耗指标的商业价值、封装和制程的成本影响、低功耗设计实现的可行度和复杂度,以及设计风险和制程影响的评估。当选取参考值时,要根据同类产品、经验值和工具分析确定,并随着设计的深入而不断修正。

评估不同操作模式下的功耗,确定主攻的优化方向。低功耗SoC的主要操作模式有运行模式(Run Mode)、待机模式(Wait Mode)和休眠模式(Sleep Mode)。

在运行模式下,处理器和外设正常工作,在持续供电且不用考虑功耗的情况下,系统往往采用运行模式。在待机模式下,系统内核(System Core)以低速保持工作,部分组件则进入休眠状态,等待一个外部或内部的中断事件来唤醒。在休眠模式下,系统绝大部分组件(包括系统内核)都断电,以大幅度减少功耗。

针对具体的优化场景,分析模块的功耗情况,找出主要的耗能模块,如确认是内部模拟模块,还是数字模块。

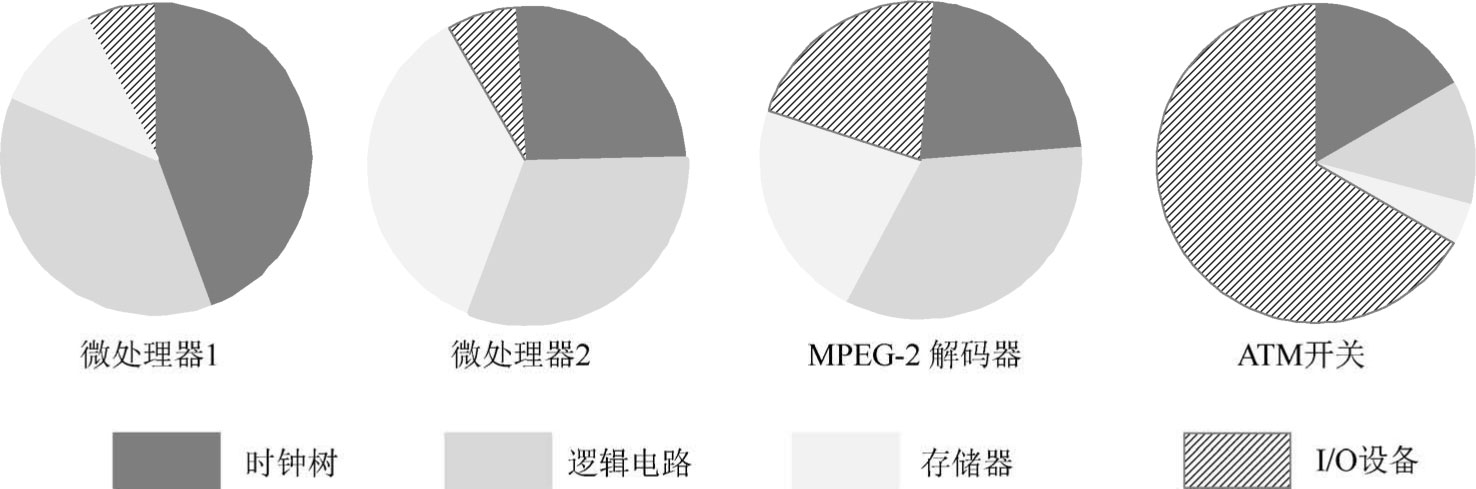

芯片功耗分布在系统内核和I/O设备中。其中,系统内核功耗主要分布在存储器(RAM、ROM)、时钟树和逻辑电路中。

典型设计中的功耗分布如图1.52所示。

图1.52 典型设计中的功耗分布

现代SoC非常复杂,设计时必须切分为若干层次,包括系统级、算法和架构级、RTL(寄存器传输级)、逻辑级、物理级。层次越高,降低功耗的效率越高。所以,降低功耗是一个系统工程,需要软件、硬件、电路、工艺等方面的统筹协调。各层次优化策略及优化效果如图1.53所示。

设计者可以根据特定应用,关掉整个模块或减少无效动作。在系统级,需要考虑如何将设定任务合理分配到各个模块,以及采用合适的功耗管理策略;在算法和架构级,采用流水线、算法优化、排序等技术,以达成最大效率;在RTL,通过时钟门控(Clock Gating)等方法降低功耗;在逻辑级,利用综合(Synthesis)工具实现逻辑时序和功耗的优化;在物理级,通过晶体管选择、时钟树设计等手段,减少电路耗能。

图1.53 各层次优化策略及优化效果

架构级低功耗设计的主要任务是探索提高电源使用效率的架构,选择适当的频率和电压控制策略。

从芯片工作场景出发,选择若干工作频点进行频率控制。通过分频器和倍频器,可以实现频率可调。

如果在特定场景下,某些模块完全可以停止工作,则可采用时钟门控的方法。即使触发器输出不变,也可以使其时钟失效,降低5%~10%的动态功耗。

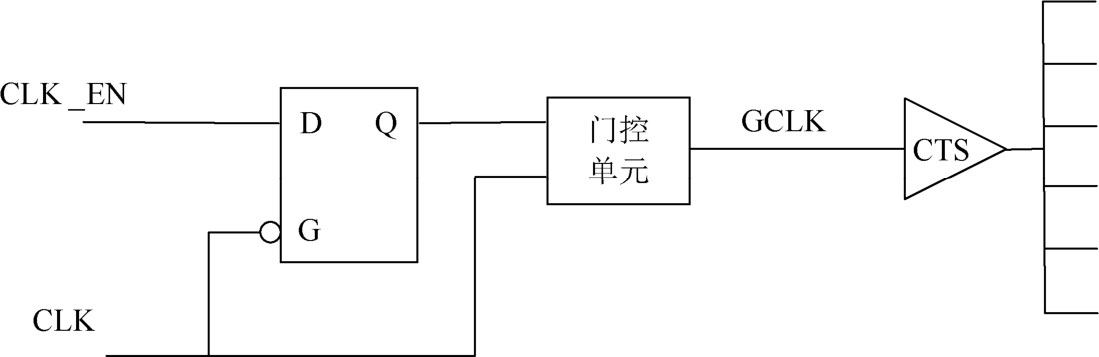

在典型的数字芯片中,时钟树由大量缓冲单元或反相器对组成,其功耗高达整个设计功耗的40%。加入全局时钟门控电路,减少时钟树及所驱动寄存器时钟引脚的反转将降低功耗。在图1.54中,当时钟使能CLK_EN置低时,可以将右侧寄存器的时钟都关闭。在布局时将全局时钟门控电路摆放在时钟源GCLK附近,关闭时钟后,整个时钟树上的缓冲单元和时钟树驱动的模块都会停止反转。

图1.54 时钟树门控

通过电压调节技术,可调节SoC在不同工作模式下的工作电压,从而在保证性能的基础上降低功耗。

在多电压(Multi-Voltage)供电技术中,对不同模块按其性能要求不同而采用不同电压供电,如图1.55所示。

图1.55 多电压供电技术

使用动态电压频率调节技术,针对运行中的芯片,依据不同的场景动态调节其供电电压和工作频率,实现计算性能和功耗之间的平衡。

当某一部分电路处于休眠状态时,可使用电源门控(Power Gating)技术关闭其供电电源。SoC经常需要设置一个电源常开区,负责内核停电期间的对外通信与低功耗管理,当唤醒信号到来后,负责重新打开内核电源。