实现全加器,需要算出本位的加法结果以及向上进位的结果。

向上进位的结果计算式如下(该式使用了Verilog的符号来表示运算逻辑)。

w i + 1 =( a i & b i )|[ w i &( a i ^ b i )]

式中, w i +1 为从 i 位向第 i +1位的进位; a i 和 b i 分别为被加数和加数在第 i 位的值。

本位的加法结果由3个部分取异或得到,这3个部分分别是:被加数、加数和来自低位的进位。该运算可表示为

c i = a i ^ b i ^ w i

以下给出一个使用Verilog实现7位全加器的RTL实例(配套参考代码full_adder.v),其原理基于上述两个公式。

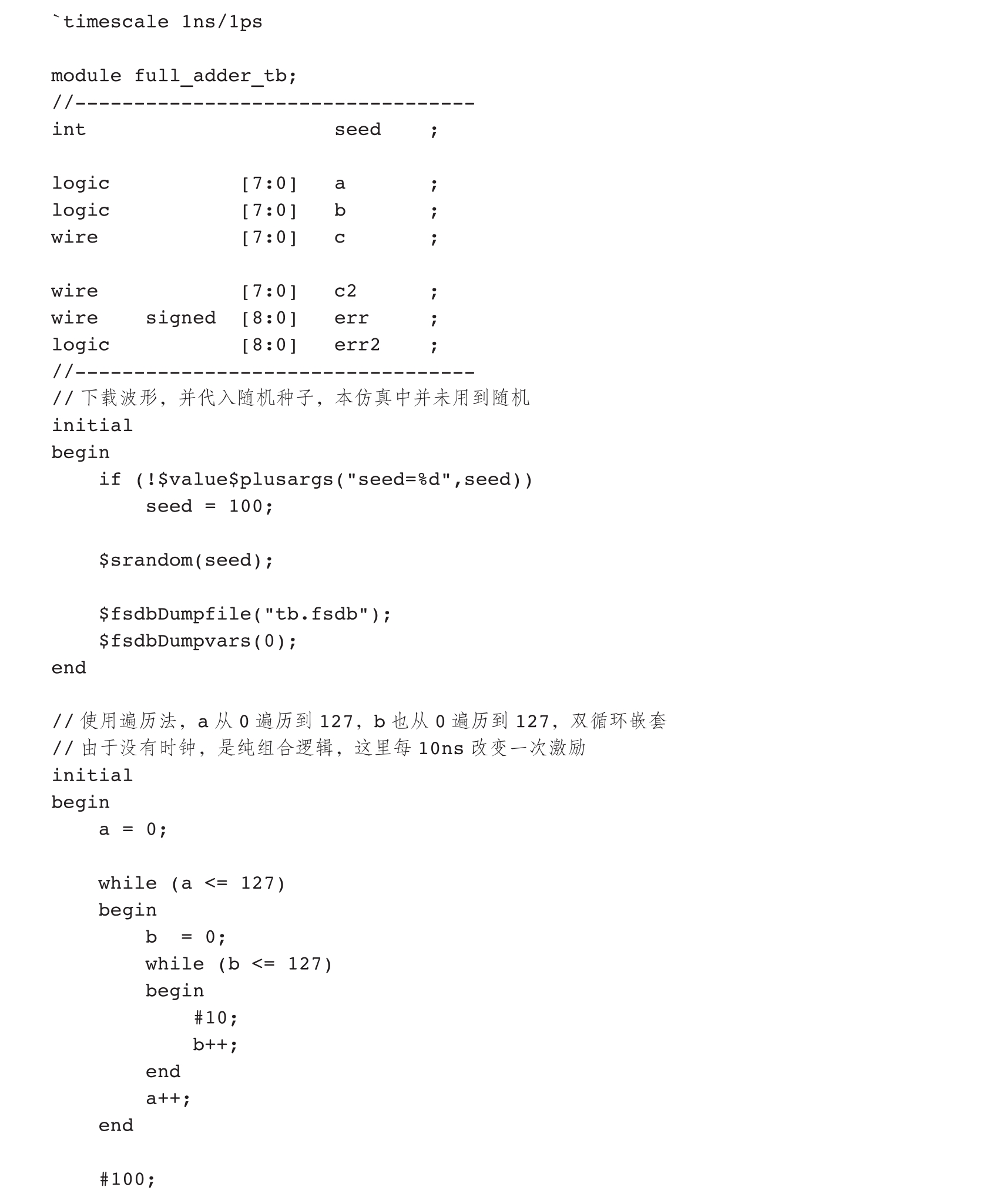

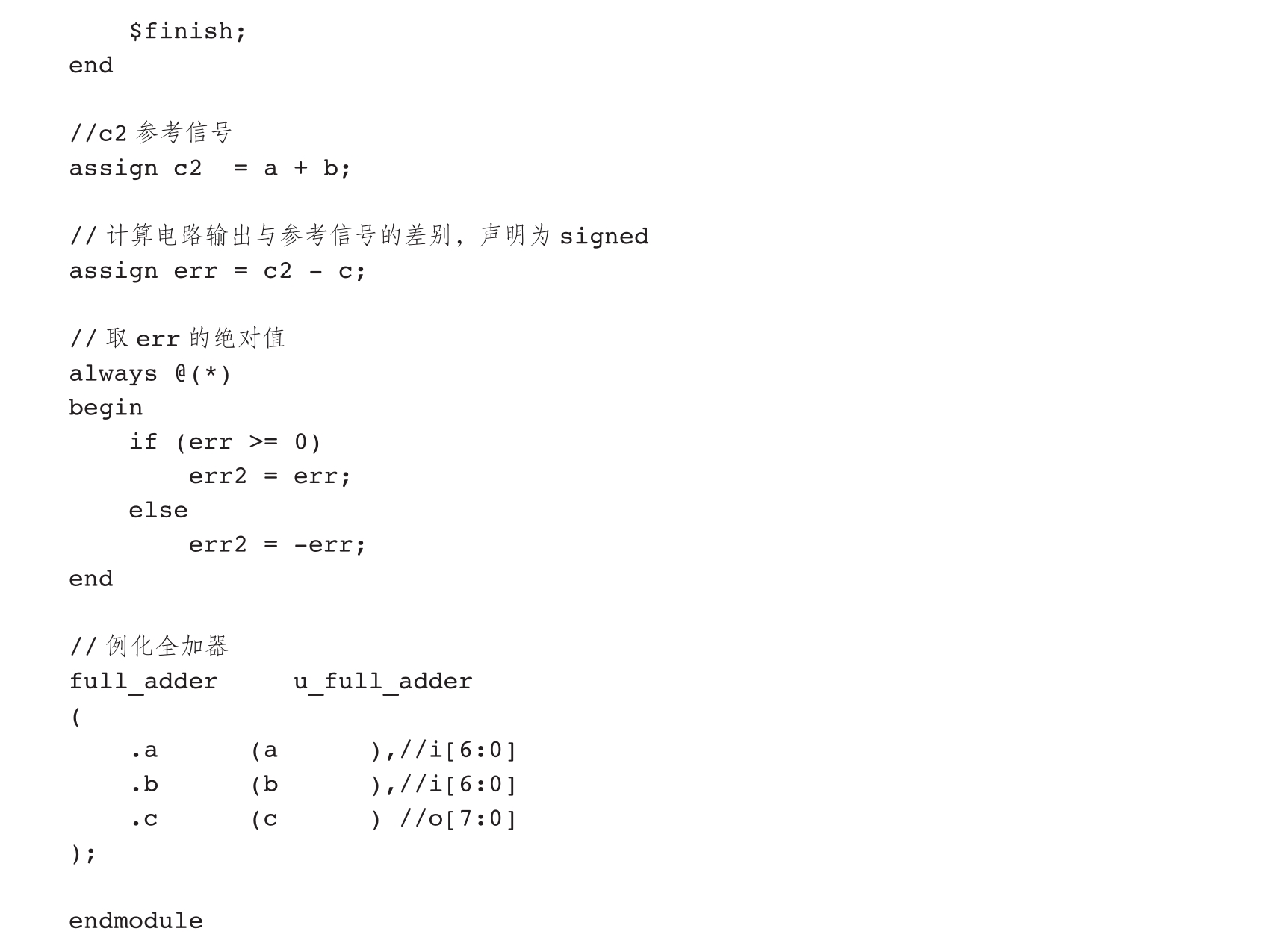

该全加器对应的仿真验证环境(TestBench,TB)如下(配套参考代码full_adder_tb.v)。由于数据的位宽小,仿真全部情况的数据量并不大,因此这里采用遍历法仿真了该加法器所能涉及的全部情况。注意,在T B中a和b的位宽都不是RTL中的7位,而是8位,因为在TB中,a和b都会在遍历到RTL的最大值127后出现128的情况,TB用该数来标示循环遍历的结束。只有a和b的位宽为8,才能够令其表示出128。

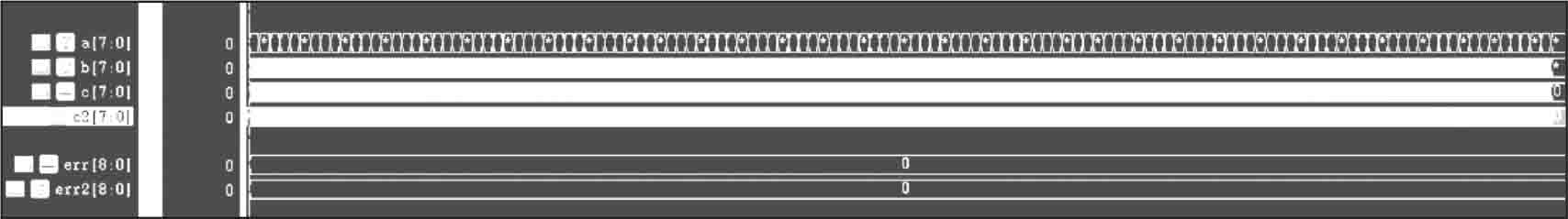

仿真结果如图3-4所示,RTL运算结果与参考结果保持一致,err2一直保持0。

图3-4 全加器仿真结果