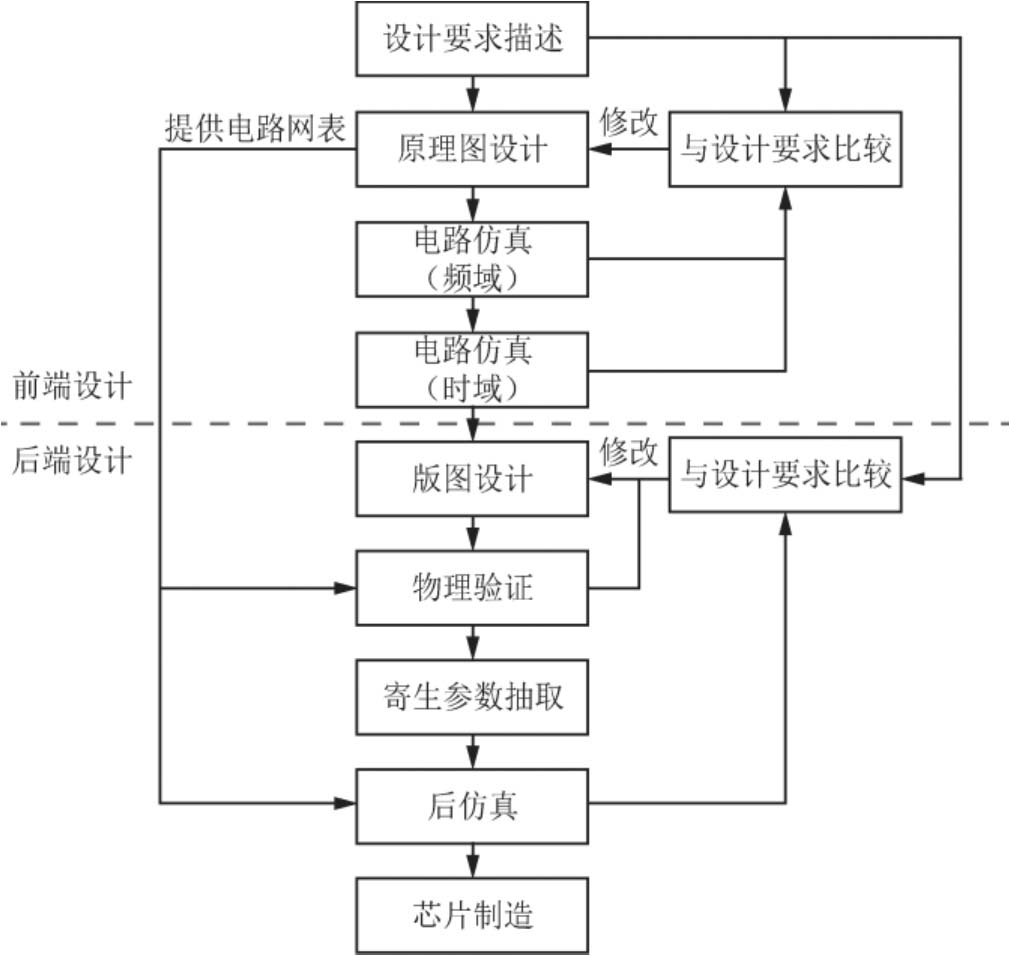

随着CMOS工艺的快速发展,以MOSFET为基础的模拟集成电路的性能也得到快速提升,在片上系统中发挥着重要的作用。CMOS模拟集成电路设计相比于传统分立元件模拟电路设计复杂很多,需要采用EDA软件进行仿真和模拟来验证电路的性能。模拟集成电路的设计流程如图1-2所示,主要分为前端设计和后端设计,其中前端设计主要完成电路原理图的设计和验证,而后端设计主要完成版图的设计和验证,最终将版图文件交付工艺厂完成芯片的物理制造。

图1-2 模拟集成电路的设计流程

模拟集成电路的总体设计从定义电路规格开始,首先,描述设计要求。其次,根据设计要求,在EDA软件中设计电路的原理图,通过EDA仿真工具进行电路的频域仿真,将仿真结果与设计要求进行比较,如果仿真结果不能达到设计要求则修改原理图,反复迭代直至该环节的仿真结果达到设计要求。最后,通过EDA软件进行电路的时域仿真,从电路输出的具体时域信号波形上观测是否达到设计要求,如果该仿真结果不能达到设计要求则继续修改原理图,反复迭代直至该环节的仿真结果达到设计要求。至此,完成了模拟集成电路的前端设计流程。随后进入后端设计流程:首先,进行版图设计;其次,对设计好的版图进行物理验证,主要包含设计规则检查(DRC)和版图与原理图对比(LVS)检查。DRC主要检查版图中图形的几何规则,用以保证版图在工艺上的可实现性。LVS检查主要从版图中提取出电路网表,然后与原理图网表进行比对,检查两者的一致性。如果物理验证不通过,则对版图进行修改,反复迭代直至物理验证通过。最后,进行版图寄生参数提取,将原理图设计环节所提供的网表与寄生参数合并,形成后仿真网表,开展后仿真。后仿真在电路原理图基础上考虑了版图的寄生效应,该仿真更加接近芯片制造后的结果。这个过程要进行多次迭代,不断修改优化版图,直至后仿真结果能够达到最初的设计要求,整体模拟集成电路设计环节结束。通过后仿真后,即可导出版图数据(GDSII)文件,将其交付工艺厂进行芯片制造。