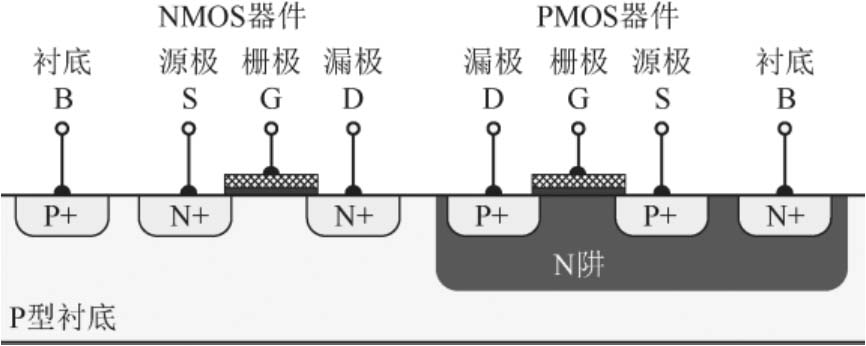

MOSFET是集成电路的核心器件,包含4个端口,分别是源极(S)、栅极(G)、漏极(D)和衬底(B),如图2-12所示。MOSFET是利用电场效应来控制电流的,即通过改变栅源电压 V GS 来改变导电沟道的电阻,最终达到对沟道电流 I D 的控制作用。在硅基工艺下,由多晶硅、二氧化硅和P型或N型硅形成的MIS结构是MOSFET的核心部分。N型MOSFET(简称NMOS器件)的衬底是P型硅,源极和漏极均为P型衬底上的N型重掺杂区域。源漏方向的栅的尺寸叫作栅长 L ,与之垂直方向的栅的尺寸叫作栅宽 W 。NMOS器件正常工作时,其源极和漏极与P型衬底之间的PN结必须处于反偏或零偏状态,因此P型衬底要接到最低电位上,通常选择连接至地线。对于NMOS器件,当栅极和源极电压差(即栅源电压) V GS >0且足够高时,栅极下方的P型衬底出现反型,形成N型沟道连通源极与漏极。P型MOSFET(简称PMOS器件)的衬底是N型半导体,源极和漏极均为N型衬底上的P型重掺杂区域。在互补MOS(CMOS)工艺中要同时使用NMOS器件和PMOS器件,且必须制备在同一晶圆上,晶圆通常是P型硅。为了在该晶圆上形成PMOS器件的N型衬底,需要做一个局部衬底,通常称为阱,因此PMOS器件实际的衬底是N阱。需要注意,N阱和P型衬底之间会形成PN结,正常工作时需要保证该PN结反偏,因此在大多数电路中N阱连接至最高电位,通常选择连接至电源 V DD 。对于PMOS器件,当栅极和源极电压差 V GS <0且足够高时,栅极下方的N阱出现反型,形成P型沟道连通源极和漏极。

图2-12 MOSFET结构

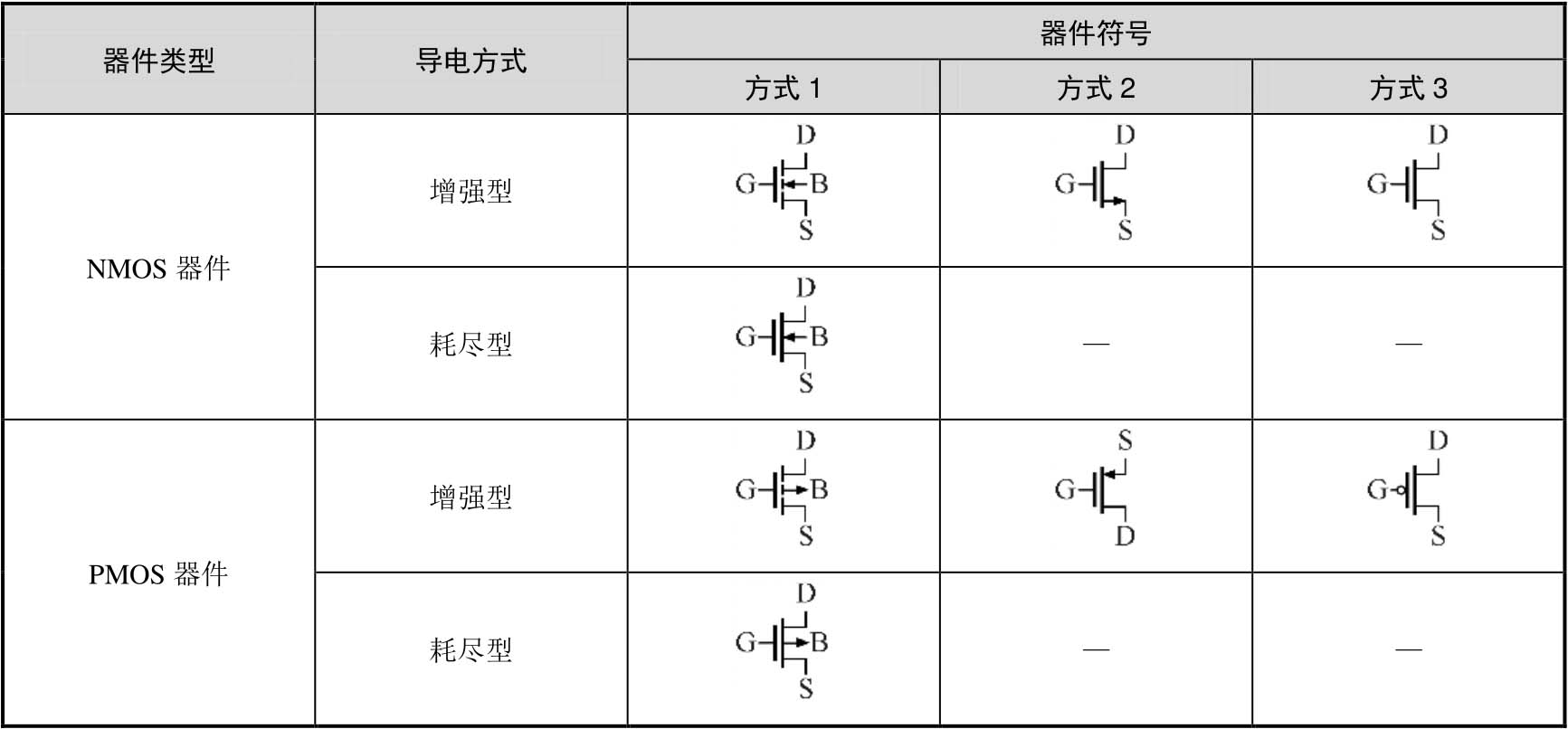

根据导电方式的不同,MOSFET又分为增强型和耗尽型。对于增强型NMOS器件,当 V GS =0时器件不导通,只有当 V GS 正向增大到一定程度时器件才会导通。对于耗尽型NMOS器件,当 V GS =0时器件已经导通,如果需要关闭器件则需要反向增大 V GS 。对于增强型PMOS器件,当 V GS =0时器件不导通,只有当 V GS 反向增大到一定程度时器件才会导通。对于耗尽型PMOS器件,当 V GS =0时器件已经导通,如果需要关闭器件则需要正向增大 V GS 。

MOSFET晶体管的常见电路符号如表2-1所示。在这些符号中,方式1包含了MOSFET的衬底端(带箭头的直线),箭头指向栅极代表N型器件,反之则为P型器件。在方式1的符号中,沟道为虚线的表示增强型器件,沟道为实线的则表示耗尽型器件。由于在大多数电路中NMOS器件和PMOS器件的衬底分别接地和 V DD ,所以我们可以采用忽略衬底的方式2和方式3表示的器件符号。在模拟电路中,通常需要区分器件的源极和漏极,因此往往采用方式2表示器件,其箭头端表示器件的源极。值得注意的是,在方式2中箭头的方向也表明了器件类型和电流方向,但要与方式1中箭头的方向有所区分。在数字电路中,MOSFET表现为开关,通常无须区分源极和漏极,只要能区分器件类型即可。此外,NMOS器件是栅极接高电平导通,即高电平时器件有效,而PMOS器件是栅极接低电平导通,即低电平时器件有效,因此常采用方式3表示数字电路中的MOSFET。本书重点讲解模拟电路,因此后续主要采用方式2来表示MOSFET。

表2-1 MOSFET晶体管的常见电路符号

了解器件的工艺流程可以让我们理解制造工艺对电路性能的影响,这对于设计电路和版图来说都是非常重要的。本节将简要介绍CMOS关键工艺流程。

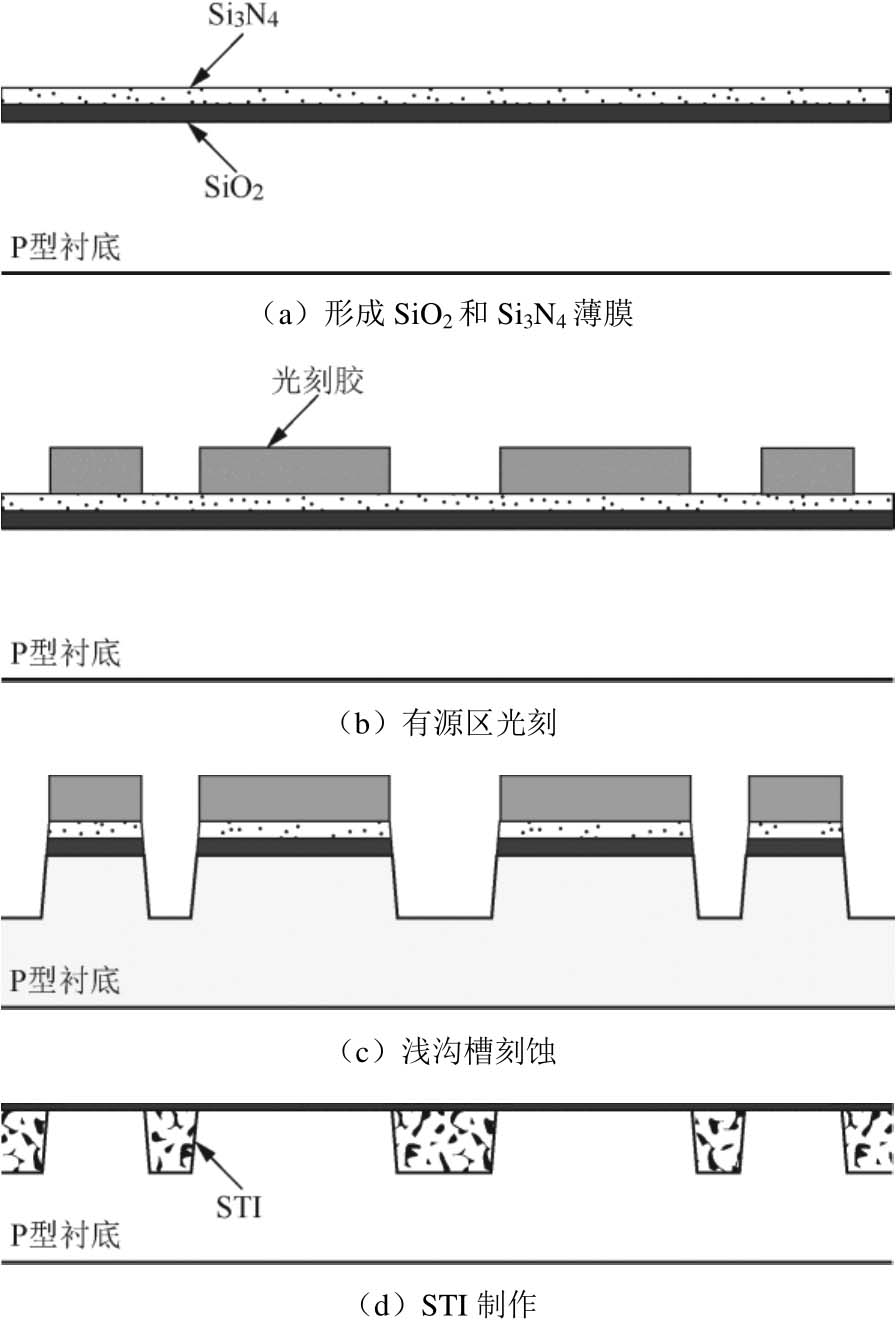

有源区的形成过程如图2-13所示,首先在P型衬底上热氧化生成一层二氧化硅(SiO 2 ),随后通过化学气相沉积(CVD)形成氮化硅(Si 3 N 4 )薄膜。SiO 2 起到缓解Si 3 N 4 和硅衬底之间应力的作用。其次旋涂光刻胶,使用有源区掩模版进行光刻,去除有源区以外(即器件隔离区)的光刻胶。再次通过湿法刻蚀依次去除Si 3 N 4 、SiO 2 和硅,形成硅的浅槽。去除光刻胶后通过CVD沉积氧化物形成浅沟槽隔离(STI)。最后通过化学机械抛光(CMP)对晶圆表面进行平整化处理。STI以外的区域是有源区,将来用于制作MOSFET。

图2-13 有源区的形成过程

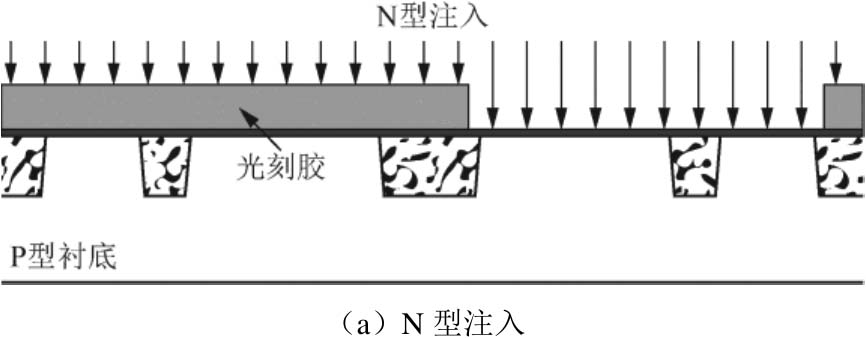

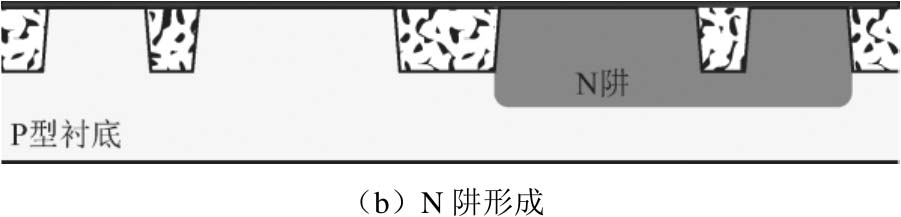

首先旋涂光刻胶,然后通过N阱掩模版进行光刻,去除N阱区域的光刻胶。最后进行N型注入,未被光刻胶覆盖的区域将被有效注入,N阱的形成过程如图2-14所示。去除光刻胶后,形成N阱。

图2-14 N阱的形成过程

图2-14 N阱的形成过程(续)

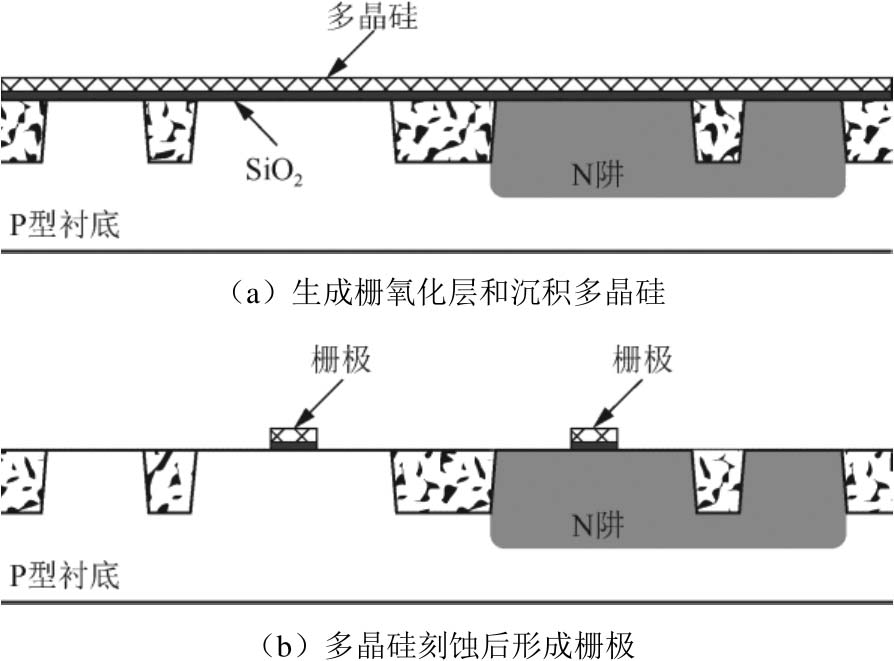

栅极的形成过程如图2-15所示,首先去除前面工序中遗留的表面SiO 2 薄膜,重新热氧化生成高质量的SiO 2 薄膜用作栅氧化层,这是工艺中非常关键的一步,栅氧化层的厚度要求精确到0.1nm量级。通过CVD沉积多晶硅,之后旋涂光刻胶,使用栅极掩模版进行光刻,去除栅极以外的光刻胶。通过干法刻蚀去除未被光刻胶保护的多晶硅,完成刻蚀后去除光刻胶,形成多晶硅栅极。

图2-15 栅极的形成过程

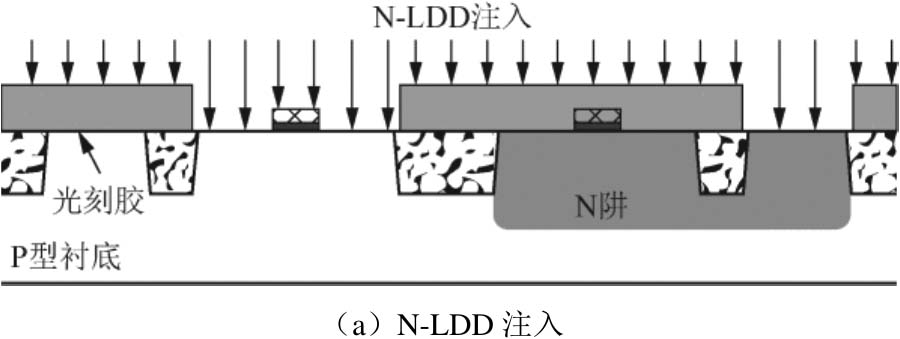

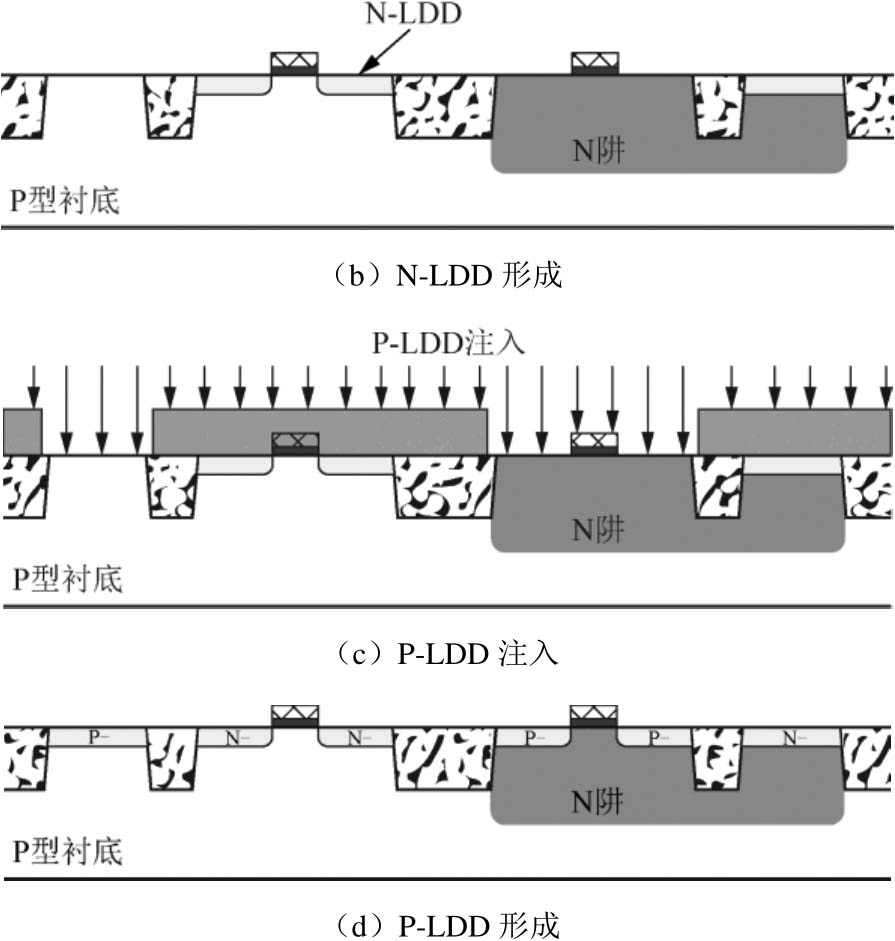

为了防止晶体管源极和漏极与栅极交叠区域的电场过强而出现热载流子问题,往往需要在栅极两侧先形成一个浓度较低的源漏掺杂区域,即轻掺杂漏(LDD),其形成过程如图2-16所示。首先旋涂光刻胶,使用N-LDD掩模版进行光刻。然后进行低浓度的N型杂质注入,NMOS器件区域以及N阱的衬底连接区域均未被光刻胶屏蔽,得到有效注入。在NMOS器件的栅极两侧形成N-LDD,同时N阱的衬底接触区域也形成了N-浓度的注入。同理进行P-LDD的形成,最终如图2-16(d)所示,完成N-LDD和P-LDD的制作。

图2-16 轻掺杂漏的形成过程

图2-16 轻掺杂漏的形成过程(续)

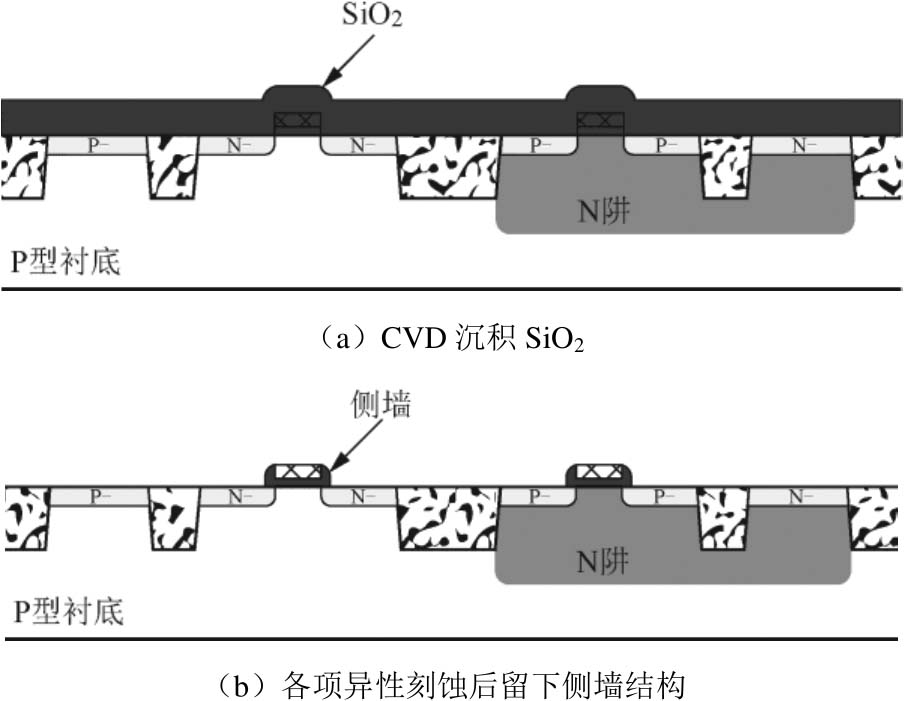

为了在对源漏区域进行重掺杂时能够保留栅极两侧的LDD区域,需要在栅极两侧形成一个用于屏蔽注入的SiO 2 的侧墙,其形成过程如图2-17所示。首先通过CVD沉积SiO 2 ,然后通过各项异性刻蚀去除大部分SiO 2 ,仅在栅极两侧留下一小部分充当侧墙的SiO 2 。

图2-17 侧墙的形成过程

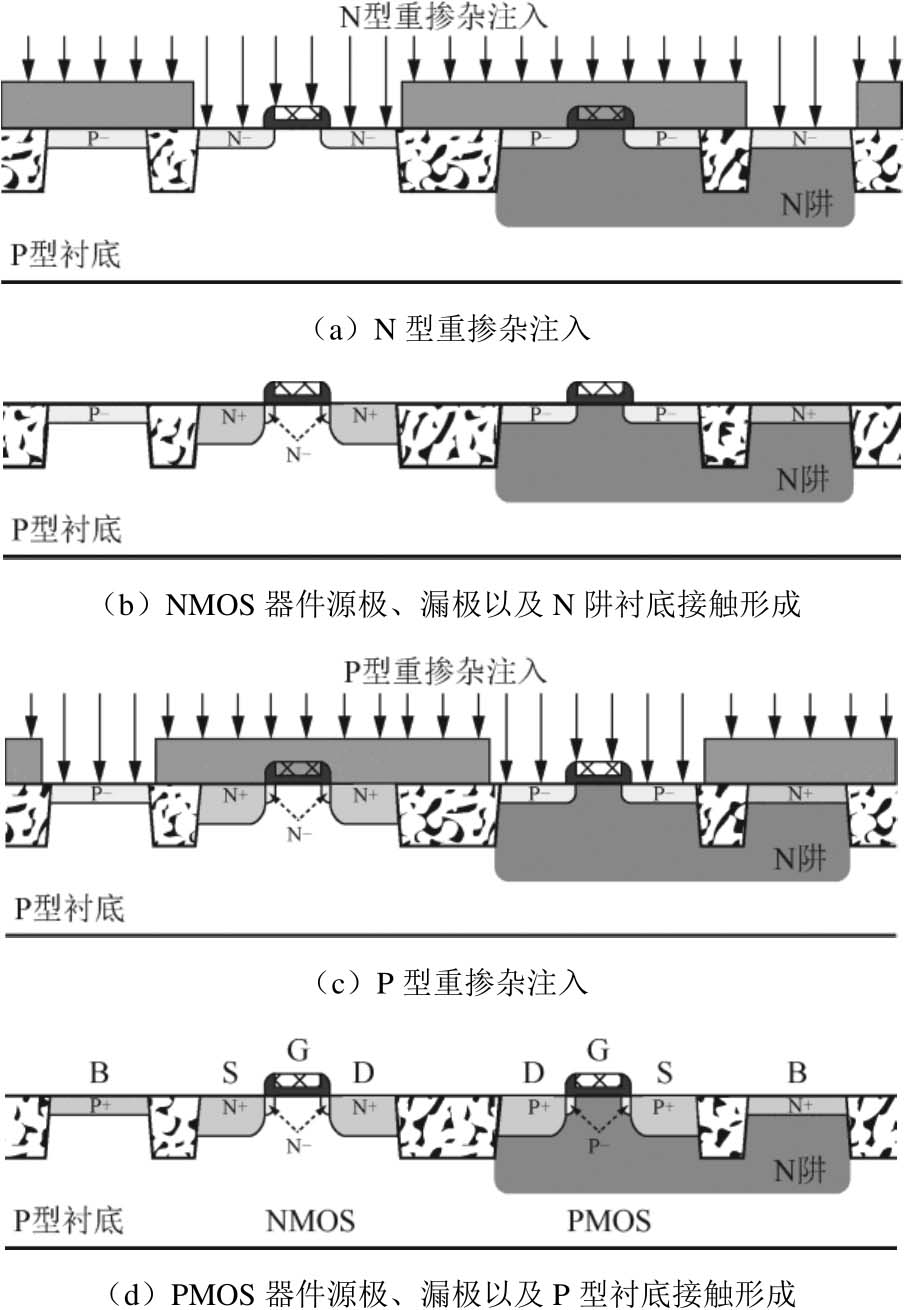

MOSFET源极、漏极的制作过程如图2-18所示,首先光刻NMOS器件和N阱的接触区域,然后进行高浓度的N型注入,形成NMOS器件的源极、漏极以及N阱的衬底接触。因为NMOS器件栅极两侧存在SiO 2 侧墙,因此该重掺杂注入后,栅极两侧还保留了一小块N-LDD区域防止出现热载流子问题。同理形成PMOS器件的源极、漏极以及P型衬底接触。至此,NMOS器件和PMOS器件均在同一P型衬底晶圆上制作完成。

图2-18 MOSFET源极、漏极的制作过程

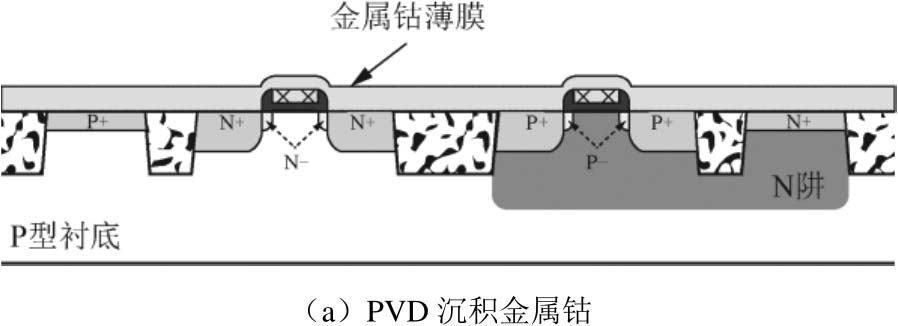

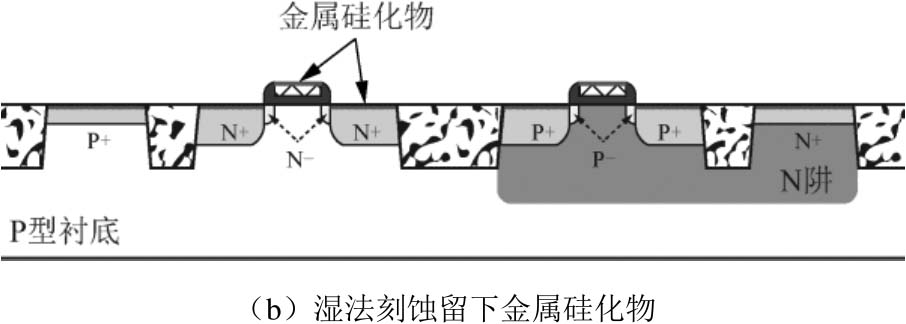

为了减小多晶硅和硅与金属之间的接触电阻,形成良好的欧姆接触,CMOS工艺一般采用金属硅化物工艺,金属硅化物的形成过程如图2-19所示。通过物理气相沉积(PVD)在晶圆表面沉积一层金属钴薄膜。在高温下,让钴和多晶硅、硅发生反应形成金属硅化物。由于STI区域既无硅也无多晶硅,因此不会形成金属硅化物。最后通过湿法刻蚀去除掉未发生反应的金属钴,这样便在有源区和栅极上形成了金属硅化物薄层。

图2-19 金属硅化物的形成过程

图2-19 金属硅化物的形成过程(续)

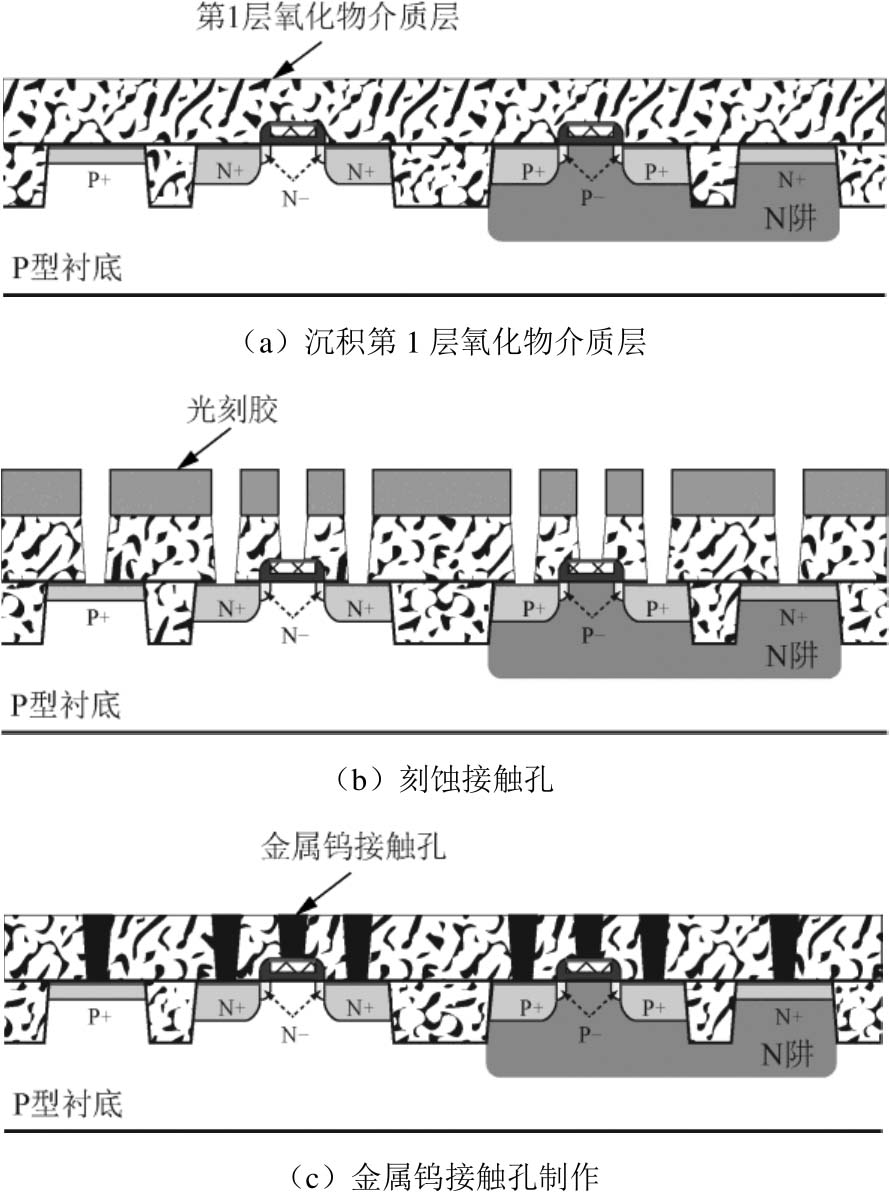

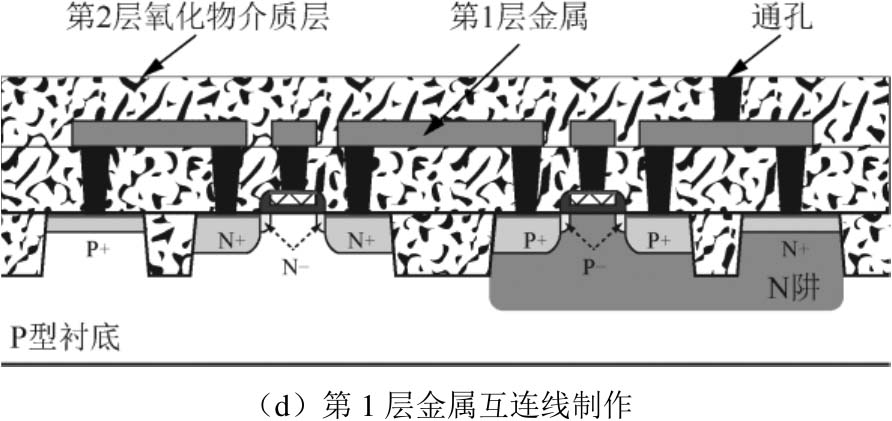

前段工序完成CMOS器件的制备,后段工序则主要进行器件之间的互连。金属互连的形成过程如图2-20所示,首先,通过CVD沉积第1层氧化物介质层,用来隔离器件和第1层金属。其次,光刻接触孔,通过干法刻蚀去除接触孔区域的介质层,提供金属和底层器件的连接通道。采用CVD沉积金属钨,填充接触孔,再通过CMP去除表面不需要的金属钨,完成接触孔制作。再次,采用PVD沉积第1层金属,通过光刻保留金属连线区域的光刻胶。最后,通过干法刻蚀去除光刻胶以外的金属,保留第1层金属的互连线,至此完成第1层金属与底层器件的互连。此后,再制作第2层氧化物介质层用以隔离第1层金属和第2层金属,利用穿通第2层氧化物介质层的通孔连通第1层金属和第2层金属,依次类推,完成多层金属的互连,实现复杂的电路连接关系。

图2-20 金属互连的形成过程

图2-20 金属互连的形成过程(续)