说起芯片,大家都不陌生。这个黑黑的小方块遍布在我们生活的各个角落。可是说到芯片是怎么“变”出来的,可能大家了解得就不那么清楚了。大多数芯片的主要材料是硅,硅是最重要的半导体材料,可以通过一定工艺实现导电与不导电的控制。硅也是地球上最丰富的元素之一,它存在于沙子、岩石中。可以说芯片就是由沙子“变”出来的,制作芯片的工艺,就是实现“点沙成金”的过程。

在实现这个的过程里,有五大工艺步骤。具体如下。

晶圆制备:“画布”始开

芯片制备工艺的第一步,就是制造晶圆。晶圆是一种很薄且非常光滑的半导体材料圆片,是集成电路的“画布”。一切后续的芯片制备工艺都是在这个“画布”上展开的。

以硅基晶圆为例,晶圆的主要制备步骤如下。

● 硅提炼及提纯。大多数晶圆是由从沙子中提取的硅制成的。将沙石原料放入电弧熔炉中,还原成冶金级硅,再使其与氯化氢反应,生成硅烷,经过蒸馏和化学还原工艺,得到高纯度的多晶硅。

● 单晶硅生长。将高纯度的多晶硅放在石英坩埚中,并用外面围绕着的石墨加热器不断加热,使多晶硅熔化。然后把一颗籽晶浸入其中,拉制棒带着籽晶反方向旋转,同时慢慢地、垂直地向上拉出。这样就形成了圆柱状的单晶硅晶棒。

● 晶圆成型。单晶硅晶棒经过切段、滚磨、切片、倒角、抛光等工序,被制成一片片薄薄的半导体衬底,即晶圆。晶圆的尺寸在这一步骤中确定。

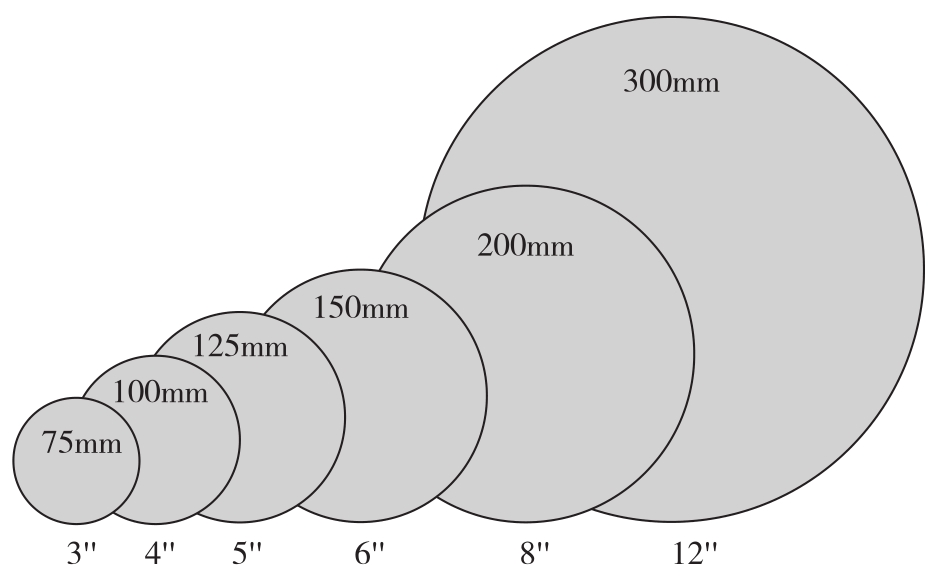

晶圆的尺寸一般以“英寸”为单位。在半导体行业发展初期,由于工艺能力的限制,晶圆直径只有3英寸,约75毫米。此后,随着技术进步和生产效率提高,晶圆尺寸不断增大。目前,在半导体制造中使用的晶圆最大直径为12英寸(约300毫米)。晶圆尺寸演进过程如图3-1所示。

图3-1 晶圆尺寸演进

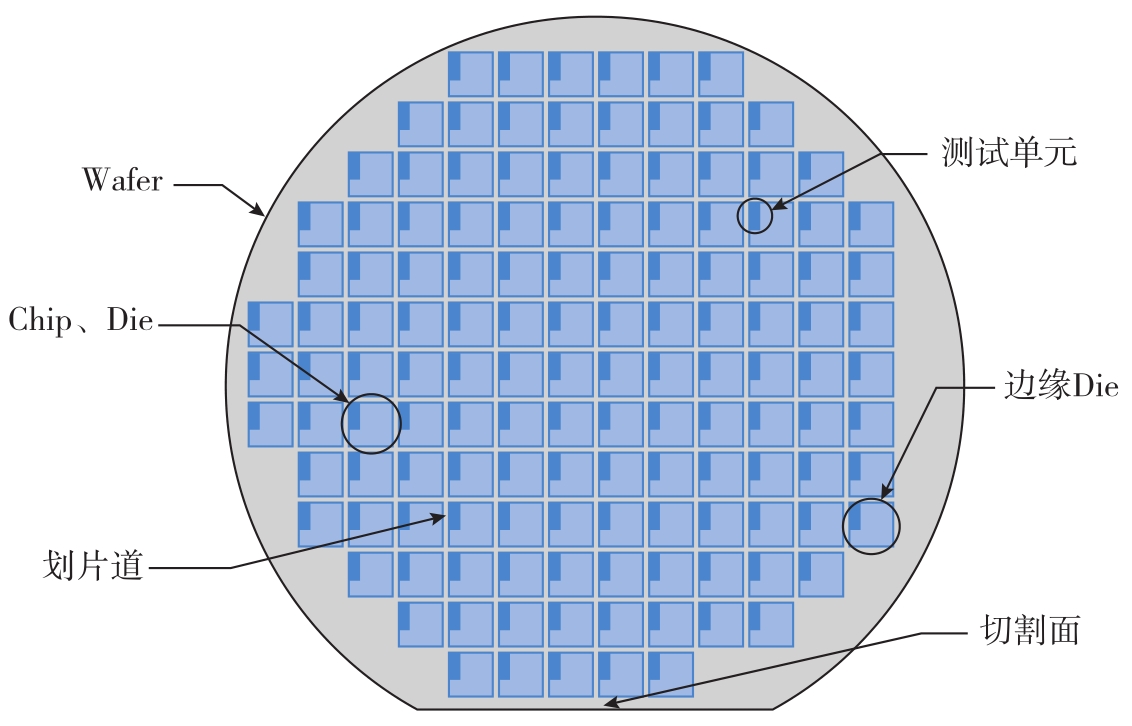

在芯片晶圆上,有一些特殊的部分和特定的名称,如图3-2所示。

图3-2 芯片晶圆的构成

● Wafer:指整张晶圆。

● Chip、Die:指一小片带有电路的硅片。

● 划片道(Scribe line):指Die与Die之间无功能的空隙,可以在这里安全地切割晶圆,而不会损坏到电路。

● 测试单元:一些用于表征Wafer工艺性能的测试电路单元,规律分布于Wafer各位置。

● 边缘Die(Edge Die):Wafer边缘的一部分电路,通常因为工艺一致性或切割破坏,这部分会损失。这部分损失在大的晶圆中占比会减少。

● 切割面(Flat Zone):被切成一个平面的晶圆的一条边,可以帮助识别晶圆方向。

晶圆制备完成后,芯片制备的“画布”就形成了。后续芯片制备工艺由此开始。

氧化工艺:制作“铠甲”

在芯片电路中,除了用于可控导电的各种二极管、三极管,还必须用绝缘物质将不同的电路隔离开来。对于硅基元素来说,得到这种绝缘物质最方便的方法就是将硅进行氧化,形成二氧化硅(SiO 2 )。

SiO 2 是自然界中常见的一种材料,也是玻璃的主要元素。SiO 2 材料的主要特点有:具有高熔点和高沸点(分别为1713℃和2950℃);不溶于水和部分酸,溶于氢氟酸;具有良好的绝缘性、保护性和化学稳定性。

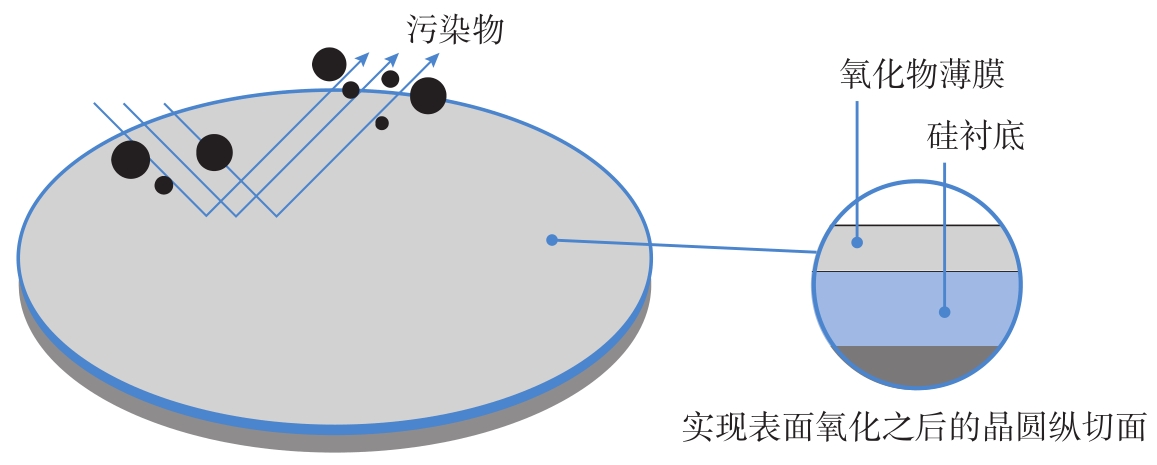

由于以上特性,SiO 2 在芯片制备的多个步骤中被反复使用。芯片制备中的氧化工艺,是在制造过程中在晶圆表面形成一层薄薄的氧化层的过程。这层氧化层可以作为绝缘层,阻止电路之间的漏电;也可以作为保护层,防止后续的离子注入和刻蚀对晶圆造成损伤(见图3-3);还可以作为掩膜层,定义电路图案。

图3-3 氧化层在晶圆表面的保护作用

这些氧化层在半导体器件中也有举足轻重的作用。例如,CMOS器件中的重要结构——MOS(金属-氧化物-半导体)结构中用于金属和半导体之间绝缘的氧化物层(或称栅氧),就是采用氧化工艺制备的。另外,用于隔离不同CMOS器件的厚层氧化物场氧(Field Oxide)、SOI器件中用于隔离衬底与器件的绝缘隔离层,都是采用氧化工艺实现的。

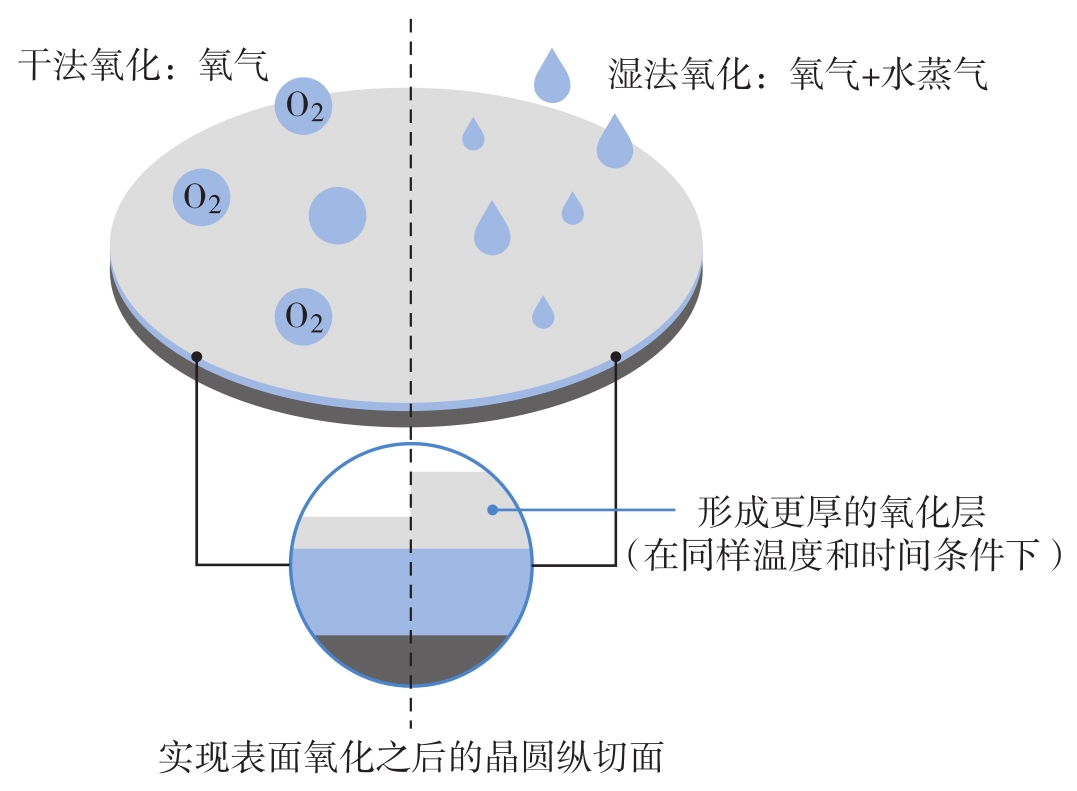

氧化工艺的实现方法有多种,如热氧化法、电化学阳极氧化法等。最常用的是热氧化法,即在高温(800~1200℃)下,利用纯氧或水蒸气与硅反应生成氧化层。热氧化法又分为干法氧化和湿法氧化,干法氧化只使用纯氧,形成较薄、质量较好的氧化层,但生长速度较慢;湿法氧化使用纯氧和水蒸气,形成较厚、密度较低的氧化层,但生长速度较快(见图3-4)。不同类型和厚度的氧化层可以满足不同功能和要求。

图3-4 干法氧化和湿法氧化

在芯片制备工艺中,氧化工艺非常重要,它为后续的制造步骤提供了基础和保障。氧化层不仅可以隔离和保护晶圆,还可以作为掩膜层来定义电路图案。没有氧化层,芯片就无法达到高性能、高可靠性和高集成度的标准。

SiO 2 和部分氧化物有透光特性,由于这些材料的厚度不同,就会对特定波长的光线产生衍射或反射,也就使芯片表面看上去五彩斑斓。所以芯片表面的颜色并不是真正的彩色,而是这些薄膜结构对光的衍射或反射。

通过氧化工艺,脆弱的硅基晶圆穿上了一层“铠甲”。

光刻、刻蚀:图案绘制

有了“画布”素材,终于可以任由芯片设计师挥毫泼墨,自由创作了。光刻和刻蚀步骤就是将芯片设计师所设计的图案,转移到晶圆上的过程。

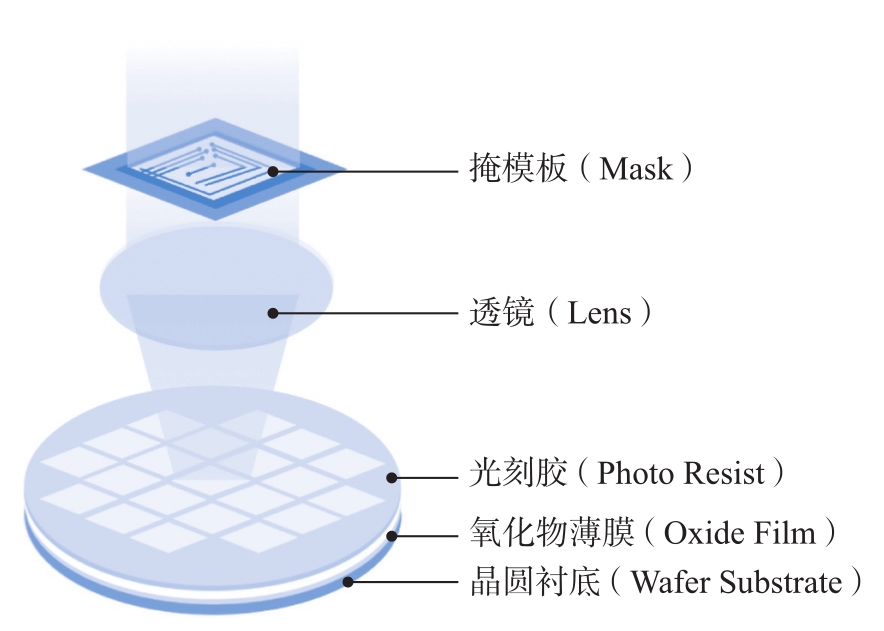

光刻是一种将掩模板(Mask)上的图形转移到涂有光刻胶的晶圆上的技术(见图3-5)。光刻可以将芯片表面上特定的区域去除或保留。

图3-5 芯片的光刻

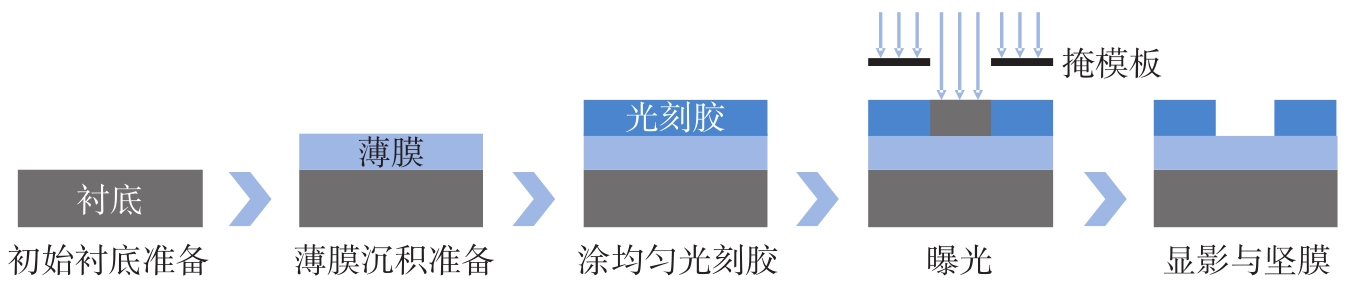

光刻步骤如下(见图3-6)。

● 设计电路并制作掩模板。这一步一般通过计算机辅助设计(CAD)软件完成,在完成电路设计正确性检查(LVS)和设计规则检查(DRC)后,设计图形被转移到掩模板上。掩模板一般是由透明的超纯石英玻璃基片制成,在基片上,需要透光的地方保持透明,需要遮光的地方用金属遮挡。

● 涂光刻胶。涂光刻胶是为了使晶圆对光敏感。在执行这一步骤时,会在晶圆表面均匀涂抹一层对光敏感的物质——光刻胶。光刻胶在光照射后会产生化学变化,于是根据光照射与否,光刻胶也形成溶解和不可溶解的部分。

● 曝光。将光源发出的光线经过掩模板照射到晶圆上时,掩模板上的图形也就被转移到了晶圆上。根据掩模板上图形的不同,光刻胶会溶解形成对应图形。

● 显影与坚膜。用化学显影液溶解掉光刻胶中可溶解的区域,使可见的图形出现在晶圆上。显影后再进行高温烘焙,使剩余的光刻胶变硬并提高黏附力。

图3-6 光刻的主要过程

光刻之所以得名,就是因为它利用光线,把带有图案的掩模板上的图形转移到晶圆上。在芯片制备中,要尽可能地缩小电路尺寸,所以对光刻的精度要求也越来越高。高精度的光刻机是光刻步骤的基础,这就是为什么“光刻”成为备受关注的工艺步骤。

为了支持更高精度的光刻,也有先进的光刻机被制造出来。目前最先进的光刻机技术是极紫外(Extreme Ultra-violet,EUV)光刻技术,它使用波长为13.5纳米的极紫外线作为光源进行电路光刻,可以制造出7纳米及以下工艺节点的芯片。ASML是EUV光刻机的领导厂商,其最新型号的光刻机号称可实现0.3纳米的精度。

光刻是芯片制备中最昂贵的工艺,在先进工艺中,光刻的成本可以占整个芯片加工成本的1/3,甚至更多。

经过光刻之后,所需要的图案已经被印在了晶圆表面的光刻胶上。但要实现芯片的制作,还需要把芯片按照光刻胶的图形复刻出来。这个复刻的过程就叫刻蚀(Etching)。

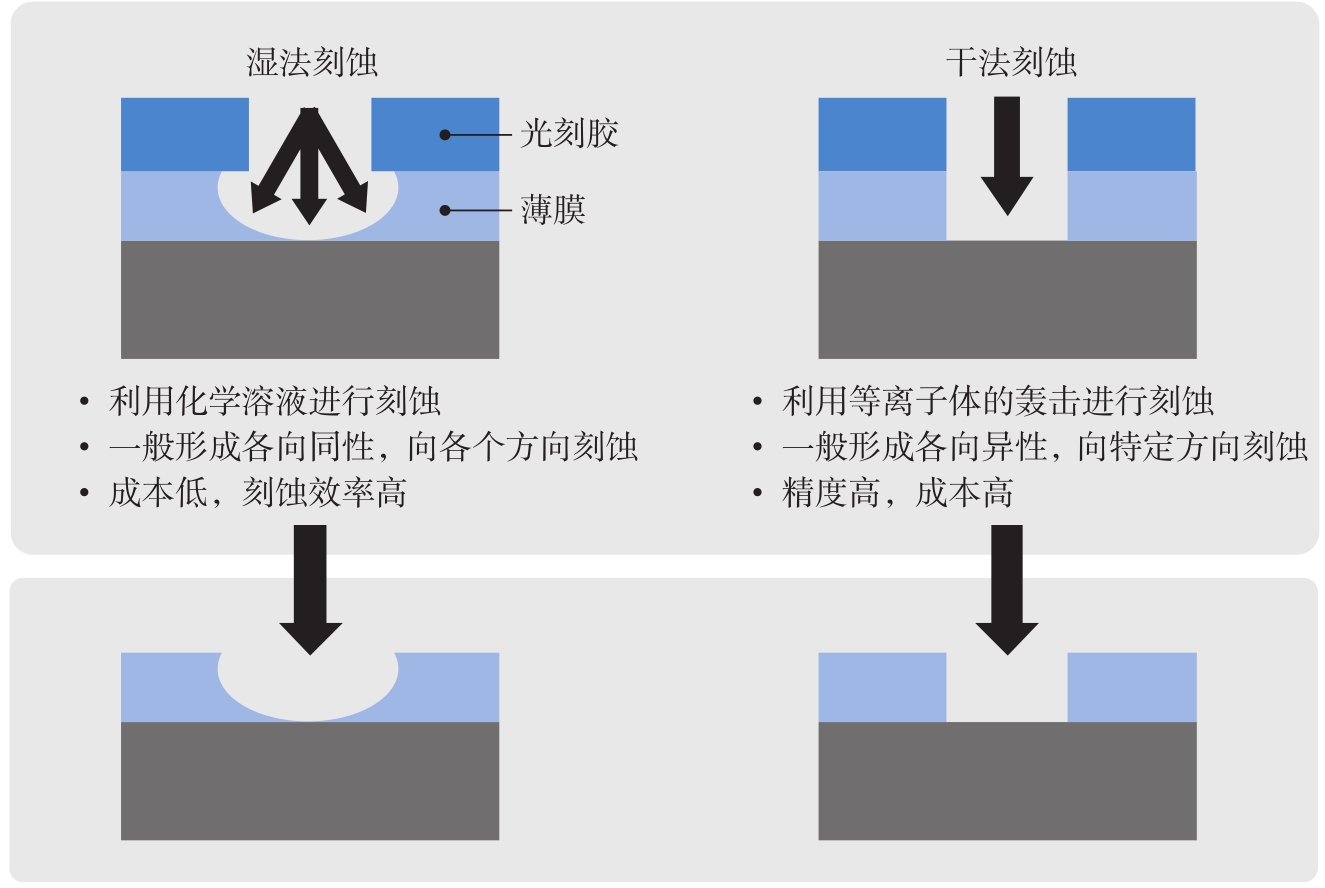

刻蚀方法分为两类,分别是湿法刻蚀和干法刻蚀(见图3-7)。

图3-7 湿法刻蚀和干法刻蚀

湿法刻蚀是将晶圆浸入含有特定化学剂的溶液中,利用化学反应来溶解掉未被光刻胶保护的半导体结构的方法。由于溶液不能被很好地控制方向,因此可能会导致刻蚀不均匀,造成刻蚀不足或过度;另外,由于溶液会残留在晶圆上,因此需要额外的清洗步骤来去除污染物。

干法刻蚀是用等离子体或离子束等来对晶圆进行轰击,去除未被保护的半导体结构的方法。相较于湿法刻蚀,干法刻蚀精度高、选择性和方向性好,并且不会产生残留物,适用于制造高集成度的芯片。干法刻蚀也有缺点,如成本高、设备复杂、处理时间长。

在芯片制备过程中,会根据不同的目标和需求,灵活选择最适合的工艺。甚至在同一个器件制作的不同步骤中,会混合使用湿法刻蚀和干法刻蚀。

通过光刻及刻蚀步骤,就可以将设计的图形真正显现在晶圆上。需要说明的是,光刻或刻蚀步骤一次只能实现一层半导体结构,由于半导体器件是多层器件,通常需要迭代多次才能将半导体器件完整刻蚀出来;并且随着工艺复杂度的不同,需要的层数也不同。例如,在0.18微米的CMOS工艺中,需要的光罩层数约为20层,而对于7纳米左右的CMOS工艺来说,则需要55~60层。

掺杂工艺:注入灵魂

如果说以上工艺步骤是任何微机械器件都必须考虑的工艺的话,那么掺杂(Doping)工艺就是芯片制备工艺中的灵魂了。

说掺杂工艺是芯片制备工艺中的灵魂,是因为电路中各半导体器件的电学性能在此步骤形成。在此步骤之前,整片晶圆不过是一片冷冰冰的材料,经过此步骤,才有了各种各样的二极管、三极管、CMOS及电阻等。

掺杂工艺是指在半导体材料中引入少量的杂质原子,以改变其电学性质的方法。掺杂工艺可以改变半导体的导电类型,形成PN结,制造半导体器件等。掺杂工艺如此重要,是因为它可以改变半导体的电导率、载流子类型和浓度、能带结构等电学性质,从而实现不同的功能和性能。半导体的导电性能可控,就是通过掺杂工艺来实现的。

有了掺杂工艺,就可以制造出PN结、双极型晶体管、场效应晶体管等基本的半导体器件,也可以用来调节MOS晶体管的阈值电压、改善接触电阻、增强辐射耐受性等。掺杂工艺是芯片制备工艺中最核心和最基础的技术之一,对于半导体器件的设计和制造具有决定性的影响。

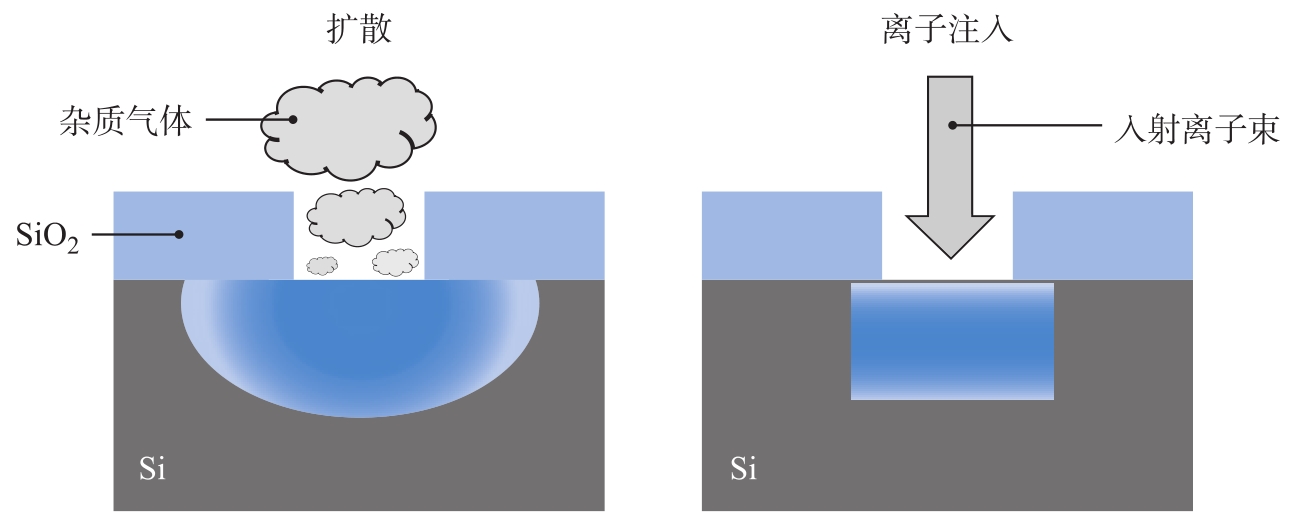

芯片制备工艺中实现掺杂的主要方法有两种,即热扩散和离子注入(见图3-8)。热扩散是在高温下(约1000℃)将半导体暴露在一定掺杂元素的气态下,利用化学反应和热运动使杂质原子扩散到半导体表层的过程。离子注入是将杂质原子电离成离子,用高能量的电场加速,然后直接轰击半导体表面,使杂质原子“挤”进晶体内部的过程。

图3-8 两种掺杂工艺对比

经历了掺杂工艺,从沙子而来的晶圆终于有了灵魂。

薄膜沉积:阡陌交通

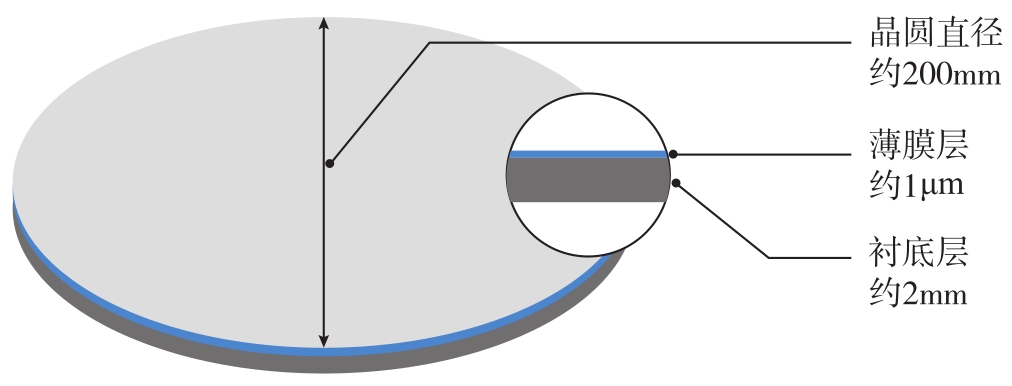

薄膜工艺是指在半导体晶圆上沉积各种材料,以实现不同电路功能或特性的过程。和前面几个工艺步骤按工艺过程来命名不同,这一步骤是按材料的“状态”来命名的。这个命名甚至让人看起来有些费解,从图3-9来看,半导体器件看上去都是一个个厚厚的器件,哪来的薄膜?

图3-9 半导体器件中大部分结构在1微米左右厚度的薄膜中实现

其实为了理解方便,半导体器件结构在图示时经过了抽象和非等比例的放大,实际中半导体器件是在晶圆上非常薄的一层内实现的,通常厚度在1微米以内。对于一个8英寸(200毫米)的晶圆来说,1微米厚度的薄膜的制作,相当于在200米直径的操场上,均匀地堆积1毫米厚的沙子。

正是因为这层结构非常薄,于是被称作薄膜工艺。这么薄的膜层不能通过机械方式来制造,于是,掺杂沉积(Deposition)工艺被发明出来。

在芯片制备工艺里,沉积是指在原子或分子水平上,将材料沉积在晶圆表面做成一个薄层的过程。沉积工艺就像是喷涂刷,将涂料均匀地薄薄喷洒在晶圆表面。

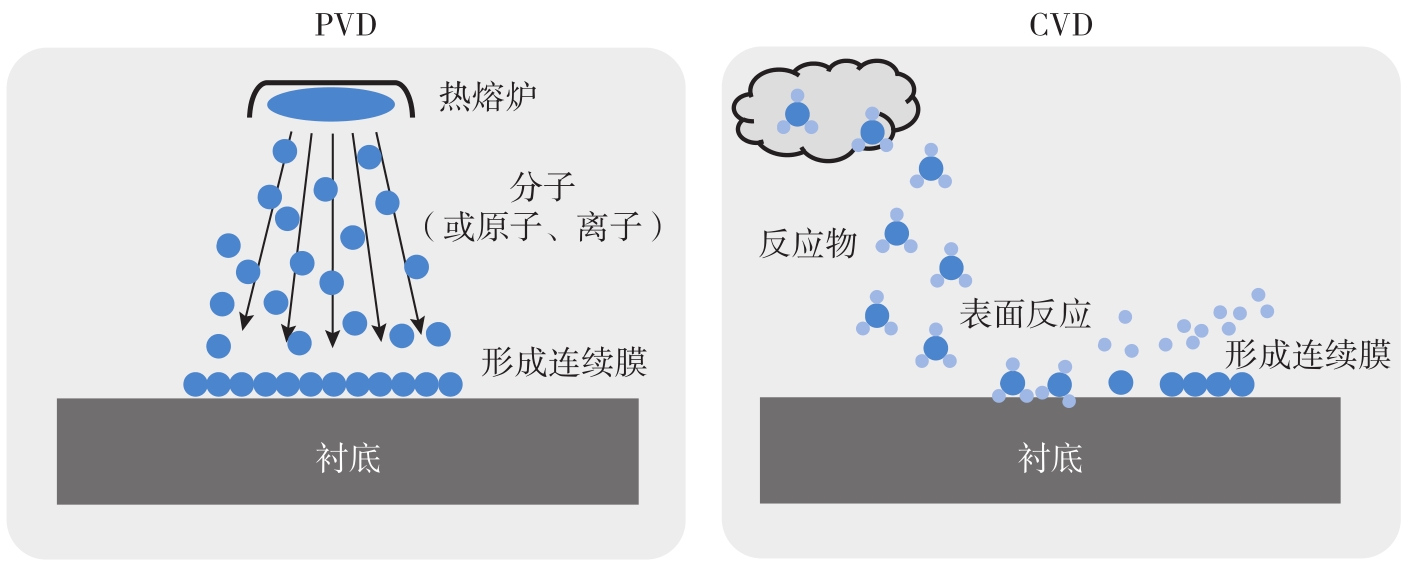

根据实现方法的不同,沉积主要分为物理气相沉积(PVD)和化学气相沉积(CVD),如图3-10所示。PVD是利用物理方法,将材料源气化成气态原子、分子,或者电离成离子,并通过低压气体,在基体表现沉积成薄膜的过程,一般用来沉积金属薄膜。CVD是利用含有薄膜元素的一种或几种气相化合物,在衬底表面进行化学反应形成薄膜的方法,一般用于沉积半导体或绝缘体及金属合金等。为了增强化学反应,CVD也可以与其他方法相结合,如等离子增强CVD(Plasma Enhanced CVD,PECVD)就是利用等离子体来激活化学反应,改善CVD的方法。根据不同目标和需求,PVD和CVD在实际工艺流程中也可以自由选择。

图3-10 PVD与CVD

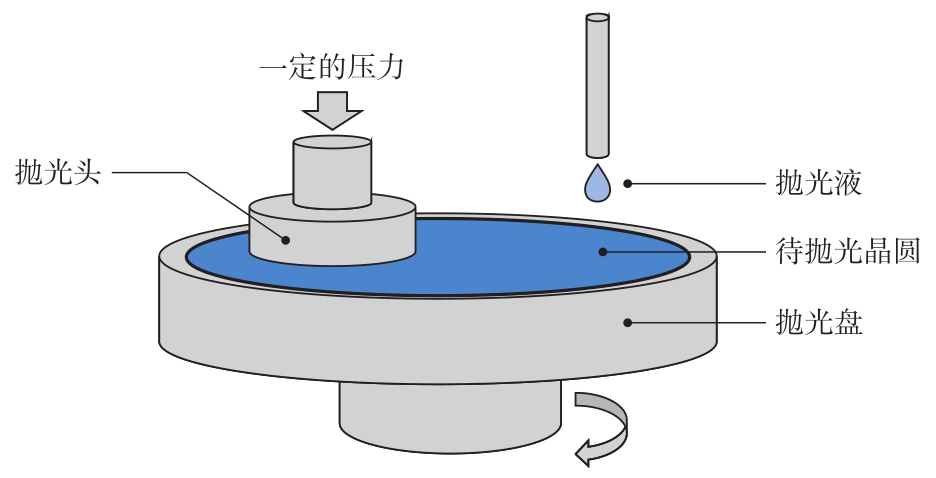

沉积完成材料的喷涂之后,还需要用抛光工艺来找平。必须对喷涂后的材料找平的原因是随着半导体技术的进步,对各薄膜层精度的要求也越来越高,于是,需要对晶圆表面进行平坦化,消除不同材料层之间的起伏和缺陷,提高光刻的精度和质量。抛光(Polishing)就是用于晶圆表面薄膜层平整化的技术。在抛光工艺中,最主要的工艺是化学机械抛光(Chemical Mechanical Polishing,CMP),CMP是一种利用化学腐蚀和机械摩擦来实现晶圆表面平坦化的技术,研磨对象主要是浅沟槽隔离(STI)、层间膜和铜互连层等(见图3-11)。

图3-11 CMP

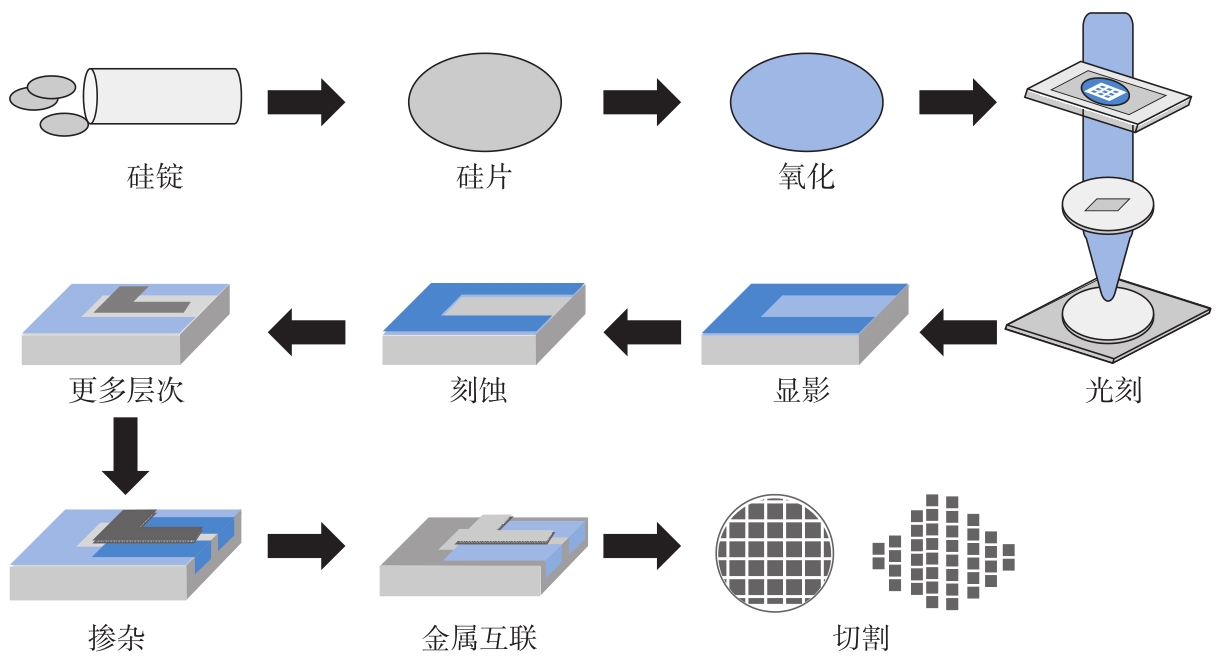

以上就是芯片制备的主要工艺,以上工艺以硅基半导体为主要参考,其他工艺(如GaAs、SiGe等化合物半导体)会略有不同,但基本思路一致。在具体半导体工艺实现上,通过将以上关键工艺有机整合,形成一个完整的工艺流程(见图3-12),就可以完成半导体工艺的开发。

图3-12 半导体工艺流程整合

虽然看起来半导体工艺步骤并不是太复杂,但在实际工艺中,需要考虑各个工艺步骤之间的影响和优化,需要确保各工艺步骤的稳定性和一致性,需要达到最佳的器件特性、产量和成本,这就使半导体工艺整合变得非常重要。半导体工艺整合是推动半导体行业发展和创新的关键因素,也成为半导体器件代工厂的核心竞争力之一。