本节介绍Cortex-M0+处理器的存储空间结构,内容包括存储空间映射、代码区域地址映射、SRAM区域地址映射、外设区域地址映射、PPB地址空间映射、SCS地址空间映射,以及系统控制和ID寄存器。

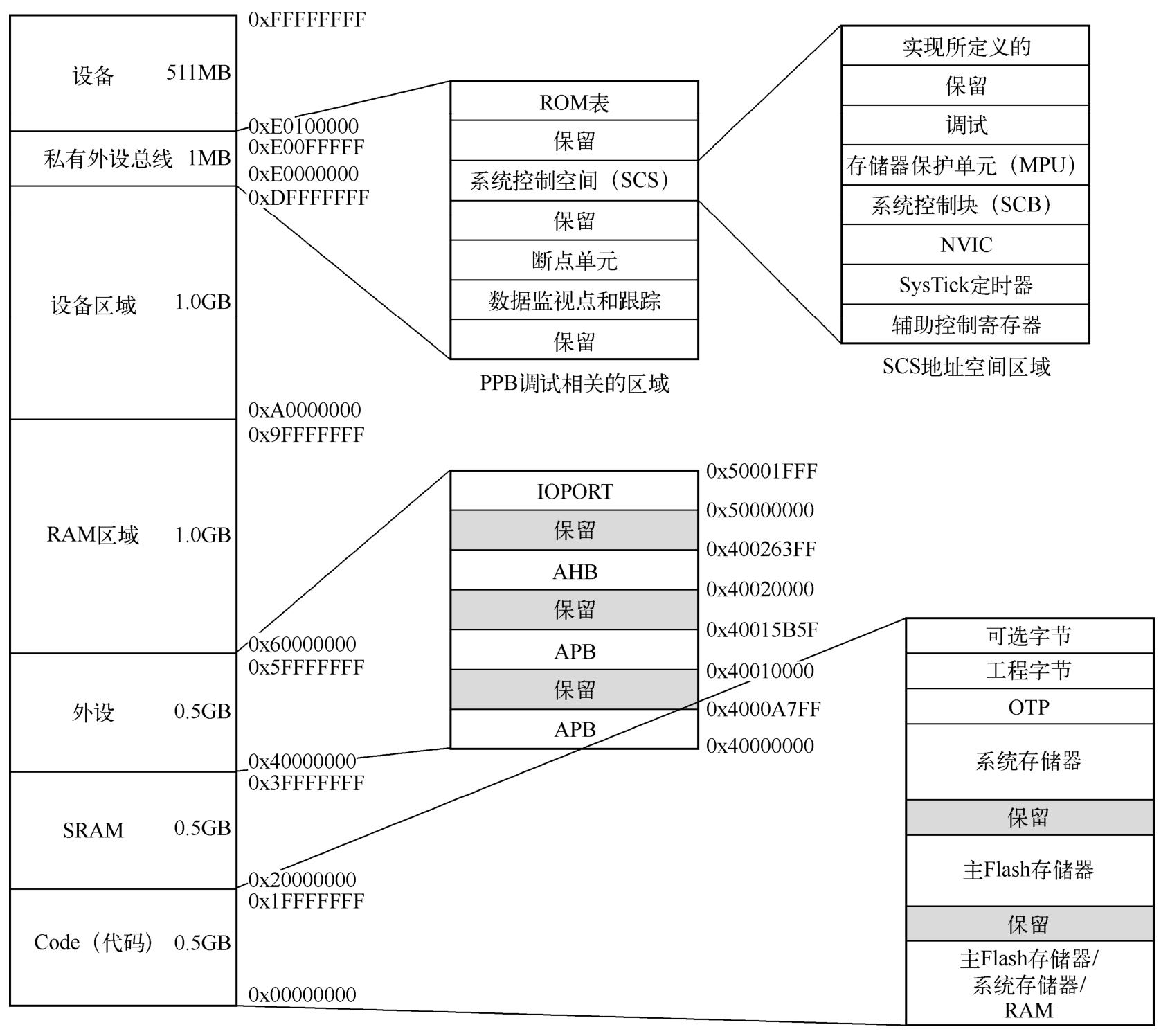

Cortex-M0+处理器采用了Armv6-M架构,该架构支持预定义的32位地址空间,并细分为代码、SRAM和外设,以及片上和片外资源的区域,如图2.12所示。其中,片上是指紧耦合到处理器的资源。地址空间支持8个基本分区,每个分区是0.5GB,包括:

(1)代码;

(2)SRAM;

(3)外设;

(4)两个RAM区域;

(5)两个设备区域;

(6)系统。

该架构分配用于系统控制、配置以及用作事件入口点或向量的物理地址。该架构定义相对基地址的向量,该基地址在Armv6-M中固定为地址0x00000000。

地址空间0xE0000000到0xFFFFFFFF保留供系统级使用。

注: 尽管默认规定了这些区域的使用方法,但是程序设计人员可以灵活地根据具体要求定义存储器地址空间映射,例如,访问内部私有外设总线。

图2.12 Cortex-M0+处理器的存储器地址空间映射

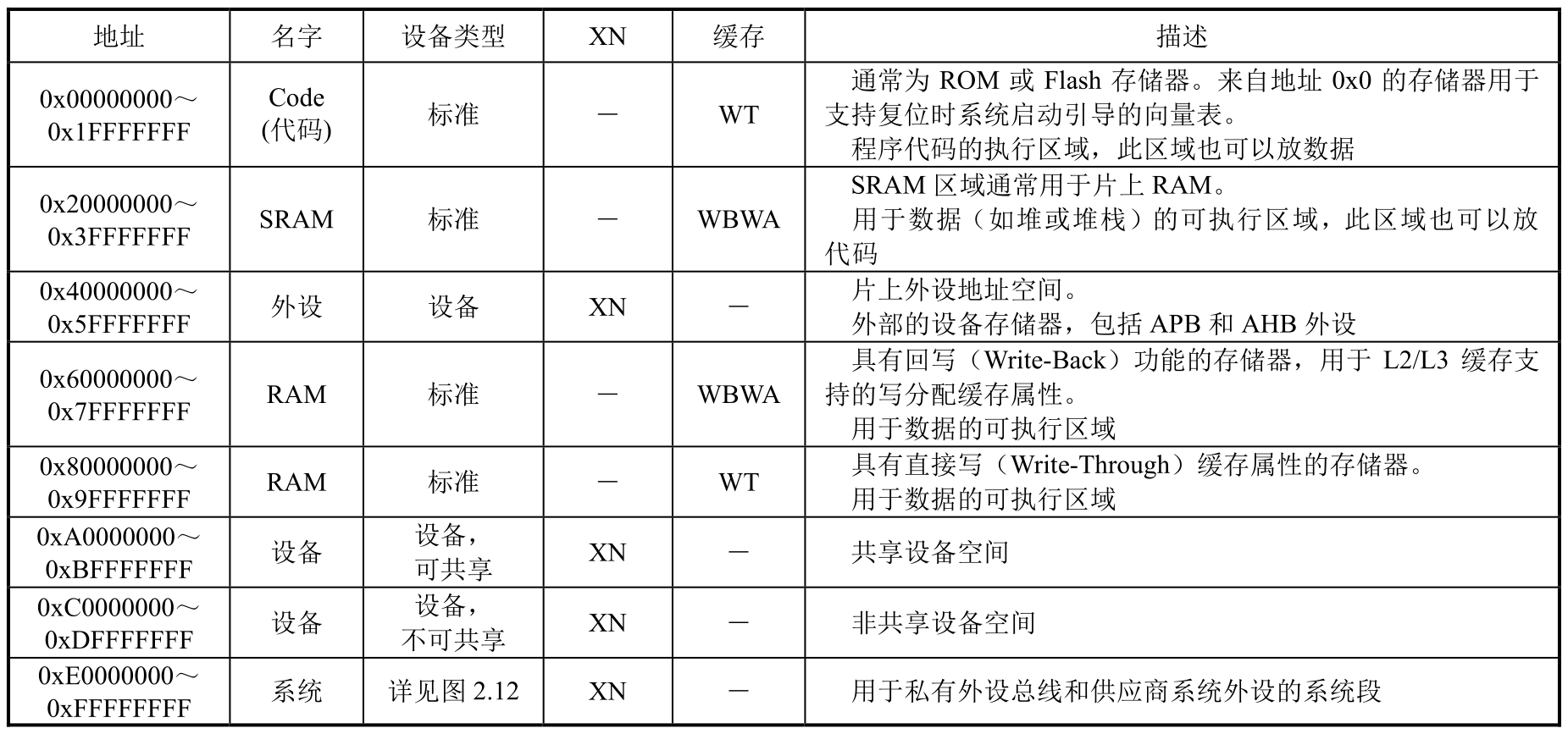

Armv6-M地址映射关系如表2.2所示。

表2.2 Armv6-M地址映射关系

表中:

(1)XN表示从不执行区域(execute never region)。从XN区域执行代码的任何尝试都会出错,从而生成硬件故障异常。

(2)缓存列指示用于标准存储器区域、内部和外部缓存的缓存策略,以支持系统缓存。声明的缓存类型可以降级,但不能升级,如下:

①直接写(Write-Through,WT),可以看作非缓存;

②回写和写分配(Write-Back,Write Allocate,WBWA),可以看作直接写或非缓存。

(3)在设备类型一列中,可共享表示该区域支持同一存储器区域中多个代理共享使用。这些代理可以是处理器和DMA(直接存储器访问)代理的任意组合。标准表示处理器可以对交易进行重新排序以提高效率或者执行预测读取。设备表示处理器将保持相对于到设备或强顺序存储器的其他交易的顺序。

注: (1)Armv6-M不支持诸如LDREX或STREX之类的互斥访问指令,也不支持任何形式的原子交换指令。在使用共享存储器的多处理环境中,软件必须考虑这一点。

(2)代码、SRAM和外部RAM区域都可以保存程序。

(3)MPU可以覆盖该部分介绍的默认存储器访问行为。

Code(代码)区域地址映射关系如表2.3所示。

表2.3 Code区域地址映射关系(STM32G071xx和STM32G081xx)

Flash存储器的构成形式为72位宽的存储单元(64位加8个ECC位),可用于保存代码和数据常量。Flash存储器的组织方式如下。

(1)一个主存储器块,包含64个(具体数量和器件型号有关)2KB的页面,每页有8行,每行256B。

(2)信息块。

①在系统存储器模式中,CPU从系统存储器启动引导。该区域是保留区域,包含用于通过以下接口之一对Flash存储器进行重新编程的启动引导程序,这些接口包括:USART1、USART2、I2C1和I2C2(适用于所有器件),USART3、SPI1和SPI2(适用于STM32G071xx、STM32G081xx、STM32G0B1xx和STM32G0C1xx),以及USB(DFU)和FDCAN2(适用于STM32G0B1xx和STM32G0C1xx)。在生产线上,对芯片进行编程并提供保护,以防止伪造的写/擦除操作。

②1KB(128个双字)一次性可编程(One-Time Programmable,OTP)用于用户数据。OTP数据无法删除,只能写入一次。如果只有1位为0,则即使值0x0000 0000 0000 0000,也无法再写入整个双字(64位)

当读出保护机制(RDP)级别为1,并且引导源不是主Flash存储器区域时,无法读取OTP区域。

③用于用户配置的选项字节。

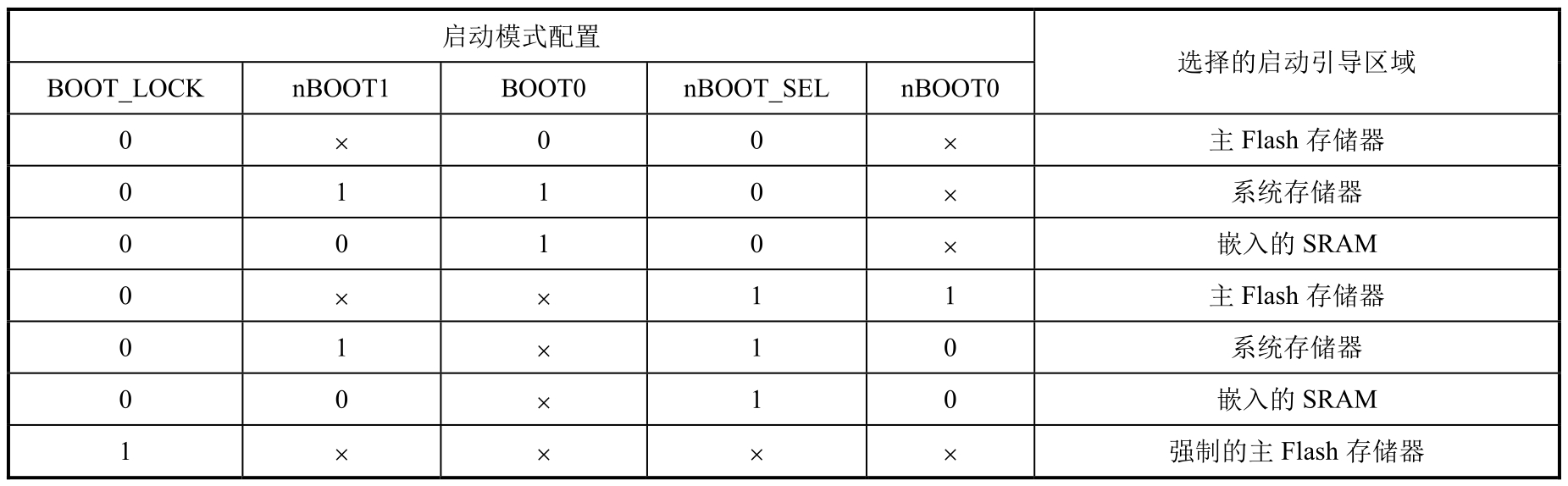

注: 在STM32G0x1中,可以通过BOOT0引脚,FLASH_SECR寄存器中的BOOT_LOCK位以及用户选项字节中的引导配置位nBOOT1、nBOOT_SEL和nBOOT0选择三种不同的引导模式,启动模式配置如表2.4所示。

表2.4 启动模式配置

复位后,在SYSCLK的第四个上升沿,锁存引导模式配置。用户可以设置与所需引导模式相关的引导模式配置。

当从待机模式退出时,也会重新采样引导模式配置。因此,在待机模式下必须保持所要求的启动引导模式。当从待机模式退出时,CPU从地址0x00000000获取堆栈顶部的值,然后从在0x00000004的启动存储器启动代码。

根据所选择的启动引导模式,可以按如下方式访问主Flash存储器、系统存储器或SRAM。

(1)从主Flash存储器启动:主Flash存储器在启动存储器空间(0x00000000)具有别名,但是仍可以从其原始存储空间(0x08000000)访问。换句话说,可以从地址0x00000000或0x08000000开始访问主Flash存储器内容。

(2)从系统存储器启动:系统存储器在启动引导存储器空间(0x00000000)中是别名,但仍可以从其原始的存储器空间0x1FFF0000访问。

(3)从SRAM启动:SRAM在引导存储器空间(0x00000000)中具有别名,但仍可以从其原始存储空间(0x20000000)对其进行访问。

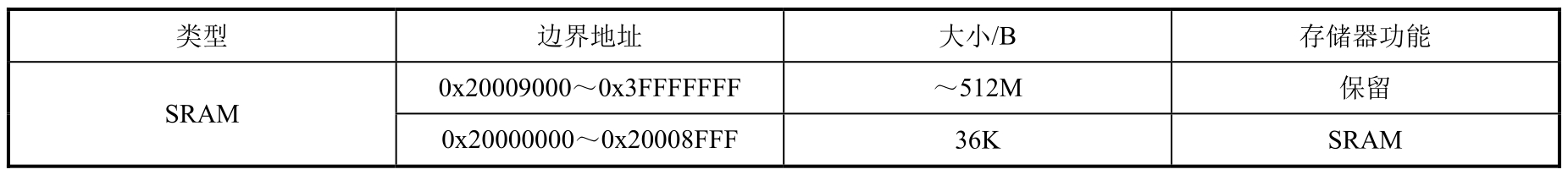

SRAM区域地址映射关系如表2.5所示。

表2.5 SRAM区域地址映射关系

STM32G071x8/xB器件提供了32KB的具有奇偶校验的嵌入式SRAM。硬件奇偶校验可以检测到存储器的数据错误,这将有助于提高应用程序的功能安全性。

当由于应用程序的安全性要求不高而不需要奇偶校验保护时,可以将奇偶效验存储位用作附加的SRAM,以将其总大小增加到36KB。

片内嵌入SRAM的优势是可以以零等待状态和CPU的时钟速度读写存储器。

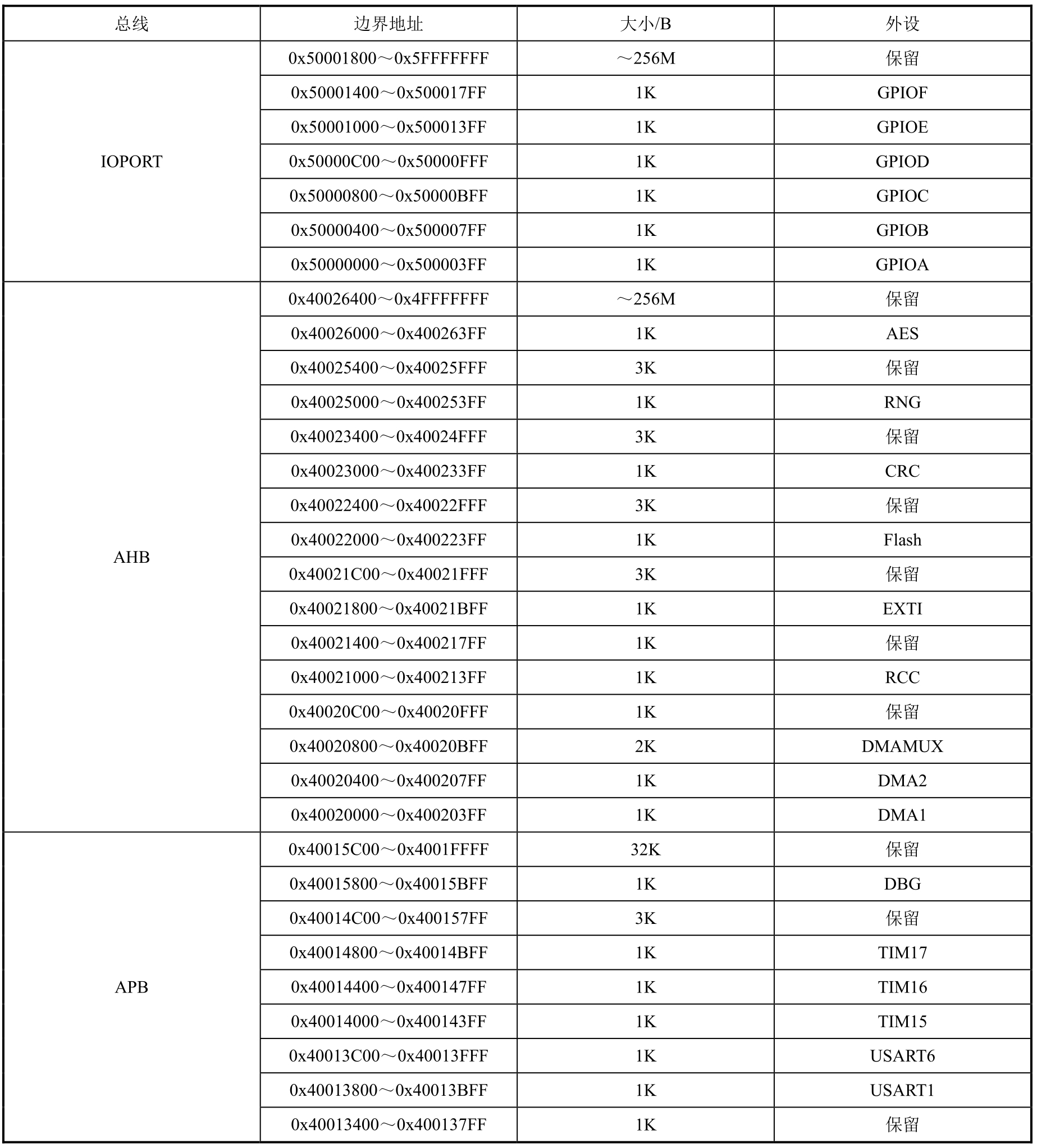

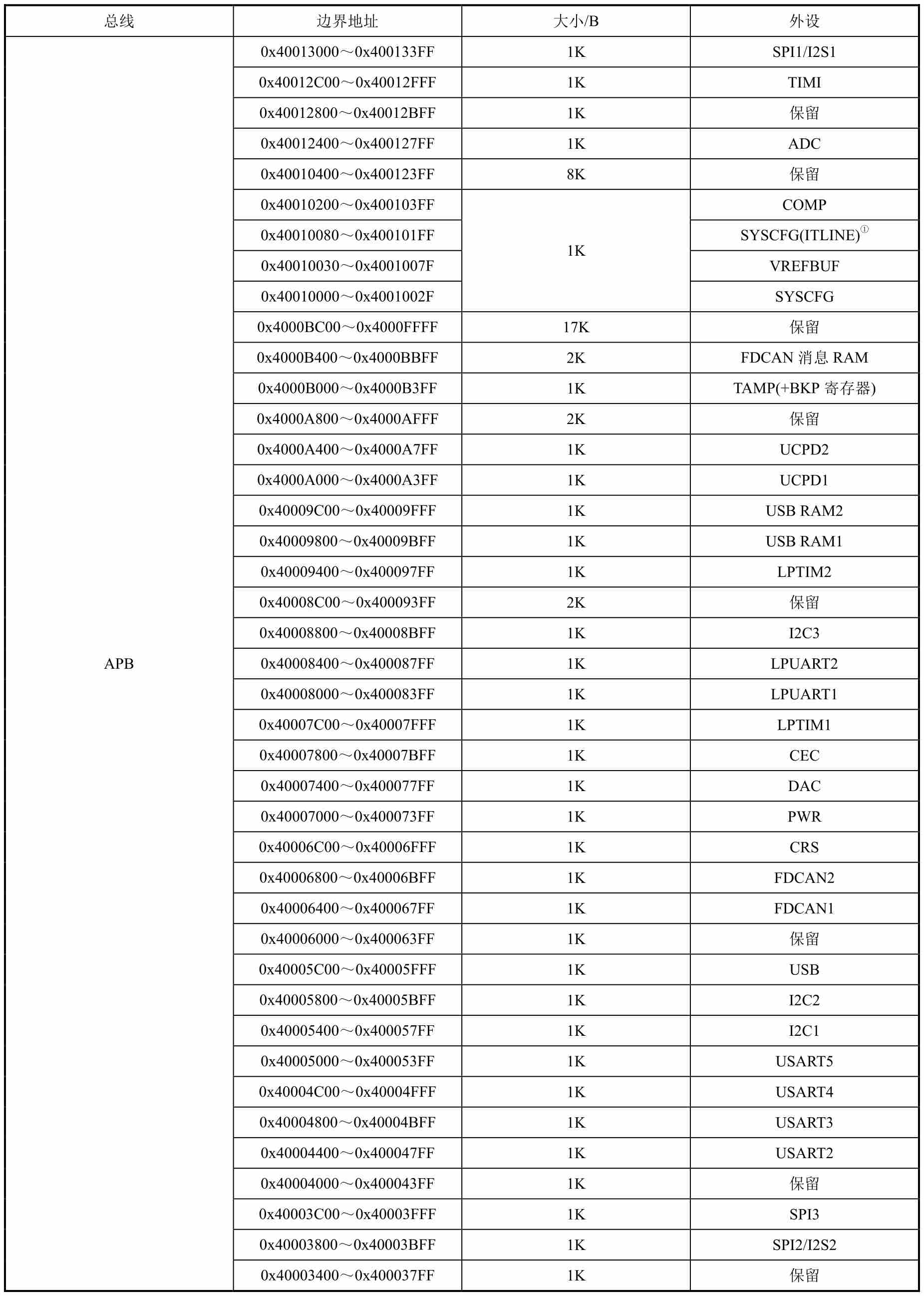

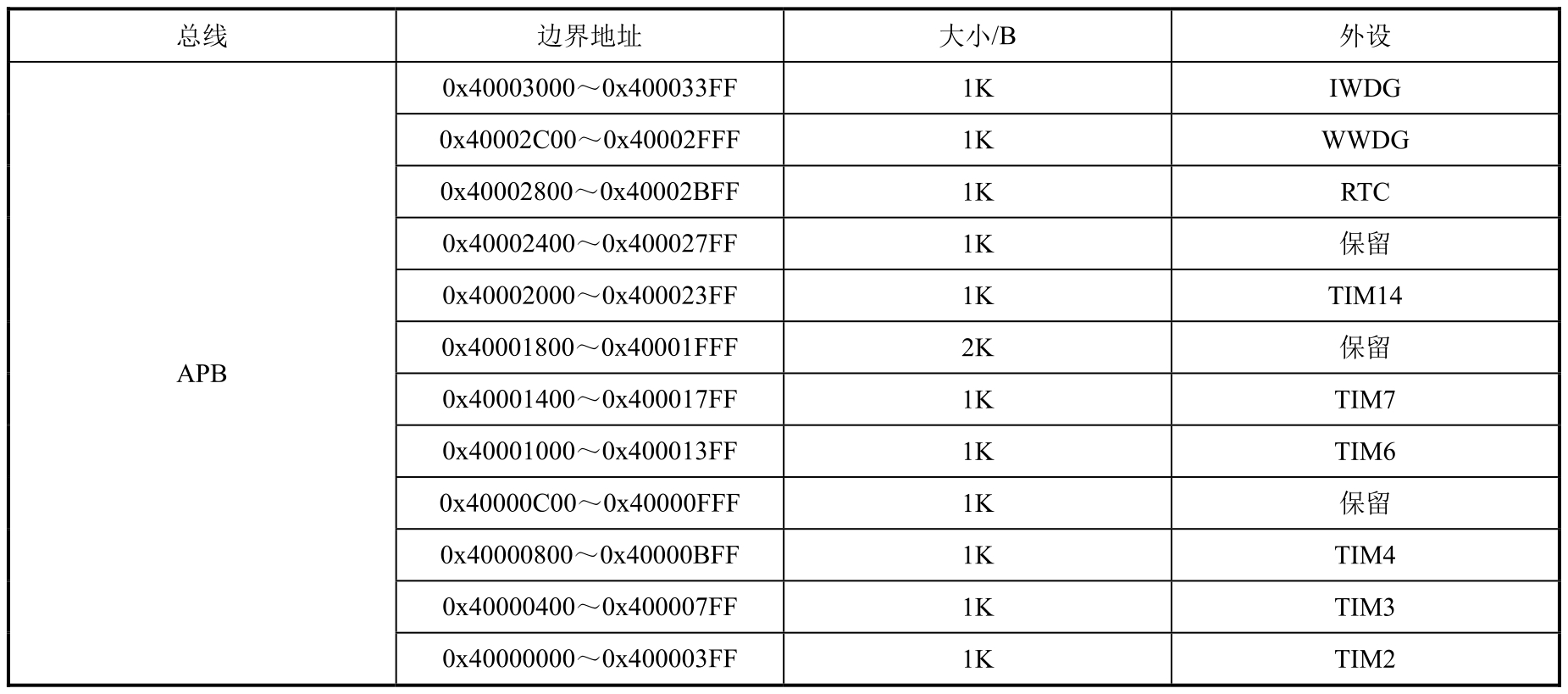

外设区域地址映射关系(不包括Cortex-M0+内部外设)如表2.6所示。

表2.6 外设区域地址映射关系

续表

续表

①SYSCFG(ITLINE)寄存器使用0x40010000作为参考外设基地址。

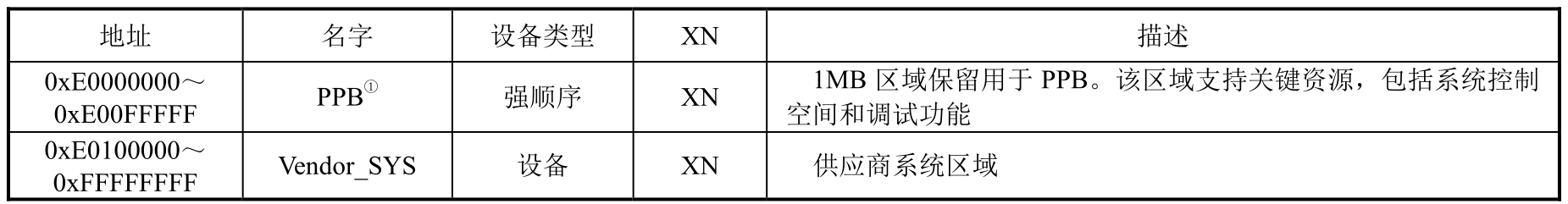

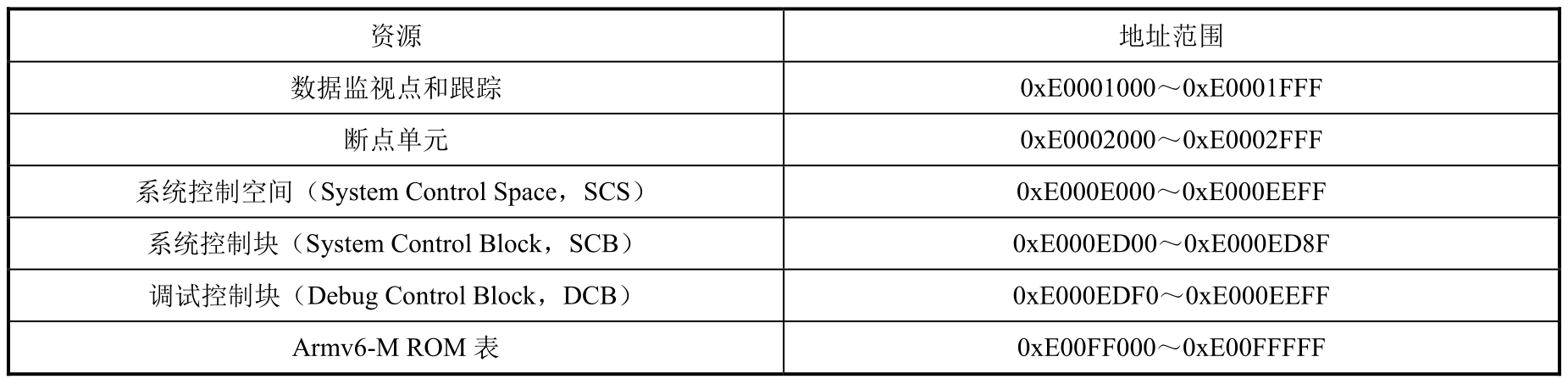

0xE0000000~0xFFFFFFFF区域的存储空间映射关系如表2.7所示。

表2.7 0xE0000000~0xFFFFFFFF区域的存储空间映射关系

①在所有实现中,对它只能通过特权访问。

从表2.7中可知,地址空间为0xE0000000~0xE00FFFFF的区域为PPB区域,PPB地址空间映射关系如表2.8所示。

表2.8 PPB地址空间映射关系

注: 表中地址不连续的区域为保留区域。

除了SCB、DCB和SCS中的其他调试控制外,其他与调试相关的资源在Armv6-M系统地址映射的PPB区域内分配了固定的4KB区域。这些资源如下。

(1)断点单元(BreakPoint Unit,BPU)。它提供了断点支持。BPU是Armv7-M中可用的Flash补丁和断点块(Flash Patch and Breakpoint,FPB)的子集。

(2)ROM表。ROM表的入口为调试器提供了一种机制,以标识实现所支持的调试基础结构。

通过DAP接口,可以访问这些资源以及SCS中的调试寄存器。

在Armv6-M架构中,PPB区域中的通用规则包括:

(1)将该区域定义为强顺序存储器;

(2)始终以小端方式访问寄存器,与处理器当前的端状态无关;

(3)PPB区域地址空间仅支持对齐的字访问,字节和半字访问是不可预测的。

注: 这与Armv7-M不同,后者在某些情况下支持字节和半字访问。对于Armv6-M,软件必须执行读-修改-写访问序列,在该序列中,软件必须修改PPB区域中某个字内的字节字段。

(4)术语“设置”,表示写入1;术语“清除”,表示写入0。该术语适用于多个位,所有位均为写入值。

(5)通过将0写入相应的寄存器位来禁用功能,并通过将1写入该位来使能。

(6)在将某一定义位在读取时清零的情况下,当该位的读取与将该位设置为1的事件一致时,该架构保证以下原子行为:

①如果该位读取为1,则通过读操作将该位清除为0;

②如果该位读取为0,则将该位设置为1,并通过后续的读取操作将其清零。

(7)保留的寄存器或位字段必须看作UNK/SBZP。

(8)对PPB的非特权访问会产生硬件故障错误,而不会引起PPB访问。

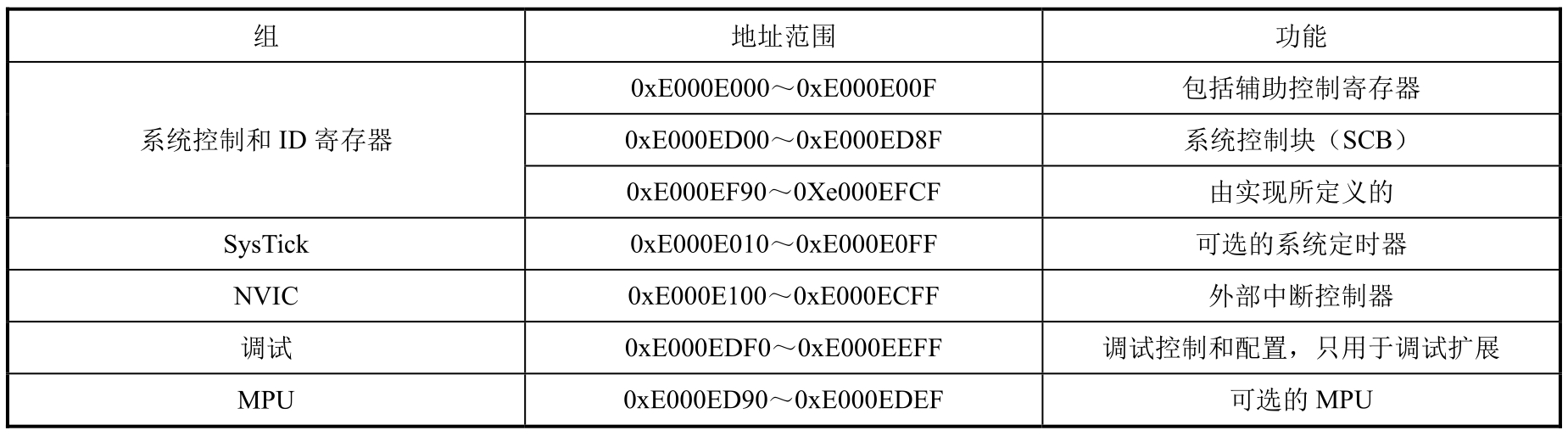

SCS是存储器映射的4KB地址空间,它提供了32位寄存器用于配置、状态报告和控制。SCS寄存器一般分为以下几组:

(1)系统控制和识别;

(2)CPUID处理器标识空间;

(3)系统配置和状态;

(4)可选的系统定时器,SysTick;

(5)嵌套向量中断控制器(Nested Vectored Interrupt Controller,NVIC);

(6)调试。

SCS地址空间映射如表2.9所示。

表2.9 SCS地址空间映射关系

注: 未分配的地址被保留。

在Armv6-M中,SCS中的系统控制块(SCB)提供了处理器的关键状态信息和控制功能。SCB支持如下功能。

(1)不同级别的软件复位控制。

(2)通过控制表的指针来管理异常模型的基地址。

(3)系统异常管理,包括:

①异常使能;

②将异常的状态设置为“挂起”,或者从异常中删除挂起的状态;

③将每个异常的状态显示为非活动、挂起或者活动;

④设置可配置系统异常的优先级;

⑤提供其他控制功能和状态信息。

这里不包括外部中断处理,NVIC管理所有的外部中断。

(4)当前正在执行代码和挂起的最高优先级异常的异常号。

(5)其他控制和状态功能。

(6)调试状态信息。这是通过调试专用寄存器区域中的控制和状态来实现的。

思考与练习2.12:Cortex-M0+处理器的存储器地址空间为_____________。

思考与练习2.13:Cortex-M0+处理器的中断向量表的开始地址是________________。

思考与练习2.14:Cortex-M0+处理器的PPB所实现的功能是_________________。

思考与练习2.15:说明Cortex-M0+处理器SCS实现的功能。

思考与练习2.16:说明Cortex-M0+处理器SCB实现的功能。

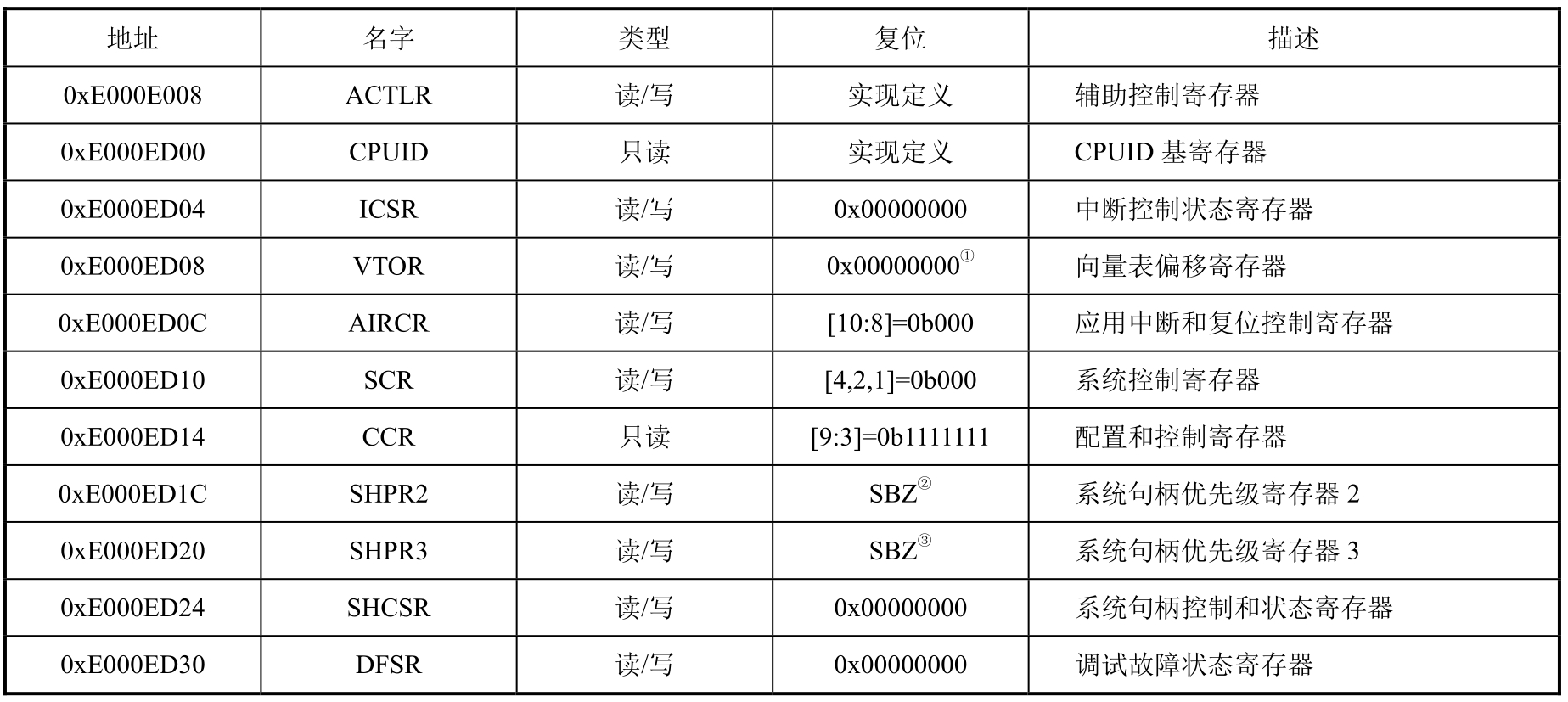

系统控制和ID寄存器如表2.10所示,从存储器基地址开始按地址顺序显示系统控制和ID寄存器。

表2.10 系统控制和ID寄存器

①查看寄存器描述,以获取更多信息;

②SVCall优先级位[31:30]是0;

③SysTick位[31:30]和PendSV位[23:22]是0。

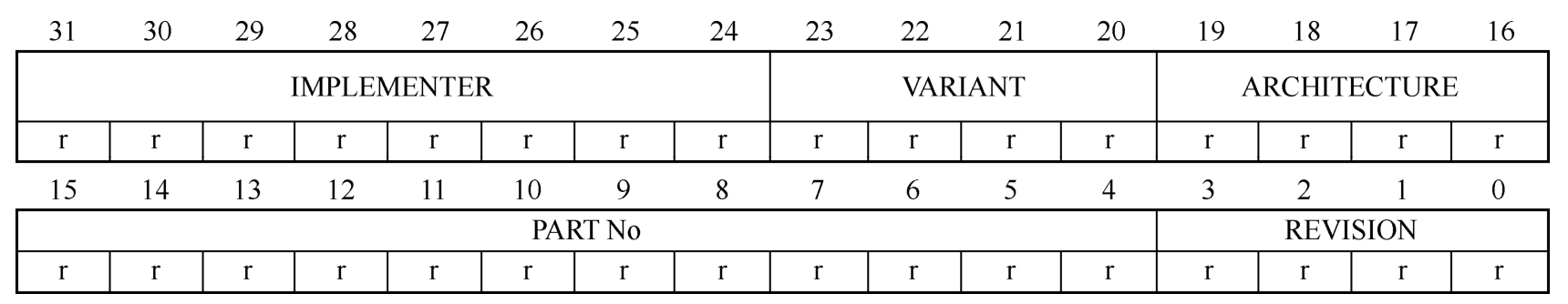

1.CPUID基寄存器

CPUID基寄存器包含处理器部件号、版本和实现信息,其位分配如图2.13所示。

图2.13 CPUID基寄存器的位分配

(1)[31:24](IMPLEMENTER):表示实施者代码,取值为0x41,标识为Arm;

(2)[23:20](VARIANT):表示rnpm修订状态中的主要修订号n,取值为0x0,表示修订版0;

(3)[19:16](ARCHITECTURE):表示定义处理器架构的常数,取值为0xC,表示Armv6-M架构;

(4)[15:4](PART No):表示处理器的器件号,取值为0Xc60,表示Cortex-M0+;

(5)[3:0](REVISION):表示rnpm修订状态中的小修订号m,取值为0x1,表示补丁1。

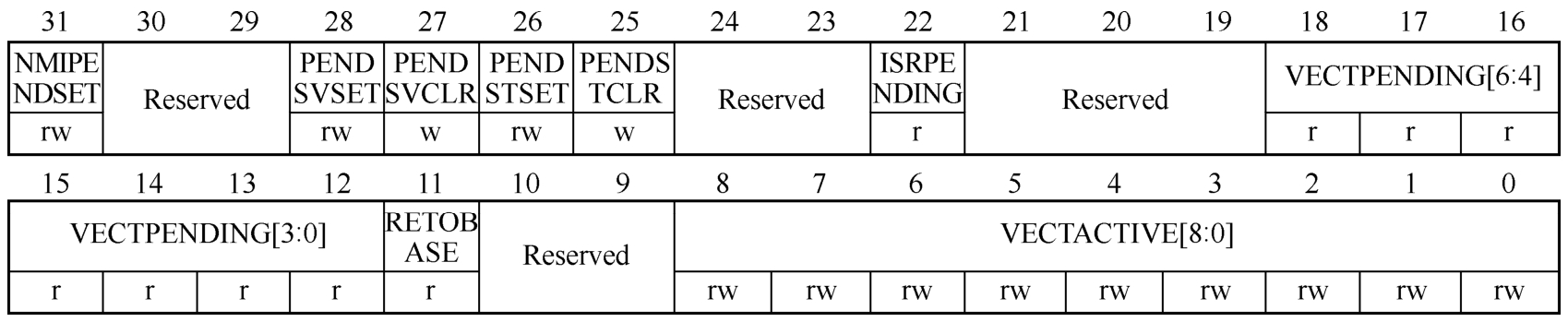

2.中断控制和状态寄存器

中断控制和状态寄存器(Interrupt Control and State Register,ICSR)提供:

(1)不可屏蔽中断(Non-Maskable Interrupt,NMI)异常的设置挂起位;

(2)为PendSV和SysTick异常设置挂起和清除挂起位。

此外,它还给出正在挂起的最高优先级异常的异常号,该寄存器的位分配如图2.14所示。

图2.14 ICSR的位分配

(1)[31](NMIPENDSET):表示NMI设置挂起位。当给该位写1时,将NMI异常修改为挂起;当读取该位时,0表示没有挂起NMI异常,1表示正在挂起NMI异常。

由于NMI是优先级最高的异常,因此通常处理器一旦检测到对该位写入1,便立即进入NMI异常句柄。当进入句柄时,将该位清零。

这意味着只有在处理器执行该句柄重新使NMI信号有效时,NMI异常句柄对该位的读取才返回1。

(2)[30:29]:保留;

(3)[28](PENDSVSET):设置PENDSVSET挂起位。当该位设置为1时,将PendSV异常修改为挂起。读取该位时,0表示没有挂起PendSV异常,1表示正在挂起PendSV异常。对该位写1是使得PendSV异常挂起的唯一方法。

(4)[27](PENDSVCLR):清除PendSV挂起位。当该位设置为1时,从PendSV异常中删除挂起。

(5)[26](PENDSTSET):设置SysTick异常挂起位。当该位设置为1时,将SysTick异常修改为挂起。读取该位时,0表示没有挂起SysTick异常,1表示正在挂起SysTick异常。

(6)[25](PENDSTCLR):清除SysTick异常挂起位。当该位设置为1时,从SysTick异常中删除挂起。该位是只写位。在寄存器上读取它的值是未知。

(7)[24:18]:保留。

(8)[17:12](VECTPENDING):表示优先级最高的挂起的使能异常号。读取该位,返回0表示没有挂起的异常;非零表示优先级最高的挂起的使能异常号。

从该值减去16,即可获得CMSIS IRQ的编号,该编号表示中断清除使能、设置使能、清除挂起、设置挂起和优先级寄存器中相应的位。

(9)[11:0]:保留。

当写ICSR时,如果执行下面的操作,则结果是不可预知的。

(1)给PENDSVSET写1,并且给PENDSVCLR位写1。

(2)给PENDSTSET写1,并且给PENDSTCLR位写1。

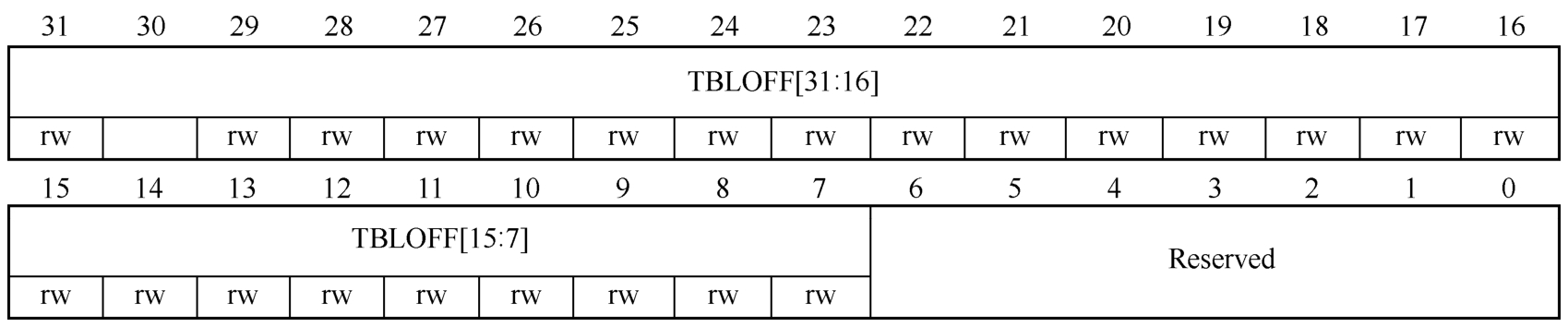

3.向量表偏移寄存器

向量表偏移寄存器(Vector Table Offset Register,VTOR)表示向量表基地址与存储器地址0x00000000的偏移量,该寄存器的位分配如图2.15所示。

图2.15 VTOR的位分配

(1)[31:7](TBLOFF):表示向量表的基本偏移字段。它包含表的基地址与存储器映射底部偏移量的位[31:7]。

(2)[6:0]:保留。

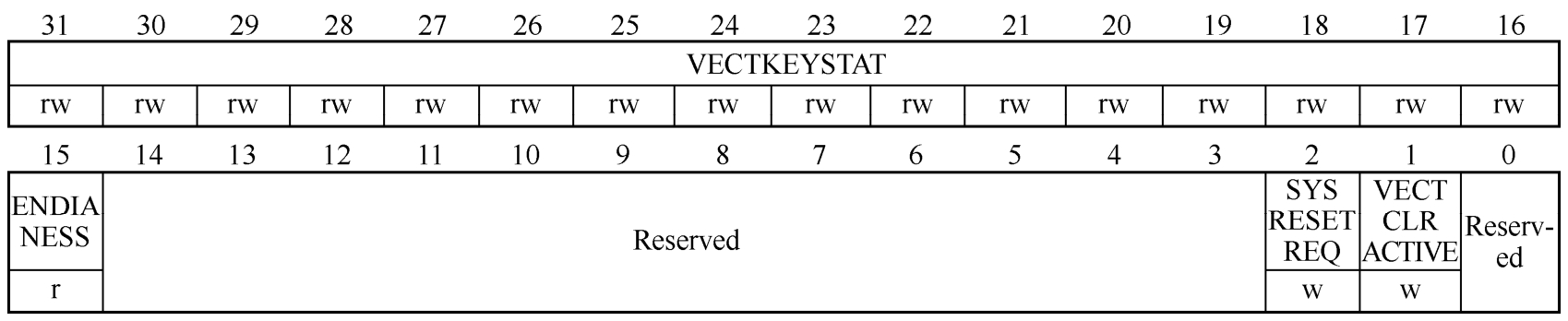

4.应用中断和复位控制寄存器

应用中断和复位控制寄存器(Application Interrupt and Reset Control Register,AIRCR)为数据访问和系统的复位控制提供端状态。要写入该寄存器,必须将0x05FA写入VECTKEY字段,否则处理器将忽略该写入操作。该寄存器的位分配如图2.16所示。

图2.16 AIRCR的位分配

(1)[31:16](VECTKEYSTAT):VECTKEY注册键,为注册密钥。当读取时,未知;当写入时,将0x05FA写入VECTKEY字段,负责忽略写操作。

(2)[15](ENDIANESS):数据端比特。当读取该位时,返回值为0,表示小端模式。

(3)[14:3]:保留。

(4)[2](SYSRESETREQ):系统复位请求。当给该位设置为1时,请求一个系统级复位。当读取该位时,返回值为0。

(5)[1](VECTCLRACTIVE):保留用于调试。当读取该位时,返回值为0。当写入该位时,必须向该位写0,否则行为不可预测。

(6)[0]:保留。

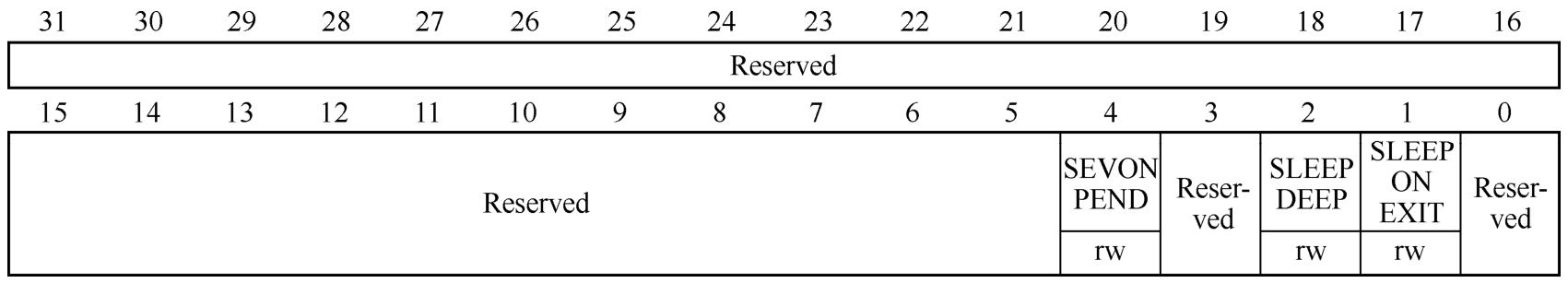

5.系统控制寄存器

系统控制寄存器(System Control Register,SCR)控制进入和退出低功耗的功能。SCR的位分配如图2.17所示。

图2.17 SCR的位分配

(1)[31:5]:保留。

(2)[4](SEVONPEND):表示在挂起位上发送事件。当该位为0时,只有允许的中断或事件才能唤醒处理器,禁止的中断将被排除在外;当该位为1时,使能的事件和所有中断(包括禁止的中断)都可以唤醒处理器。

当挂起一个事件或中断时,事件信号将处理器从WFE唤醒。如果处理器不等待一个事件,则寄存该事件并影响下一个WFE。

在执行SEV指令或一个外部事件时,也会唤醒处理器。

(3)[3]:该位必须保持清零。

(4)[2](SLEEPDEEP):控制处理器在低功耗模式时使用休眠或深度休眠。当该位为0时,使用休眠;当该位为1时,使用深度休眠。

(5)[1](SLEEPONEXIT):当从句柄模式返回到线程模式时,表示退出时休眠。将该位设置为1时,可使中断驱动的应用程序避免返回到空的主应用程序。当该位为0时,返回线程时不休眠;当该位为1,并且从中断服务程序(Interrupt Service Routine,ISR)返回线程模式时,进入休眠或深度休眠。

(6)[0]:保留,必须保持清除状态。

6.配置和控制寄存器

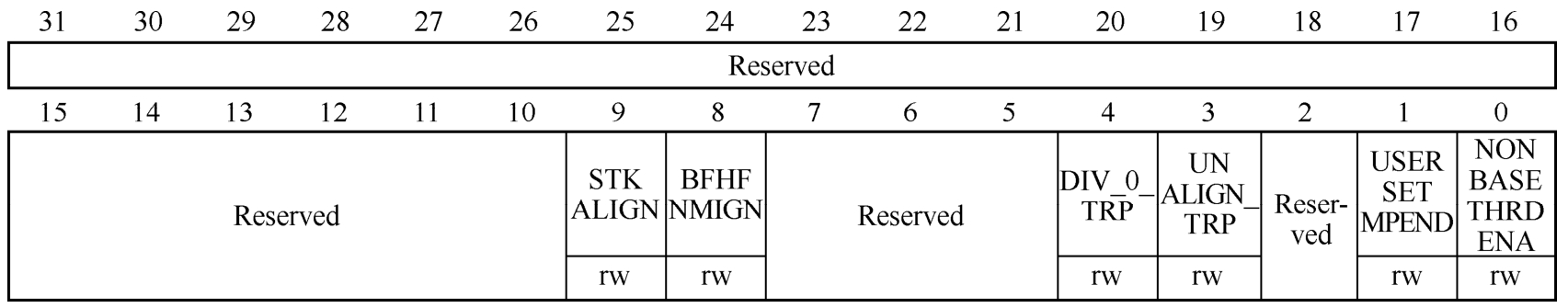

配置和控制寄存器(Configuration and Control Register,CCR)是只读存储器,它指示Cortex-M0+处理器行为的某些方面。CCR的位分配如图2.18所示。

图2.18 CCR的位分配

(1)[31:10]:保留,必须保持清除状态。

(2)[9](STKALIGN):始终读为1,表示在异常入口上8个字节堆栈对齐。在异常入口处,处理器使用入栈PSR的第[9]位指示堆栈对齐。从异常返回时,它使用这个堆栈位恢复正确的堆栈对齐方式。

(3)[8:4]:保留,必须保持清除状态。

(4)[3](UNALIGN_TRP):总是读取为1,指示所有未对齐的访问将产生一个硬件故障。

(5)[2:0](Reserved):保留,必须保持未清除状态。

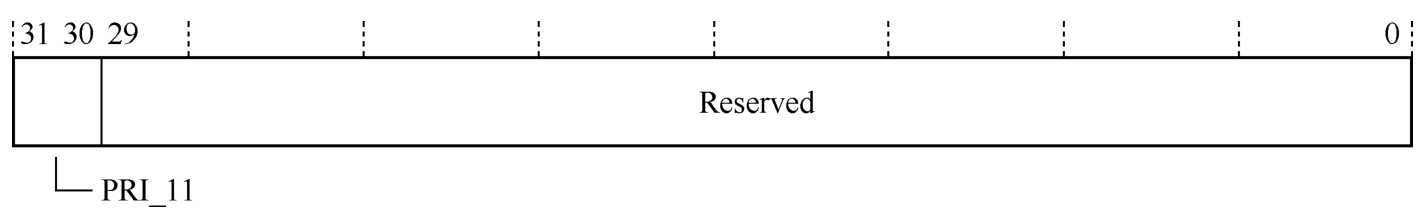

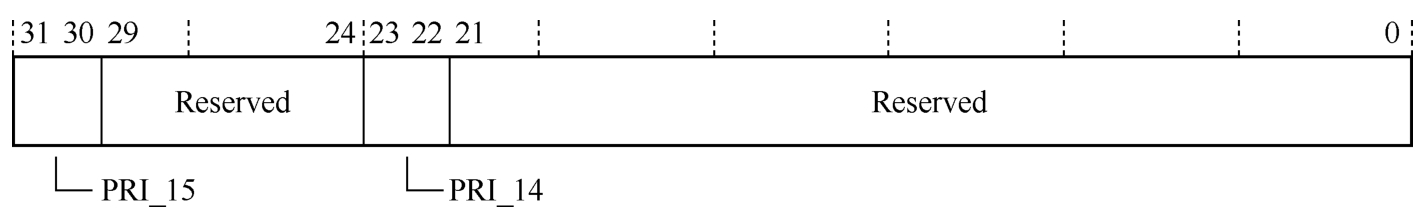

7.系统句柄优先级寄存器

系统句柄优先级寄存器(System Handler Priority Register,SHPR)2和3,将具有可配置优先级的系统异常句柄的优先级设置为0~192。SHPR2、SHPR3是字访问的。SHPR2的位分配如图2.19所示,SHPR3的位分配如图2.20所示。

图2.19 SHPR2的位分配

(1)[31:30](PRI_11):系统句柄11(SVCall)的优先级。

(2)[29:0]:保留,必须保持清除状态。

图2.20 SHPR3的位分配

(1)[31:30](PRI_15):系统句柄15(SysTick异常)的优先级(当没有实现SysTick定时器时,该字段为保留字段)。

(2)[23:22](PRI_14):系统句柄14(PendSV)的优先级。

当使用CMSIS访问系统异常优先级时,使用下面的CMSIS函数:

(1)uint32_t NVIC_GetPriority(IRQn_Type IRQn)

(2)void NVIC_SetPriority(IRQn_Type IRQn,uint32_t priority)

输入参数IRQn是IRQ的编号。