即计数的方法,我们把多位数码中每一位的构成方法以及从低位到高位的进位规则称为数制。

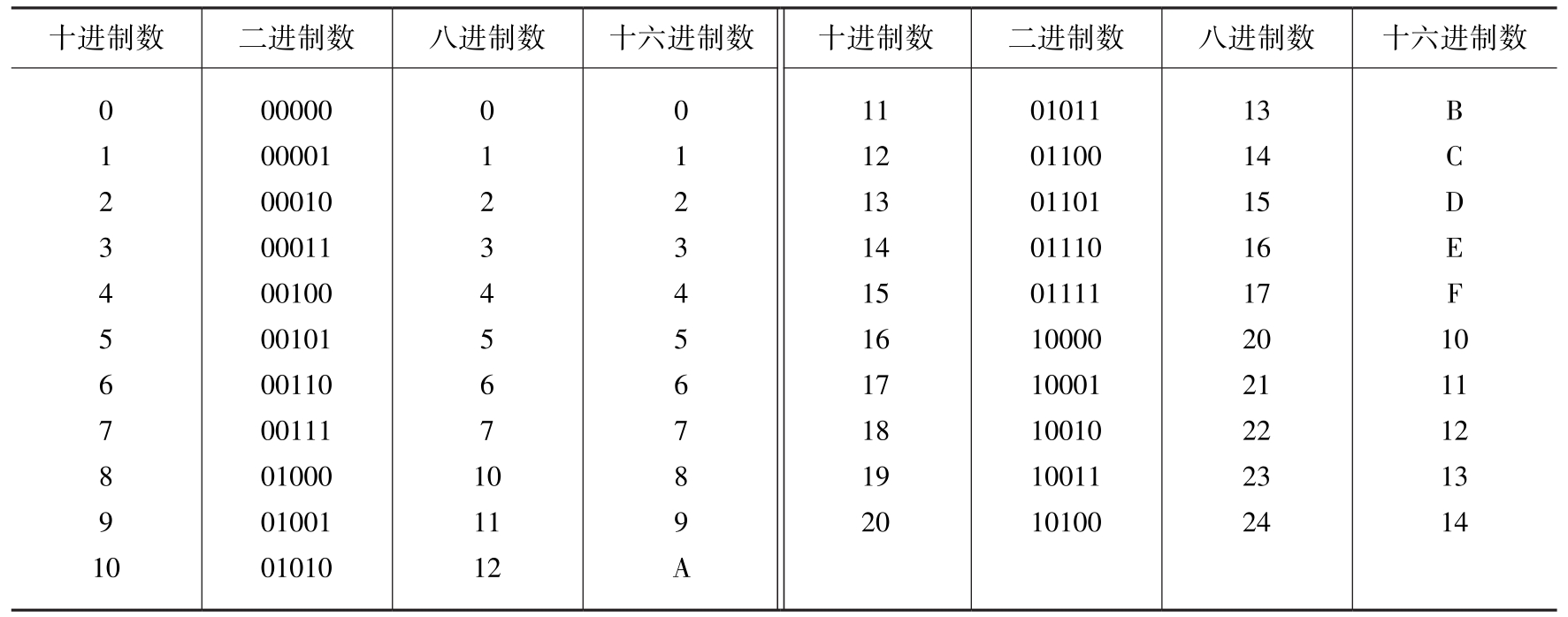

数字电路中常用的数制有二、八、十六进制。二进制只用0和1两个数码来表示数,基数是“二”,“逢二进一”。八进制有0、1、2、3、…、7八个数码,基数是“八”,“逢八进一”。十六进制有0、1、2、3、…、9,A、B、C、D、E、F十六个数码(A~F分别对应十进制中的10~15),基数是“十六”,“逢十六进一”。各种常用数制的对照见表4.6-1。

通常在十进制、二进制、八进制、十六进制后分别标记英文字母D、B、O、H加以区分。例如(16) D 、(16) O 、(16) H 分别表示十进制16、八进制数16、十六进制数16。不同制式之间可以相互转换。例如二进制数(11010) B 转换为十进制等于

(11010) B =1×2 4 +1×2 3 +0+1×2 1 +0=(26) D

表4.6-1 几种数制的对照

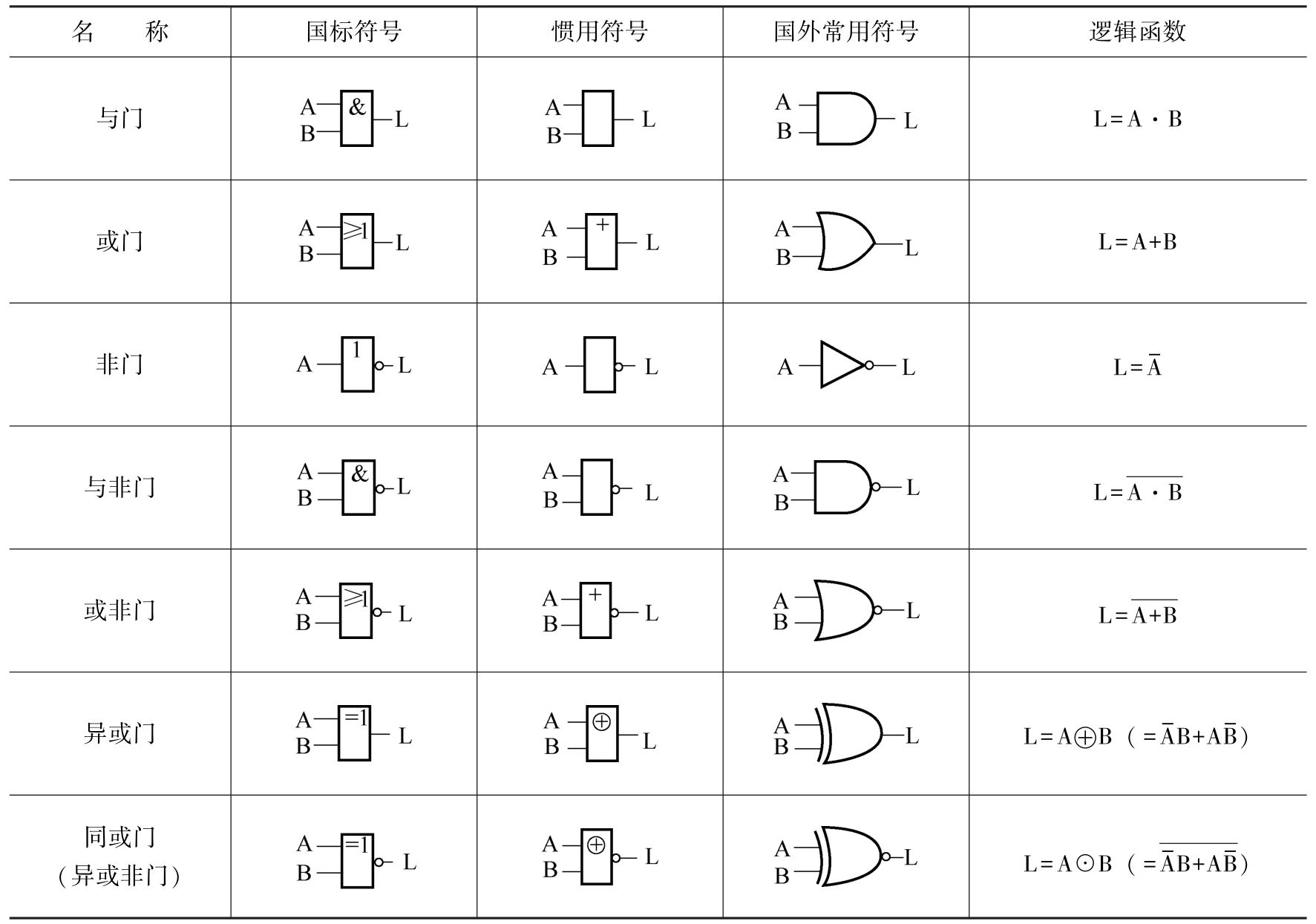

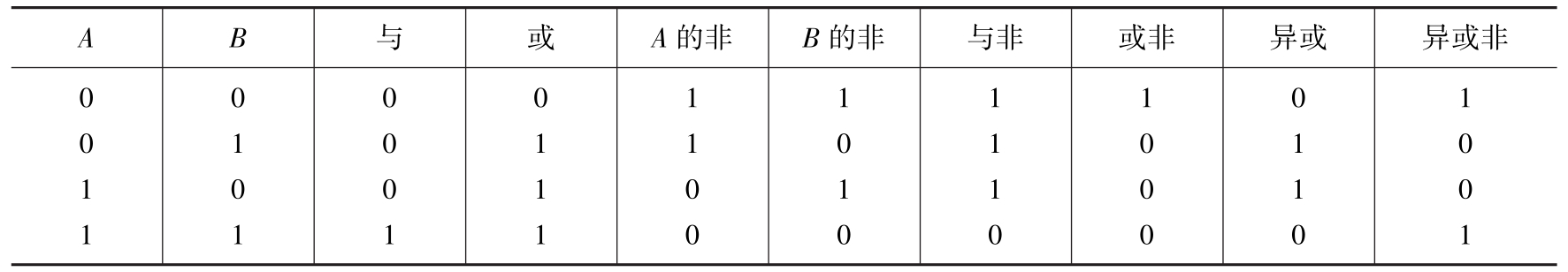

数字电路中的信息具有二值性,即只有两个可能的取值“0”或“1”,它们不表示数量的大小,而是表示完全对立的两个状态。由取值“0”或“1”的逻辑变量 A 和 B 构成的基本逻辑运算主要有:“与”(AND)、“或”(OR)和“非”(NOT);常用的还有:“与非”(NAND)、“或非”(NOR)、“异或”(Exclusive OR)和“异或非”(Exclusive NOR,也称“同或”)等。

实现上述逻辑运算的电路叫逻辑门,常用逻辑门的符号及逻辑函数如表4.6-2,运算关系见表4.6-3。

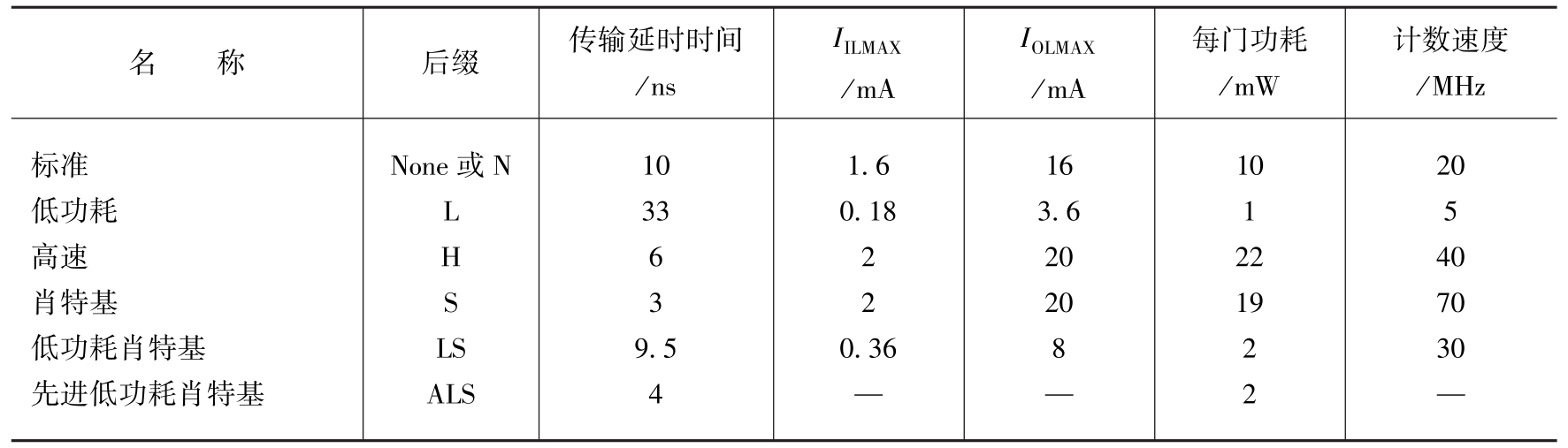

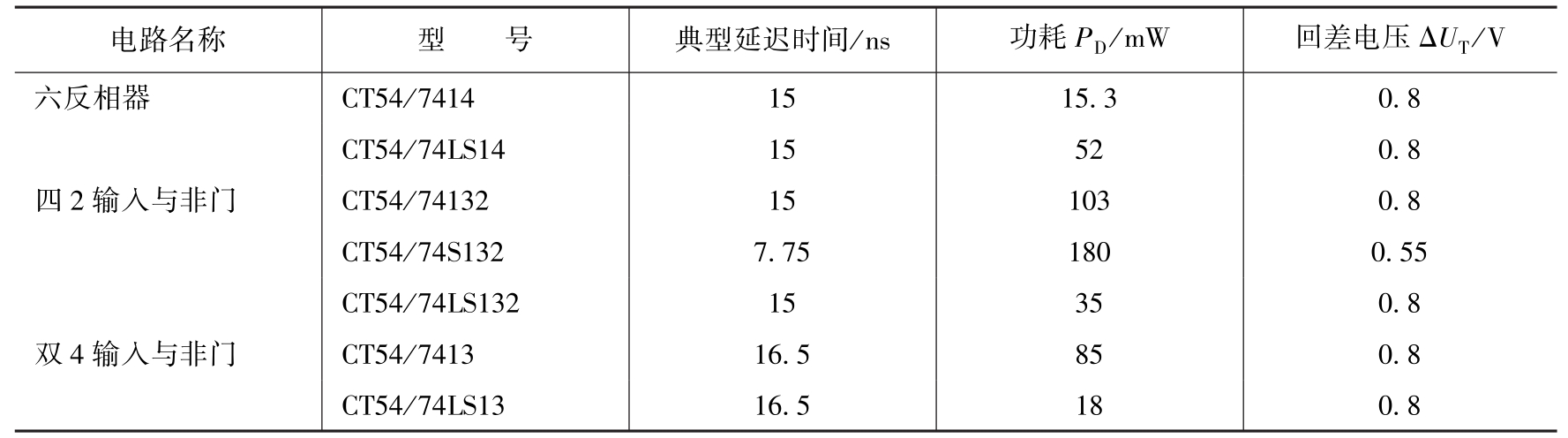

六种晶体管-晶体管逻辑(TTL)系列门的主要性能比较见表4.6-4,例如,74LS00为低功耗肖特基四二输入与非门,其中LS为后辍。其他以此类推,但后缀N可不写。CT为国标,与国际通用的74系列完全相同。国标CT又分为CT1000(74××),CT2000(74H××),CT3000(74S××),CT4000(74LS××)。

在数字系统中,各种信息都表现为一系列的高、低电平信号。若将高电平(H)规定为逻辑“1”,低电平(L)规定为逻辑“0”,则为正逻辑;反之若将高电平规定为逻辑“0”,低电平规定为逻辑“1”,则为负逻辑。在同一系统中,只能采用一种逻辑体制,数字电路一般都采用正逻辑。

表4.6-2 常用逻辑门符号及逻辑函数

表4.6-3 常用逻辑运算关系

表4.6-4 六种TTL系列门的主要性能比较

又称布尔代数,是分析数字系统的重要数学工具,它构成了数字系统的设计基础。在逻辑代数中的变量(即逻辑变量)的取值只有两种可能性:即“真(true)和假(false)”。常把“真”简记作“1”,表示条件成立、事情发生;把“假”简记作“0”,表示条件不成立,事情不发生。

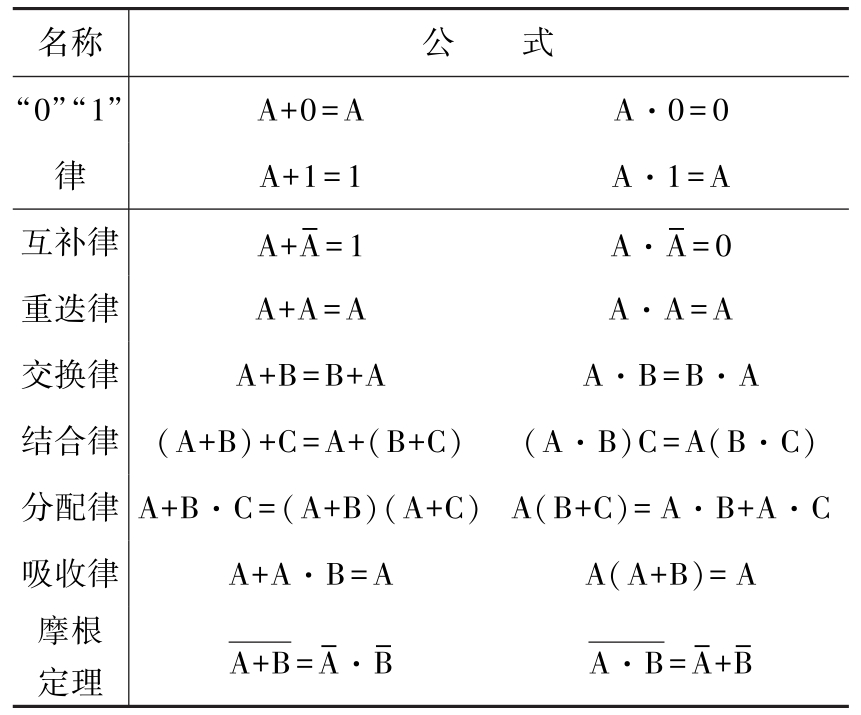

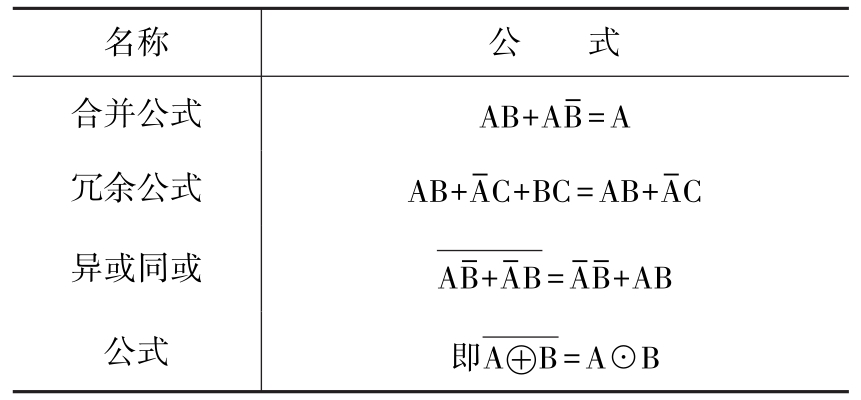

逻辑代数中最常用的基本逻辑运算是“与”运算、“或”运算和“非”运算。常用的定理和定律如表4.6-5,几个常用公式见表4.6-6。

表4.6-5 逻辑代数常用定理和定律

表4.6-6 几个常用公式

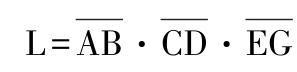

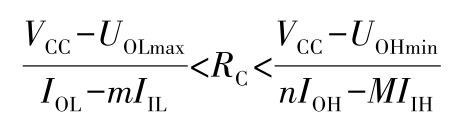

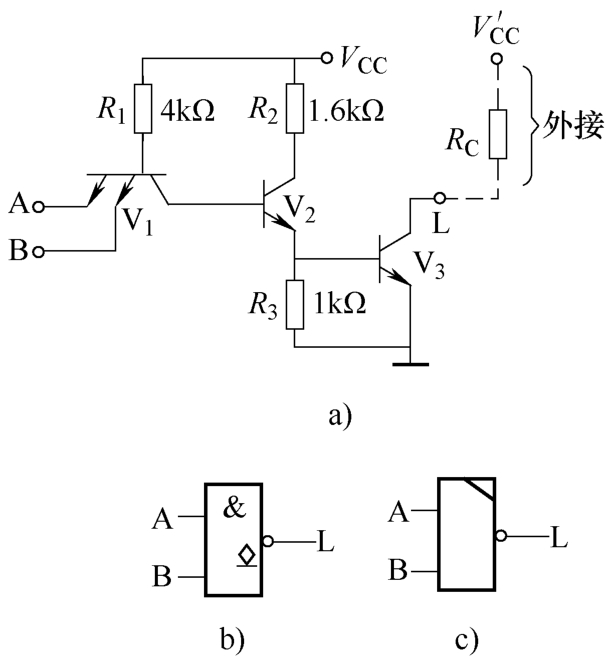

工程上对门的功能、工作速度、抗干扰能力等要求有所不同,所以除了标准型TTL门系列外,还有许多其他类型的集成逻辑门,例如:TTL集电极开路逻辑门(OC门)是一种能够实现门输出逻辑上“线与”连接的集成门,电路结构与逻辑符号见图4.6-1,由图可见OC与非门采用集电极开路的晶体管作输出级。必须强调指出,OC门只有在外接负载电阻

R

C

和电源

V

CC

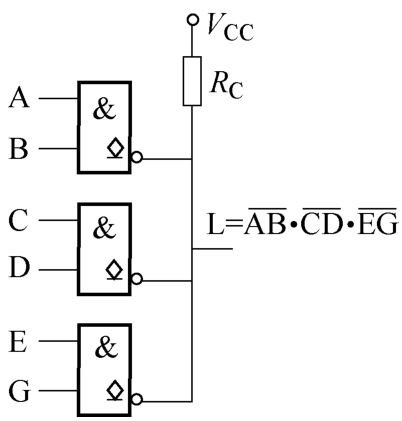

相连后才能正常工作。几个OC门输出线与见图4.6-2,

。

。

如果有 n 个OC门线与,每个门输出管的截止漏电流为 I OH ,最大灌入电流为 I OL ;若带 m 个同类门,这些负载的输入端总数为 M ,每个负载门的低电平输入电流为 I IL ,高电平输入电流为 I IH ,此时外接电阻 R C 按下式选取:

图4.6-1 集电极开路与非门

a)电路结构 b)国标逻辑符号 c)惯用逻辑符号

图4.6-2 用OC门进行线与

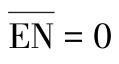

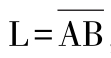

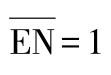

TTL三态逻辑门(TSL)是用于数字控制系统和微型计算机总线结构的器件,它的特点是输出有三种状态,除通常的逻辑0和逻辑1外,还有第三种状态,即高阻状态。如三态TTL与非门,电路见图4.6-3,当控制端

时,与普通的TTL与非门一样,实现

时,与普通的TTL与非门一样,实现

,当

,当

时,输出呈高阻抗。

时,输出呈高阻抗。

另外还有高阈值逻辑门(HTL门)和发射极耦合逻辑门(ECL门)等双极型集成门及CMOS门。HTL门的特点是抗干扰能力比TTL集成与非门高得多,缺点是速度较低,功耗较大。ECL门的特点是带负载能力强,具有极高的工作速度,缺点是抗干扰能力差,功耗大。CMOS集成逻辑电路是一种互补对称MOS场效应管集成电路,它的特点是静态功耗低,电源电压范围宽,抗干扰能力强,扇出系数(即最多能带同类门的个数)大。

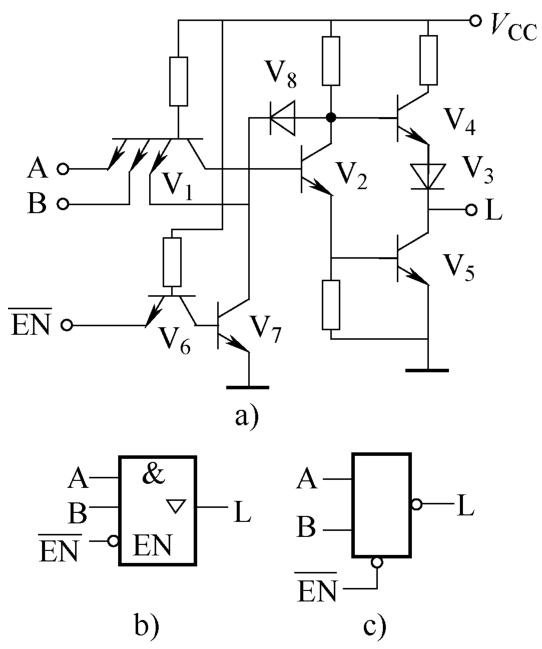

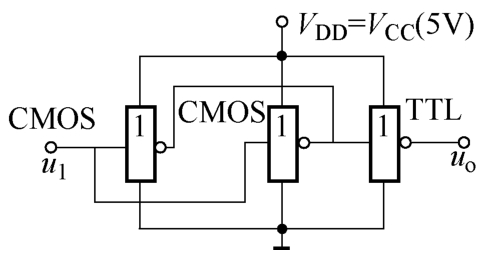

TTL电路驱动CMOS电路,当两者电源电压均为5V时,为了保证TTL电路能正常工作,可靠地驱动CMOS电路,必须在TTL电路输出和电源之间加一上拉电阻,电阻取值在3.3~4.7kΩ之间,见图4.6-4,若TTL电路驱动高速型HCMOS器件不需要外接上拉电阻,可直接连接。

图4.6-3 TTL三态与非门

a)电路结构 b)国标逻辑符号 c)惯用逻辑符号

图4.6-4 TTL驱动CMOS

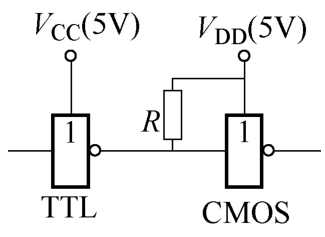

TTL驱动CMOS电路,若两者使用电源电压不同,解决办法之一是将TTL电路改为输出端耐压较高的OC门或增加一级OC门。将外接上拉电阻 R C (取值10kΩ)接到CMOS电路的电源 V DD ,电路见图4.6-5。

图4.6-5 使用OC门做TTL到CMOS的接口

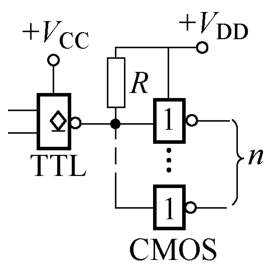

CMOS电路驱动TTL电路,两者电源电压为5V时,CMOS门电路、触发器直接带TTL电路负载能力很差,只能带1~2个TTL LS系列门。可在CMOS与TTL电路之间加一级晶体管反相器或CMOS缓冲器,以加大CMOS带负载的能力。若两者使用的电源电压不同,常用的方法是将同一芯片内的CMOS门电路并联使用,降低电源电压至5V,同时提高吸收电流能力,电路见图4.6-6。另外也可在CMOS和TTL电路之间增加一级CMOS驱动器,还可以用分立器件的电流放大器实现电流扩展。

图4.6-6 用多个CMOS门并联驱动TTL门的电路

是数字逻辑电路的两大类型,组合逻辑电路的输出状态只取决于该时刻各输入状态的组合,而与此时刻之前电路的原状态无关,从电路结构上看,组合逻辑电路由逻辑门组成,电路中没有记忆元件,输出与输入之间没有反馈连线。时序逻辑电路的任一时刻输出值不仅取决于当前的输入信号,而且还与电路原来的状态有关,即与以前的输入信号有关,在电路结构上,时序逻辑电路通常包括组合逻辑电路和具有记忆功能的存储单元电路,组合逻辑电路输出的一部分通过存储电路反馈到组合逻辑电路的输入端,与输入信号一起决定组合逻辑电路的输出。典型的组合逻辑电路有半加器、全加器、译码器、编码器、多路选择器、码制转换电路、奇偶校验电路和数值比较器等。典型的时序逻辑电路有触发器、寄存器、移位寄存器、计数器和存储器等。

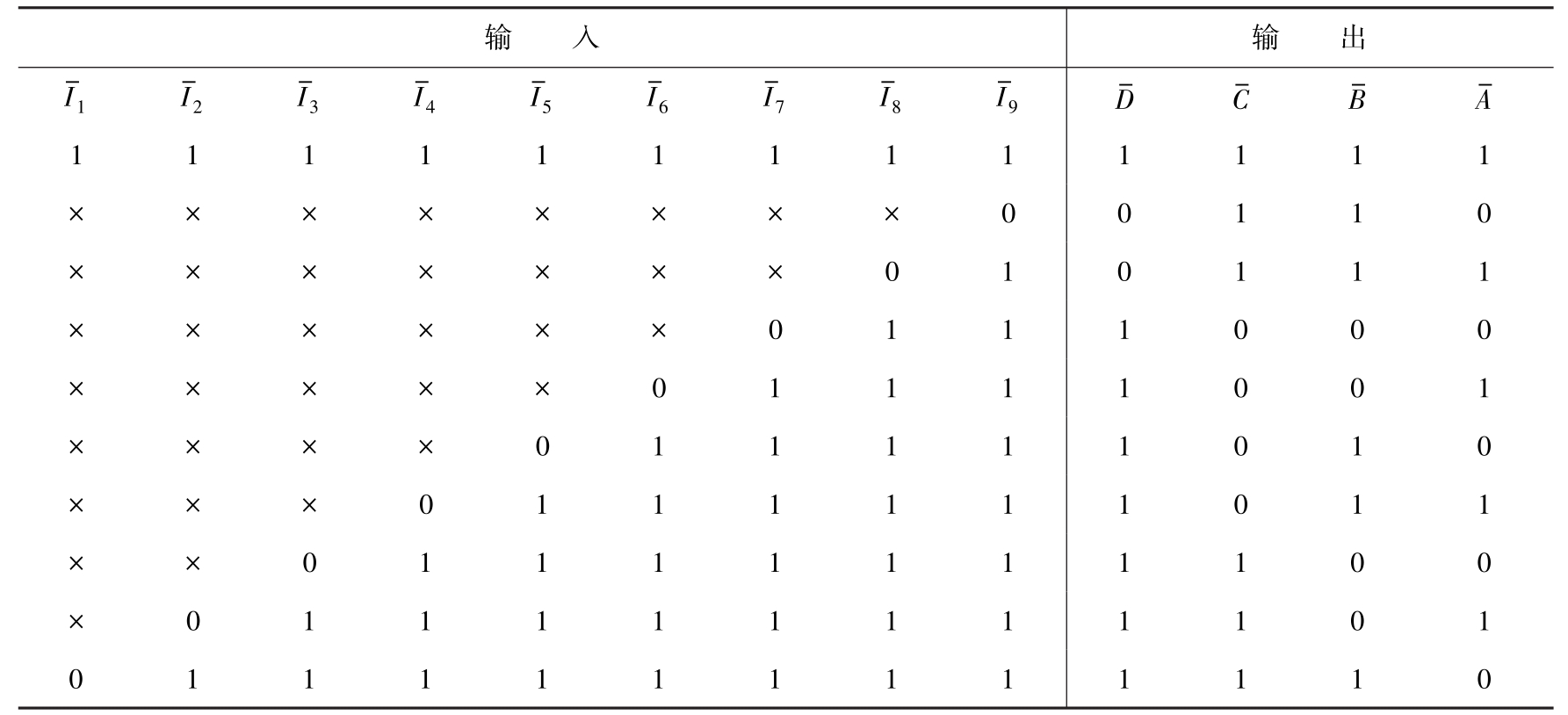

用二进制数0和1按一定规则组成的代码表示特定对象的过程叫做编码。具有编码功能的逻辑电路叫做编码器。常用的编码器有74LS147(8421BCD码)编码器,又称十线—四线优先编码器。即在设计时就安排好了输入信号的优先顺序,因此当有

n

个被编对象同时输入时,只对优先权最高的一个进行编码。其功能见表4.6-7。从表中可以看出74LS147输入是十路(

隐含其中)被编对象,优先权以

隐含其中)被编对象,优先权以

为最高,

为最高,

为最低。输入输出均为低电平有效输出是反码形式的8421BCD码,74LS147的逻辑图和符号见图4.6-7。此外,还有74LS148(八线-三线优先编码器)仍为输入输出低电平有效,CMOS的CD4532(八线-三线优先编码器)为输入输出高电平有效。

为最低。输入输出均为低电平有效输出是反码形式的8421BCD码,74LS147的逻辑图和符号见图4.6-7。此外,还有74LS148(八线-三线优先编码器)仍为输入输出低电平有效,CMOS的CD4532(八线-三线优先编码器)为输入输出高电平有效。

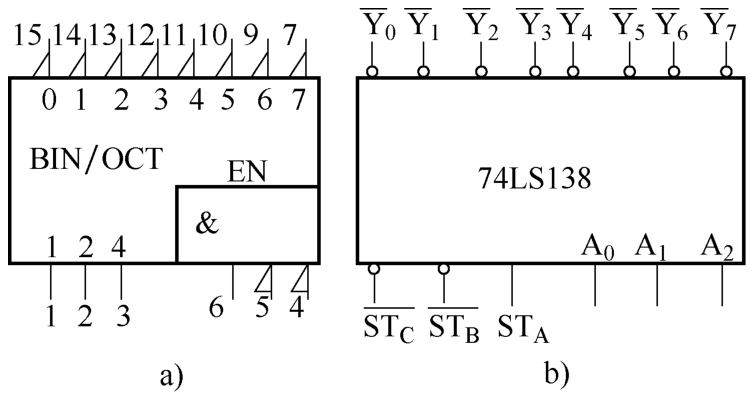

表4.6-7 74LS147功能表

图4.6-7 BCD输出的10线—4线优先编码器74147

a)国标逻辑符号 b)惯用逻辑符号

又称解码器,是编码的逆过程,即把二进制代码的特定含义“翻译”出来,转变成对应的控制信号。译码器有两大类:通用译码器和显示译码器。

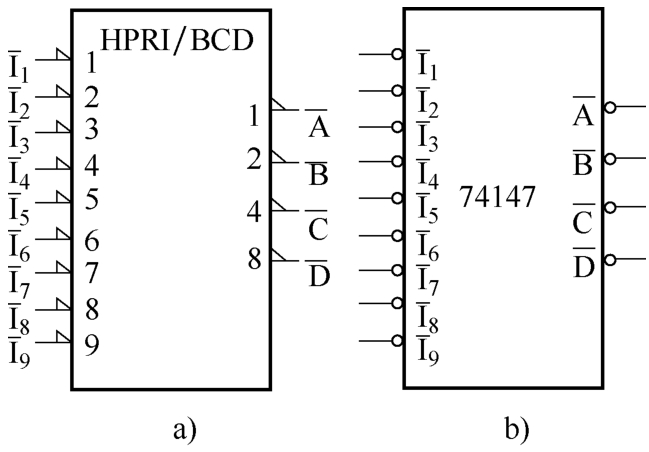

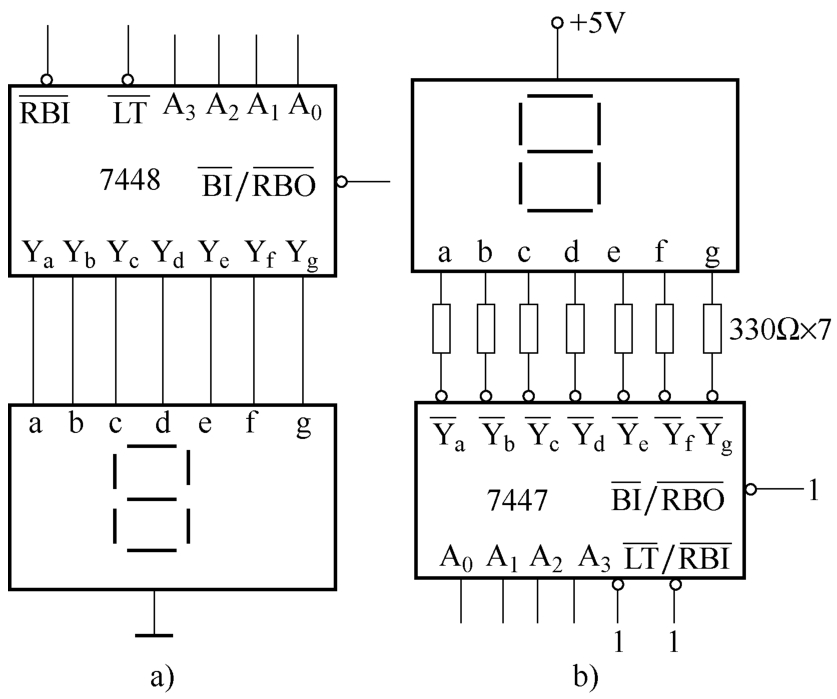

常用的中规模集成译码器有74LS138,它的逻辑符号和功能表分别见图4.6-8和表4.6-8。

图4.6-8 中规模集成译码器74LS138

a)国标逻辑符号 b)惯用逻辑符号

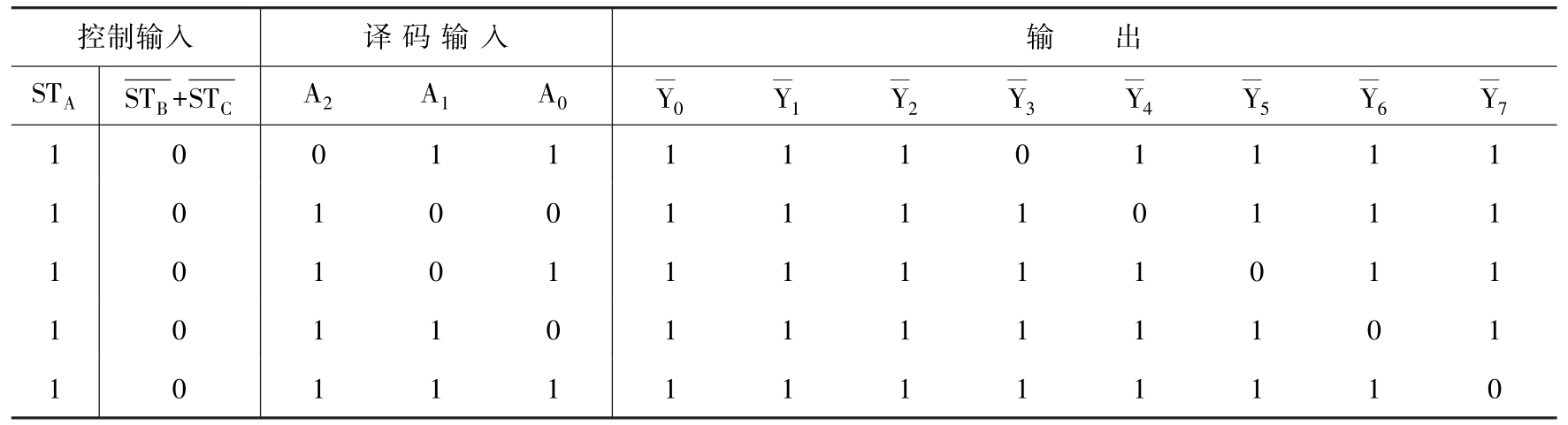

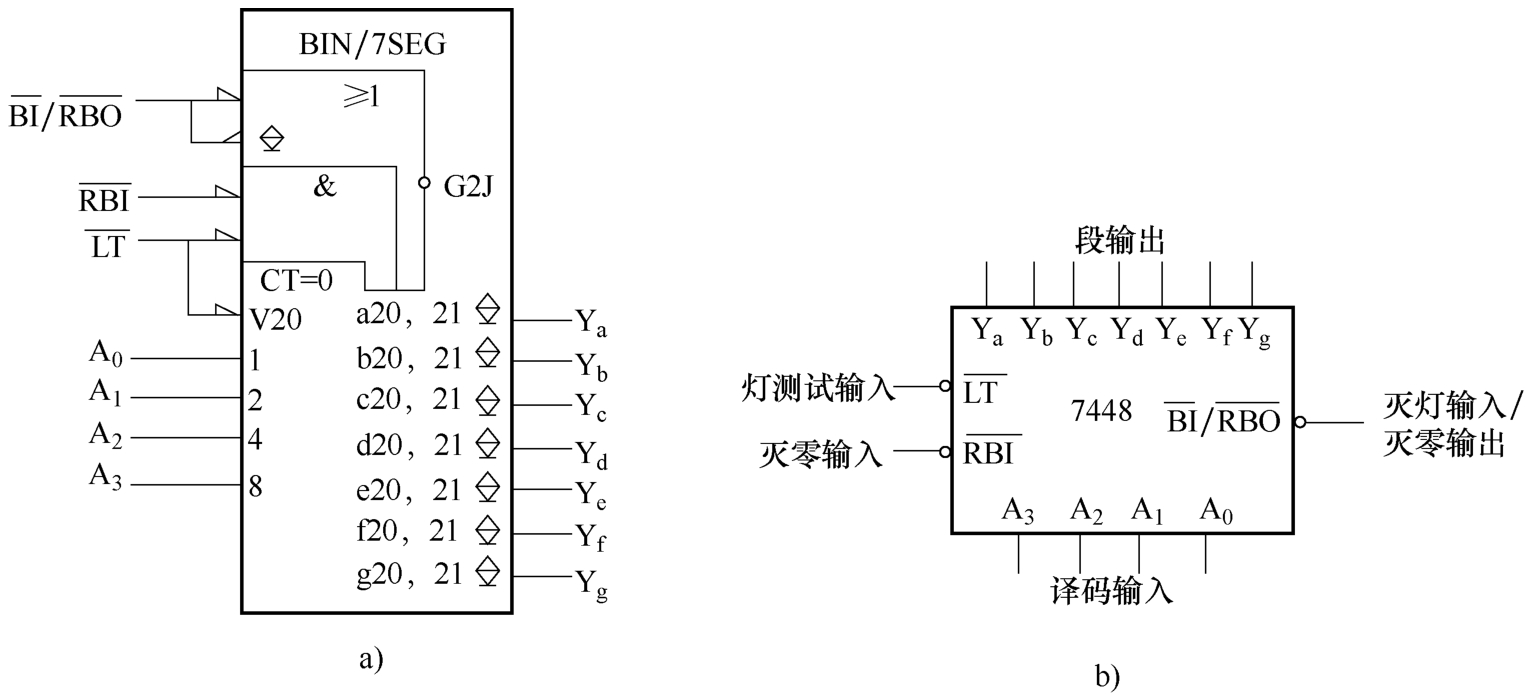

显示译码器又称字形译码器,常用的集成七段译码器TTL有7447、7448。CMOS有CD4055、CD4511等。7447为驱动共阳七段LED器件,7448或CD4511为驱动共阴七段LED器件,CD4055为驱动七段LCD器件。7448的符号见图4.6-9。显示译码器和数码管显示器连接图见图4.6-10,其中图4.6-10a为共阴极显示,图4.6-10b为共阳极显示。

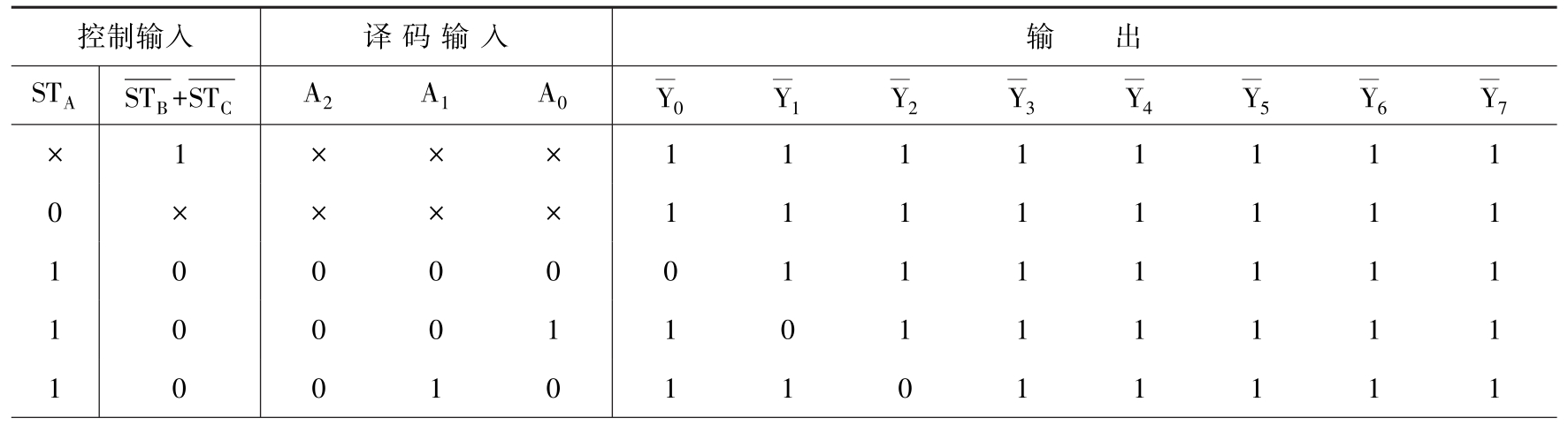

表4.6-8 74LS138功能表

(续)

图4.6-9 4线~7线译码器/驱动器7448

a)国标逻辑符号 b)惯用逻辑符号

图4.6-10 显示译码器和数码管显示器的连线图

a)共阴极显示 b)共阳极显示

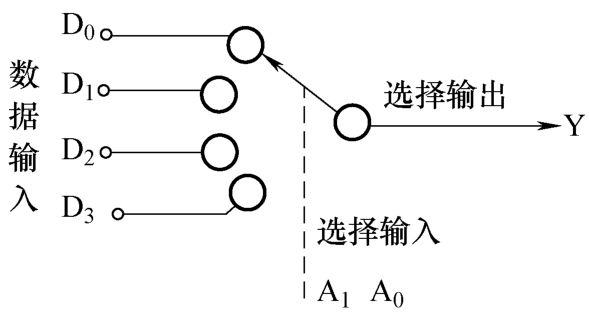

又称多路选择器,其作用类似单刀多掷开关。能按通道地址选择信号,从多个数据输入信号中选择一个,送往输出端。图4.6-11为四选一数据选择器示意图。

图4.6-11 数据选择器示意图

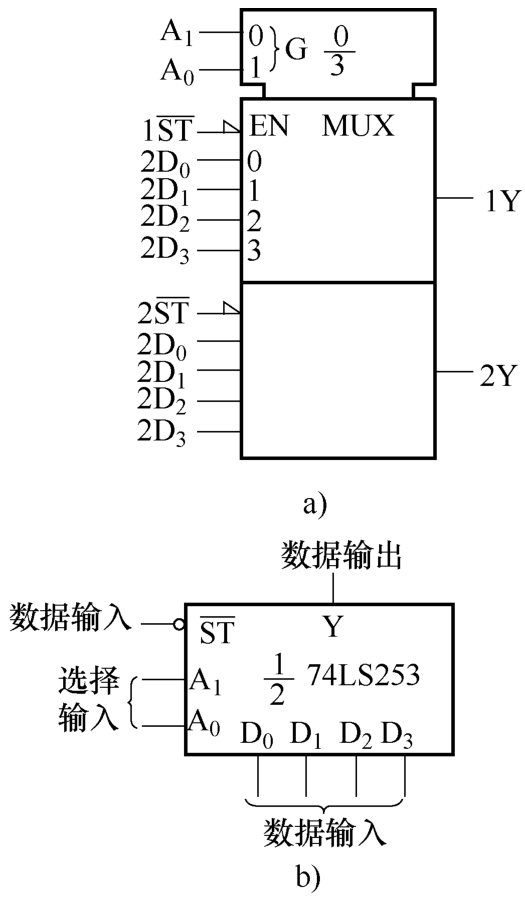

常用的集成数据选择器TTL有74153(双四选一),74151(八选一),74150(十六选一),74253(双四选一,三态输出),还有74353是双四选一三态反码输出。74LS253的逻辑符号见图4.6-12,它由两个完全相同的四选一数据选择器构成,A

1

A

0

为共用的选择输入或称地址输入,

和

和

分别为两个数据选择器的选通输入。74LS253的功能见表4.6-9,从中可以看出2位地址可选4路数据,依次类推3位地址可选8路数据,4位地址可选16路数据,…,

n

位地址可选2

n

路数据。

分别为两个数据选择器的选通输入。74LS253的功能见表4.6-9,从中可以看出2位地址可选4路数据,依次类推3位地址可选8路数据,4位地址可选16路数据,…,

n

位地址可选2

n

路数据。

图4.6-12 双四选一数据选择器74LS253

a)国标逻辑符号 b)惯用逻辑符号(半片)

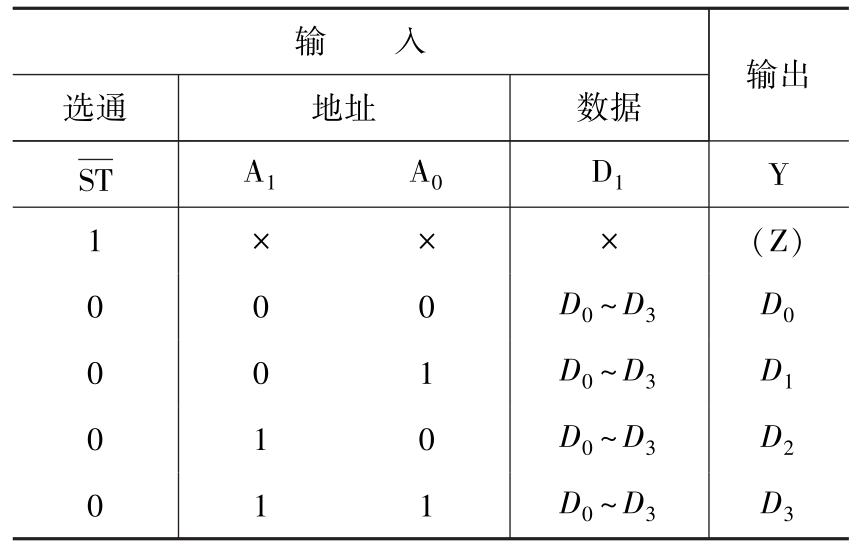

表4.6-9 74LS253功能表

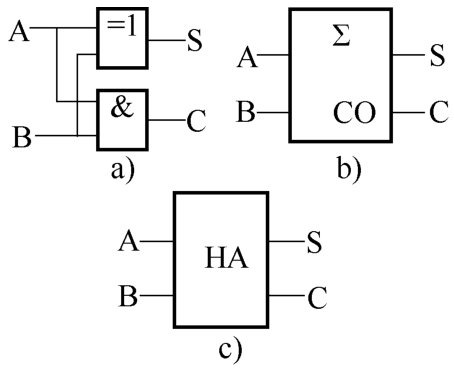

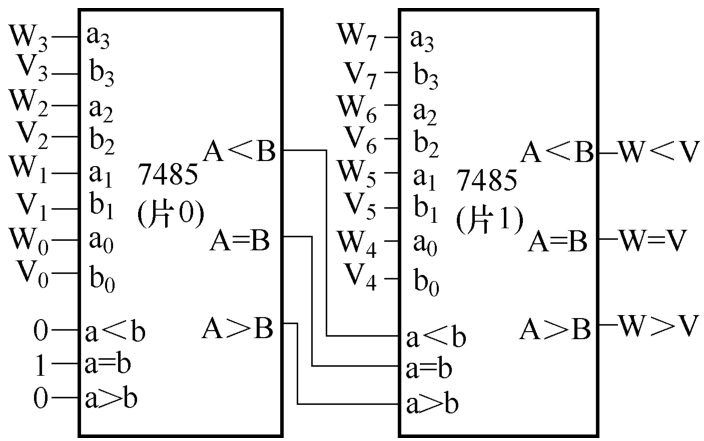

加法器可分为半加器和全加器。完成仅一位二进制数A、B本身相加功能的电路称半加器,见图4.6-13。A为被加数,B为加数,S表示半加器和,C表示本位进位输出。

图4.6-13 半加器

a)逻辑图 b)国标逻辑符号 c)惯用逻辑符号

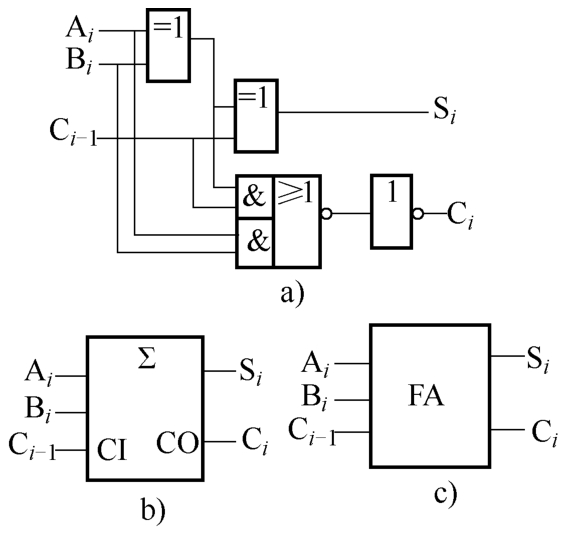

考虑了低位进位的一位加法器称为全加器,全加器的逻辑图和逻辑符号见图4.6-14,真值表见表4.6-10,其中C i -1 为来自低位的进位。输出S i 及进位C i 的逻辑表达式为

S i =A i ⊕B i ⊕C i -1 C i =(A i ⊕B i )C i -1 +A i B i

图4.6-14 全加器

a)逻辑图 b)国标逻辑符号 c)惯用逻辑符号

表4.6-10 全加器真值表

两个多位二进制数相加时,每一位都是进位相加,所以必须用全加器。中规模集成加法器7483是四位串行进位加法器,这种加法器结构简单,但运算速度慢;超前进位全加器,如74283、CC4008等,由于电路中采用超前进位技术,使加法器各级的进位信号不再是逐级传递,仅由加数和被加数决定,使其运算速度大大提高。

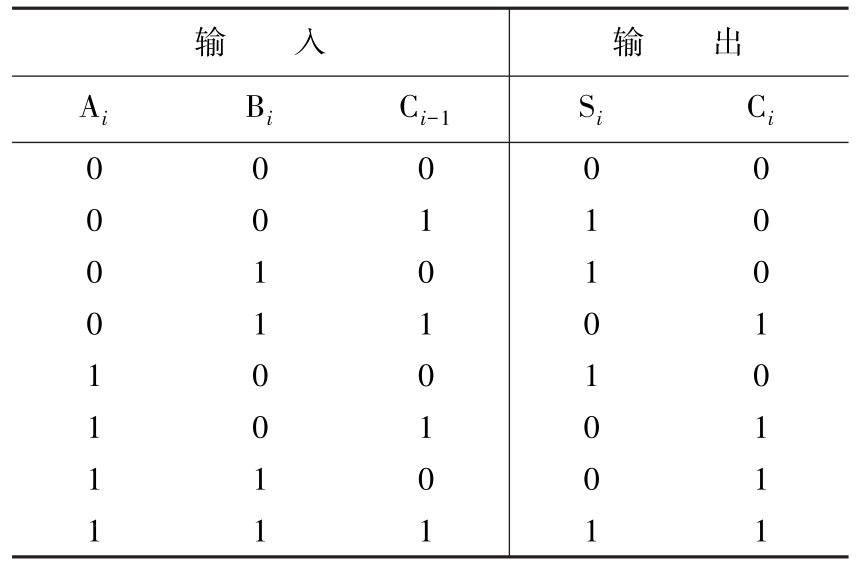

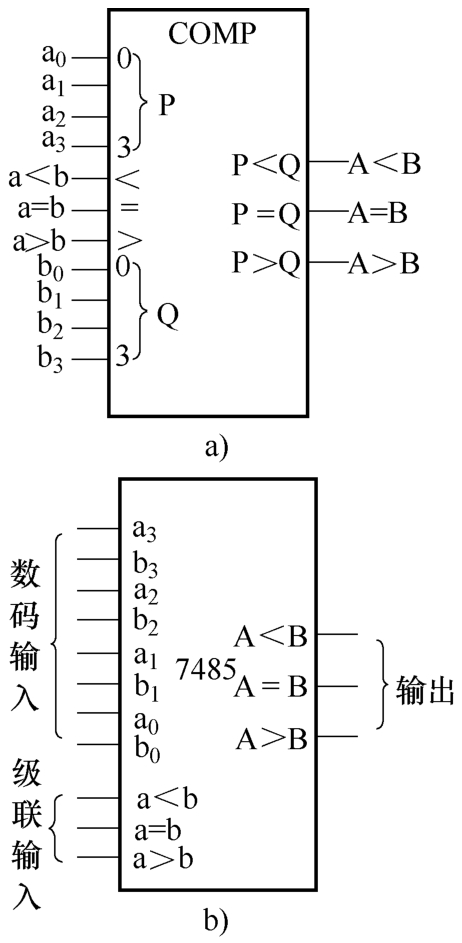

能判别两个数 A 、 B 大小的器件。图4.6-15是四位TTL型数码比较器7485的符号,它比较的两个四位二进制数 A 、 B 分别输入a 3 ~a 0 、b 3 ~b 0 八个输入端。它有三个输出端“A>B”、“A=B”和“A<B”。三个输出端总是只有一个为1,表示比较结果。例如:若 A < B ,则输出“A<B”为1,“A>B”和“A=B”均为0。

当要比较的数是八位时,就必须用两片7485串联使用,低位比较器的级联输入端,应使“a=b”端为“1”,“a<b”和“a>b”端为“0”,即告诉比较器,前级比较结果是 A = B 。用7485组成的两个八位二进制数比较电路见图4.6-16。

图4.6-15 四位数值比较器7485的逻辑符号

a)国标逻辑符号 b)惯用逻辑符号

图4.6-16 用7485实现两个八位二进制数的比较

若用CMOS型四位比较器CD4585组成串联比较电路与图4.6-16略有不同:1)最低位比较器级联输入端的=端、>端接1,<端接0;2)相邻低位片的输出A<B端和A=B端分别接到相邻高位片级联输入的<端和=端,高位片的>端接1。

触发器是一种能存储一位二进制信息的双稳态存储单元,它有两个基本性质:1)有两个能自行保持的稳定状态:1状态或0状态;2)在一定的外界信号作用下,从一个稳定状态翻转到另一个稳定状态。

触发器的种类很多,根据是否有时钟脉冲输入端可将其分为基本触发器和时钟触发器两大类。

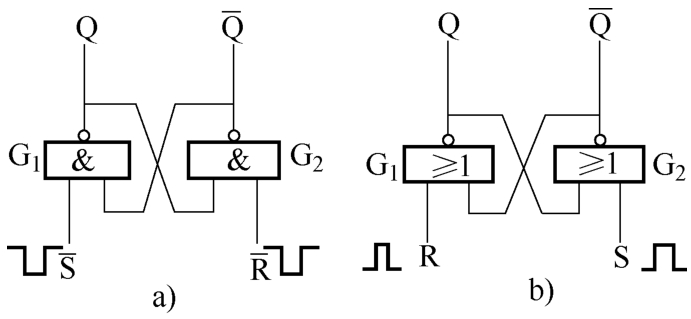

(1)基本触发器 由两个“与非”门或“或非”门交叉耦合构成,没有时钟脉冲输入端,见图4.6-17。无输入脉冲作用时,触发器保持原态,有脉冲输入置位端后,成为“1”状态;输入复位端后成为“0”状态;脉冲同时输入置、复位端后,新状态不定,因此这种情况应当避免。由“与非”门构成的基本触发器,输入脉冲应为负脉冲;而由“或非”门构成的则应为正脉冲。

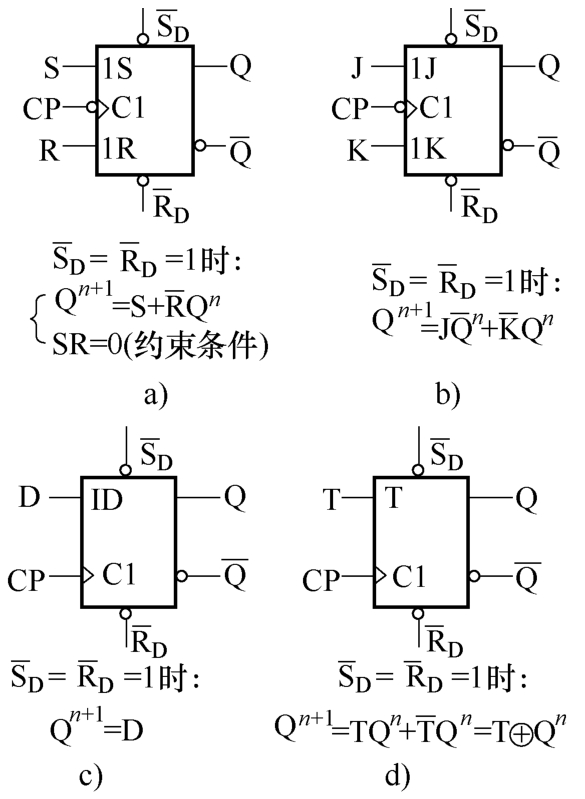

(2)时钟触发器 具有时钟脉冲输入端,按逻辑功能分为RS型,JK型、D型和T型四种,其中T型触发器实际上是JK触发器当 J = K (即J、K端连在一起)时的特例。由于集成电路种类很多,使用时必须了解各种时钟触发器的逻辑功能、结构形式及采用何种触发方式等。其逻辑符号和功能见图4.6-18。

图4.6-17 基本触发器

a)由“与非”门构成的触发器 b)由“或非”门构成的触发器

图4.6-18 时钟触发器的四种逻辑功能

a)RS触发器 b)JK触发器 c)D触发器 d)T触发器

按照触发方式又可分为:边沿触发、主从触发和电平触发。常见的集成块CT54/74S112、CT54/74LS112是下降沿触发的JK触发器,其中前者工作频率为125MHz,功耗150mW;后者工作频率45MHz,功耗20mW。常用的前沿触发D触发器有国产的T047、T077、T177和美国的74LS74,此类结构又称维持阻塞D触发器。CT54/7472与CT54/74H72为主从结构触发器,前者工作频率20MHz,功耗50mW;后者工作频率为30MHz功耗80mW。

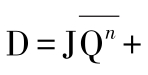

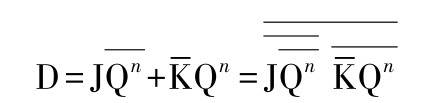

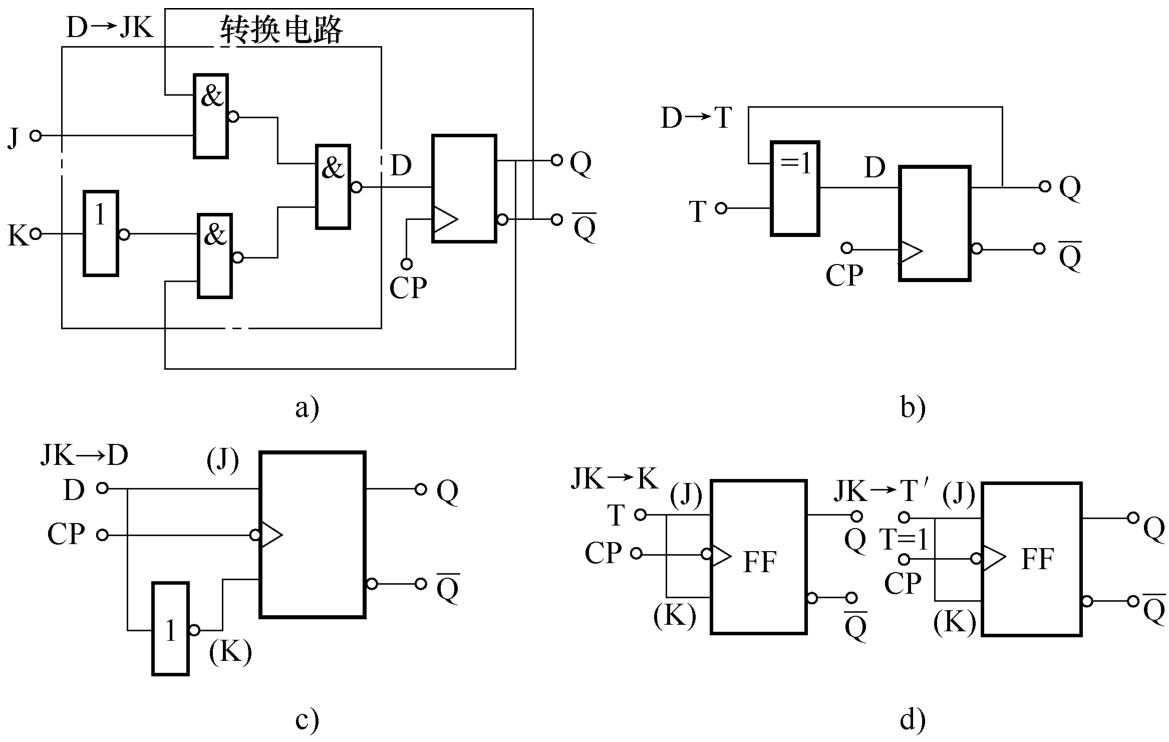

将已有触发器与能完成转换的组合逻辑电路联接,可以转换逻辑功能。比较图4.6-18中的D触发器和JK触发器的状态方程,可见用一个组合逻辑转换电路使

就能将D触发器转换为JK触发器,将此式用摩根定理简化为与非-与非逻辑式:

就能将D触发器转换为JK触发器,将此式用摩根定理简化为与非-与非逻辑式:

可得功能转换电路,如图4.6-19a所示。同理可将D触发器转换成T触发器,或者将JK触发器转换为D、T触发器,如图4.6-19b、c、d所示。

图4.6-19 触发器功能转换

a)D功能转换为JK功能 b)D功能转换为T功能 c)JK功能转换为D功能 d)JK功能转换为T功能

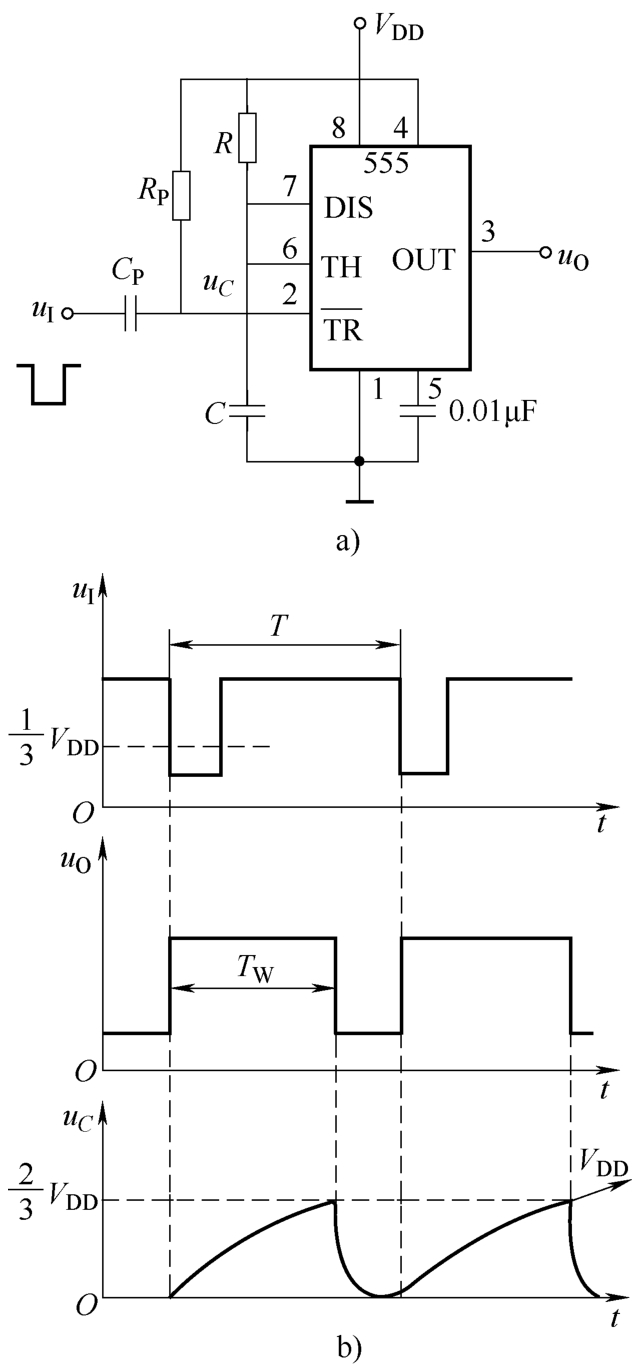

常在数字系统的整形、延时、定时电路中使用,它只有一个稳态,在触发脉冲作用下,电路从稳态经暂稳态后能自动返回稳态,电路处于暂稳态的时间等于单稳态触发器输出脉冲的宽度 T W 。常用的单稳态触发器有555定时器构成的单稳和集成单稳态触发器。

图4.6-20为CMOS集成电路CC7555构成的单稳态电路及工作波形。负触发脉冲由

端输入,

R

、

C

为外接定时元件。电路输出脉冲宽度,即暂稳态时间电路正常工作时,要求输入负脉冲宽度

T

W1

<

T

W

。若

T

W1

>

T

W

,则输入触发脉冲应先经微分电路后,再接到

端输入,

R

、

C

为外接定时元件。电路输出脉冲宽度,即暂稳态时间电路正常工作时,要求输入负脉冲宽度

T

W1

<

T

W

。若

T

W1

>

T

W

,则输入触发脉冲应先经微分电路后,再接到

端。

端。

T W = RC ln3≈1.1 RC

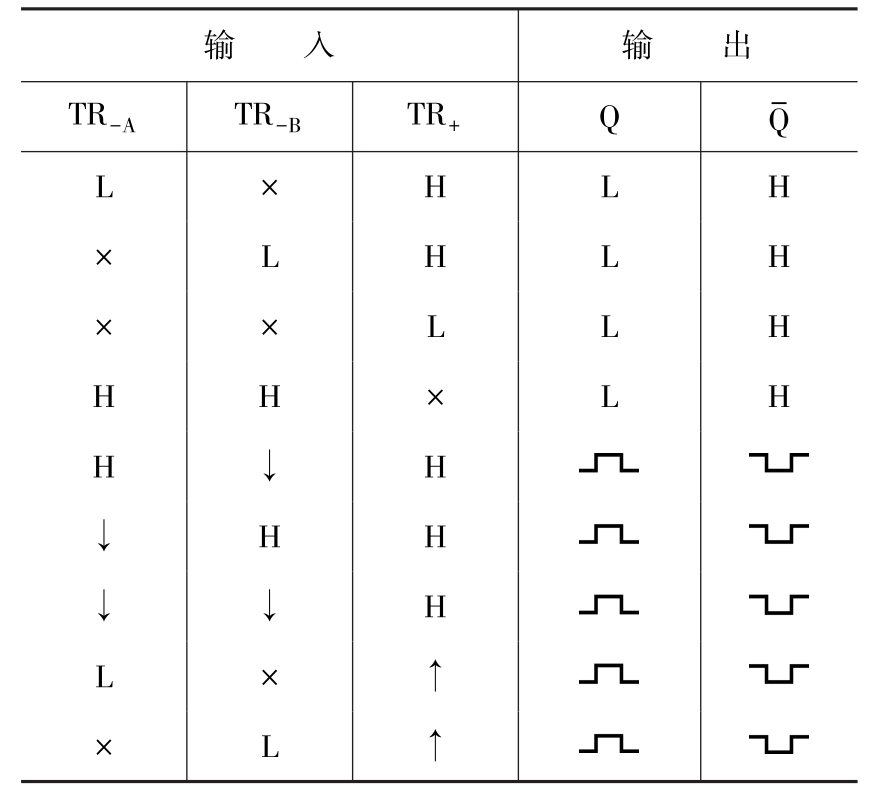

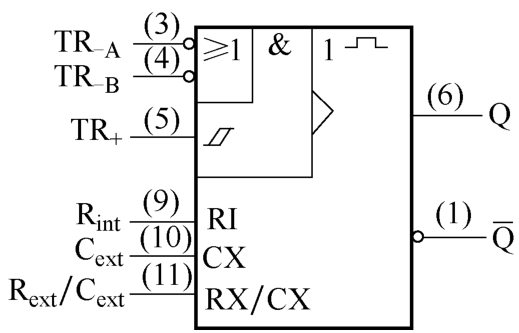

集成单稳态触发器分为不可重复触发与可重复触发两大类。74121是不可重复触发单稳集成电路,其符号及功能表见图4.6-21和表4.6-11。它采用施密特触发输入方式,具有较强的抗干扰能力,有三个触发输入端,两输出端。输出脉冲宽度也是暂稳态的持续时间取决于定时电阻 R 和定时电容 C 的取值,即

T W = RC ln2≈0.7 RC

表4.6-11 74121功能表

图4.6-20 定时器555构成的单稳态触发器

a)电路图 b)电路各点波形图

图4.6-21 单稳态触发器74121逻辑符号

定时电容接在CX和RX/CX端之间。定时电阻有两种接法:1)选用内定时电阻(2kΩ),此时只要将RI端接 V CC 即可;2)在RX/CX端与 V CC 间接外定时电阻(取值范围:1.4~40kΩ),这种方式还可改善脉宽的可重复性和精度。

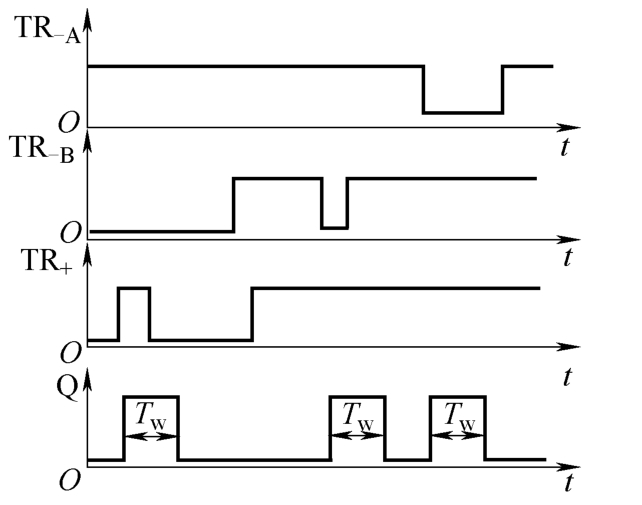

图4.6-22为在输入信号TR -A 、TR -B 、TR + 的作用下,74121单稳态触发器的工作波形图。

74122是可重复触发的单稳态触发器,它的输出脉冲宽度

T

W

可以由三种方式控制:1)通过选择外接定时元件电容和电阻的值来确定脉冲宽度;2)通过正触发输入端(TR

+A

、TR

+B

)和负触发输入端(TR

-A

、TR

-B

)的重触发,可延长暂稳态时间,即展宽单稳的输出脉冲;3)通过清除端

,可中止暂稳态,从而缩小输出脉冲宽度

T

W

。

,可中止暂稳态,从而缩小输出脉冲宽度

T

W

。

图4.6-22 74121工作波形图

常用作脉冲变换、整形和鉴幅,且具有很强的抗干扰能力。

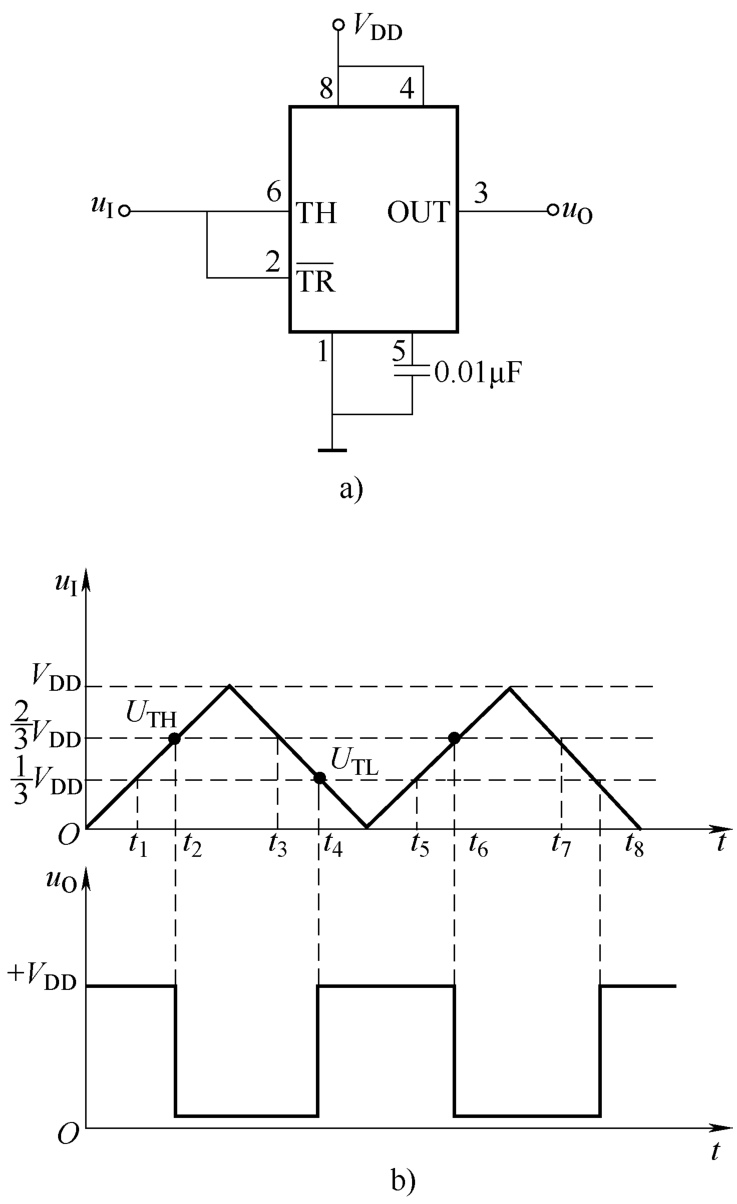

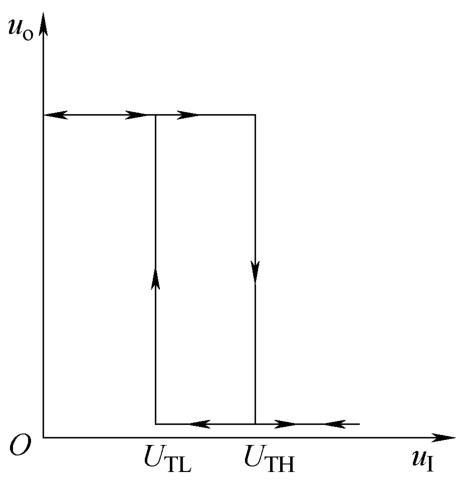

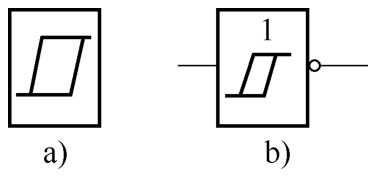

用CC7555构成的施密特触发器及工作波形如图4.6-23所示。 u i 上升和下降时,电路的触发电平分别为上限触发电平 U TH 和下限触发电平 U TL ,它们之差△ U T = U TH -U TL ,称回差电压。电路的传输特性见图4.6-24。图4.6-25为施密特触发器的定性图形符号及施密特反相器逻辑符号。

图4.6-23 定时器555构成的施密特触发器

a)电路图 b)当 u i 为三角波时输出 u o 的波形

图4.6-24 传输特性

图4.6-25 施密特触发器

a)定性图形符号

b)施密特反相器的逻辑符号

集成施密特触发器性能一致性好,触发阈值稳定,应用越来越广泛。TTL集成施密特触发器的主要类型及特性见表4.6-12。CMOS集成施密特触发器典型产品有:CC40106(六反相器)和CC4093(四2输入与非门)。

表4.6-12 集成施密特触发器主要类型及特性

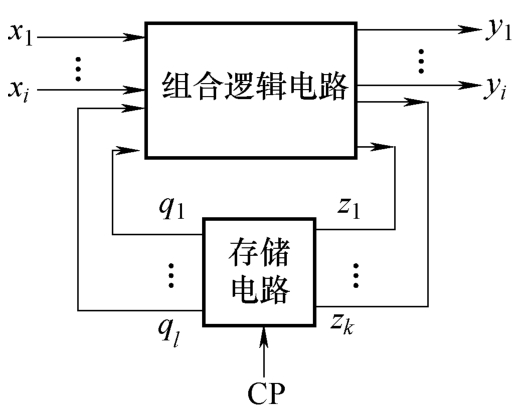

电路框图见图4.6-26,图中 X ( x 1 、 x 2 、…、 x i )代表输入信号, Y ( y 1 、 y 2 、…、 y i )代表输出信号。这些信号之间的逻辑关系可表示为

Y ( t n )= F [ X ( t n ), Q ( t n )]输出方程

Q ( t n +1 )= G [ Z ( t n ), Q ( t n )]状态方程

Z ( t n )= H [ X ( t n ), Q ( t n )]驱动方程

图4.6-26 时序逻辑电路方框图

时序逻辑电路可以分为“同步”和“异步”两大类。在同步时序电路中,有一个统一的时钟脉冲,所有触发器状态变化都在该时钟到达时同时发生。而在异步时序电路中,没有统一的时钟脉冲,触发器状态变化由各自时钟脉冲信号或输入信号决定。两者相比,同步时序逻辑电路工作速度快,分析、设计容易,但需要设备较多。典型的时序逻辑电路有:触发器、寄存器、移位寄存器、计数器和随机存储器等。

寄存器是一种常用的逻辑部件,主要用于接收、暂存和传送数码。触发器具有记忆作用,可以存储一位二进制数,因此 n 个触发器的组合就是能存放 n 位二进制数码的寄存器。

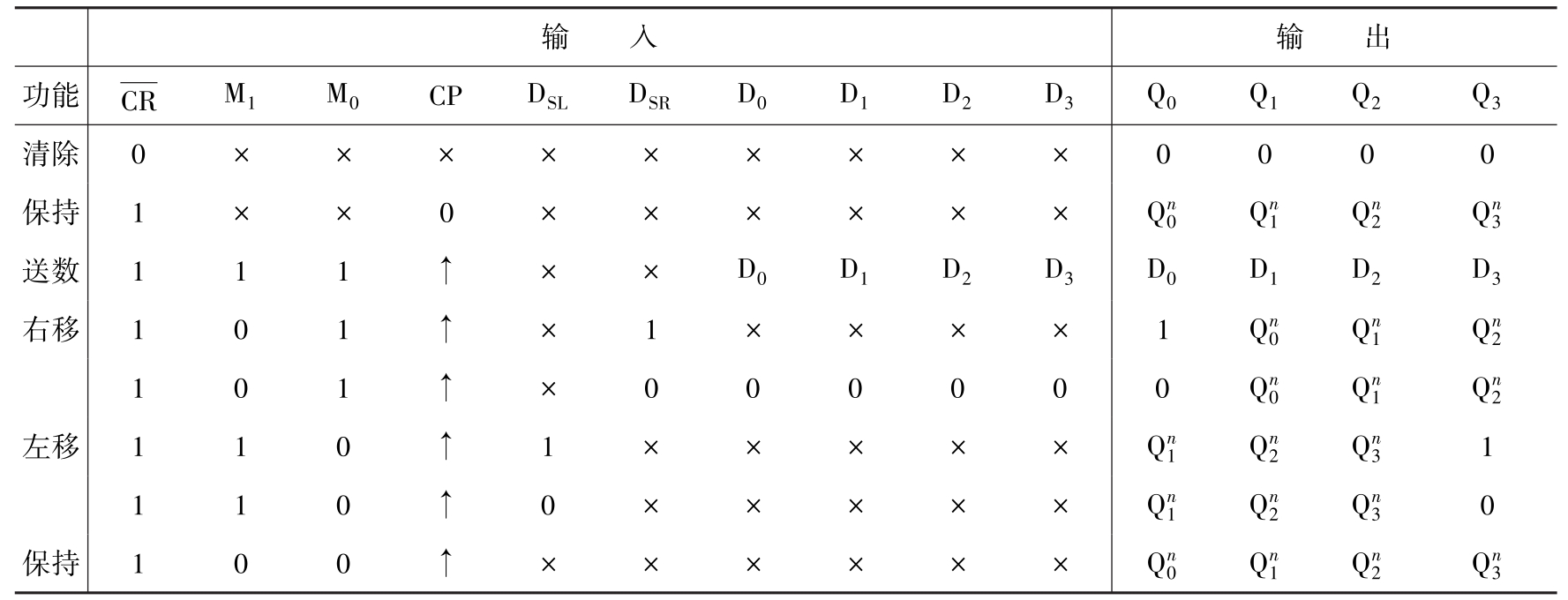

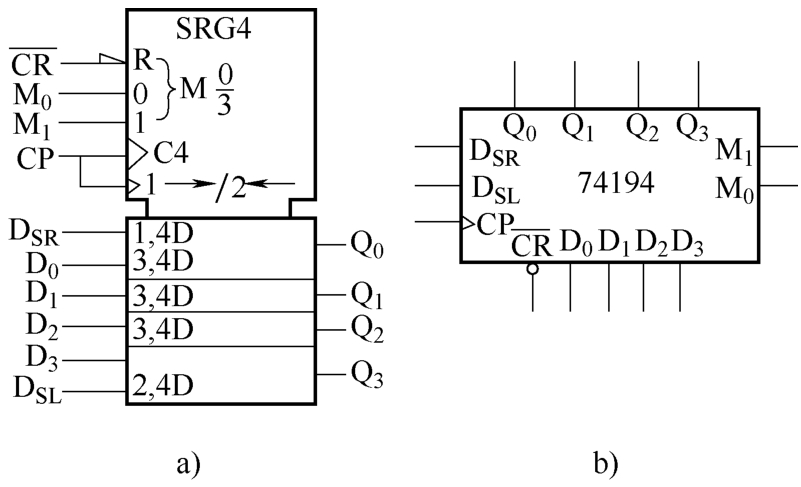

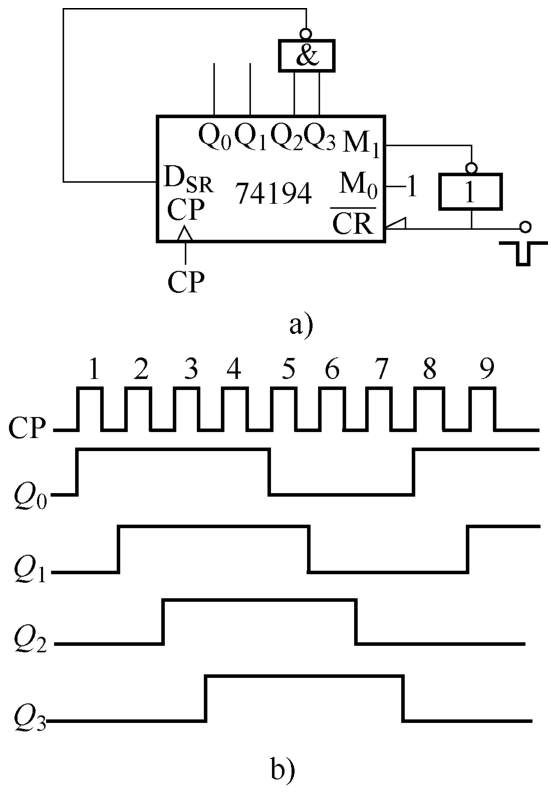

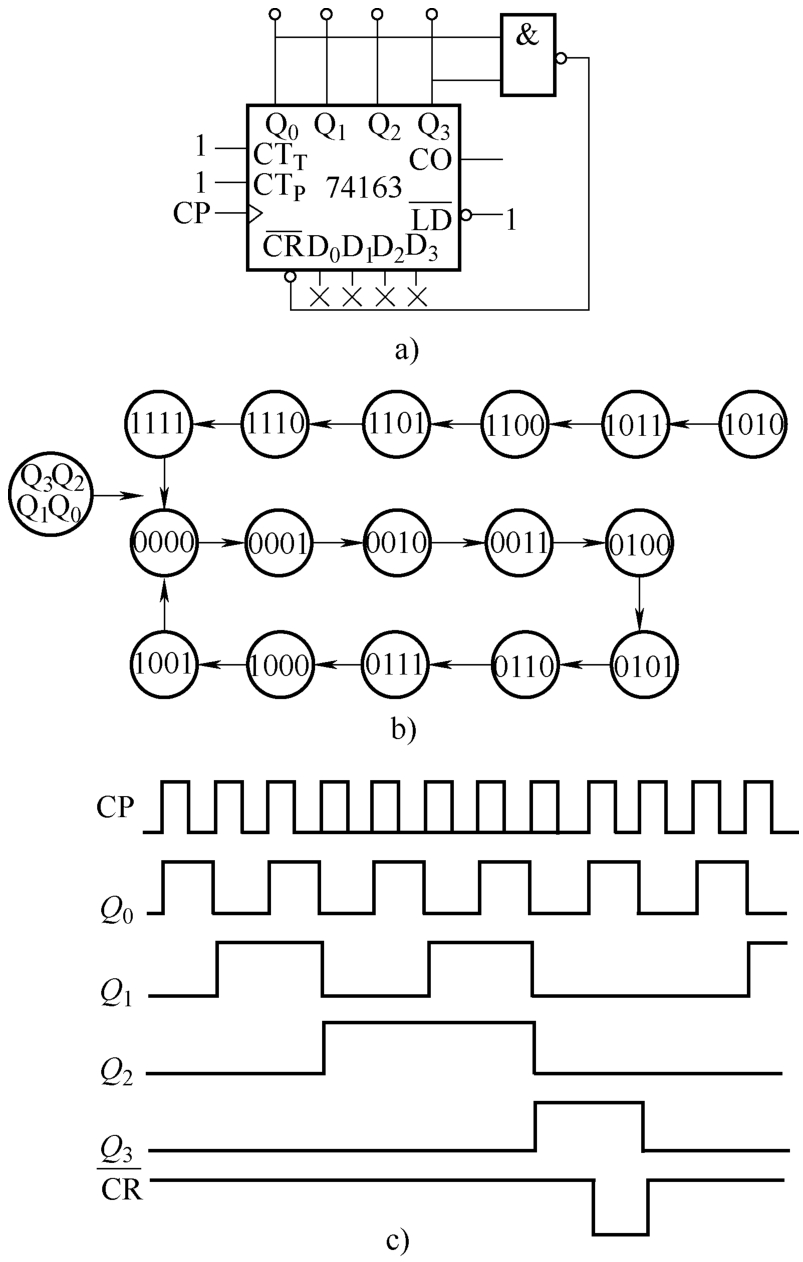

移位寄存器除了有寄存数码的功能,还具有将数码移位的功能,即在移位脉冲作用下将寄存器中各位的内容依次向左(或向右)移动一位。按移位方式可将其分为:单向移位寄存器(左移或右移)和双向移位寄存器(兼有左移和右移的功能)。74194是四位双向移位寄存器,其符号、功能见图4.6-27和表4.6-13。用74194移位寄存器构成的四位右移时序脉冲发生电路及工作波形见图4.6-28。

表4.6-13 74194功能表

图4.6-27 双向移位寄存器74194

a)国标逻辑符号 b)惯用逻辑符号

图4.6-28 用74194构成的右移时序脉冲发生电路及工作波形

a)逻辑图 b)波形图

常用的集成寄存器有74174,74175及三态寄存器74173等。移位寄存器有74164,7495等。中规模的MOS动态移位寄存器是利用栅电容的暂存作用存储二进制信息,为了防止信息丢失,需要实时地对所存信息进行“刷新”。

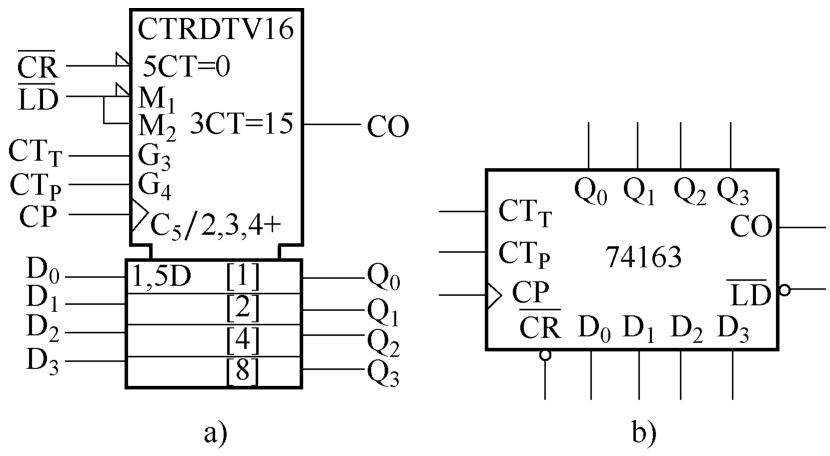

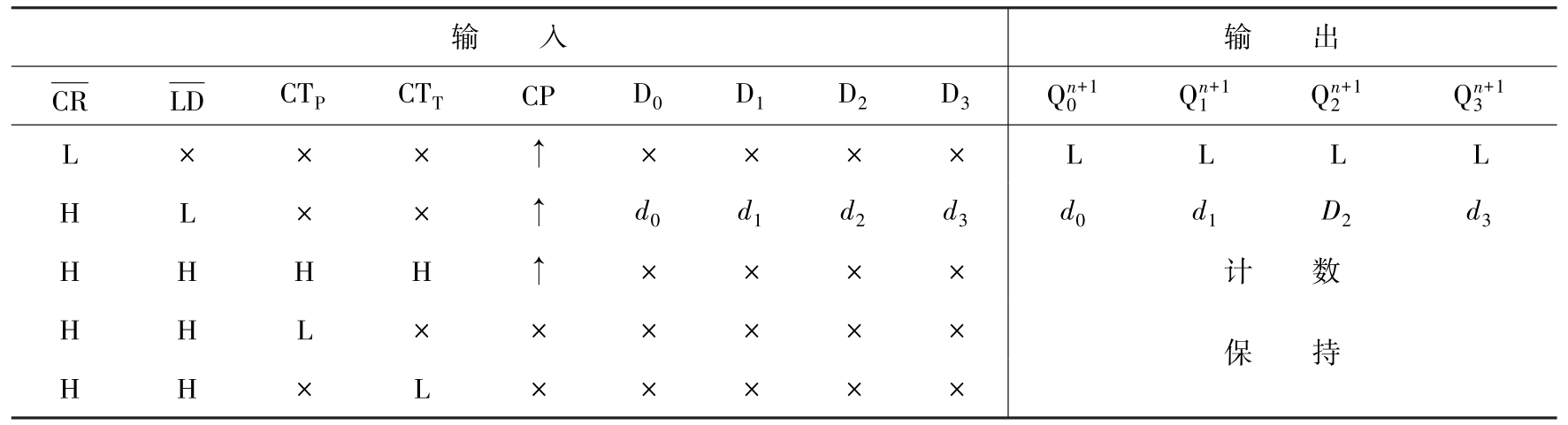

计数器是一种能对输入脉冲进行计数的逻辑器件。按计数脉冲引入方式分为同步计数器和异步计数器;按进位基数可分为二进制,十进制,任意进制的计数器;按计数增减趋势分为递增计数器,递减计数器和可逆计数器。计数器可作为分频器,一个 n 进制的计数器,对周期性的输入脉冲可实现 n 分频。

常用中规模集成计数器74LS163是一个四位同步二进制计数器,其逻辑符号和功能表分别如图4.6-29和表4.6-14所示。图中

为同步清零端,CT

P

、CT

T

是使能控制端,

为同步清零端,CT

P

、CT

T

是使能控制端,

是置数端,D

0

~D

3

是数据输入端,CO是进位输出端。74163有清零、送数、保持和计数功能。图4.6-30是借助74163的“同步清零”功能构成的同步十进制加法计数器。

是置数端,D

0

~D

3

是数据输入端,CO是进位输出端。74163有清零、送数、保持和计数功能。图4.6-30是借助74163的“同步清零”功能构成的同步十进制加法计数器。

图4.6-29 集成计数器74163

a)国标逻辑符号 b)惯用逻辑符号

表4.6-14 74163的功能表

图4.6-30 借助74163的“同步清零”功能构成同步十进制加法计数器

a)连线图 b)状态图 c)时序图

在数字计算机和控制系统中为了协调各部分电路的工作,需要一种按时间顺序逐个地出现节拍控制脉冲的电路,即顺序脉冲分配器,又称顺序脉冲发生器或节拍脉冲发生器。脉冲分配器可分为移位寄存器型和计数器型两大类,若将同步计数器与移位寄存器适当地集合于一体,就可以集中这两种电路的优点。

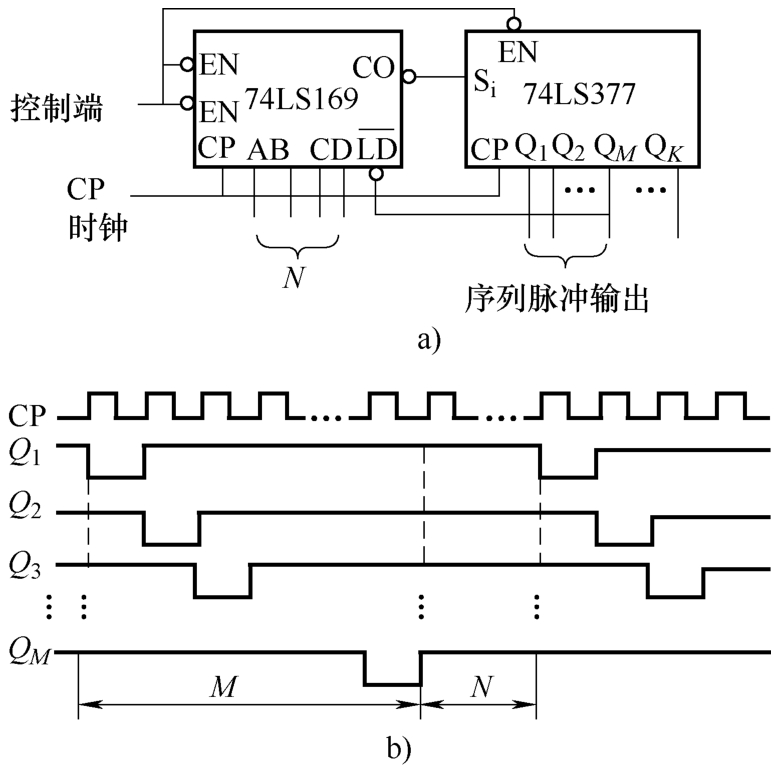

图4.6-31为用四位二进制可逆计数器74LS169和八 D 触发器74LS377构成的混合式序列脉冲发生器,将74LS377接成八位右移移位寄存器,并以74LS169的进位输出作为串行输入信号,在输出端就可得到如图4.6-18b)的序列脉冲。

通过计数器级联可以任意改变序列长度,同时该电路还提供了一个控制端,当此控制端为高电平时,禁止计数器和移位寄存器工作。

图4.6-31 混合式序列脉冲发生器

a)逻辑电路图 b)波形图

即数模转换器,能实现数字量转换为模拟量的功能。D/A转换器种类繁多,主要有权电阻网络、T型或倒T型电阻网络、权电流型和电容型D/A转换器等。

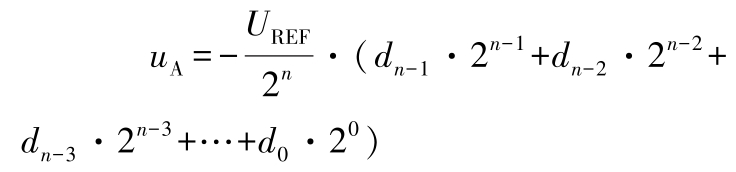

倒T型电阻网络D/A转换器的结构见图4.6-32。它由参考电压源 U REF 、倒T型电阻网络和模拟开关三部分组成。 d n -1 、 d n -2 、 d n -3 、…、 d 0 。为 n 位输入数字量,分别控制 n 个模拟开关S n -1 、S n -2 、S n -3 、…、S 0 ,当某位输入数字量为1时,相应开关与运放反相输入端相接;为0时接地。输出模拟电压为

图4.6-32 倒T型电阻网络D/A转换器

倒T型电阻网络D/A转换器的特点是只采用 R 、2 R 两种电阻,能保证电阻网络的精度,转换速度较快。在集成芯片中被广泛应用。

权电阻网络D/A转换器,电阻值离散性大,精度不高,在集成D/A转换器中很少采用。T型电阻网络D/A转换器速度较低,权电流D/A转换器克服了倒T型电阻网络数模转换器中,由模拟开关压降引起的转换误差,但电路较复杂。电容型D/A转换器主要用于MOS型单片集成电路。

5G7520(国产)和AD7541都是单片集成倒T型D/A转换器,采用CMOS模拟开关,分辨率分别为10位和12位。BG381(国产)和AD561均为双极型单片集成权电流数模转换器,采用双极型非饱和模拟开关,分辨率分别为8位和10位。使用时需外接运算放大器和补偿电阻。

即模/数转换器,能实现模拟量转换为数字量的功能。A/D转换器一般可分为两大类:1)直接模/数转换器,常见的有并行比较型和逐次比较型两种;2)间接模/数转换器,常见的有双积分型模/数转换器和电压-频率模/数转换器两种。

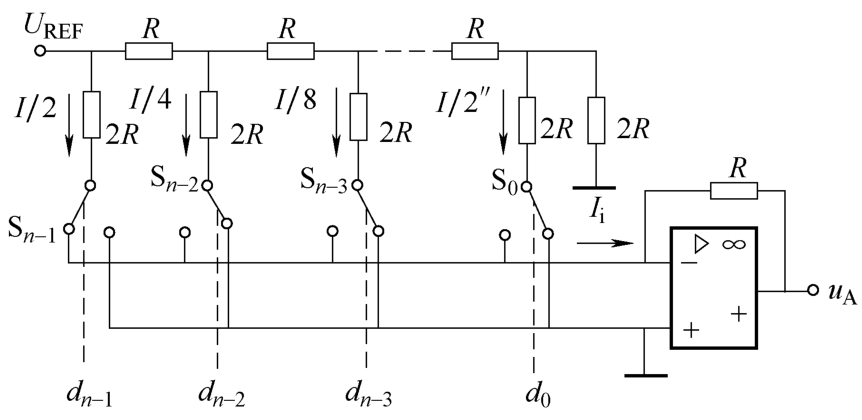

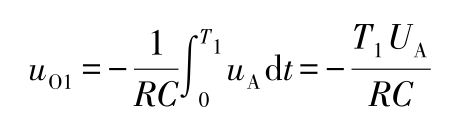

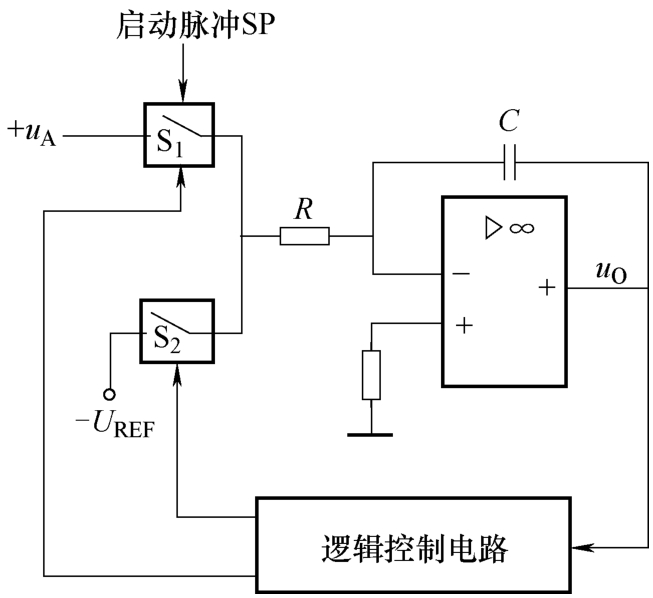

双积分型A/D转换器的原理框图如图4.6-33所示。它的转换过程为两次积分。第一次定时积分,设积分器初始电压为0,逻辑控制电路使模拟开关S 1 闭合,S 2 断开,积分器对输入的模拟电压 U A 进行固定时间(0~ T 1 )的采样积分,当 t = T 1 时,积分器输出电压为

图4.6-33 双积分型A/D转换器原理框图

第二次定值积分,使S 1 断开,S 2 闭合,积分器对基准电压 -U REF 进行反向积分,这时积分器的输出电压上升,当上升到0时,定值积分结束。反向积分时间间隔为

这表明反向积分的时间Δ t 与 U A 成正比,对时间Δ t 进行计数,就可以把输入模拟电压转换成相应的数字量。

双积分型A/D转换器转换速度较低,但电路简单,工作可靠,且具有很强的抗干扰能力,广泛应用于数字仪表中。

在A/D转换器中,并行比较型转换速度最快,但精度不高。逐次比较型转换速度较快,分辨率较高,误差较低,在集成芯片中被广泛采用。

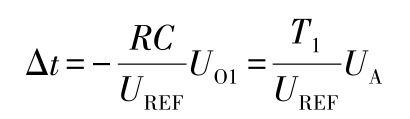

是存储内容固定不变,只能读出,不能随时写入的存储信息的半导体器件。ROM种类很多,按所用的器件类型分,有二极管ROM、双极型ROM和MOS型ROM三种。按存入信息的方式分,可分为固定ROM、可编程ROM(即PROM),可擦除可编程ROM(即EPROM)三种。

地址译码器有字译码结构和复合译码结构两种。字译码结构ROM见图4.6-34。字线W

3

、W

2

、W

1

、W

0

和

、

、

、

、

、

、

位线的交叉点就是一个存储单元,当存储单元为1时,相应交叉点用

位线的交叉点就是一个存储单元,当存储单元为1时,相应交叉点用

表示,反之当存储单元为0时,相应的交叉点用+表示。位线经过输出电路作为ROM的输出端。输出电路作用是信号驱动和三态缓冲。

表示,反之当存储单元为0时,相应的交叉点用+表示。位线经过输出电路作为ROM的输出端。输出电路作用是信号驱动和三态缓冲。

图4.6-34 字译码结构ROM

存储矩阵可有三种方式,其中固定存储器的存储矩阵是由生产厂家做成的,用户不能修改。PROM的内容可由用户自己编写,但只能一次编程,编程后存储的内容不能再改变。EPROM可进行多次编程,并能长期保存其存储内容,若要改变EPROM内容,可用紫外线照射该器件,然后可重复编程。另外还有一种能用电压信号快速擦除和编程的EPROM,称为EEPROM。

目前使用最为广泛的是只读存储器EPROM,有2716(2k×8bit)、2732(4k×8bit)、2764(8k×8bit)、27128(16k×8bit)、27256(32k×8bit)等型号。

Flash存储器又称闪存,它结合了ROM和RAM的长处,不仅具备EEPROM的性能,还可以快速存取数据,是一种非易失的RAM(NVRAM),数据不会因为断电而丢失。U盘和固态硬盘里用的就是这种存储器。过去嵌入式系统一直使用ROM(EPROM)作为它们的存储设备,现在Flash全面代替了ROM(EPROM)在嵌入式系统中的地位,用作存储Bootloader以及操作系统或者程序代码。常见的FLASH存储芯片型号有W25Q40BW、IS25WD040、MX25VB006E等。

目前Flash主要有NOR Flash和NAND Flash两种。NAND flash内部构成存储逻辑单元的连接方式与NAND门一样,NOR flash内部构成存储逻辑单元的连接方式与NOR门一样。NOR Flash的读取和常见的SDRAM的读取是一样,用户可以直接运行装载在NOR FLASH里面的代码,这样可以减少SRAM的容量从而节约了成本。NAND Flash没有采取内存的随机读取技术,它的读取是以一次读取一块的形式来进行的,通常是一次读取512个字节,采用这种技术的Flash比较廉价。用户不能直接运行NAND Flash上的代码,因此好多使用NAND Flash的开发板除了使用NAND Flah以外,还装上了一块小的NOR Flash来运行启动代码。

一般小容量的用NOR Flash,因为其读取速度快,多用来存储操作系统等重要信息,而大容量的用NAND FLASH,最常见的NAND FLASH应用是嵌入式系统采用的DOC(Disk On Chip)和通常用的“闪盘”,可以在线擦除。目前市面上的FLASH主要来自Intel,AMD,富士通和东芝,而生产NAND Flash的主要厂家有三星和东芝,常见的NOR FLASH型号有:S25FL128、MX25L1605、W25Q64等;常见的NAND Flash存储芯片型号有KLMAG8DEDD、THGBMAG8B4JBAIM、EMMC04G-S100等。

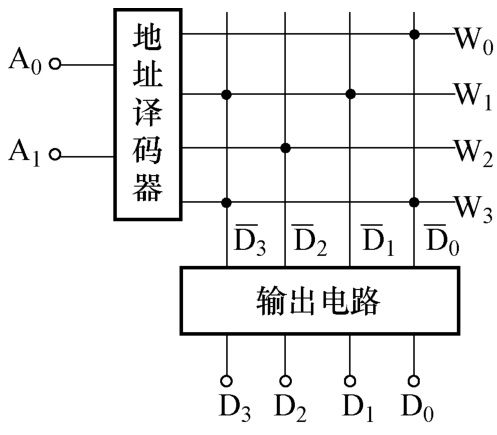

是能够随时在存储器任一指定单元存入或取出信息的存储器,又称读/写存储器。RAM有双极型和MOS型两种;按其工作方式不同分为静态RAM(SRAM)和动态RAM(DRAM)两大类。

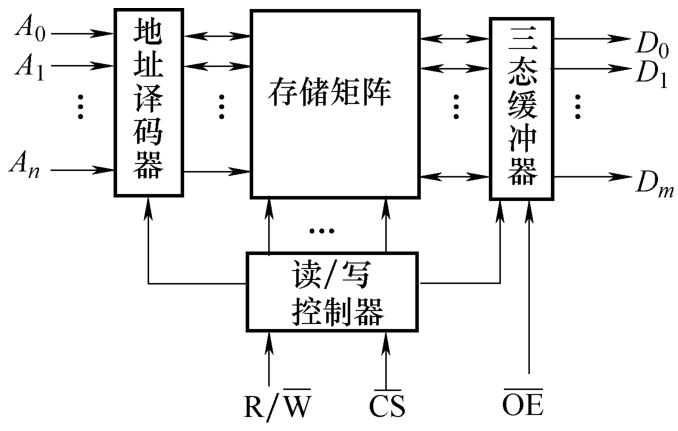

RAM主要由存储矩阵、地址译码器、三态缓冲器和读/写控制器组成,其结构见图4.6-35。

图4.6-35 RAM结构图

存储矩阵是由大量基本存储单元组成,每个基本存储单元可以存储一位二进制数码。这些基本存储单元按一定规则组合起来,就构成了存储矩阵。基本存储单元是一种双稳态触发器。MOS基本存储单元分为静态存储单元和动态存储单元两种。

存储矩阵中基本存储单元的编址方法有两种,单译码编址方式和双译码编址方式。在单译码编址方式中,地址线由一个地址译码器译码输出作为存储矩阵的字线;而双译码编址方式有 X 、 Y 两个地址译码器,地址线分成两组。一组送入 X 地址译码器译码输出作为存储矩阵的行线,另一组送入 Y 地址译码器译码输出作为存储矩阵的列线。存储矩阵中的某个基本存储单元能否被选中由行线和列线共同决定。

图4.6-35中

为读写控制线,高电平时对存储器进行读操作,低电平时为写操作。

为读写控制线,高电平时对存储器进行读操作,低电平时为写操作。

和

和

分别为片选和输出允许控制线,都是低电平有效。若

分别为片选和输出允许控制线,都是低电平有效。若

和

和

均为高电平,则三态缓冲器呈高阻状态,即该RAM芯片与系统的数据总线完全隔离。

均为高电平,则三态缓冲器呈高阻状态,即该RAM芯片与系统的数据总线完全隔离。

SRAM是Static Random Access Memory的缩写,中文含义为静态随机访问存储器,它是一种类型的半导体存储器。“静态”是指只要不掉电,存储在SRAM中的数据就不会丢失。这一点与DRAM不同,DRAM需要进行周期性的刷新操作。SRAM与ROM和Flash存储器不同,因为它是一种易失性存储器,只有在电源保持连续供应的情况下才能够保持数据。“随机访问”是指存储器的内容可按任何顺序访问,与前一次访问位置无关。SRAM中的每一位均存储在四个晶体管当中,这四个晶体管组成了两个交叉耦合反向器。这个存储单元具有两个稳定状态,通常表示为0和1。另外还需要两个访问晶体管用于控制读或写操作过程中存储单元的访问。因此,一个存储位通常需要六个MOSFET。对称的电路结构使得SRAM的访问速度要快于DRAM。SRAM比DRAM访问速度快的另外一个原因是SRAM可以一次接收所有的地址位,而DRAM则使用行地址和列地址复用的结构。

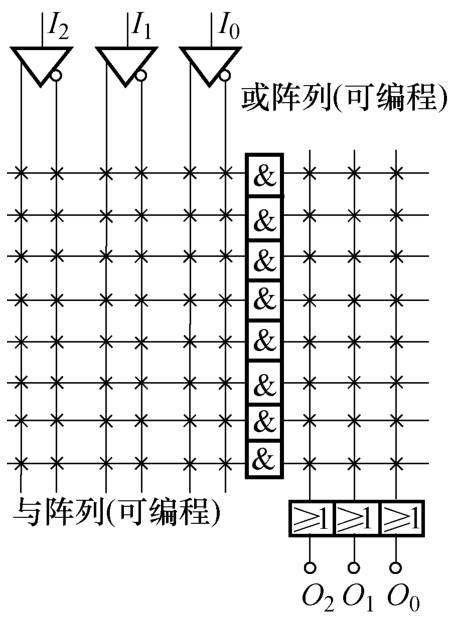

ROM的一种变型,与ROM的主要区别在于不仅存储阵列(或阵列)可编程,其译码阵列(与阵列)也可编程。这样与门阵列不采用全译码方式,与门个数小于 n ( n 为输入项数),减小了与门阵列规模,提高了器件工作速度,其基本结构见图4.6-36。

图4.6-36 PLA的基本结构

PLA既是一个可编程的与或逻辑阵列,便可将它看成与或两级结构的多输出逻辑电路,可用它实现逻辑函数。首先求出逻辑函数的最简与或表达式,然后用与阵列构成逻辑函数的各乘积项,再由或阵列构成各乘积项的或关系。PLA除能实现各种组合逻辑电路外,若再增加存储电路(触发器网络),还可实现时序逻辑电路。

编程方式有两种:1)掩模PLA,由制造厂家根据用户提供的真值表完成;2)现场编程FPLA,由用户自己编程,如12×50×6的FPLA,它有12个输入端、50个积项、6个输出。

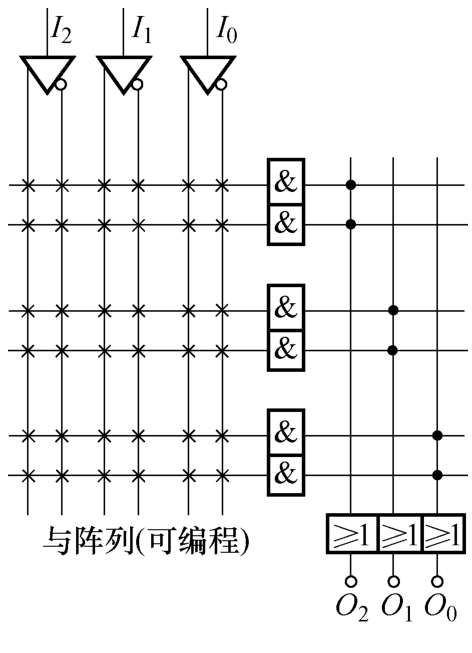

由与阵列和或阵列两部分组成,与PLA不同的是PAL只有与阵列是可编程的,而或阵列是固定连接的。每个输出是若干个积项之和,而其中积项的数目是固定的。通常典型的逻辑函数要求3~4个积项,在PAL产品中最多积项可达8个,这种结构十分有效且有较高工作速度,PAL的基本结构见图4.6-37。

图4.6-37 PAL的基本结构

不同的PAL芯片有不同的输出和反馈结构,主要有:

1)专用输出的基本门阵列结构。

2)异步可编程的输入/输出(I/O)结构,这类PAL芯片的输入/输出端数可在一定范围内变化,可以比较方便地利用一个芯片构成多级组合逻辑电路,或异步时序电路。

3)寄存器输出结构,这种结构的PAL具有记忆能力,可实现时序逻辑功能。

4)异或结构,这种结构的PAL不但具有寄存器输出结构PAL的功能,而且利用异或功能还很容易实现保持操作。

5)算术选通反馈结构,这种结构是在PAL的基础上增加了反馈选通电路,使其能方便地实现快速算术操作。

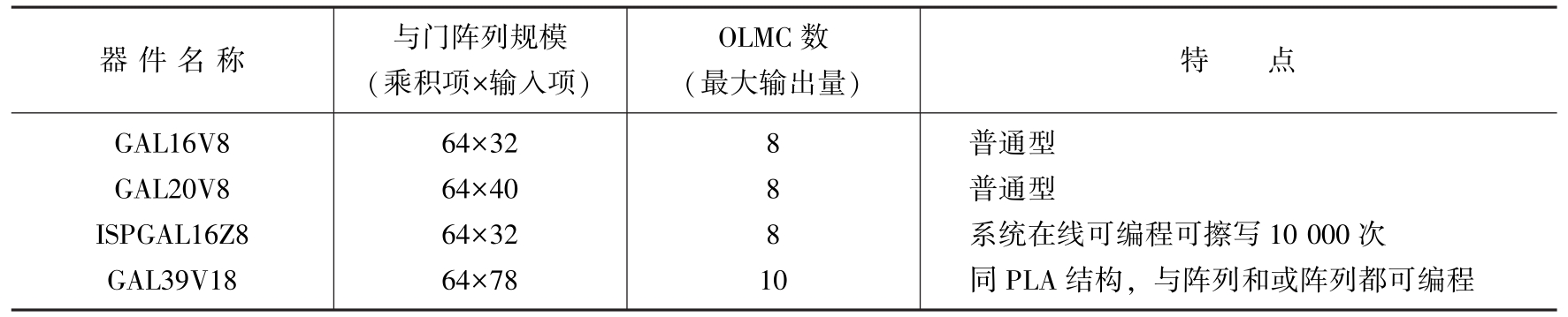

是一种高性能,高可靠性的理想可编程逻辑器件,由于采用了E 2 CMOS工艺,实现了快速的电可擦除和重新编程,并具有双极型的高速性能(25~35ns)和CMOS的低功耗特点(最大工作电流45mA,最大维持电流35mA),因此集成度很高。在结构上,GAL器件延袭了PAL的与或平面结构,还在此基础上发展出了独特的输出逻辑宏单元,实现了结构的通用性。使为数不多的几种GAL器件能代替数十种PAL器件和数百种SSI/MSI标准器件,其结构的灵活性是以前的PLD器件所不具备的。另外为防止逻辑复制,GAL芯片具有保密单元,此外,其电子标签功能便于文档管理。

目前GAL产品主要有三类:1)通用型GAL,包括GAL16V8和GAL20V8。GAL16V8是20脚器件,器件型号中的16表示有16个输入端,8个输出端;2)FPLA型GAL,GAL39V18和GAL6001均采用FPLA结构,其中GAL39V18是24脚器件,它的与阵列和或阵列都可编程,具有极强的灵活性;3)系统在线可编程GAL,如ISPGAL16Z8器件,它也是24脚器件,具有在线可编程和实时在线诊断能力,可擦写1万次。表4.6-15为几种GAL器件的比较。

表4.6-15 几种GAL器件比较

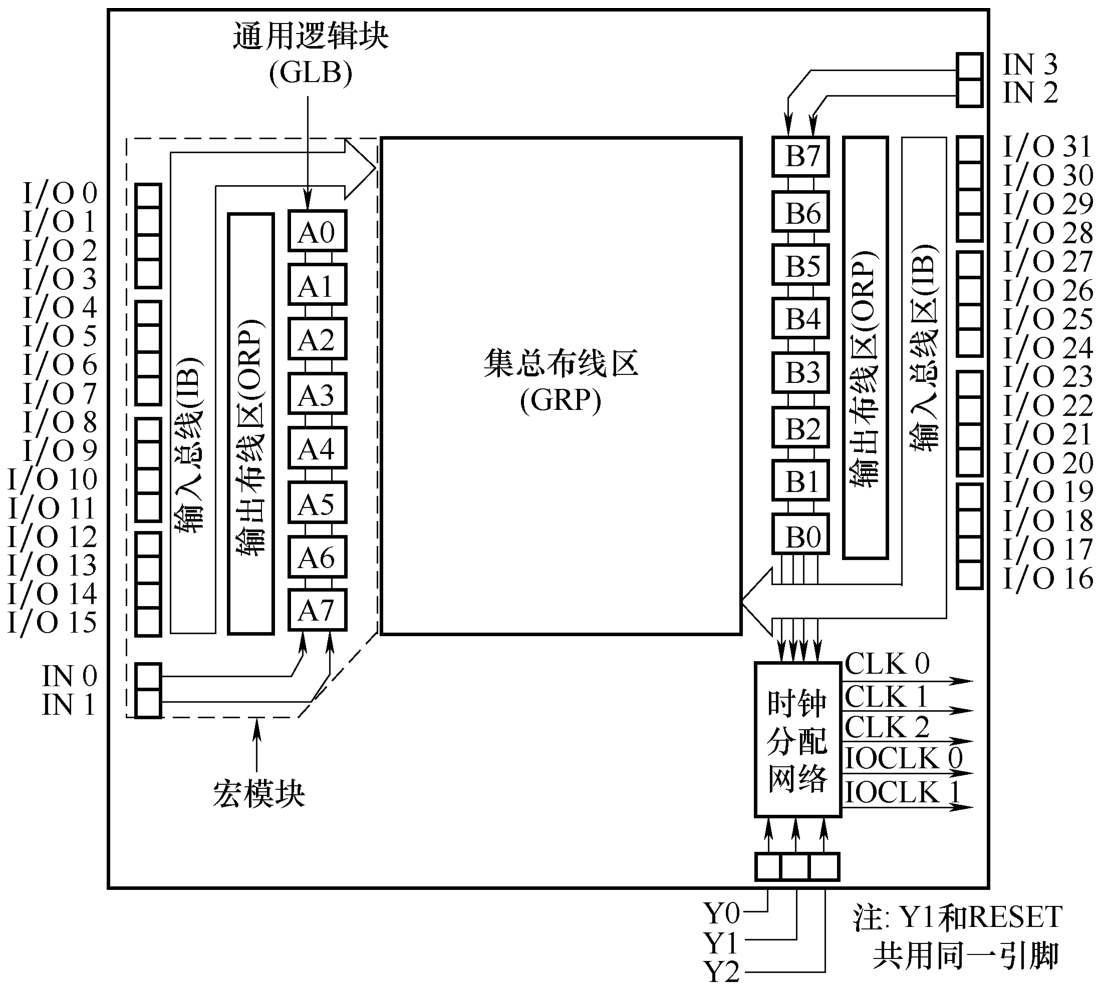

这种器件最大的特点是在系统可编程(In System Programmability,ISP)特性。它由四部分组成:通用逻辑块(Generic Logic Block,GLB)、集总布线区(Global Routing Pool,GRP)、输入/输出单元(I/O cell,IOC)、输出布线区(Output Routing Pool,ORP)。其中GLB是整个芯片核心,芯片的逻辑功能主要由它来实现;GRP是器件的内部连线资源,它可提供100%的连线布通率;IOC主要用于I/O引脚和器件内部逻辑结构的信号连接;ORP负责GRP输出信号到IOC的连接。此外,还有一些控制信号,如时钟信号、输出允许信号等。

ispLSI系列CPLD器件采用了Ultra MOS工艺,具有集成度高、速度快的特点以及在系统可编程、边界扫描测试、加密及短路保护等功能。

图4.6-38为ispLSI1016的基本结构框图为ispLSI1016的基本结构框图,它由16个相同的GLB(A0~A7、B0~B7)、32个相同的IOC(I/O0~I/O31)、可编程的GRP、时钟分配网络以及ISP控制电路等部分组成。在GRP的左边和右边各形成一个宏模块。每个宏模块包括:8个GLB、16个IOC、四个直接输入端(IN0~IN3)、一个ORP以及16位的输入总线。GRP位于芯片的中央,将所有片内逻辑联系在一起,其特点是输入输出之间的延迟恒定和可预知,与它们的位置无关。

美国Lattice公司已经推出了ispLSI1000、ispL-SI2000、ispLSI3000、ispLSI5000、ispLSI6000和is-pLSI8000等6个系列的ISP CPLD产品。其中ispL-SI1000系列为通用CPLD产品,适合在一般的数字系统中使用。ispLSI2000系列是高速、多引脚的CPLD产品,适合在速度要求高或需要较多输入、输出管脚的电路或系统中使用。ispLSI3000是高密度的CPLD产品,适用于数字信号处理、图形处理、数据加密、解密与压缩等。ispLSI5000系列是第二代在系统可编程逻辑器件,是3.3V的高密度CPLD产品,可支持64位总线系列等复杂数字系统的设计。ispLSI6000系列是专门为DSP等用途设计的CPLD产品,其在结构上增加了存储器,把FIFO或者RAM模块和可变成逻辑电路集成到同一块硅片上,这样可以减小互连延时,提高系统工作速度。ispLSI8000系列是规模最大的ISP器件,其集成密度最高(可达到58000门),适合于系统级的数字信号处理。

是一种高密度现场可编程逻辑器件,由若干独立的可编程逻辑模块组成,用户可以通过编程将这些模块连接成所需要的数字系统,具有更强的逻辑实现能力和更大的灵活性。

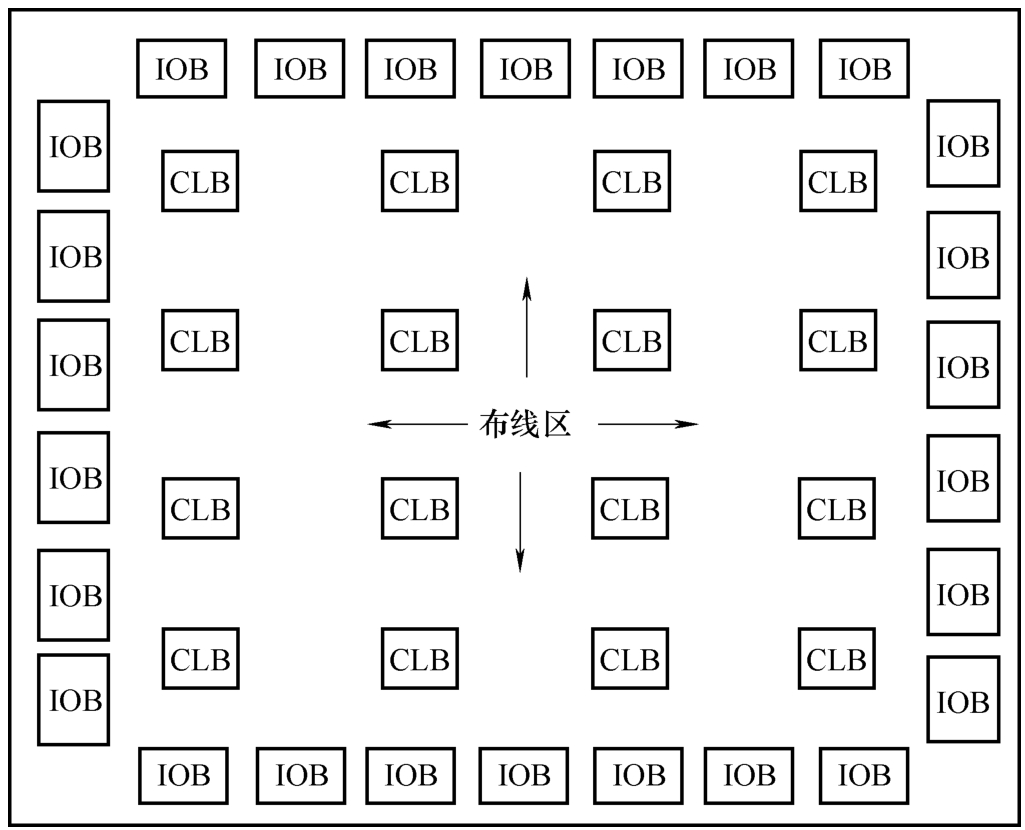

图4.6-39为FPGA的基本结构,它由三种可编程单元和一个用于存放编程数据的静态存储器组成。这三种可编程的单元是输入/输出模块(Input/Output Block,IOB),可编程逻辑模块(Configurable Logic Blocks,CLB)和可编程内部连线(Programmable Interconnect,PI)。其中CLB是FPGA的基本逻辑单元,它提供用户所需要的逻辑功能,通常规则地排列成一个阵列,散布于整个芯。IOB是芯片外部引脚数据与内部数据进行交换的接口电路,通过编程可将I/O引脚设置成输入、输出和双向三种方式,通常排列于芯片四周。PI包括各种长度的连线线段和一些可编程连线开关,它们将各个可编程逻辑块或输入/输出块连接起来,构成特定功能的电路。

图4.6-38 ispLSI1016的基本结构框图

图4.6-39 FPGA的基本结构框图

近年来,国产FPGA有了长足发展,以紫光同创为龙头,安路、高云、复旦微、京微齐力、易灵思等正在追赶,虽然国产FPGA起步较晚,但发展势头强劲,紫光同创的Titan系列是第一款国产自主产权千万门级高性能FPGA产品,采用40nm CMOS工艺和自主产权的体系结构,广泛适用于通信网络、信息安全、数据中心、工业控制等领域。

这种芯片由于采用特殊的软硬件结构,可以用来快速地实现各种数字信号处理算法。DSP芯片的结构特征主要是指:哈佛结构、流水线操作、专用的硬件乘法器、特殊的DSP指令、快速的指令周期。

哈佛结构的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址,独立访问,与两个存储器相对应的是系统中设置了程序总线和数据总线,从而使数据的吞吐率提高了一倍。由于程序和存储器在两个分开的空间中,因此取指和执行能完全重叠。流水线与哈佛结构相关,DSP芯片采用流水线技术以减少指令执行的时间,从而增强了处理器的处理能力。处理器可以并行处理二到四条指令,每条指令处于流水线的不同阶段。DSP芯片具有专用的乘法器,从而提高了乘法运算速度,另外还有特殊的DSP指令,再加上集成电路的优化设计可使DSP芯片的指令周期在200ns以下。

DSP芯片可按照以下三种方式分类:

(1)按基础特性分 可分为静态与一致性DSP芯片。若DSP处理器在某时钟频率范围内的任何时钟频率上能正常工作,除计算速度有变化外,没有性能的下降,则为静态DSP芯片。若有多种DSP处理器的指令系统和相应的机器代码及引脚结构相互兼容,则为一致性DSP芯片。

(2)按数据格式分 可分为两种:数据以定点格式工作的DSP处理器,称之为定点DSP芯片;以浮点格式工作的,称为浮点DSP芯片。不同的浮点DSP芯片所采用的浮点格式不完全一样,有的DSP芯片采用自定义的浮点格式,有的DSP芯片则采用IEEE的标准浮点格式。

(3)按用途分 可分为通用型和专用型两种。通用型DSP芯片适合普通的DSP应用;专用型DSP芯片是为特定的运算而设计的,更适合特殊的运算,如数字滤波,卷积和FFT等。

在众多的DSP芯片种类中,最成功的是美国德克萨斯仪器公司(Texas Instruments,TI)和美国模拟器件有限公司(Analog Device Inc,ADI)的一系列产品。

TI公司第一代DSP芯片TMS32010及其系列产品TMS32011、TMS32C10/C14/C15/C16/C17等,第二代DSP芯片TMS32020、TMS320C25/C26/C28,第三代DSP芯片TMS32C30/C31/C32,第四代DSP芯片TMS32C40/C44,第五代DSP芯片TMS32C50/C51/C52/C53以及集多个DSP于一体的高性能DSP芯片TMS32C80/C82等。另外,TI公司在原来的基础上发展了三种新的DSP系列,它们是:TMS320C2000、TMS320C5000、TMS320C6000系列,成为当前和未来相当长时期内TI DSP的主流产品。其中,TMS320C6000系列的速度已超过1G flops。

ADI公司的DSP相对与TI公司的DSP系列,具有内部存储容量较大,多片协同工作能力强等优点。ADI的DSP有21xx系列、SHARC系列、TigerSHARC系列、Blackfin系列、ADAU146x系列等。

DSP系统具有接口方便、编程方便、稳定性好、精度高、可重复性好、集成方便等优点,因而在信号处理、自动控制、军事、通信、语音/语言、图形/图像和仪器仪表、工业和医疗等领域得到广泛应用。

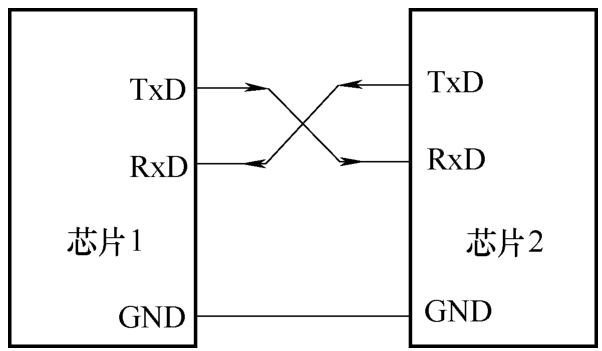

UART(Universal Asynchronous Receiver/Transmitter,通用异步接收器/发射器)通信需要三根线,RxD、TxD和GND,RxD是数据接收引脚,TxD是数据发送引脚。对于两个芯片之间的连接,见图4.6-40,两个芯片GND共地,同时TxD和RxD交叉连接。这里的交叉连接的意思就是,芯片1的RxD连接芯片2的TxD,芯片2的RxD连接芯片1的TxD。这样,两个芯片之间就可以进行TTL电平通信。

图4.6-40 TTL串口连接

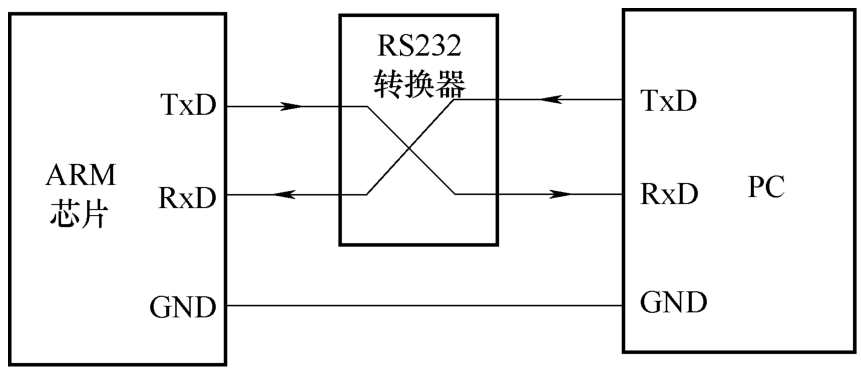

如图4.6-41所示,若是芯片与PC(或上位机)相连,除了共地之外,不能直接交叉连接。尽管PC和芯片都有TxD和RxD引脚,但是通常PC(或上位机)通常使用的都是RS232接口(通常为DB9封装),因此不能直接交叉连接。RS232接口是9针(或引脚),通常是TxD和RxD经过电平转换得到的。故要想使得芯片与PC的RS232接口直接通信,需要也将芯片的输入输出端口电平转换成RS232类型,再交叉连接。

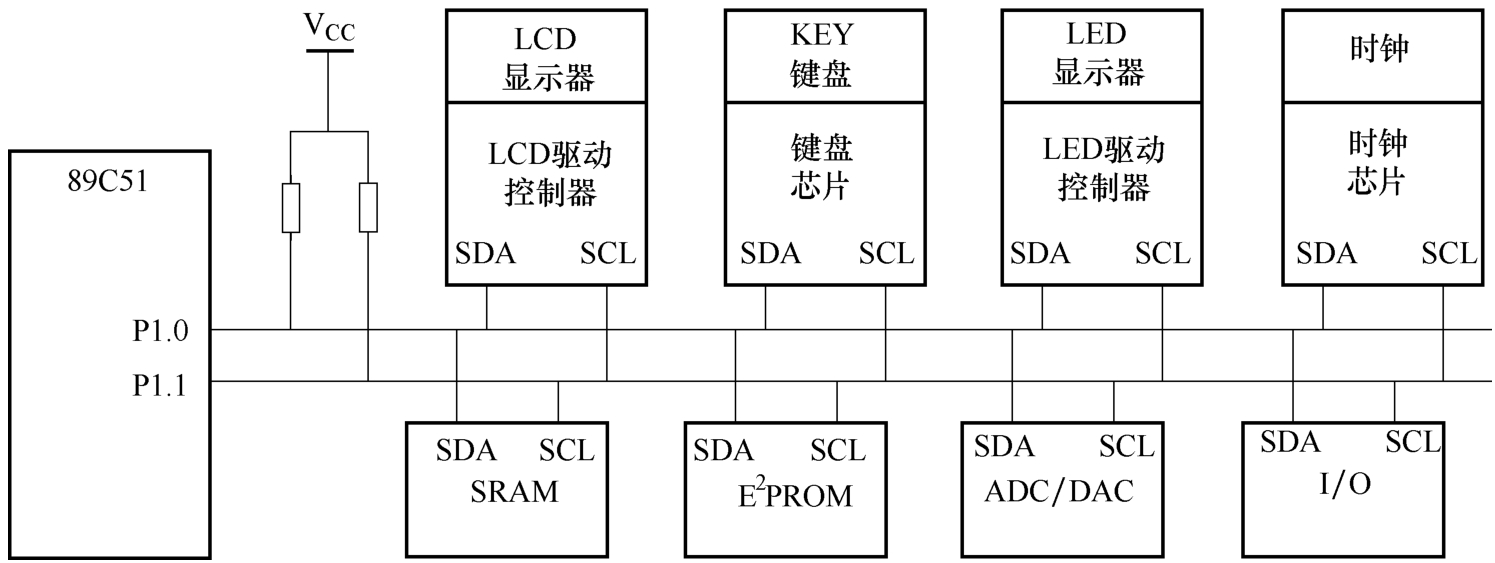

I 2 C总线是Philips公司开发的一种双向两线串行总线,以实现集成电路之间的有效控制,这种总线也称为Inter IC总线。目前,Philips及其他半导体厂商提供了大量的含有I 2 C总线的外围接口芯片,I 2 C总线已成为广泛应用的工业标准之一。标准模式下,基本的I 2 C总线规范的规定的数据传输速率为100kbit/s。快速模式下,数据传输速率为400kbit/s。高速模式下其数据传输速率为3.4Mbit/s。

图4.6-41 RS232接口连接方式

I 2 C总线始终和先进技术保持同步,并保持其向下兼容性。1)I 2 C总线采用二线制传输,一根是数据线SDA(Serial Data Line),另一根是时钟线SCL(serial clock line),所有I 2 C器件都连接在SDA和SCL上,每一个器件具有一个唯一的地址。2)I 2 C总线是一个多主机总线,总线上可以有一个或多个主机(或称主控制器件),总线运行由主机控制。主机是指启动数据的传送(发起始信号)、发出时钟信号、发出终止信号的器件。通常,主机由单片机或其他微处理器担任。被主机访问的器件叫从机(或称从器件),它可以是其他单片机,或者其他外围芯片,如A/D、D/A、LED或LCD驱动、串行存储器芯片。3)I 2 C总线支持多主(multi-mastering)和主从(master-slave)两种工作方式。多主方式下,I 2 C总线上可以有多个主机。I 2 C总线需通过硬件和软件仲裁来确定主机对总线的控制权。主从工作方式时系统中只有一个主机,总线上的其他器件均为从机(具有I 2 C总线接口),只有主机能对从机进行读写访问,因此不存在总线的竞争等问题。在主从方式下,I 2 C总线的时序可以模拟产生,I 2 C总线的使用不受主机是否具有I 2 C总线接口的制约。单主机系统I 2 C总线扩展示意图如图4.6-42。

图4.6-42 单主机系统I 2 C总线扩展示意图

采用I 2 C总线设计系统的优点:1)功能框图中的功能模块与实际的外围器件对应,可以使系统设计直接由功能框图快速地过渡到系统样机。2)外围器件直接“挂在”I 2 C总线上,不需设计总线接口;增加和删减系统中的外围器件,不会影响总线和其他器件的工作,便于系统功能的改进和升级。3)集成在器件中的寻址和数据传输协议可以使系统完全由软件来定义。

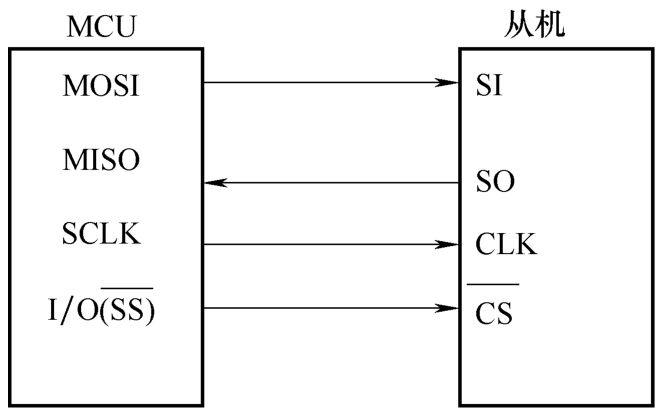

SPI(Serial Pe-ripheral Interface)是摩托罗拉公司提出的一种同步接口,它可以使微控制器(MCU)与各种外围设备以串行方式进行通信以交换信息。外围设备包括Flash存储器、网络控制器、LCD显示驱动器、模数转换器和微控制器等。SPI总线使用同步协议传送数据,接收或发送数据时由主机产生的时钟信号控制。SPI接口可以连接多个SPI芯片或装置,主机通过选择它们的片选来分时访问不同的芯片。

(1)SPI总线构成

MOSI(Master Out Slave In):主机发送,从机接收

MISO(Master In Slave Out):主机接收,从机发送

SCLK或SCK(Serial Clock):串行时钟

(Chip Select for the peripheral):外围器件的片选。有的微控制器设有专用的SPI接口的片选,称为从机选择

(Chip Select for the peripheral):外围器件的片选。有的微控制器设有专用的SPI接口的片选,称为从机选择

。

。

MOSI(SI或SDI)信号由主机产生,接收者为从机;ISO(SO或SDO)信号由从机发出;CLK或SCK由主机发出,用来同步数据传送;片选信号也由主机产生,用来选择从机芯片或装置。

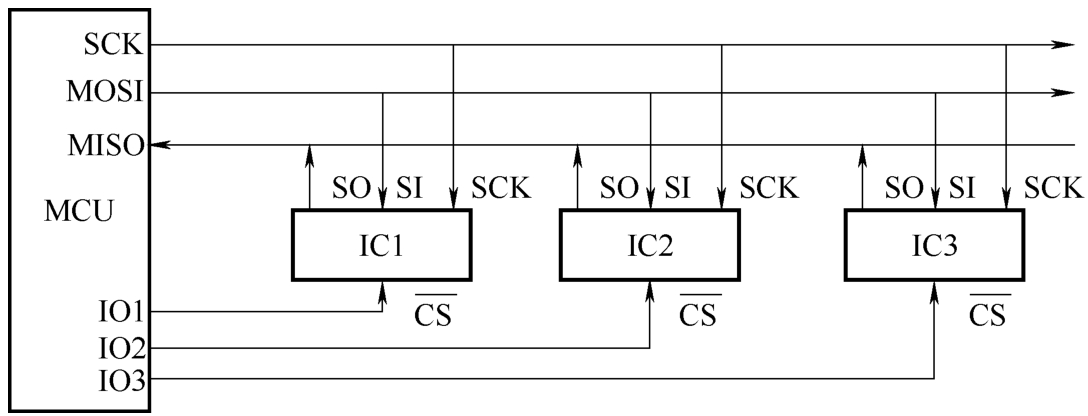

(2)SPI总线信号线基本连接关系 见图4.6-43。SPI总线系统有以下几种形式:一个主机和多个从机、多个从机相互连接构成多主机系统(分布式系统)、一个主机与一个或几个I/O设备构成的系统等。

图4.6-43 SPI总线信号线基本连接关系

(3)主从方式SPI总线接口系统的典型结构 见图4.6-44。

1)在大多数应用场合,可使用1个微控制器作为主控机来控制数据传送,并向1个或几个外围器件传送数据。从机只有在主机发命令时才能接收或发送数据。2)当一个主机通过SPI与多个芯片相连时,必须使用每个芯片的片选,这可通过MCU的I/O端口输出线来实现。

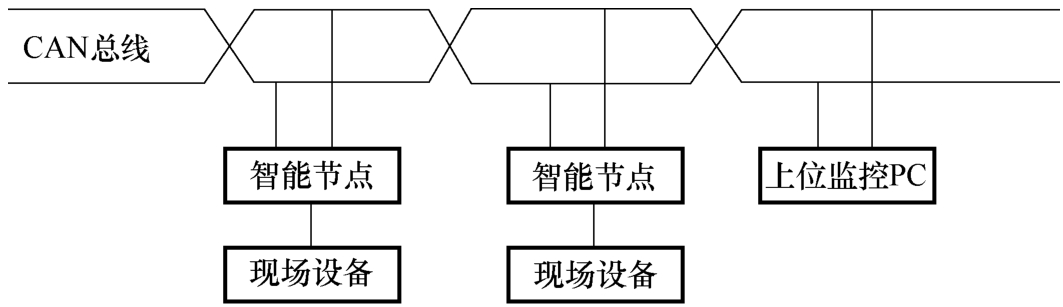

CAN(Control/Controller Area Network)是控制(器)局域网的简称。CAN是一种有效支持分布式控制或实时控制的串行通信网络,最初由德国博世公司在20世纪80年代用于汽车内部测试和控制仪器之间的数据通信。目前CAN总线规范已被国际标准化组织ISO制订为国际标准ISO11898,并得到了摩托罗拉、英特尔、飞利浦等大半导体器件生产厂家的支持,迅速推出各种集成有CAN协议的产品。目前CAN总线主要用于汽车自动化领域,如发动机自动点火、注油、复杂的加速制动控制(ASC)、抗锁定制动系统(ABS)和抗滑系统等。此外在工业过程控制领域,CAN也得到了广泛的应用。

CAN协议可分为:目标层、传送层、物理层。其中目标层和传送层包括了ISO/OSI定义的数据链路的所有功能。目标层的功能包括:确认要发送的信息,以及为应用层提供接口。传送层功能包括:数据帧组织、总线仲裁、检错、错误报告、错误处理。

CAN总线以报文为单位进行信息交换,报文中含有标示符(ID),它既描述了数据的含义又表明了报文的优先权。CAN总线上的各个节点都可主动发送数据。当同时有两个或两个以上的节点发送报文时,CAN控制器采用ID进行仲裁。ID控制节点对总线的访问。发送具有最高优先权报文的节点获得总线的使用权,其他节点自动停止发送;总线空闲后,这些节点将自动重发报文。

CAN系统的组成见图4.6-45,由上位监控PC、智能节点和现场设备三部分组成。

图4.6-44 主从方式SPI总线接口系统的典型结构

图4.6-45 CAN系统组成

通用串行总线(Universal Serial Bus,USB)的规范是IBM、康柏、英特尔、微软、NEC等多家公司联合制订的。USB总线规范草案最早提出于1994年底,几经修订后推出了版本号为0.7的正式版本,接着于1996年推出了USB1.0的正式版本,到了1998年又推出了修订的版本USB1.1。2000年底,USB组织推出了USB2.0,这个版本将USB总线的理论传输速度提高到了480Mbit/s的水平,支持它的芯片称为高速(High Speed)系列。2008年推出USB3.0的理论传输速度为5.0Gbit/s,2017年推出的USB3.2的理论传输速度为20Gbit/s,新型Type C插型不再分正反。2019年发布的USB4.0接口除了具备40Gbit/s的速率之外,统一采用USB Type-C接口,让接驳统一方便。2022年发布的USB4.2规范将传输速度提高到了80Gbit/s,提出了80Gbit/s USB Type-C主动式电缆,向下兼容以前所有USB版本,USB将受益于更高性能的显示器、存储、集线器和扩展坞。USB Type-C结构共有24个引脚,呈上下对称分布,通过D+、D-实现USB2.0传输,通过其中一个高速差分线实现USB3.0通信,两对高速差分线可实现USB3.2高速通信,USB4.0采用PAM3(3级脉冲幅度调制)以每通道25.6Gbit/s的波特率通过物理介质传输数据。数据的传输对硬件也有要求,数据传输速度越高,线材长度越短,当电流大于3A以上时,线材都需要搭载eMarker芯片来作为识别。针对设备对系统资源需求的不同,在USB规范中规定了四种不同的数据传输方式。

(1)等时(Isochronous)传输方式 该方式用来联接需要连续传输数据,且对数据的正确性要求不高而对时间极为敏感的外部设备,如麦克风、喇叭以及电话等。等时传输方式以固定的传输速率,连续不断地在主机与USB设备之间传输数据,在传送数据发生错误时,USB并不处理这些错误,而是继续传送新的数据。

(2)中断(Interrupt)传输方式 该方式传送的数据量很小,但这些数据需要及时处理,以达到实时效果,此方式主要用在键盘、鼠标以及操纵杆等设备上。

(3)控制(Control)传输方式,该方式用来配置和控制主机到USB设备的数据传输方式和类型。设备控制指令、设备状态查询及确认命令均采用这种传输方式。当USB设备收到这些数据和命令后,将依据先进先出的原则处理到达的数据。

(4)批(Bulk)传输方式,该方式用来传输要求正确无误的大批量的数据。通常打印机、扫描仪和数字相机以这种方式与主机连接。

硬件描述语言(Hardware Description Language,HDL)是一种编程语言,用软件方法对硬件的结构和运行进行建模。硬件描述语言是对硬件电路及其执行过程的描述,所以程序设计过程也叫电路建模过程。目前比较流行的逻辑设计的硬件描述语言是VHDL和Verilog HDL,VHDL是在1987年成为IEEE标准,Verilog HDL则在1995年才正式成为IEEE标准。VHDL其英文全名为VHSIC Hardware Description Language,VHSIC是Very High Speed Integerated Circuit的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言。

Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的结构和行为;支持逻辑设计中层次与模块的描述;可借用高级语言的精巧结构来简化电路的描述;具有电路仿真与验证机制以保证设计的正确性;支持电路描述由高层到低层的综合转换;硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去);便于文档管理、易于理解和设计重用。

但是Verilog HDL和VHDL又各有其自己的特点。由于Verilog HDL早在1983年就已推出,至今已有30多年的应用历史,因而Verilog HDL拥有更广泛的设计群体,成熟的资源也远比VHDL丰富。目前版本的Verilog HDL和VHDL在行为级抽象建模的覆盖范围方面也有所不同。一般认为Verilog HDL在系统级抽象方面比VHDL略差一些,而在门级开关电路描述方面比VHDL强得多。与VHDL相比,Verilog HDL的最大优点是:它是一种相对容易掌握的硬件描述语言,与C语言较接近,只要有C语言的编程基础,通过学习和实际操作,一般在较短时间内就可以掌握这种设计技术。而掌握VHDL设计技术相对困难一些。