在 Vivado 设计套件中,Vivado 综合可以综合不同类型的属性。在大多数情况下,这些属性具有相同的语法和相同的行为。

(1)如果Vivado综合支持该属性,它将使用该属性,并创建反映所使用属性的逻辑。

(2)如果工具无法识别指定的属性,Vivado综合会将该属性及其值传递给生成的网表。

如果流程中稍后的工具可以使用该属性。例如,LOC 约束不用于综合,但 Vivado 布局器使用该约束,并由Vivado综合转发。

ASYNC_REG 是一个影响 Vivado 工具流程中许多进程的属性。该属性的目的是通知工具,寄存器能够接收 D 输入引脚相对于源时钟的异步数据,或者说该寄存器是一个同步链上的同步寄存器。

Vivado 综合在遇到该属性时将其看作 DONT_TOUCH 属性,并在网表中向前推送ASYNC_REG 属性。这个过程确保带有 AYNC_REG 属性的对象不会被优化,并且流程之后的工具会接收该属性以正确处理它。

设计人员可以将该属性放置在任何寄存器上,其值为 FALSE(默认)或者 TRUE。该属性可以在RTL或XDC中设置。

注: 在无负载的信号上设置该属性时要小心。属性和信号可能不会被保留。

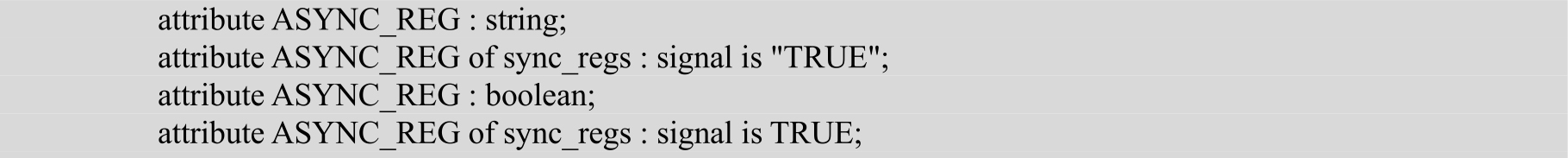

ASYNC_REG属性的Verilog HDL和VHDL描述例子如代码清单2-4和代码清单2-5所示。

代码清单2-4 ASYNC_REG属性的Verilog HDL描述例子

代码清单2-5 ASYNC_REG属性的VHDL描述例子

BLACK_BOX 是一个非常有用的调试属性,它指导综合为该模块或者实体创建一个黑盒。当找到属性时,即使模块或实体有有效的逻辑,Vivado综合也会为该级创建一个黑盒。该属性可以放置在一个模块、实体或者元件上。由于该属性影响综合编译器,所有只能在RTL级上设置。

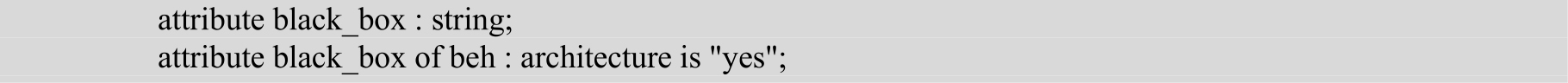

BLACK_BOX属性的Verilog HDL和VHDL描述例子如代码清单2-6和代码清单2-7所示。

代码清单2-6 BLACK_BOX属性的Verilog HDL描述例子

代码清单2-7 BLACK_BOX属性的Verilog HDL描述例子

注: 在Verilog描述中,不需要任何值。该属性的存在会创建黑盒。

CASCADE_HEIGHT属性是一个整数,用于描述放入BRAM的大型RAM级联链的长度。当描述的 RAM 大于单个 BRAM 时,Vivado 综合工具必须确定如何配置,通常 Vivado 综合工具会选择级联其创建的BRAM。CASCADE_HEIGHT属性可用于缩短链的长度,其防止在有问题的RAM上,设计人员可以在RTL文件中放置该属性。该属性的值为0或1时,可有效关闭BRAM的任何级联。

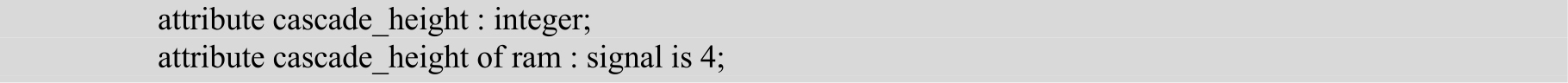

CASCADE_HEIGHT 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-8 和代码清单2-9所示。

代码清单2-8 CASCADE_HEIGHT属性的Verilog HDL描述例子

代码清单2-9 CASCADE_HEIGHT属性的VHDL描述例子

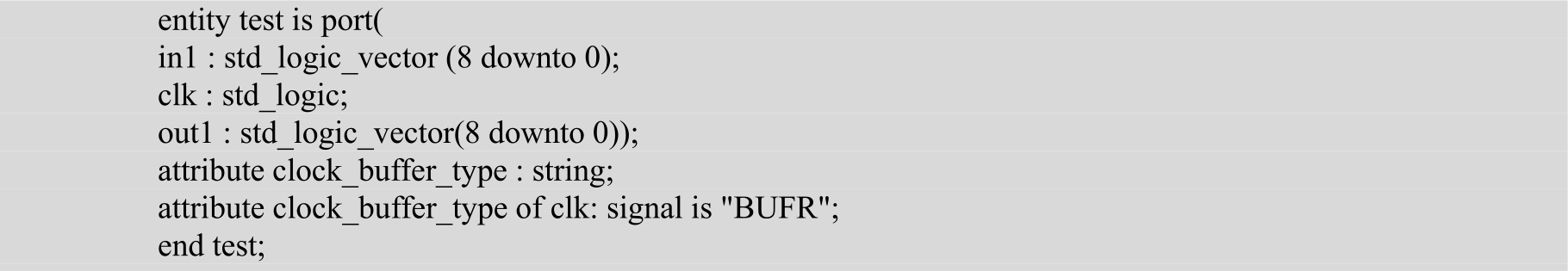

在输入时钟上应用CLOCK_BUFFER_TYPE来描述要使用的时钟缓冲区类型。Vivado综合默认使用 BUFG 作为时钟缓冲区。支持的值有 BUFG、BUFH、BUFIO、BUFMR、BUFR 或NONE。CLOCK_BUFFER_TYPE 属性可以放在任何顶层时钟端口上,可以在 RTL 或 XDC 中设置该属性。

CLOCK_BUFFER_TYPE属性的Verilog HDL和VHDL描述例子如代码清单2-10和代码清单2-11所示,该属性在XDC中描述的例子如代码清单2-12所示。

代码清单2-10 CLOCK_BUFFER_TYPE属性的Verilog HDL描述例子

代码清单2-11 CLOCK_BUFFER_TYPE属性的VHDL描述例子

代码清单2-12 CLOCK_BUFFER_TYPE属性在XDC中描述的例子

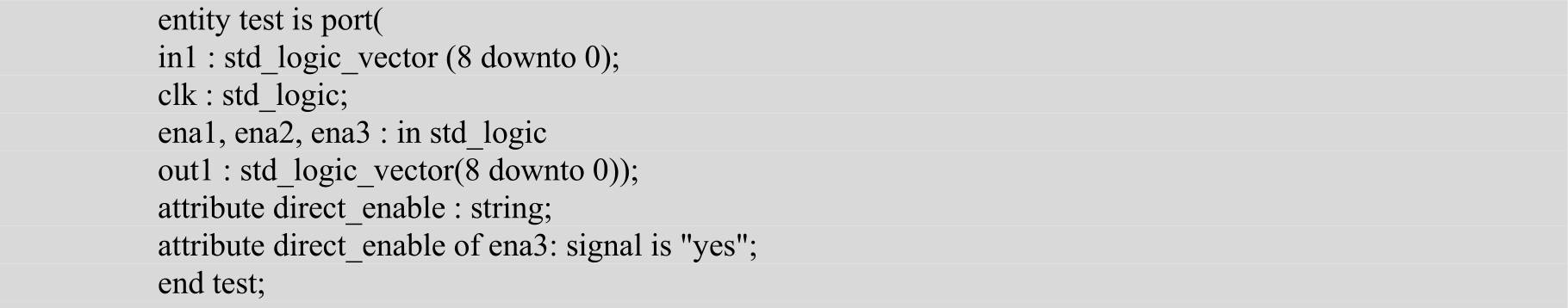

在输入端口或其他信号上应用 DIRECT_ENABLE 属性,使其在有多个可能的使能时,或当设计人员想强制综合工具使用触发器的使能线时,直接进入触发器的使能线。DIRECT_ENABLE属性可以放置在任何端口或信号上。

DIRECT_ENABLE 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-13 和代码清单2-14所示,该属性在XDC中描述的例子如代码清单2-15所示。

代码清单2-13 DIRECT_ENABLE属性的Verilog HDL描述例子

代码清单2-14 DIRECT_ENABLE属性的VHDL描述例子

代码清单2-15 DIRECT_ENABLE属性在XDC中描述的例子

注: 当 DIRECT_ENABLE 属性在 XDC 中使用时,由于该属性仅用于类型 net,因此必须对对象使用get_nets命令。

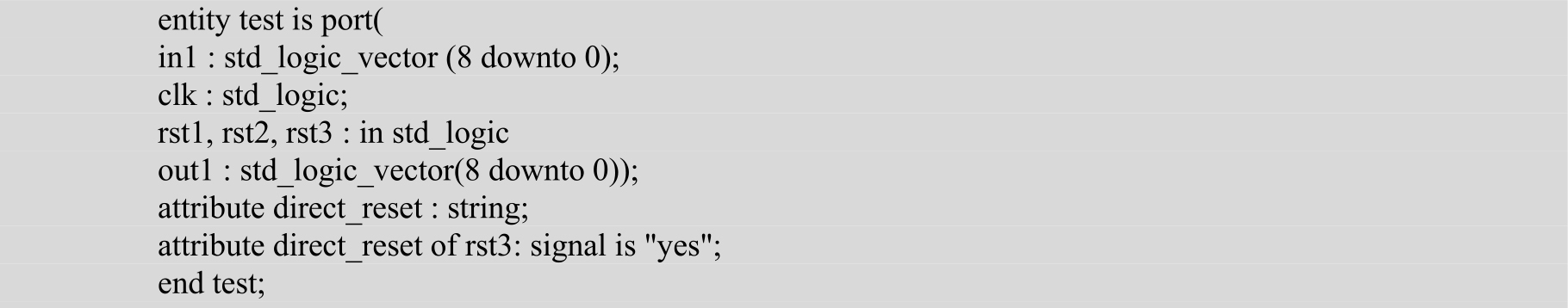

在输入端口或其他信号上应用 DIRECT_RESET 属性,使其在有多个可能的复位时,或当设计人员想强制综合工具使用触发器的复位线时,直接进入触发器的复位线。DIRECT_RESET属性可以放置在任何端口或信号上。

DIRECT_RESET属性的Verilog HDL和VHDL描述例子如代码清单2-16和代码清单2-17所示,该属性在XDC中描述的例子如代码清单2-18所示。

代码清单2-16 DIRECT_RESET属性的Verilog HDL描述例子

代码清单2-17 DIRECT_RESET属性的VHDL描述例子

代码清单2-18 DIRECT_RESET属性在XDC中描述的例子

注: 当 DIRECT_RESET 属性在 XDC 中使用时,由于该属性仅用于类型 net,因此必须对对象使用get_nets命令。

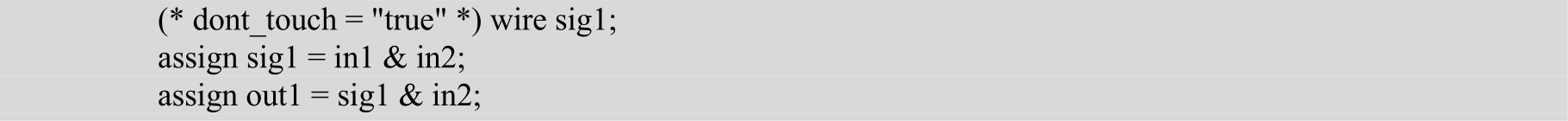

使用DONT_TOUCH属性代替KEEP或者KEEP_HIERARCHY,DONT_TOUCH属性的工作方式与KEEP或KEEP_HIERARCHY属性相同。但是,与KEEP和KEEP_HIERARCHY属性不同的是,DONT_TOUCH属性向前注解到布局和布线,以阻止逻辑优化。

注: 与 KEEP 和 KEEP_HIERARCHY 属性类似,使用 DONT_TOUCH 属性时要小心。如果其他属性与DONT_TOUCH属性冲突,则DONT_TOUCH属性优先。

DONT_TOUCH属性的值为TRUE/FALSE或yes/no。该属性可以放置在任何信号、模块、实体或者元件上。

注: 模块或实体的端口不支持 DONT_TOUCH 属性。如果需要保留特定的端口,请使用-flatten_hierarchy none设置,或者将DONT_TOUCH属性放置在模块/实体本身。

通常,DONT_TOUCH 属性仅在 RTL 中设置。需要保留的信号通常可以在读取 XDC 文件之前进行优化。因此,在 RTL 中设置该属性可确保使用该属性。有一个示例建议在 XDC 文件中设置 DONT_TOUCH 属性,即当 DONT_TOUCH 属性在 RTL 中设置为 yes 时,并且希望在不更改RTL 的情况下取出。在这种情况下,当同一信号的DONT_TOUCH 属性在 RTL 中设置为yes时,在XDC中将DONT_TOUCH属性设置为no将有效删除该属性,而不必更改RTL。

注: 当使用XDC删除RTL中设置的DONT_TOUCH属性时,当实现流程读取相同的XDC但有问题的信号已被优化时,设计人员可能会在综合后收到警告。这些警告可以忽略。但是,设计人员也可以通过将DONT_TOUCH属性放在标记为仅用于综合的XDC文件中来绕过它们。

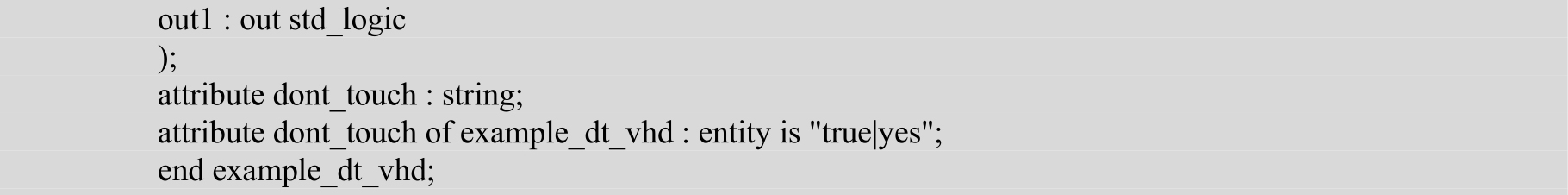

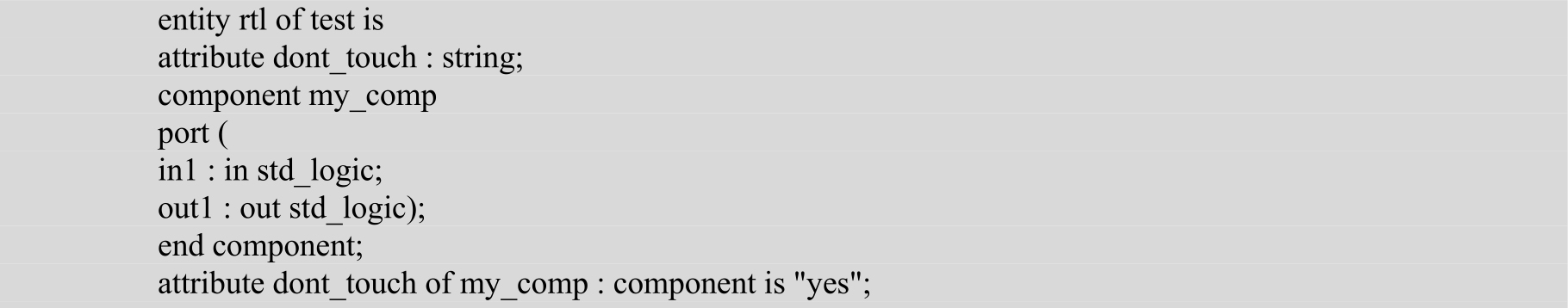

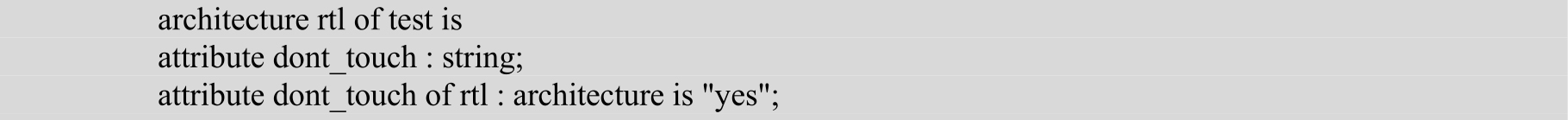

DONT_TOUCH属性的Verilog HDL 和 VHDL 描述例子如代码清单2-19~代码清单2-25所示。

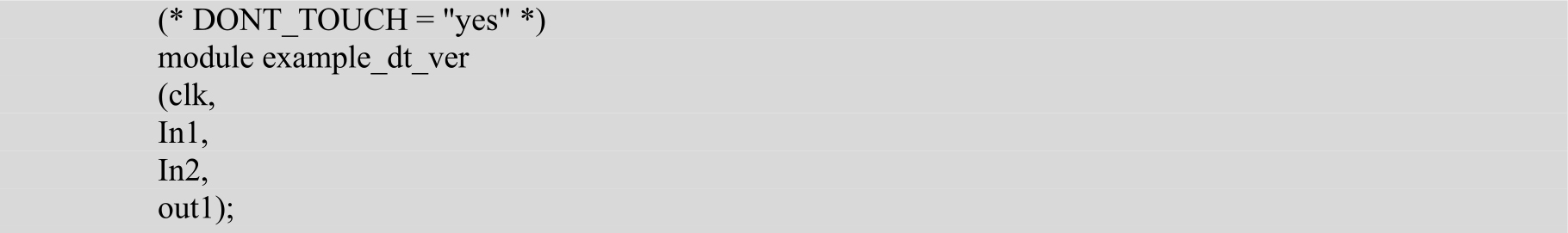

代码清单2-19 DONT_TOUCH属性应用于wire类型的Verilog HDL描述例子

代码清单2-20 DONT_TOUCH属性应用于module的Verilog HDL描述例子

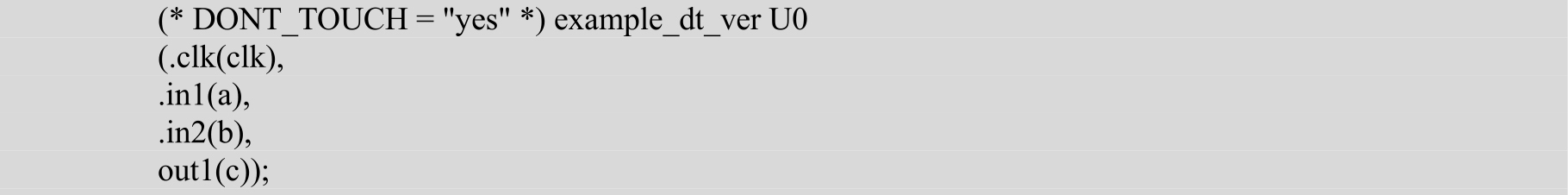

代码清单2-21 DONT_TOUCH属性应用于实例的Verilog HDL描述例子

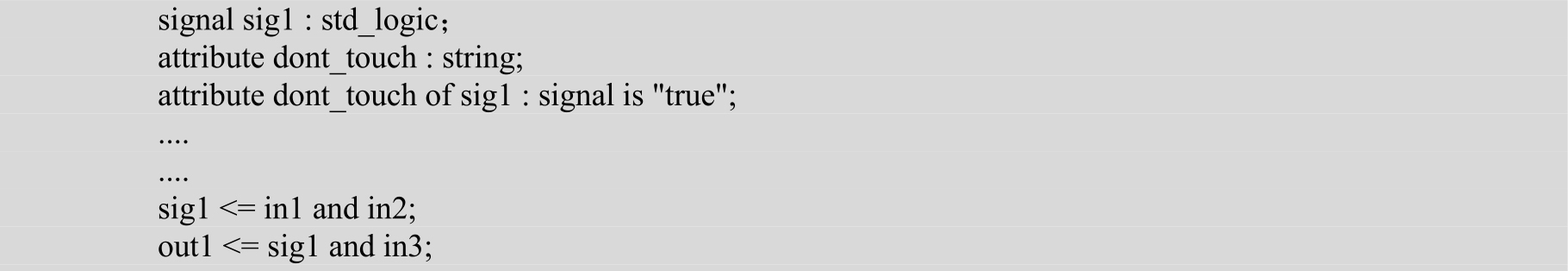

代码清单2-22 DONT_TOUCH属性应用于signal的VHDL描述例子

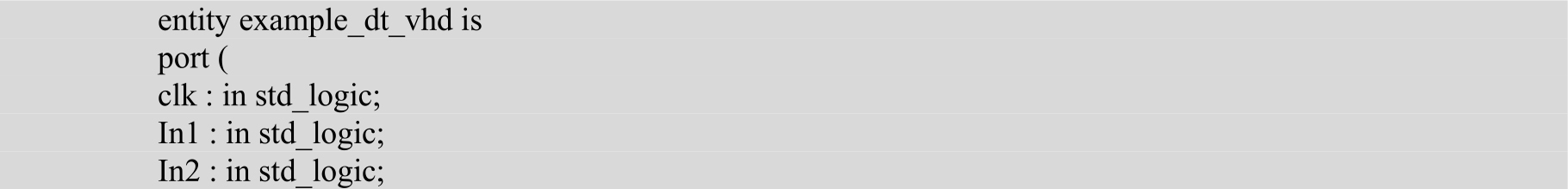

代码清单2-23 DONT_TOUCH属性应用于entity的VHDL描述例子

代码清单2-24 DONT_TOUCH属性应用于component的VHDL描述例子

代码清单2-25 DONT_TOUCH属性应用于architecture的VHDL描述例子

DSP_FOLDING属性控制Vivado综合是否将与一个加法器连接的两个MAC结构折叠为一个DSP原语。DSP_FOLDING属性的值为:

(1)“yes”:工具将转换MAC结构。

(2)“no”:工具将不会转换MAC结构。

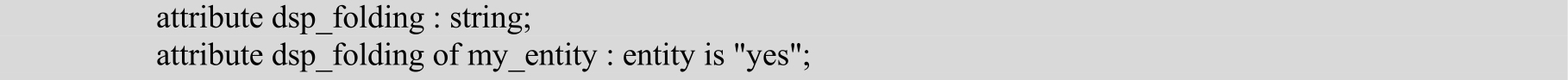

仅RTL支持DSP_FOLDING属性,它应该放在将包含MAC结构的逻辑模块/实体/结构体上。

DSP_FOLDING属性的Verilog HDL和VHDL描述例子如代码清单2-26和代码清单2-27所示。

代码清单2-26 DSP_FOLDING属性的Verilog HDL描述例子

代码清单2-27 DSP_FOLDING属性的VHDL描述例子

DSP_FOLDING_FASTCLOCK 属性告诉工具在使用 DSP 折叠时,哪个端口应成为新的更快时钟。DSP_FOLDING_FASTCLOCK属性的值为:

(1)“yes”:工具将使用该端口作为连接新时钟的端口。

(2)“no”:工具将不会使用该端口。

仅RTL支持DSP_FOLDING_FASTCLOCK属性,仅将该属性放置在端口或引脚上。

DSP_FOLDING_FASTCLOCK属性的Verilog HDL和VHDL描述例子如代码清单2-28和代码清单2-29所示。

代码清单2-28 DSP_FOLDING_FASTCLOCK属性的Verilog HDL描述例子

代码清单2-29 DSP_FOLDING_FASTCLOCK属性的VHDL描述例子

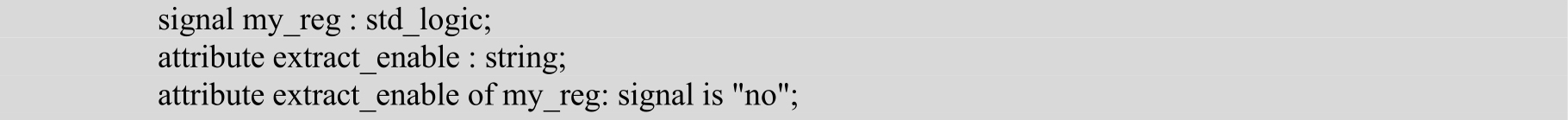

EXTRACT_ENABLE属性控制是否使能寄存器推断。通常,Vivado工具提取或不提取基于启发法的使能,这些启发法通常有利于大多数的设计。如果Vivado的行为不符合要求,则该属性将覆盖工具的默认行为。

如果触发器的 CE 引脚有一个不需要的使能,则该属性将其强制到 D 输入逻辑。相反,如果工具没有推断RTL中指定的使能,则该属性告诉工具将该使能移动到触发器的CE引脚。

如果将 EXTRACT_ENABLE 属性放置在寄存器上,且在 RTL 和 XDC 中受支持,那么它可以采用的布尔值为yes或no。

EXTRACT_ENABLE 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-30 和代码清单2-31所示,该属性在XDC中描述的例子如代码清单2-32所示。

代码清单2-30 EXTRACT_ENABLE属性的Verilog HDL描述例子

代码清单2-31 EXTRACT_ENABLE属性的VHDL描述例子

代码清单2-32 EXTRACT_ENABLE属性在XDC中描述的例子

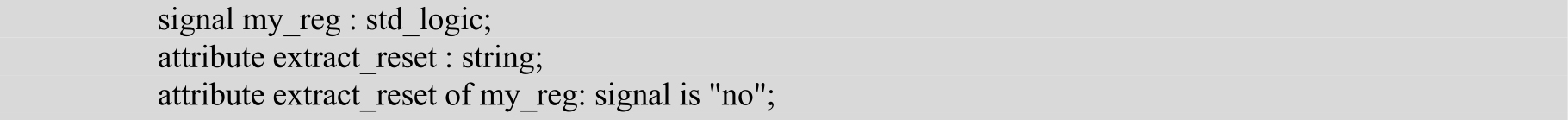

EXTRACT_RESET 属性控制是否推断寄存器复位。通常,Vivado 工具基于启发法提取或不提取复位,这些启发法通常有利于大多数的设计。如果Vivado的行为不符合要求,则该属性将覆盖工具的默认行为。

如果有一个不希望的同步复位进入触发器,则 EXTRACT_RESET 属性将其强制到 D 输入逻辑。相反,如果工具没有推断 RTL 中指定的复位,则 EXTRACT_RESET 属性告诉工具将该复位移动到触发器的专用复位。EXTRACT_RESET属性只能与同步复位一起使用,其不支持异步复位。

如果将 EXTRACT_ENABLE 属性放置在寄存器上,且在 RTL 和 XDC 中受支持,那么它可以采用的布尔值为 yes 或 no。值 no 表示复位不会到达寄存器的 R 引脚,而是通过逻辑布线到寄存器的D引脚;值yes表示复位将直接进入寄存器的R引脚。

EXTRACT_RESET 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-33 和代码清单2-34所示,该属性在XDC中描述的例子如代码清单2-35所示。

代码清单2-33 EXTRACT_RESET属性的Verilog HDL描述例子

代码清单2-34 EXTRACT_RESET属性的VHDL描述例子

代码清单2-35 EXTRACT_RESET属性在XDC中描述的例子

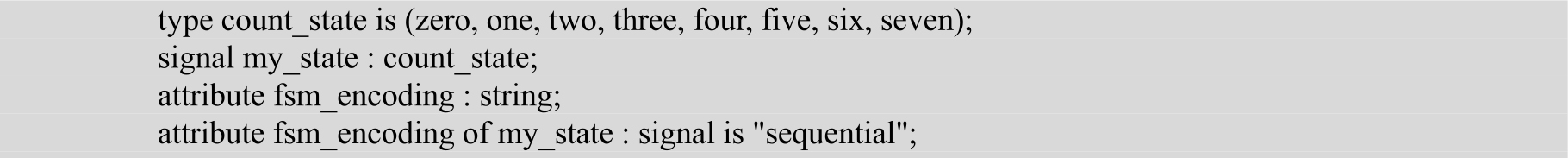

FSM_ENCODING 属性用于控制状态机上的编码。通常,Vivado 工具基于启发式算法为状态机选择一个编码协议,这种算法对大多数设计都是最好的。

FSM_ENCODING 属性可以放置在状态寄存器上,其合法的值为 one_hot、sequential、johnson、gray、user_encoding 和 none。auto 值是默认值,允许工具确定其最佳编码;user_encoding值告诉工具仍然可以推断状态机,但使用用户在RTL中给定的编码。可以在RTL或者XDC中设置FSM_ENCODING属性。

FSM_ENCODING属性的 Verilog HDL和 VHDL 描述例子如代码清单 2-36 和代码清单2-37所示。

代码清单2-36 FSM_ENCODING属性的Verilog HDL描述例子

代码清单2-37 FSM_ENCODING属性的VHDL描述例子

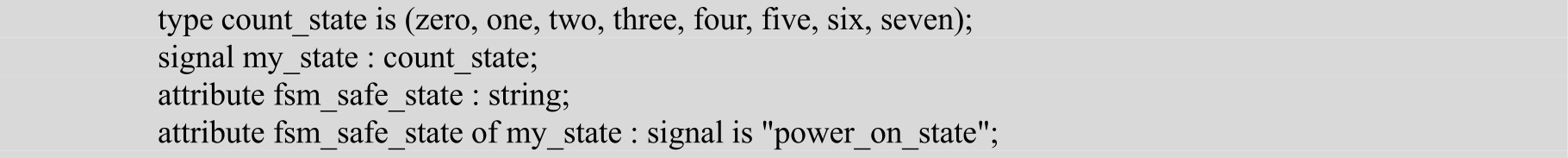

FSM_SAFE_STATE 属性指示 Vivado 综合将逻辑插入检测到非法状态的状态机中。当下一个时钟周期到来时,将其置为一个已知的良好状态。

例如,如果一个状态机具有one_hot编码,并且处于0101状态(对于one_hot来说这是非法的),则状态机应该能够恢复。该属性可放置在状态机寄存器上。设计人员可以在 RTL 或XDC中设置该属性。

FSM_SAFE_STATE的合法值如下所示。

(1)auto_safe_state:使用Hamming-3编码对一位/翻转进行自动校正。

(2)reset_state:使用Hamming-2编码对一位/翻转检测,强制状态机进入复位状态。

(3)power_on_state:使用Hamming-2编码对一位/翻转检测,强制状态机进入上电状态。

(4)default_state:强制状态机进入 RTL 中指定的默认状态,即 Verilog 中 case 语句的default 分支中指定的状态或 VHDL 中 case 语句 others 分支中指定的状态。要使其工作,RTL中必须要有default状态或others状态。

FSM_SAFE_STATE属性的Verilog HDL和VHDL描述例子如代码清单2-38和代码清单2-39所示。

代码清单2-38 FSM_SAFE_STATE属性的Verilog HDL描述例子

代码清单2-39 FSM_SAFE_STATE属性的VHDL描述例子

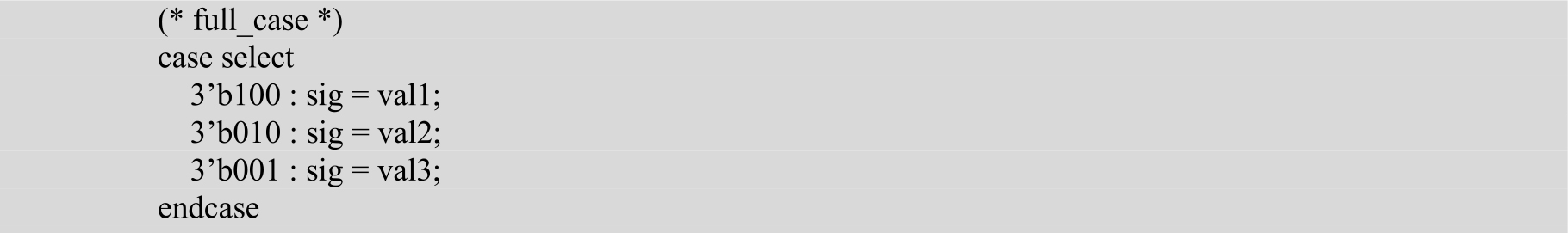

FULL_CASE属性表示在case、casex或者casez语句中指定了所有可能情况的取值。如果指定了 case 的值,Vivado 综合工具则不能创建额外的逻辑用于 case 值。FULL_CASE 属性放置在case语句中,该属性的Verilog HDL描述如代码清单2-40所示。

代码清单2-40 FULL_CASE属性的Verilog HDL描述例子

注: 由于 FULL_CASE 属性影响编译器,可以改变设计的逻辑行为,因此只能在 RTL中设置。

Vivado综合允许门控时钟的转换。要执行该转换,请使用:

(1)Vivado GUI的开关,用于指导工具尝试转换。

(2)RTL属性指导工具,用于确认在门控逻辑中指示哪个信号是时钟。

将 GATED_CLOCK 属性放置在作为时钟的信号或端口上,要控制开关,则应按照下述步骤进行操作。

(1)在 Vivado 2023.1 IDE 工程界面左侧 Flow Navigator 窗口中,找到并用鼠标右键单击SYNTHESIS,出现浮动菜单。在浮动菜单中,执行菜单命令【Synthesis Settings】。

(2)在弹出的“Settings”对话框中找到名字为“Settings”的标题窗口。

(3)在Settings窗口中,找到并展开“Synth Design(vivado)”。

(4)在展开项中,找到“-gated_clock_conversion”条目。通过该条目右侧的下拉框,将该条目的值设置为off、on和auto。下面对这三个值的含义进行简要说明。

① off:禁止门控时钟转换。

② on:如果在 RTL 代码中设置了 GATED_CLOCK 属性,则发生门控时钟转换。该选项使得设计人员能更好地控制结果。

③ auto:如果发生下面事件,则进行转换。

● GATED_CLOCK属性设置为true。

● Vivado综合可以检测到门,并且存在有效的时钟约束集。

注: 使用 KEEP_HIERARCHY、DONT_TOUCH 和 MARK_DEBUG 属性时要小心。如果将这些属性放置在需要更改以支持转换的层次结构或实例上,则这些属性可能会干扰门控时钟的转换。

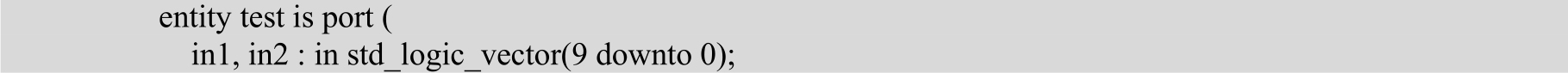

GATED_CLOCK属性的Verilog HDL和VHDL描述例子如代码清单2-41和代码清单2-42所示。

代码清单2-41 GATED_CLOCK属性的Verilog HDL描述例子

代码清单2-42 GATED_CLOCK属性的VHDL描述例子

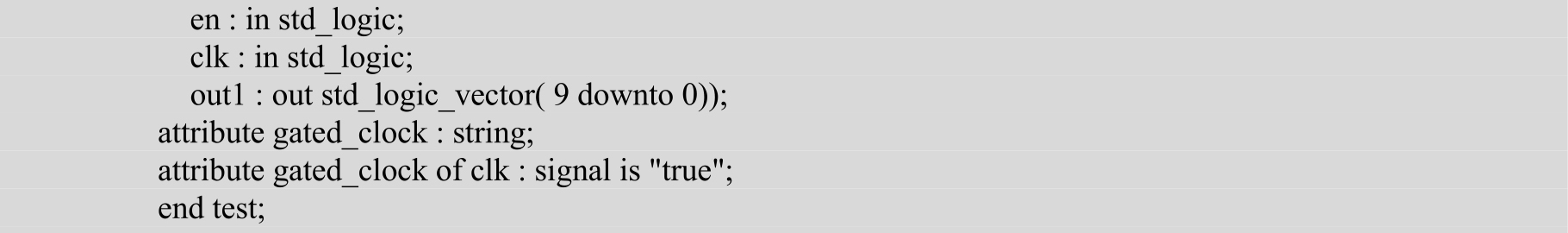

IOB 属性控制寄存器是否应进入 I/O 缓冲区,它的值为 TRUE 或 FALSE。将该属性放在I/O缓冲区所需要的寄存器上。该属性只能在RTL中设置。

IOB属性的Verilog HDL和VHDL描述例子如代码清单2-43和代码清单2-44所示。

代码清单2-43 IOB属性的Verilog HDL描述例子

代码清单2-44 IOB属性的VHDL描述例子

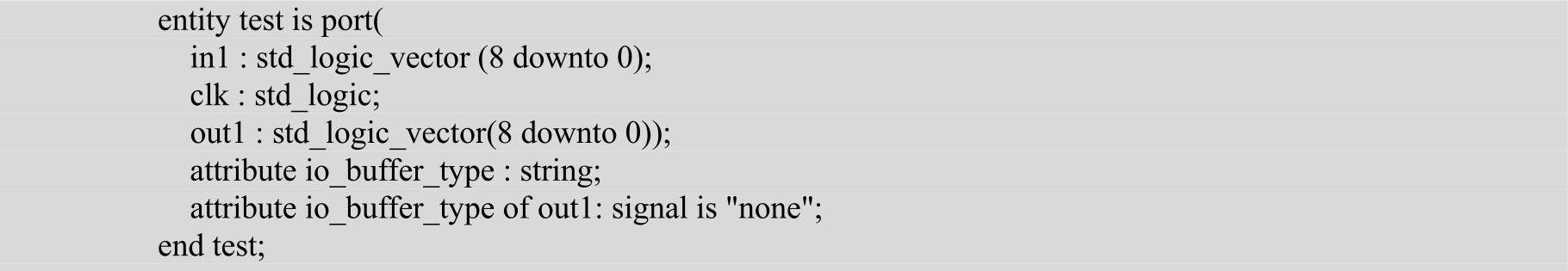

将 IO_BUFFER_TYPE 属性应用于任何顶层端口以指示工具使用缓冲区。添加值为 NONE的属性将禁止输入或输出缓冲区上缓冲区的自动推断,这是 Vivado 综合的默认行为。IO_BUFFER_TYPE属性仅支持和设置在RTL中。

IO_BUFFER_TYPE属性的 Verilog HDL和 VHDL描述例子如代码清单2-45和代码清单2-46所示。

代码清单2-45 IOB_BUFFER_TYPE属性的Verilog HDL描述例子

代码清单2-46 IOB_BUFFER_TYPE属性的VHDL描述例子

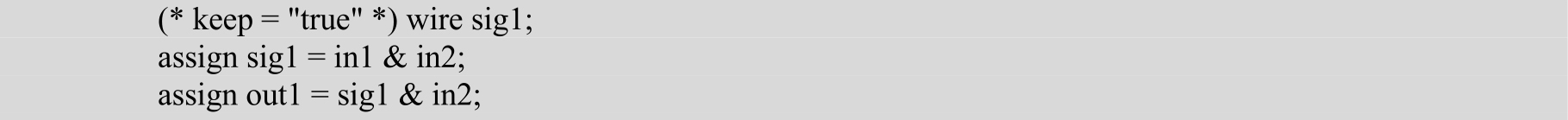

KEEP 属性可以阻止信号被优化或吸收到逻辑块中,该属性指示综合工具保留其放置的信号,并且该信号被放置在网表中。

例如,如果一个信号是两输入的逻辑“与”门输出,并且它驱动另一个逻辑“与”门,则KEEP属性可用于阻止该信号合并到包含两个逻辑“与”门的较大LUT中。

注: 将 KEEP 与其他属性一起使用时要小心。在其他属性与 KEEP 属性冲突的情况下,KEEP属性通常优先。

KEEP 属性也通常与时序约束结合使用。如果信号上存在通常会优化的时序约束,KEEP属性会阻止这种情况,并允许使用正确的时序规则。

注: (1)模块或实体的端口不支持KEEP属性。如果需要保留特定的端口,请使用-flatten_herarchy none设置,或者在模块或实体本身上放置DONT_TOUCH属性。

(2)在无负载信号上使用 KEEP 属性时要小心。综合将保留这些信号,这些信号将在流程的后期产生问题。

例如:

(1)当一个信号具有 MAX_FANOUT 属性,而由第一个信号驱动的第二个信号具有 KEEP属性时,第二个信号上的KEEP属性不允许扇出复制。

(2)对于RAM_STYLE=“block”,当寄存器上有一个KEEP需要成为RAM的一部分时,KEEP属性可防止推断BRAM。

支持的 KEEP 值为 TRUE 时,表示保持信号;值为 FALSE 时,允许 Vivado 综合进行优化,此时不会强制工具删除信号。默认值为FALSE。

KEEP属性可以放置在signal、reg或者wire上。Xilinx建议仅在RTL中设置该属性。由于需要保留的信号通常在XDC文件之前进行了优化,因此在RTL中设置该属性可以确保使用该属性。

注: KEEP 属性不强迫布局和布线工具保持该信号。在这种情况下,使用 DONT_TOUCH属性。

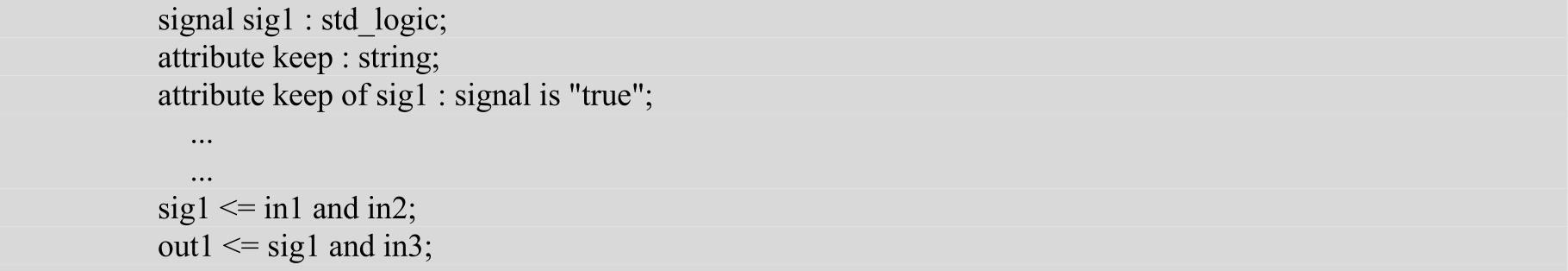

KEEP属性的Verilog HDL和VHDL描述例子如代码清单2-47和代码清单2-48所示。

代码清单2-47 KEEP属性的Verilog HDL描述例子

代码清单2-48 KEEP属性的VHDL描述例子

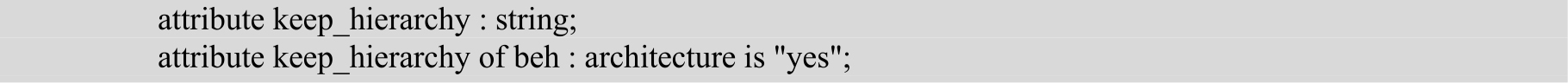

KEEP_HIERARCHY 属性用于阻止在层次边界的优化。如果在实例上放置了 KEEP_HIERARCHY 属性,综合工具将保持静态级的逻辑层次。这可能会影响 QoR,也不能用于那些描述三态输出和 I/O 缓冲区控制逻辑的模块。KEEP_HIERARCHY 属性可以放置在模块或结构体级,或实例中。如果在XDC中使用它,那么它只能放在实例上。

KEEP_HIERARCHY 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-49~代码清单2-51所示。在XDC的实例上使用该属性的描述例子如代码清单2-52所示。

代码清单2-49 在模块上使用KEEP_HIERARCHY属性的Verilog HDL描述例子

代码清单2-50 在实例上使用KEEP_HIERARCHY属性的Verilog HDL描述例子

代码清单2-51 在结构体上使用KEEP_HIERARCHY属性的VHDL描述例子

代码清单2-52 在XDC的实例上使用KEEP_HIERARCHY属性的描述例子

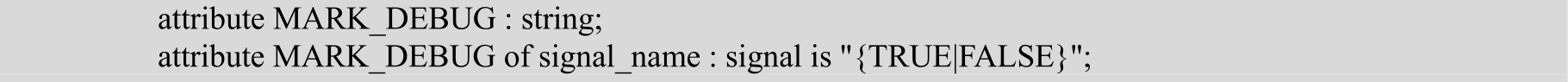

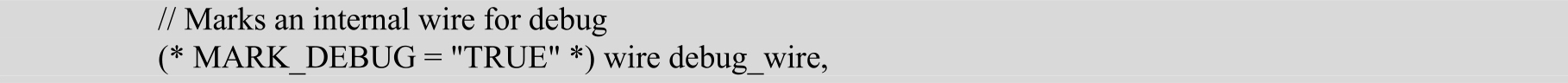

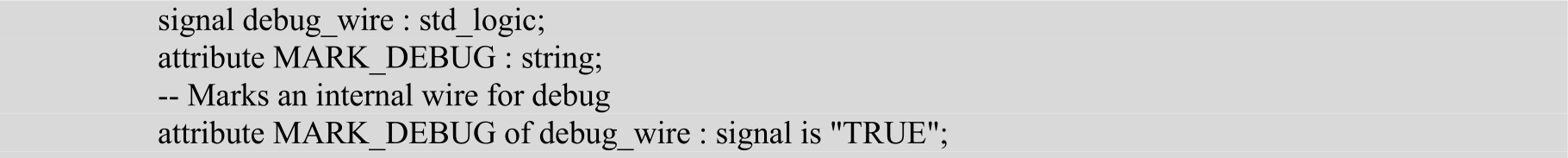

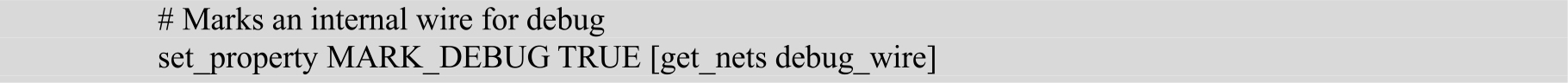

MARK_DEBUG 属性适用于网络对象。一些网络可以具有专用连接或其他方面,这些方面禁止用于调试目的的可见性。MARK_DEBUG属性的值为TRUE或FALSE。

(1)要设置该属性,请在有问题的信号上放置正确的Verilog HDL属性:

(*MARK_DEBUG="{TRUE|FALSE}"*)

(2)要设置该属性,请在有问题的信号上放置正确的VHDL属性:

其中,signal_name为内部信号。

(3)在XDC中设计该属性的格式如下:

其中,<net_name>为信号的名字。

MARK_DEBUG属性的Verilog HDL和VHDL描述例子如代码清单2-53和代码清单2-54所示,该属性在XDC中的描述例子如代码清单2-55所示。

代码清单2-53 MARK_DEBUG属性的Verilog HDL描述例子

代码清单2-54 MARK_DEBUG属性的VHDL描述例子

代码清单2-55 MARK_DEBUG属性在XDC中的描述例子

通常,MARK_DEBUG 属性的使用是在层次结构的引脚上进行的,并且可以用于任何详细描述的时序元素,如 RTL_REG。当 MARK_DEBUG 属性用于网络时,建议同时使用get_nets和get_pins命令。例如:

这种建议的使用可以确保MARK_DEBUG属性进入连接该引脚的网络,与名字无关。

注: 如果将 MARK_DEBUG 属性应用于声明为 bit_vector 的信号位,则整个总线将获得MARK_DEBUG 属性。此外,如果将 MARK_DEBUG 属性放置在层次结构的引脚上,则将保留完整的层次结构。

MAX_FANOUT 属性指示 Vivado 对寄存器和信号的扇出进行限制,可以在 RTL 中指定或将其作为工程的输入。MAX_FANOUT 属性的值为一个整数,且该属性只能用于寄存器和组合信号。该属性只能在RT L中设置。

注: (1)不支持输入、黑盒、EDIF和本原通用电路(Native Generic Circuit,NGC)文件。

(2)针对UltraScale器件的Vivado设计套件不支持NGC格式的文件。建议使用Vivado设计套件 IP 定制工具和本原输出产品重新生成 IP。或者设计人员也可以使用 NGC2EDIF 命令将NGC 文件转换为 EDIG 格式以进行导入。然而,Xilinx 建议今后使用本原 Vivado IP,而不是XST生成的NGC格式文件。

在全局高扇出信号上使用 MAX_FANOUT 属性会导致综合中的次优化复制。因此,Xilinx建议仅在具有低扇出的本地信号的层次结构中使用MAX_FANOUT属性。

MAX_FANOUT属性的Verilog HDL和VHDL描述例子如代码清单2-56和代码清单2-57所示。

代码清单2-56 MAX_FANOUT属性的Verilog HDL描述例子

代码清单2-57 MAX_FANOUT属性的VHDL描述例子

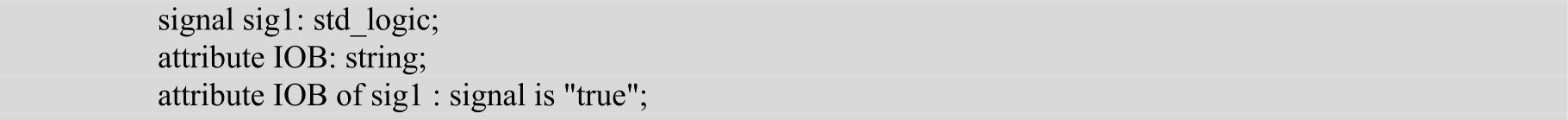

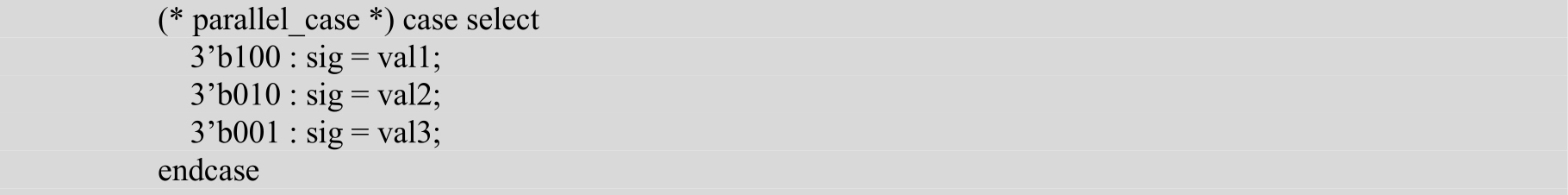

PARALLEL_CASE 属性指定 case 语句必须构建为并行结构。逻辑不是为 if-elsif 结构创建的。由于该属性会影响编译器和设计的逻辑行为,因此只能在 RTL 中设置。该属性的 Verilog HDL描述例子如代码清单2-58所示。

代码清单2-58 PARALLEL_CASE属性的Verilog HDL描述例子

注: 该属性只能通过Verilog HDL的RTL进行控制。

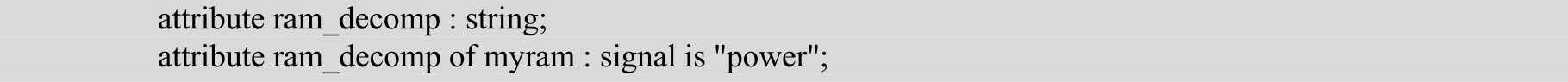

RAM_DECOMP属性指示该工具推断RTL RAM太大,无法适配到单个BRAM原语,从而使用更省电的配置。例如,指定为2K×36的RAM通常被配置为并排排列的两个2K×18 BRAM,这是产生最快设计的配置。通过设置RAM_DECOMP属性,RAM将被配置为2个1K×36 BRAM,这对电源更友好,因为在读或写过程中,只有一个使用地址的RAM是活动的。RAM_DECOMP是以时序为代价的,因为Vivado综合必须使用地址译码。RAM_DECOMP属性将强制执行该 RAM的第二种配置。

RAM_DECOMP属性可接受的值为power。该属性可以在RTL或XDC中设置。将属性放在RAM实例本身上。

RAM_DECOMP属性的Verilog HDL和VHDL描述例子如代码清单2-59和代码清单2-60所示,该属性在XDC中的描述的例子如代码清单2-61所示。

代码清单2-59 RAM_DECOMP属性的Verilog HDL描述例子

代码清单2-60 RAM_DECOMP属性的VHDL描述例子

代码清单2-61 RAM_DECOMP属性在XDC中的描述的例子

RAM_STYLE属性指示Vivado综合工具如何推断存储器。可接受的值为:

(1)block:指示Vivado综合工具推断BRAM类型元件。

(2)distributed:指示Vivado综合工具推断LUT RAM。

(3)registers:指示Vivado综合工具推断寄存器而不是RAM。

(4)ultra:指示Vivado综合工具使用UltraScale URAM原语。

(5)mixed:指示 Vivado 综合工具推断 RAM 类型的组合,以最大限度地减少未使用的空间量。

(6)auto:让 Vivado 综合工具决定如何实现 RAM。这与默认行为相同。该值的主要用途是XPM必须为RAM_STYLE选择一个值。

默认情况下,Vivado 综合工具选择启发法选择要推断的 RAM,这些启发法为大多数设计提供了最佳结果。将RAM_STYPE属性放在RAM或层次结构级别上。

(1)如果在信号上设置,则该属性将影响该特定信号;

(2)如果设置在一个层次级别上,则会影响该层次级别中的所有 RAM。层次结构的子级不受影响。

可以在RTL或XDC中设置RAM_STYPE属性。

RAM_STYPE属性的Verilog HDL和VHDL描述例子如代码清单2-62和代码清单2-63所示。

代码清单2-62 RAM_STYPE属性的Verilog HDL描述例子

代码清单2-63 RAM_STYPE属性的VHDL描述例子

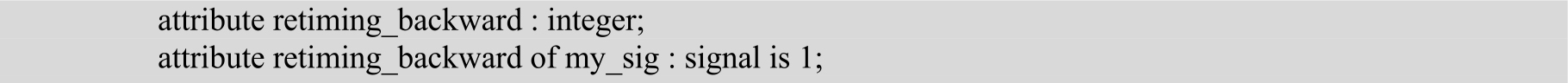

RETIMING_BACKWARD 属性指示工具通过将寄存器向后移动,使其更靠近受驱动的顺序元件。与重定时全局设置不同,该属性不是时序驱动并且将起作用,无论重定时全局设置是否处于活动状态或者是否存在时序约束。如果全局重定时设置处于活动状态,则RETIMING_BACKWARD 步骤将首先发生,然后全局重定时可以增强该寄存器以进一步向后移动链,但不会干扰属性并将寄存器移回其原始位置。

注: 具有 DONT_TOUCH/MATK_DEBUG 属性的单元,带有时序例外(false_path,multicycle_path)的单元,以及用户例化单元,将阻止该属性。

RETIMING_BACKWARD属性的Verilog HDL和VHDL描述例子如代码清单2-64和代码清单2-65所示,该属性在XDC中描述的例子如代码清单2-66所示。

代码清单2-64 RETIMING_BACKWARD属性的Verilog HDL描述例子

代码清单2-65 RETIMING_BACKWARD属性的VHDL描述例子

代码清单2-66 RETIMING_BACKWARD属性在XDC中描述的例子

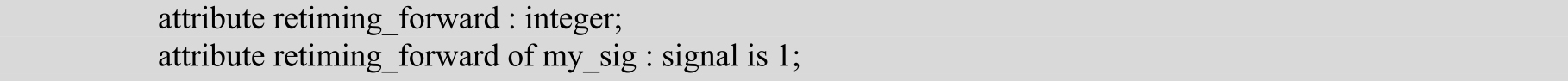

RETIMING_FORWARD 属性指示工具通过将寄存器向前移动,使其更靠近受驱动的顺序元件。与重定时全局设置不同,该属性不是时序驱动并且将起作用,无论重定时全局设置是否处于活动状态或者是否存在时序约束。如果全局重定时设置处于活动状态,则 RETIMING_FORWARD 步骤将首先发生,然后全局重定时可以增强该寄存器以进一步移动,但不会干扰属性将寄存器移回其原始位置。

注: 具有 DONT_TOUCH/MATK_DEBUG 属性的单元,带有时序例外(false_path,multicycle_path)的单元,以及用户例化单元,将阻止该属性。

RETIMING_FORWARD 属性采用一个整数作为值,该值描述了允许寄存器跨越的逻辑数量。较大的值将允许寄存器跨越更多的逻辑。值为0时,将关闭属性。

RETIMING_FORWARD属性的Verilog HDL和VHDL描述例子如代码清单2-67和代码清单2-68所示,该属性在XDC中描述的例子如代码清单2-69所示。

代码清单2-67 RETIMING_FORWARD属性的Verilog HDL描述例子

代码清单2-68 RETIMING_FORWARD属性的VHDL描述例子

代码清单2-69 RETIMING_FORWARD属性在XDC中描述的例子

ROM_STYLE属性指导Vivado综合工具如何将常数数组推断为BRAM等存储器结构,可接受的值为:

(1)block:指示Vivado综合工具推断BRAM类型的元件。

(2)distributed:指示Vivado综合工具推断LUT ROM。指示Vivado综合工具将常数数组推断为分布式 RAM(LUTRAM)资源。默认情况下,Vivado 综合工具根据启发法选择要推断的ROM,这些启发法为大多数设计提供了最佳结果。

(3)ultra:指导Vivado综合工具使用URAM原语(仅限于Versal ACAP器件)。

可以在RTL和XDC中设置该属性,该属性的Verilog HDL和VHDL描述例子如代码清单2-70和代码清单2-71所示。

代码清单2-70 ROM_STYLE属性的Verilog HDL描述例子

代码清单2-71 ROM_STYLE属性的VHDL描述例子

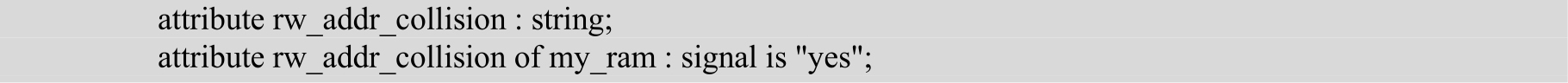

RW_ADDR_COLLISION属性用于特定类型的RAM。当RAM是一个简单的双端口并且读地址已寄存时,Vivado综合工具将推断出BRAM,并且将写入模式设置为WRITE_FIRST以获得最佳时序。此外,如果一个设计写入与其正在读取的地址相同的地址,则 RAM 的输出是不可预测的。RW_ADDR_COLLISION覆盖该行为。RW_ADDR_COLLISION的值为:

(1)auto:如上描述的默认行为。

(2)yes:插入了旁路逻辑,这样当在同一时间从写入地址读取时,将在输出看到输入的值,从而使整个阵列表现为WRITE_FIRST。

(3)no:这时值设计人员不关心时序或冲突的可能性。在这种情况下,写入模式将被设置为NO_CHANGE,从而节省功率。

仅在RTL中支持RW_ADDR_COLLISION属性。该属性的Verilog HDL和VHDL描述例子如代码清单2-72和代码清单2-73所示。

代码清单2-72 RW_ADDR_COLLISION属性的Verilog HDL描述例子

代码清单2-73 RW_ADDR_COLLISION属性的VHDL描述例子

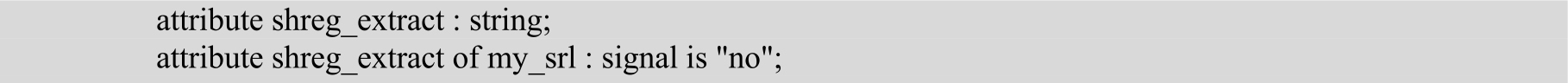

SHREG_EXTRACT属性指示Vivado综合工具是否推断SRL结构,可接受的值为:

(1)yes:工具推断SRL结构。

(2)no:不推断SRL,而是创建寄存器。

将 SHREG_EXTRACT 属性放在为 SRL 或具有 SRL 的模块/实体声明的信号上,可以在RTL或XDC中设置该属性。该属性的Verilog HDL和VHDL描述例子如代码清单2-74和代码清单2-75所示。

代码清单2-74 SHREG_EXTRACT属性的Verilog HDL描述例子

代码清单2-75 SHREG_EXTRACT属性的VHDL描述例子

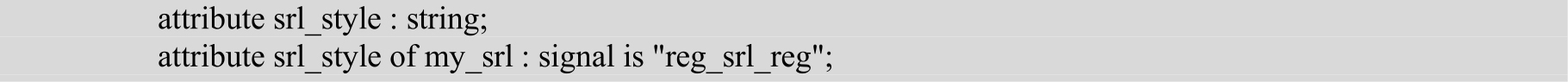

SRL_STYLE属性指示Vivado综合工具如何推断设计中发现的SRL,可接受的值为:

(1)register:Vivado综合工具不推断SRL,而是仅使用寄存器。

(2)srl:Vivado综合工具推断出一个SRL,在此之前或之后没有任何寄存器。

(3)srl_reg:Vivado综合工具推断SRL,并在SRL之后留下一个寄存器。

(4)reg_srl:Vivado综合工具推断SRL,并在SRL之前留下一个寄存器。

(5)reg_srl_reg:Vivado综合工具推断SRL,并在SRL之前和之后留下一个寄存器。

(6)block:Vivado综合工具推断SRL在BRAM中。

将SRL_STYLE属性放在为SRL声明的信号上,该属性可以在RTL和XDC中设置。该属性只能用于静态SRL。动态SRL的索引逻辑位于SRL元件本身内。因此,不能在SRL元件周围创建逻辑来查找元件外部的地址。

注: 使用 SRL_STYLE、SHREG_EXTRACT 和-shreg_min_size 的组合时要小心。SHREG_EXTRACT 属性始终优先于其他属性。如果将 SHREG_EXTRACT 属性设置为 no,将SRL_STYL 属性设置为 SRL,则使用寄存器。作为全局变量的-shreg_min_size 总是具有最小的优先级。如果设置了长度为10的SRL,SRL_STYLE属性设置为SRL且-shreg_min_size设置为20,则依然推断SRL。

SRL_STYLE属性的Verilog HDL和VHDL描述的例子如代码清单2-76和代码清单2-77所示,该属性在XDC中描述的例子如代码清单2-78所示。

代码清单2-76 SRL_STYLE属性的Verilog HDL描述例子

代码清单2-77 SRL_STYLE属性的VHDL描述例子

代码清单2-78 SRL_STYLE属性在XDC中描述的例子

在上面的例子中,SRL 都是用总线创建的,其中 SRL 从一位移动到下一位。如果要使用SRL_STYLE 属性的代码有许多不同名字的信号互相驱动,则将 SRL_STYLE 属性放在链中的最后一个信号上。这包括链中的最后一个寄存器是否与其他寄存器处于不同的层次结构级别。属性总是位于链中的最后一个寄存器中。

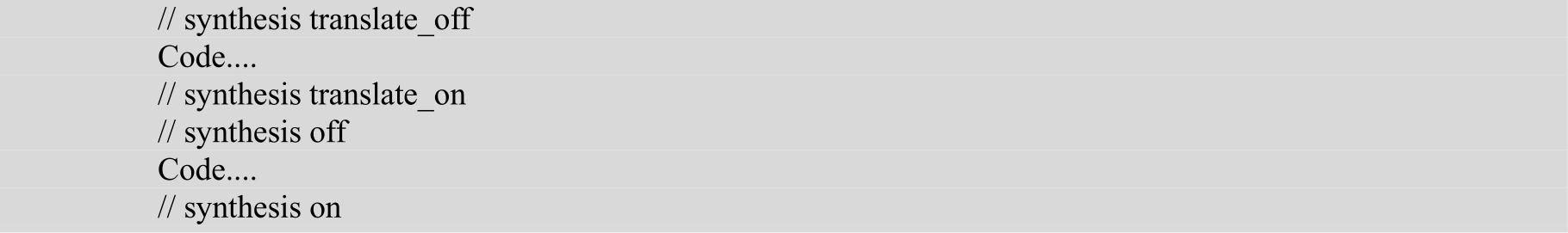

TRANSLATE_OFF/TRANSLATE_ON 属性指示 Vivado 综合工具忽略代码块,这些属性在RTL 中的注释中给出。注释可以以下面其中一个关键字开头:synthesis、synopsys、pragma 或xilinx。在 Vivado 综合工具的新版本中,使用关键字已经成为可选项,该工具将仅在注释中使用translate_off/on或off/on。

TRANSLATE_OFF启动忽略,并以TRANSLATE_ON结束。这些命令不能嵌套。TRANSLATE_OFF/TRANSLATE_ON属性只能在RTL中设置,该属性的Verilog HDL和VHDL描述的例子如代码清单2-79和代码清单2-80所示。

代码清单2-79 TRANSLATE_OFF/TRANSLATE_ON属性的Verilog HDL描述例子

代码清单2-80 TRANSLATE_OFF/TRANSLATE_ON属性的VHDL描述例子

注: 注意 translate 语句之间包含的代码类型。如果代码影响了设计行为,仿真器可能会使用该代码,并造成仿真不匹配。

USE_DSP 属性指示 Vivado 综合工具如何处理综合算术结构。默认情况下,除非存在时序问题或阈值限制,否则综合尝试将乘法、乘法-加法、乘法-减法、乘法-累加类型的结构推断到DSP块。

加法器、减法器和累加器也可以进入这些块,但默认情况下是使用逻辑而不是使用DSP实现。USE_DSP属性覆盖默认行为,并强制这些结构进入DSP块。

USE_DSP属性可接受的值为logic、simd、yes和no。

(1)logic 值专门用于 XOR 结构,以进入 DSP 原语。对于 logic,这个属性只能放置在module/architecture级。其中,module为Verilog HDL中的模块,architecture为VHDL中的结构体。

(2)simd用于指示工具将单指令多数据流结构(Single Instruction Multiple Data,SIMD)放入DSP。

(3)yes 和 no 值指示工具是否将逻辑放入 DSP。这些值可以放在 RTL 中的信号、结构体、元件、实体和模块上。优先级从1到3依次为信号、结构体和元件、模块和实体。

如果未指定属性,则 Vivado 综合的默认行为将确定正确的行为。该属性可以在 RTL 或XDC中设置。

注: (1)该属性从 USE_DSP48 重命名,以识别一些较新的DSP块的大小不同。即使使用不同大小的DSP,使用属性USE_DSP48仍然有效。

(2)Xilinx建议设计人员将任何USE_DSP48更新为新的属性名字USE_DSP。

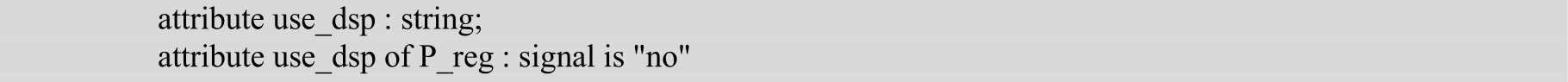

USE_DSP 属性的 Verilog HDL 和 VHDL 描述例子如代码清单 2-81 和代码清单 2-82所示。

代码清单2-81 USE_DSP属性的Verilog HDL描述例子

代码清单2-82 USE_DSP属性的VHDL描述例子