Xilinx Vivado IDE使用Xilinx设计约束(Xilinx Design Constraints,XDC)格式,而不再支持原来的用户约束文件(User Constraints File,UCF)格式。

XDC是业界标准SDC(SDC V1.9)和Xilinx专有物理约束的组合。XDC具有以下属性:

(1)它们不是简单的字符串,而是遵循Tcl语义的命令。

(2)通过Vivado Tcl翻译器,可以像理解其他Tcl命令那样理解它们。

(3)与其他Tcl命令一样按顺序读取和解析它们。

设计者可以在设计流程的不同阶段,通过下面几种方式输入XDC。

(1)将约束保存在一个或者多个XDC文件中。要在内存中加载XDC文件,需要执行下面其中一个操作:

①使用read_xdc命令。

②将它添加到其中一个设计工程约束集中。XDC 文件只接收 set、list 和 expr 内建的 Tcl命令。

(2)通过非管理的Tcl脚本生成约束。要执行Tcl脚本,需要执行下面其中一个操作:

①运行source命令。

②使用read_xdc-unmanaged命令。

③将Tcl脚本添加到一个工程约束集中。

XDC与UCF存在很大的区别,主要表现在以下几个方面:

(1)XDC是顺序语言,它带有明确的优先级规则。

(2)UCF通常应用于网络,XDC通用应用于引脚、端口和单元对象。

(3)UCF的TIMESPEC PERIOD和XDC的create_clock命令并不总是等效的,并且可能会导致不同的时序结果。

(4)默认情况下,UCF 在异步时钟组之间无时序关系;而在 XDC 中,除非有其他约束,所有时钟都看作有关联的并且有时序(set_clock_groups)。

(5)在XDC中,同一对象上可以存在多个时钟。

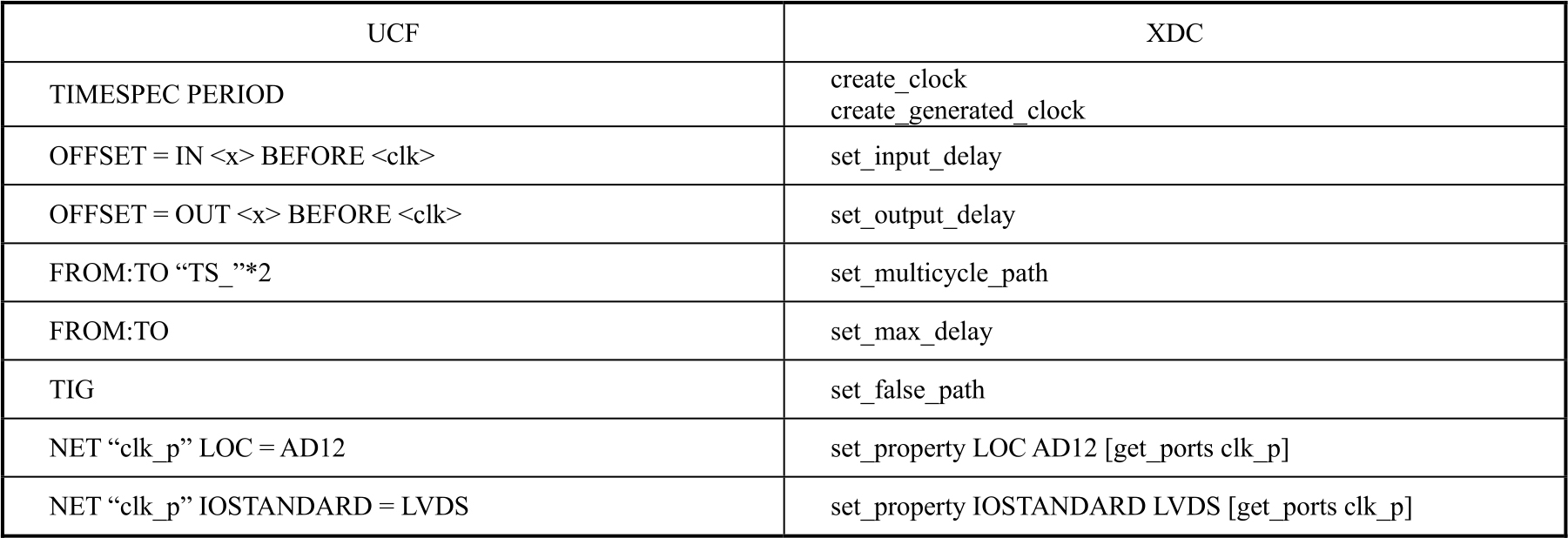

表2.2给出了UCF到XDC的映射关系。

表2.2 UCF到XDC的映射关系

设计约束定义了编译流程中必须满足的要求,以便设计在电路板上发挥作用。并非所有的约束都要在编译流程的所有步骤中使用。比如,物理约束仅在实现步骤期间使用(由布局器和布线器使用)。

由于Xilinx Vivado IDE的综合和实现算法是时序驱动的,所以设计人员必须正确地创建时序约束。过度约束或欠约束都会使设计的时序收敛变得困难。设计人员必须使用与应用要求相对应的合理约束。

Vivado IDE 允许设计人员使用一个或多个约束文件。虽然在整个编译流程中使用单个约束文件似乎更方便,但是随着设计变得更加复杂,维护所有约束可能变成一个挑战。这种情况通常适用于使用多个IP核或由不同团队开发的大型块设计。

导入时序和物理约束后,无论源文件的个数如何,也无论设计处于工程模式还是非工程模式,都可以使用write_xdc命令将所有约束导出为单个文件。约束将按照读取的工程或设计中的顺序写入指定的输出文件。命令行选项 write_xdc-type 可用于选择要导出的约束子集(时序、物理或弃权)。

注: Xilinx 推荐设计人员通过将时序约束和物理约束保存到两个不同的文件。还可以将某个模块的约束保存在单独的文件中。

设计人员可以在创建新工程期间或以后利用Vivado IDE菜单命令将XDC文件添加到约束集。需要注意,如果工程中包含使用自己约束的 IP,则相应的约束文件不会出现在约束集中。相反,它与IP源文件一起列出。

设计人员可以将 Tcl 脚本添加到约束集中,作为非管理约束或非管理的 Tcl 脚本。Vivado设计套件不会将修改后的约束写回到一个非管理的 Tcl 脚本中。Tcl 脚本和 XDC 文件的加载顺序与Vivado IDE中显示的顺序相同(如果它们属于同一个PROCESSING_ORDER组),或者与命令report_compile_ORDER-constraints报告的顺序相同。如果需要,可以在多个约束集中使用XDC或Tcl脚本。

在非工程模式下,执行编译命令前,必须单独读取每个文件。

在使用DFX的设计中,通常使用OOC方法来综合设计的一部分。当使用这样的流程时,可以仅为OOC综合指定一些约束。例如,当块是综合的OOC时,必须定义在块输入边界传播的时钟。

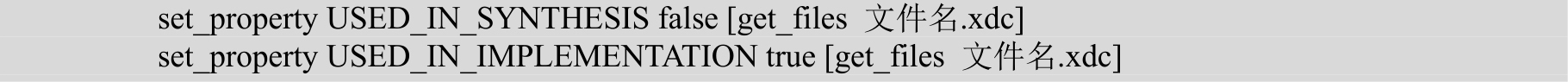

默认地,所有添加到约束集中的XDC文件和Tcl脚本都可以用于综合与实现过程。通过在XDC 文件或 Tcl 脚本中设置 USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 属性以更改此行为。该属性的值可以是TURE或FALSE。

注: DONT_TOUCH 属性不会受到上面属性设置的影响,如果在综合时使用DONT_TOUCH,则将其传递到实现过程。DONT_TOUCH 属性与 USED_IN_IMPLEMENTATION属性无关。

比如,可以使用下面的方法修改XDC只用于实现。

(1)在Source窗口中选择约束文件。

(2)在Source File Properties窗口中不勾选Synthesis前面的复选框,但勾选Implementation前面的复选框。

等效的Tcl命令为:

当在非工程模式下运行 Vivado 时,可以直接读取任何步骤之间的约束。属性 USED_IN_SYNTHESIS和USED_IN_IMPLEMENTATION在该模式下无关紧要。

由于 XDC 是按顺序应用的,并且是基于明确的优先级规则排定优先级的,因此必须仔细查看约束的顺序。

注: 如果多个物理约束冲突,则最新的约束获胜。例如,如果通过多个XDC文件为I/O端口分配了不同的位置(LOC),则分配给该端口的最新位置优先。

Vivado IDE为设计人员的设计提供了充分的可视性。要逐步验证约束,请执行以下操作:

(1)运行相应的报告命令。

(2)查看Tcl Console(Tcl控制台)或Messages(消息)窗口中的消息。

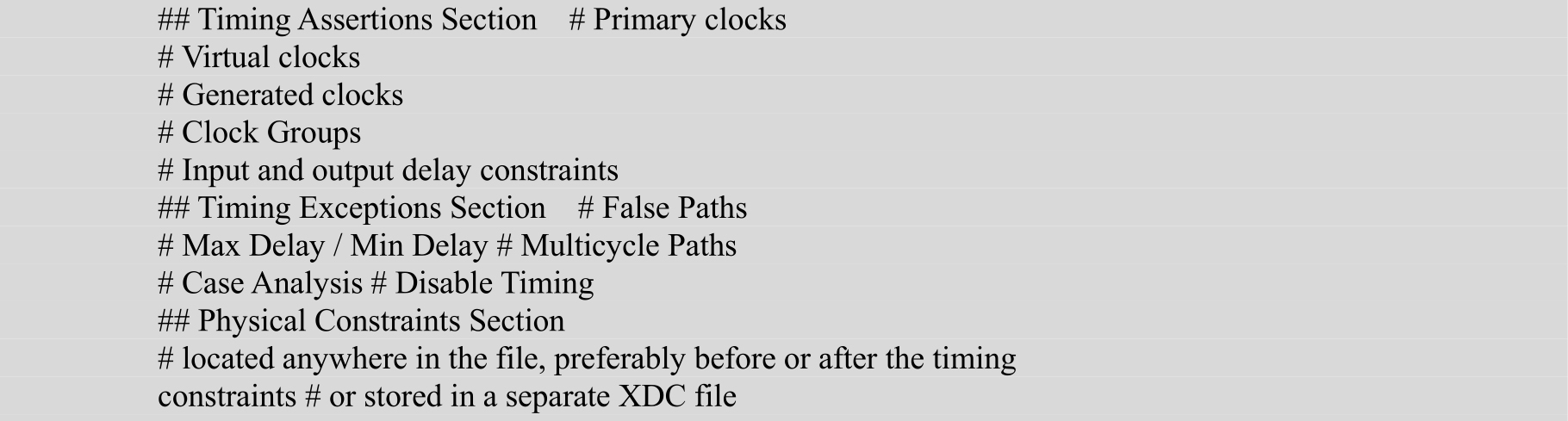

不管在设计中使用一个或多个 XDC 文件,推荐使用下面的顺序来组织约束(见代码清单2-3)。

代码清单2-3 XDC文件的约束顺序

注: 在定义生成时钟之前,应定义更改时钟关系或时钟传播情况的分析约束。这包括在时钟缓冲区上定义的情况分析,其导致缓冲区的输出时钟受到影响。

从时钟定义开始,必须先创建时钟,然后才能被后续的约束使用。在声明时钟之前,对它的任何引用都会导致错误,并且会忽略相应的约束。在单个约束文件中,以及在设计中的所有XDC文件(或Tcl脚本)中,都是这样。

约束文件的顺序很重要。设计人员必须保证每个文件中的约束不依赖于另一个文件的约束。如果是这种情况,则必须最后读取包含约束依赖项的文件。如果两个约束文件具有相互依赖关系,则必须手动将它们合并到一个包含正确序列的文件中,或者将这些文件划分为几个单独的文件并正确排序。

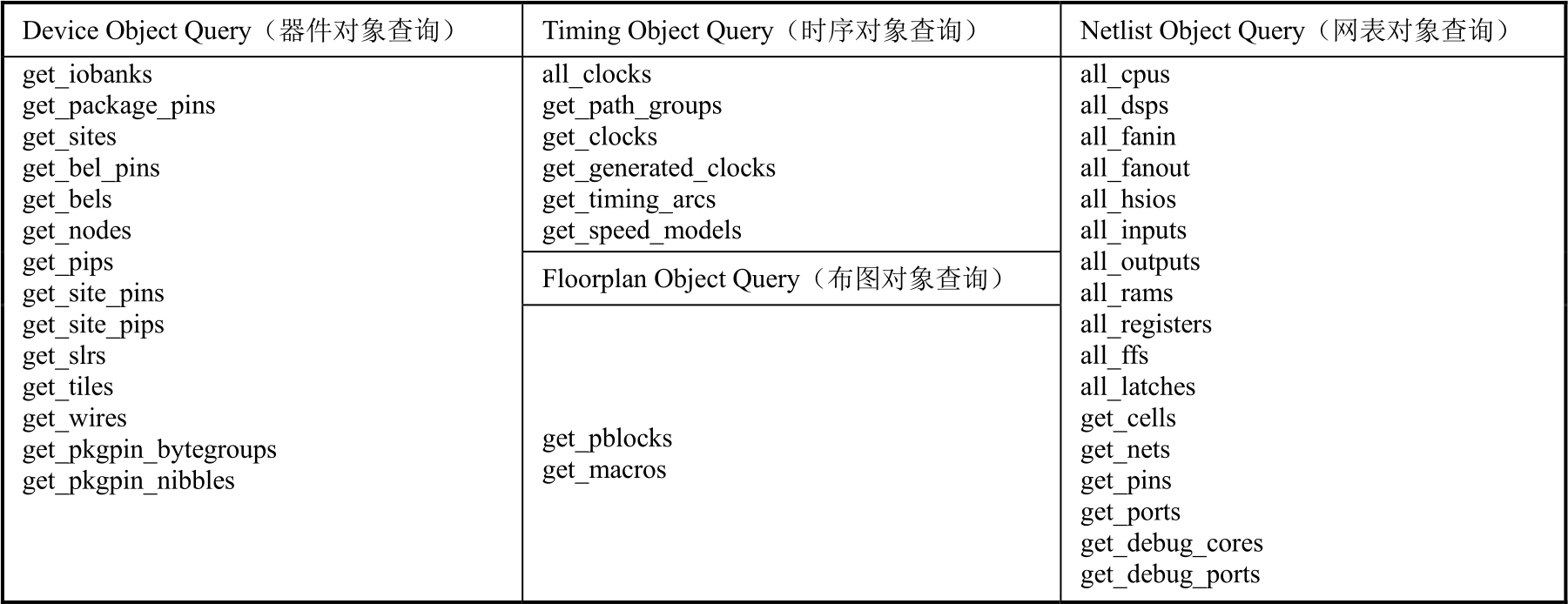

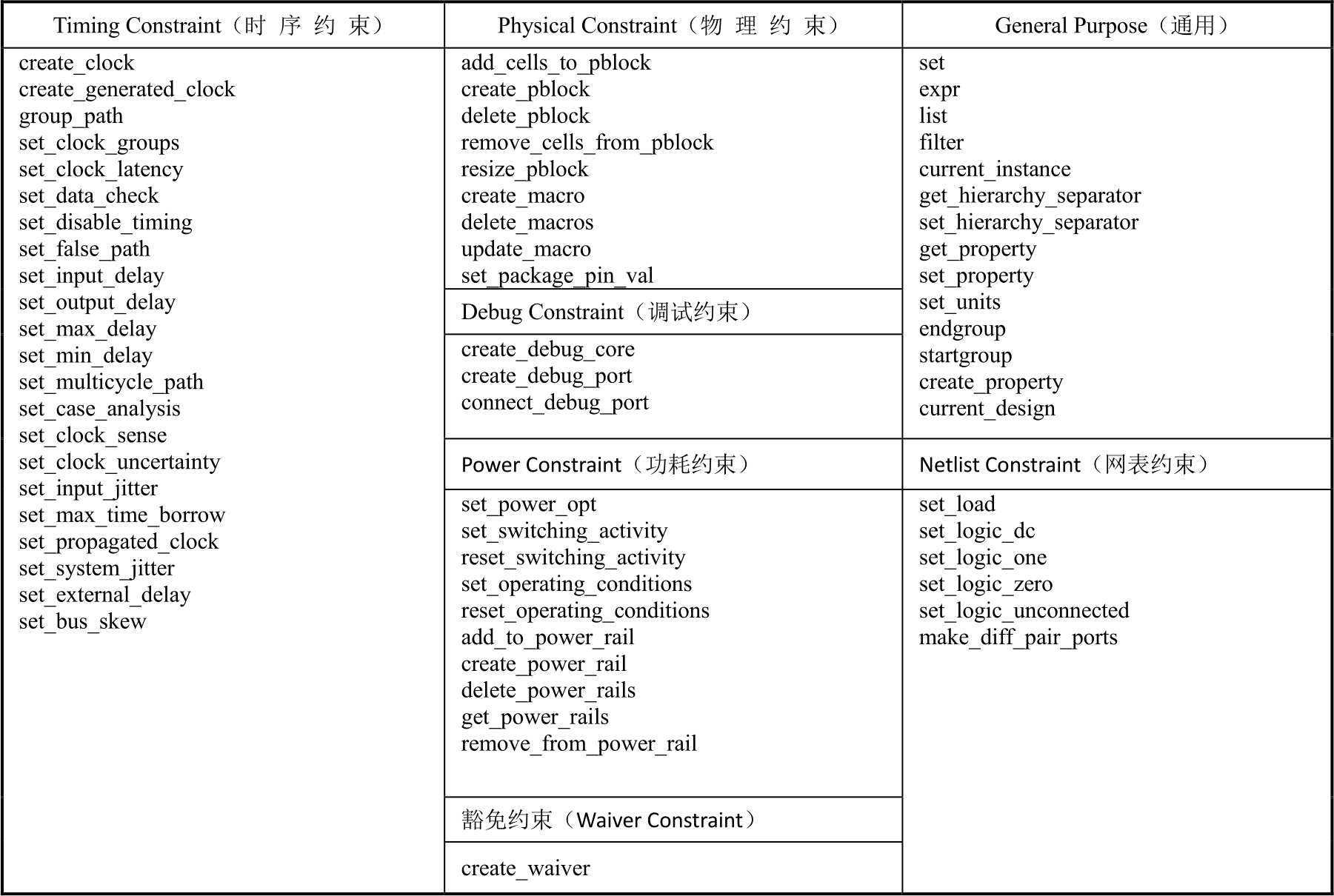

表2.3给出了XDC文件中有效的命令。在本书随后的章节中,将通过实例对这些命令进行解释。

表2.3 XDC文件中有效的命令

续表