Xilinx FPGA是高灵活性、可重新编程的逻辑器件。类似处理器那样,Xilinx FPGA也是完全可由用户编程的。对于FPGA来说,该程序称为比特流(Bitstream),它定义了特定于应用的FPGA功能。在系统上电或系统要求时,比特流加载到FPGA内的存储器中。

类似处理器和处理器外设,Xilinx FPGA 可以在系统中根据要求无限次地重新编程。在编程之后,FPGA 比特流保存在高鲁棒性的 CMOS 配置锁存器(CMOS Configuration Latch,CCL)中。尽管CCL类似 SRAM存储器那样可以重新编程,但是CCL的设计主要是为了数据完整性。由于 Xilinx FPGA比特流保存在 CCL中,因此必须在 FPGA上电后对其进行重新配置。

将定义的数据加载或编程到 FPGA 中的过程称为配置(Configuration)。配置被设计为灵活的,以适应不同的应用需求,并尽可能利用现有的系统资源来最大限度地降低系统成本。

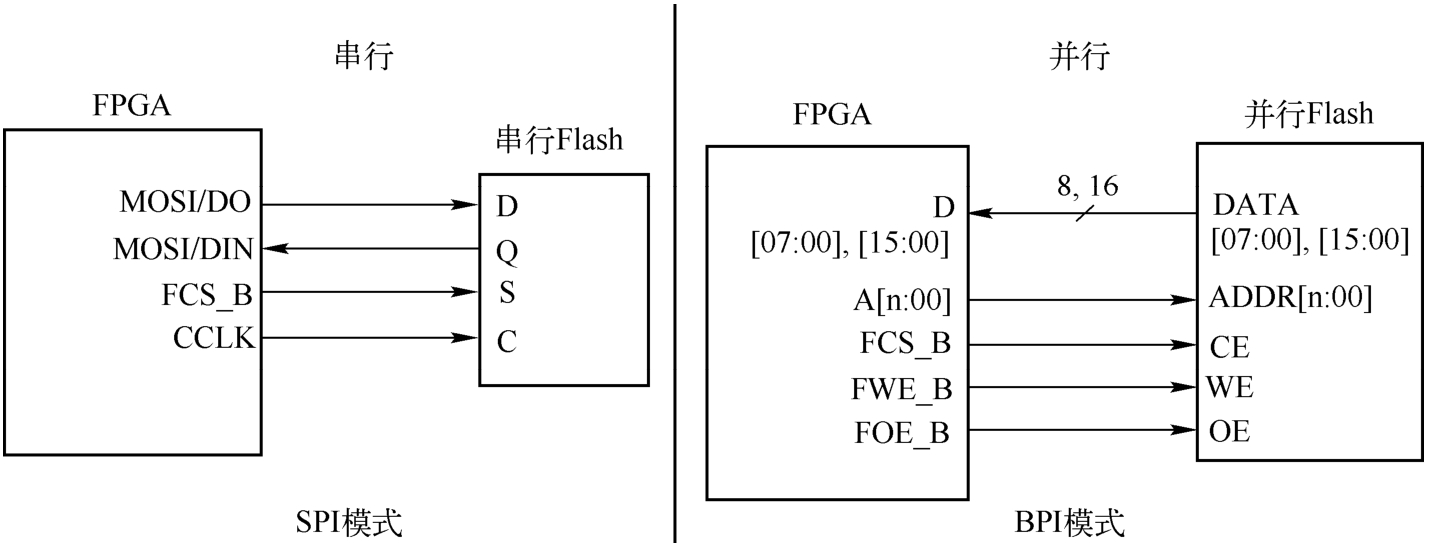

与处理器类似,Xilinx FPGA 可以选择从外部非易失性存储器中加载或引导自己。或者,类似于处理器外设,Xilinx FPGA可以由外部设备下载或编程,如微处理器、DSP处理器、微控制器、PC 或板子测试仪。配置数据路径可以是串行的,以最大限度地减少引脚要求,包括通过行业标准 IEEE 1149.1 JTAG 边界扫描接口。并行配置路径提供了最大的性能和对工业标准接口的访问,非常适合类似处理器、x8/x16 并行 Flash 存储器(闪存)的外部数据源。

通过特殊的配置引脚,将配置比特流加载到 FPGA 中。这些配置引脚用作多种不同配置模式的接口,包括从串行、从 SelectMAP(并行)(×8、×16 和×32)、JTAG 边界扫描、主串行外设接口(Serial Peripheral Interface,SPI)(串行NOR闪存×1、×2、×4和两个×4,有效×8)、主字节外设接口(Byte Peripheral Interface,BPI)(并行 NOR 闪存×8 和×16)、主串行、主SelectMAP(并行)(×8和×16)。

上面提到的“主”和“从”是指配置时钟(CCLK)的方向。

(1)在主配置模式下,FPGA 从内部振荡器驱动 CCLK。配置选项用于选择所需要的频率。配置后,默认关闭 CCLK,CCLK 引脚为三态,带有一个弱上拉。例如,在主配置模式下,FPGA的配置比特流驻留在与FPGA在相同的PCB上的非易失性存储器中。在该模式下,由FPGA内产生配置时钟信号CCLK,通过FPGA给闪存发送时钟或地址来控制配置过程。主配置模式如图1.92所示。

图1.92 主配置模式

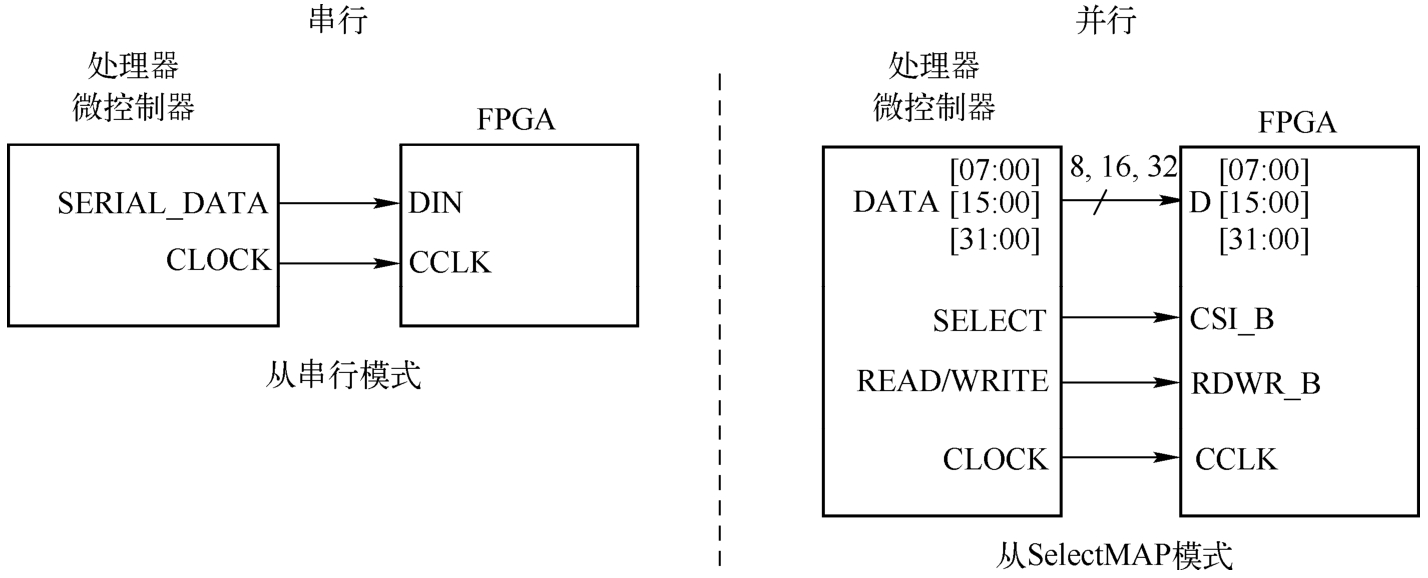

(2)在从配置模式下,CCLK 为输入。在这种模式下,外部处理器、微控制器、DSP 处理器或测试器将配置镜像下载到FPGA。从配置模式如图1.93所示。

图1.93 从配置模式

从配置模式的优势在于,FPGA 比特流几乎可以位于整个系统中的任何地方。比特流可以与主机处理器的代码一起保存在闪存中、硬盘上或网络连接的某个地方。从图 1.93 可知,从串行模式是一个简单的接口,由时钟和串行数据输入组成。从 SelectMAP 模式是×8、×16 或×32位宽的处理器外设接口,包括芯片选择输入和读/写控制输入。

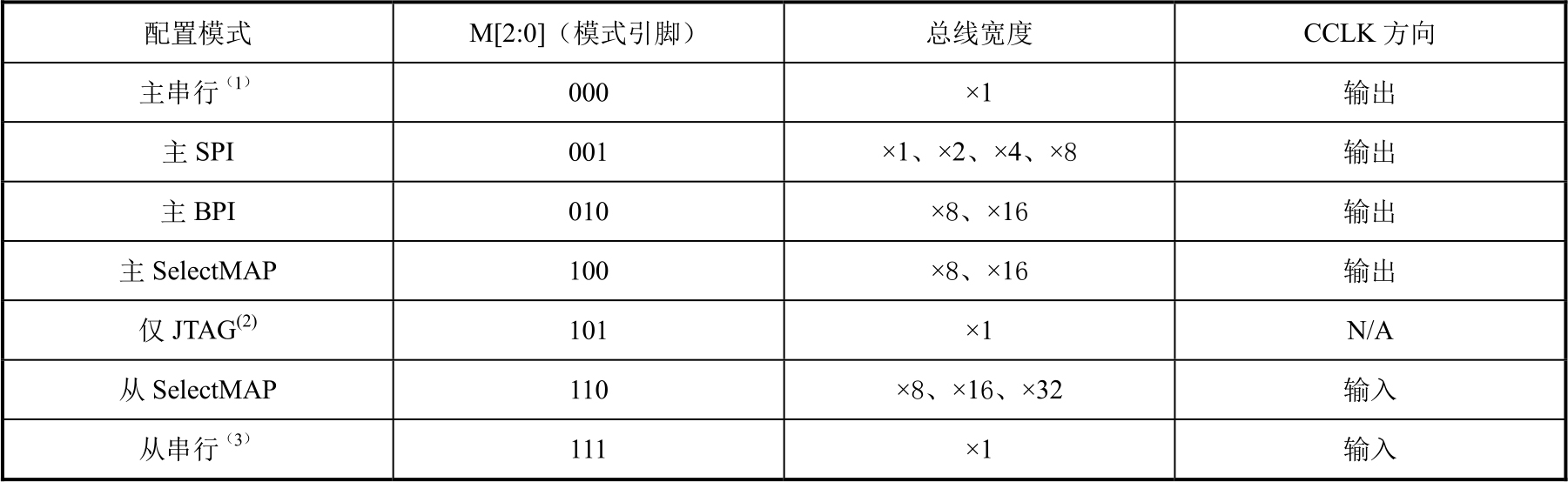

通过在模式输入引脚 M[2:0]上设置适当的电平来选择特定的配置模式,如表1.31 所示。M2、M1和M0模式引脚通过上拉或下拉电阻(<1kΩ)设置在恒定直流电平,或直接连接到地或V CCO_0 。无论如何设置模式引脚,JTAG(边界扫描)配置接口始终可用。

表1.31 配置模式

注: (1)不建议在UltraScale架构FPGA中使用,也不支持在UltraScale+架构FPGA中使用。

(2)JTAG 模式始终可用,与模式引脚设置无关。不推荐在基于 SSI 技术的 FPGA 中将模式引脚设置为仅JTAG,这是由于ICAP访问的限制。

(3)由于模式引脚上的内部上拉电阻,从串行是默认设置。

每个配置模式都有一组相应的接口引脚,这些引脚跨越 FPGA 上的一个或两个组。Bank 0包含专用的配置引脚,并且始终是每个配置接口的一部分。Bank 65 包含一些配置模式中涉及的多功能引脚。

FPGA 还可以通过从 FPGA 逻辑到配置逻辑的内部连接来控制其自身的配置。该器件可以使用其选择的替代设计进行完全重新编程,或者部分重配置以允许对 FPGA 内特定区域使用新功能进行重新编程,同时应用继续在FPGA的其他部分中运行。

下面简要给出了 UltraScale+架构的 Artix 系列、Kintex 系列和 Virtex 系列 FPGA 的配置差异:

(1) UltraScale+架构的 FPGA 不支持主串行和主 SelectMAP 配置模式。不建议在其他UltraScale架构FPGA中使用这些模式。

(2)在 UltraScale+架构的 FPGA 中,配置接口只能工作在 1.8V 或 1.5V。UltraScale+架构FPGA 中没有 CFGBVS 引脚。当从 UltraScale 架构 FPGA 转到 UltraScale+架构 FPGA 时,CFGBVS引脚位置变成RSVDGND,必须将其连接到GND。

(3)UltraScale 架构 FPGA 和 UltraScale+架构 FPGA 的配置时间与配置速率选择不同。在UltraScale+架构FPGA中,配置帧大小为93个32位字;在UltraScale架构FPGA中,配置帧大小为123个32位字。

JTAG是Joint Test Action Group的简称,中文称联合测试行动组。业界经常用JTAG来指代边界扫描,这是一种集成电路测试方法,用来对集成电路的内部结构进行测试。在 Xilinx FPGA中,将JTAG作为将比特流文件下载到FPGA的基本方法。

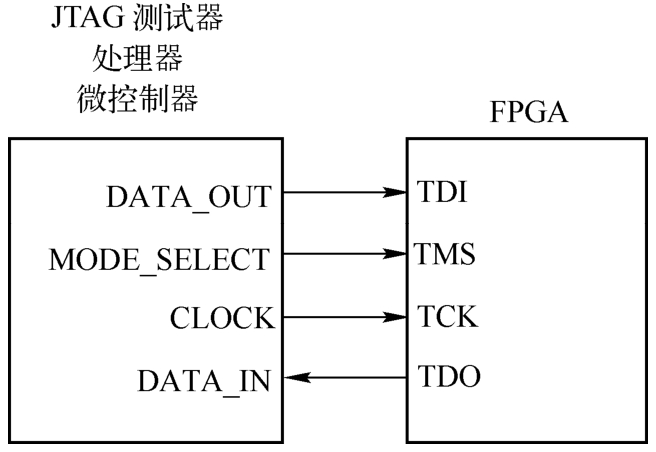

JTAG 也是一种串行配置模式,在原型设计中很受欢迎,在板测试中也经常被用到。4 个引脚地JTAG边界扫描接口在板测试器和调试硬件中常见。用于基于UltraScale+架构的FPGA的 Xilinx 编程电缆使用 JTAG 接口进行原型下载和调试。在应用中不管最终采用什么配置模式,最好还是包含一个 JTAG 配置路径以方便设计开发。JTAG 的基本连接结构如图 1.94所示。

图1.94 JTAG的基本连接结构

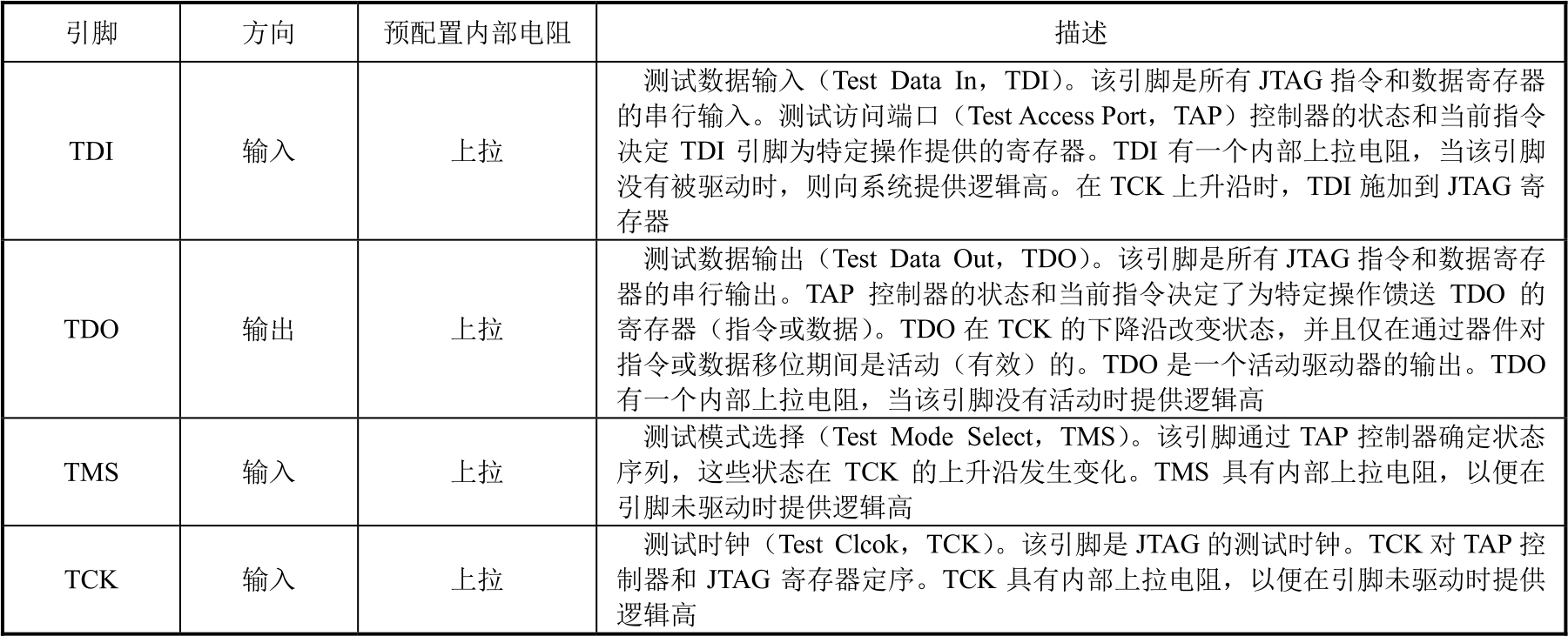

图1.94中FPGA内JTAG端口的含义如表1.32所示。

表1.32 图1.94中FPGA内JTAG端口的含义

与处理器代码类似,定义了FPGA功能的比特流在上电期间加载到FPGA中。由于该配置数据保存在芯片外,因此存在未经授权复制或修改的可能性。

与处理器类似,有多种技术可以保护比特流和任何嵌入式知识产权(Intellectual Property,IP)核。保护 FPGA 开发人员 IP 机密性的最可靠方法是使用 AES-256 密钥加密配置数据。芯片上解密逻辑的密钥可以保存在电池支持的RAM或一次性可编程eFUSE中。该技术允许对IP进行芯片外保存,并使用高级加密进行保护。

默认情况下,可以通过 JTAG 端口、SelectMAP 端口(如果选择了 Persist)或 ICAPE4 原语(如果在设计中例化了 ICAPE4)回读或重新配置活动(有效)的 FPGA 配置。安全的一种基本形式是阻止访问配置逻辑,如不允许配置端口持久存在,以及不使能 ICAP 与外部引脚的连接。此外,比特流回读安全设置(BITSTREAM.READBACK.SECURITY)可以设置为Level1(禁止回读)或Level2(禁止回读和重新配置)。在配置的FPGA中删除回读安全性设置的唯一方法就是通过使 PROGRAM_B 有效或循环加电来清除 FPGA 程序。如果用户设计是敏感的,则应该考虑比特流加密。加密的使用会自动阻止通过硬件门而不是仅仅比特流设置回读。这是阻止回读和保护 FPGA 开发人员 IP 的最强方法。比特流回读安全设置不影响 SEU 检测的回读。

具有 Xilinx UltraScale 架构的 FPGA 具有片上高级加密标准(Advanced Encryption Standard,AES)解密和身份验证逻辑,可提供很好的设计安全性。如果不知道加密密钥,其他人就无法分析外部截获的比特流或复制设计。加密的 FPGA 设计不能被复制或逆向工程。

FPGA AES系统包含基于软件的比特流加密芯片和片上的比特流解密,芯片上有用于存储加密密钥的专用存储器。FPGA 开发人员使用 Xilinx Vivado 工具生成加密密钥和加密的比特流。基于UltraScale架构的FPGA将加密密钥内部保存在由小型外部连接电池备份的专用 RAM 中,或者保存在非易失性一次可编程 eFUSE 中。所选选项是在 BITSTREAM.ENCRYPTION.ENCRYPTKEYSELECT 设置为 BBRAM 或 EFUSE 的情况下定义的。加密密钥只能通过外部JTAG端口或内部MASTER_JTAG原语编程到FPGA中,无法回读加密密钥。

在配置期间,FPGA 器件执行反相操作,对传入的比特流进行解密。FPGA AES 加密逻辑使用 256 位加密密钥。芯片上 AES 解密逻辑不能用于除比特流解密之外的任何目的。AES 解密逻辑对用户逻辑不可用,并且不能用于解密除配置比特流之外的任何数据。

尽管 AES-GCM 算法是一种自认证算法,但它使用对称密钥实现,这意味着要加密的密钥和要解密的密钥相同。该密钥必须得到保护,这是因为它是秘密的(因为保存到内部密钥空间)。但是,如果只需要身份验证,UltraScale 架构提供了 RSA-2048 形式的另一种身份验证形式。RSA 是一种非对称算法,这意味着要验证的密钥与用于签名的密钥不同。验证是用公钥完成的。该密钥是公用的,不需要保护,也不需要特殊的安全存储。如果需要,这种形式的身份验证可以与加密结合使用,以提供真实性和机密性。

思考与练习1-24: 用Vivado 2023.1打开前面任意一个工程,在Device视图中查看FPGA内CONFIG块的布局,并画图说明该布局。