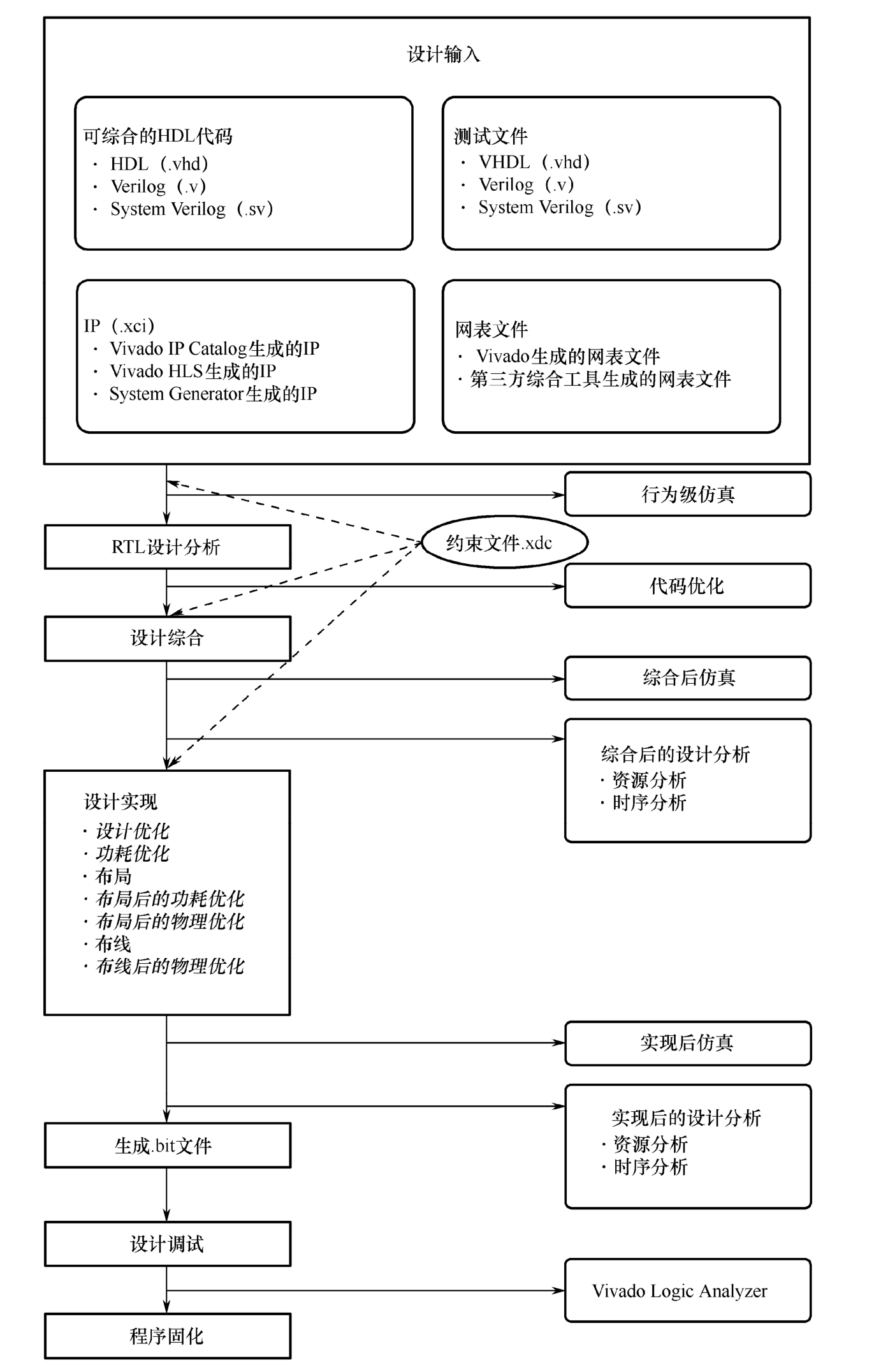

Vivado是Xilinx新一代针对7系列及后续FPGA的开发平台。Vivado下的FPGA设计流程 [7] 如图1.23所示。可以看到,借助Vivado能够完成FPGA的所有流程,包括设计输入、设计综合、设计实现、设计调试和设计验证。

相比于Xilinx前一代开发平台ISE,Vivado的设计实现环节较为复杂,多了几个步骤,如图1.23中设计实现框内的斜体字所示。这几个步骤是可选的,但布局和布线则是必需的。正是这些步骤及每个步骤自身的参数选项使得Vivado可以构造不同的实现策略。

设计优化可进一步对综合后的网表进行优化,如可以去除无负载的逻辑电路,可以优化BRAM功耗(优化BRAM功耗是在设计优化阶段而非功耗优化阶段完成的)。

功耗优化是借助触发器的使能信号降低设计的动态功耗。尽管功耗优化可以在布局前运行也可以在布局后运行,但为了达到更好的优化效果,最好在布局之前运行。布局之后的功耗优化是在保证时序的前提下进行的,因而优化受到限制。

物理优化可进一步改善设计时序。对于关键时序路径上的大扇出信号,通过复制驱动降低扇出,改善延时;对于关键时序路径上的与DSP48相关的寄存器,可以根据时序需要将寄存器从SLICE中移入DSP48内部或从DSP48内部移出到SLICE中;对于关键路径上的与BRAM相关的寄存器,可以根据时序需要将寄存器从SLICE中移入BRAM内部或从BRAM内部移出到SLICE中。

对于约束,Vivado采用了新的描述方式XDC(Xilinx Design Constraints),它是在SDC(Synopsys Design Constraints)基础上的扩展。相比于ISE,Vivado对约束的管理更为灵活,可以在设计综合前加入约束文件,也可以在设计综合后添加约束,同时还可以设定约束的作用域和作用阶段。

图1.23 Vivado下的FPGA设计流程

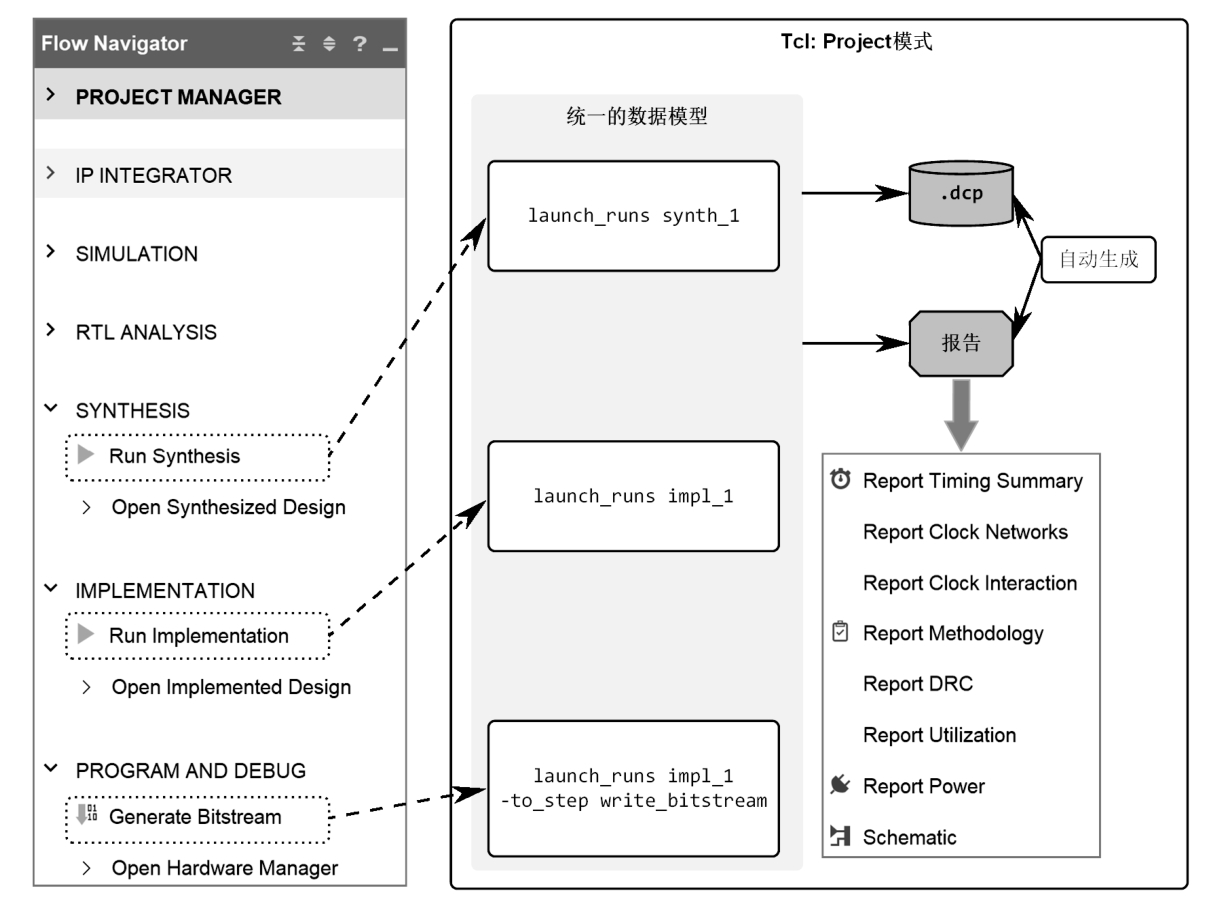

Vivado提供了两种运行模式:Project模式和Non-Project模式。其中,Project模式可以在图形界面下操作或以Tcl脚本方式在Vivado Tcl Shell中运行;Non-Project模式只能以Tcl脚本方式运行。

对于Project模式,Vivado以图形界面方式提供了Flow Navigator,使得整个设计流程一目了然。图形界面菜单操作与Tcl脚本的对应关系如图1.24所示。综合和实现之后会自动生成相应的网表文件(Design Checkpoint,DCP)。与ISE不同,Vivado采用了统一的数据模型,网表文件统一为DCP格式。

图1.24 Project模式下图形界面方式与Tcl脚本的对应关系

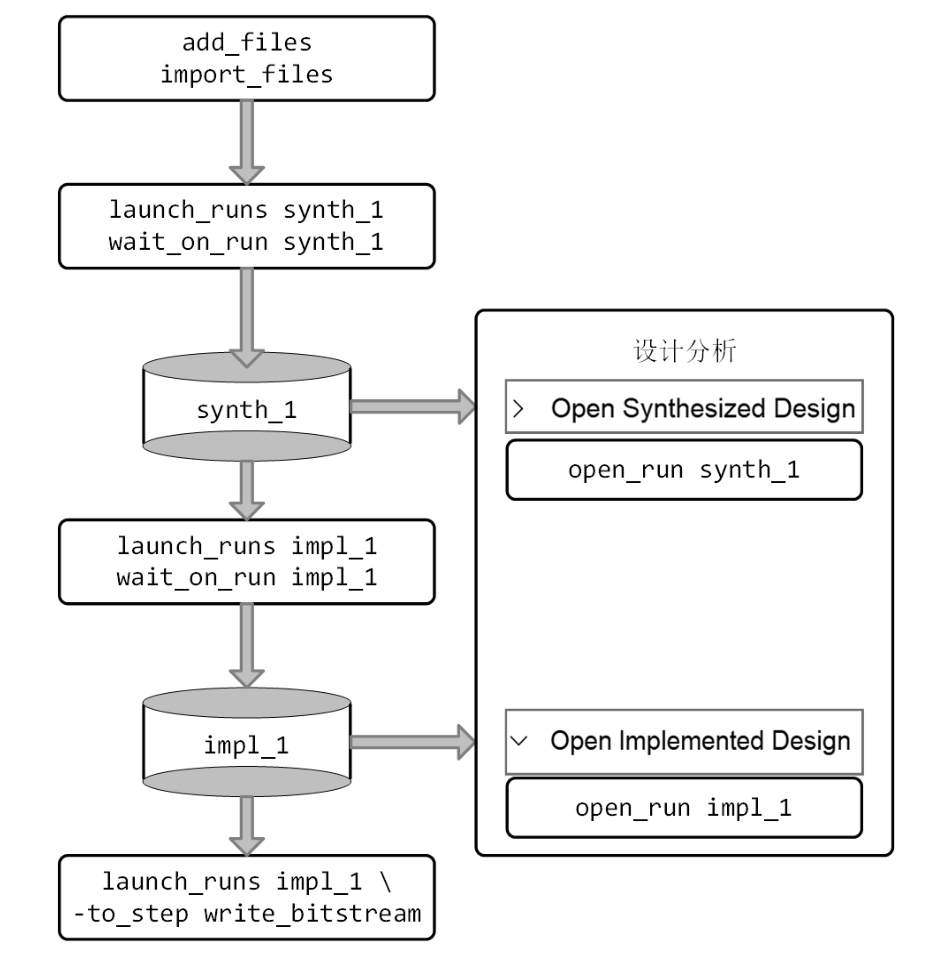

Project模式可以采用Tcl脚本的方式在Vivado Tcl Shell中运行,相应的Tcl命令和流程如图1.25所示。对综合或实现后的设计进行分析时,需要先将综合或实现后的运行结果(DCP)打开,这可通过open_run命令执行。

图1.25 Project模式以Tcl脚本方式的运行流程

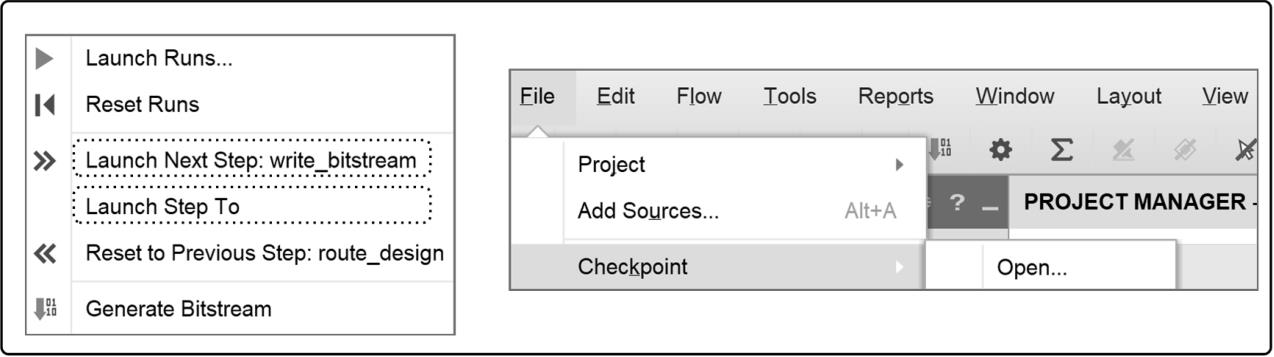

在Project模式的实现阶段,可以逐步执行每个分步骤,如图1.26所示,被执行的分步骤会自动生成相应的网表文件(DCP)。单击File菜单下的Checkpoint,打开该网表文件可进行设计分析。

图1.26 Project模式下逐步执行实现阶段的每个分步骤

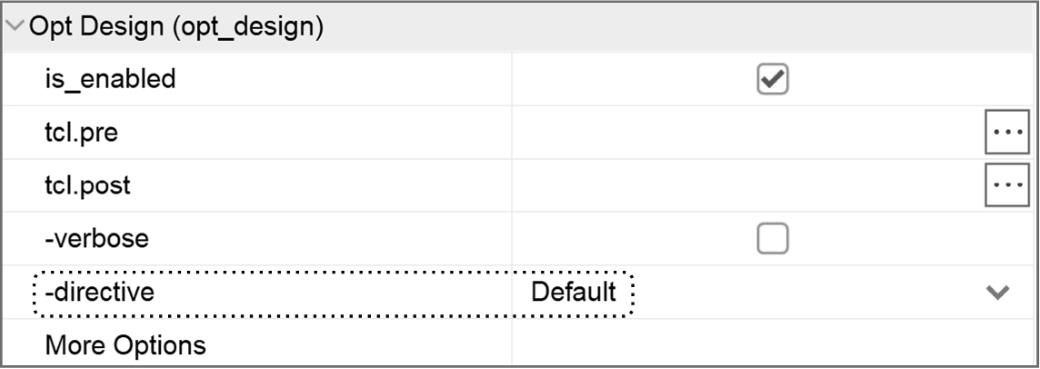

对于实现阶段的各个分步骤可以指定其指令(-directive),还可以指定其他参数(具体参数可参考ug835),如图1.27所示。

图1.27 Project模式下设置分步骤参数

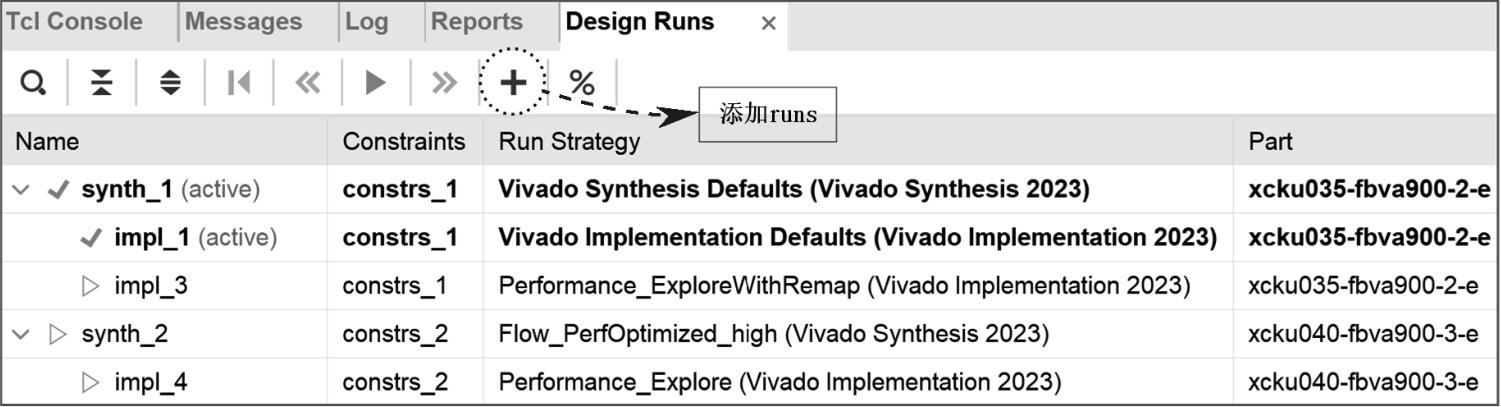

在Project模式下,可以添加多个runs同时运行,如图1.28所示。Impl_1建立在synth_1的基础上。不同的synth run可以有不同的约束文件、芯片型号和综合策略。

图1.28 Project模式下添加多个runs

Non-Project模式类似于ASIC的开发流程,全部采用Tcl脚本在Vivado Tcl Shell中运行。相应的Tcl脚本和流程如图1.29所示。与Project模式不同,Non-Project模式下需要手动生成各个分步骤的网表文件(DCP)和报告(如时序报告、资源利用率报告等)。

图1.29 Non-Project模式操作流程

Non-Project模式尽管只能在Vivado Tcl Shell中运行,但并不意味着无法与图形界面方式交互使用。在Vivado Tcl Shell中执行start_gui命令可以回到图形界面方式,利用图形界面方式对设计进行分析,分析完毕后可以执行stop_gui命令返回Vivado Tcl Shell。

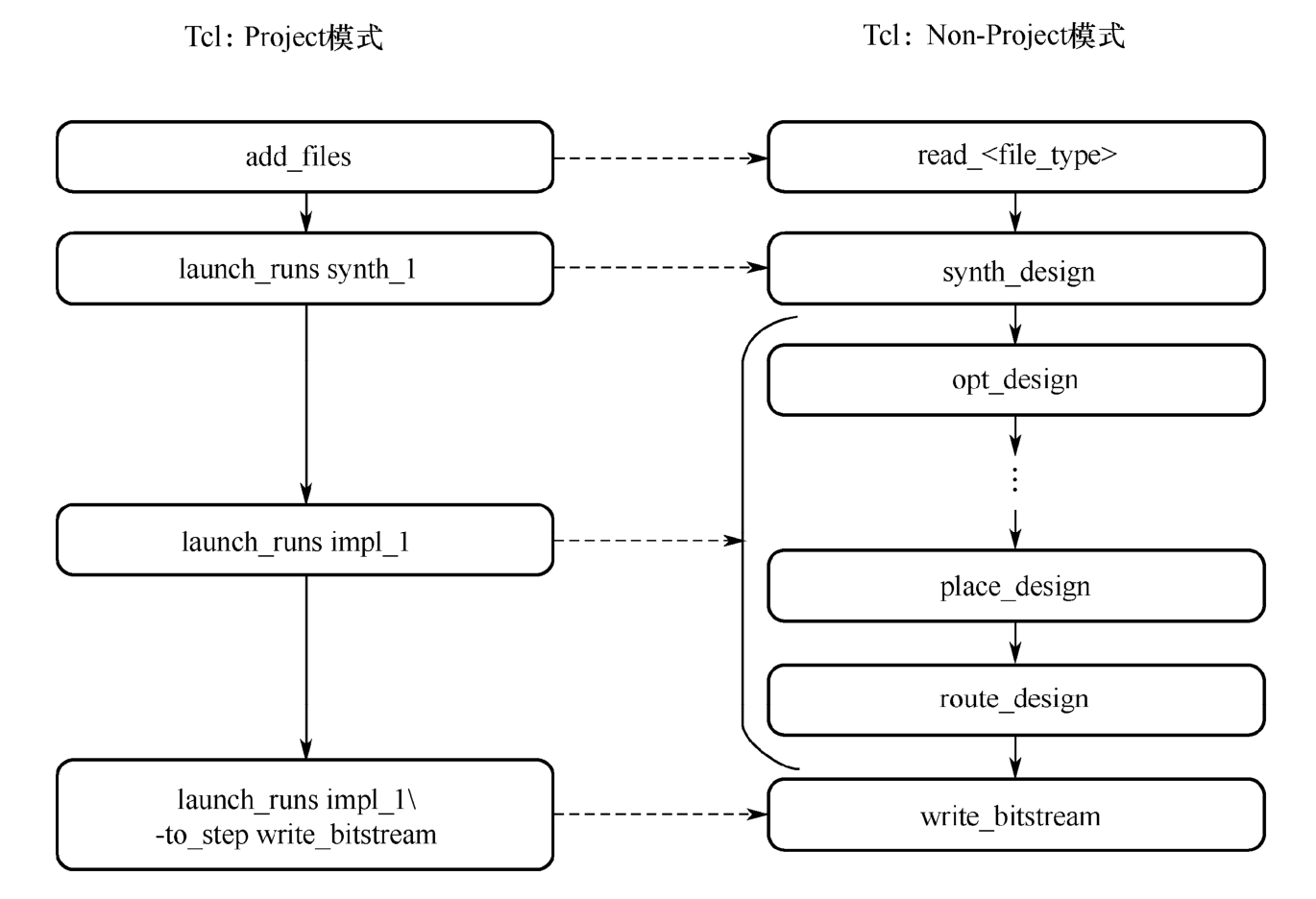

尽管Project和Non-Project均可采用Tcl脚本运行,但两者用到的Tcl命令是不一致的且不可混用,如图1.30所示。

图1.30 Project模式和Non-Project模式下的Tcl命令对比

Project模式的优势在于可以设定多个runs以比较不同综合策略或实现策略对设计结果的影响,而Non-Project模式的优势在于设计源文件、设计流程和生成文件可全部定制,相比Project模式有更短的运行时间。

与前一代开发平台ISE相比,Xilinx新一代开发平台Vivado有5个显著的特征,这5个特征也体现了与ISE的重大差异。

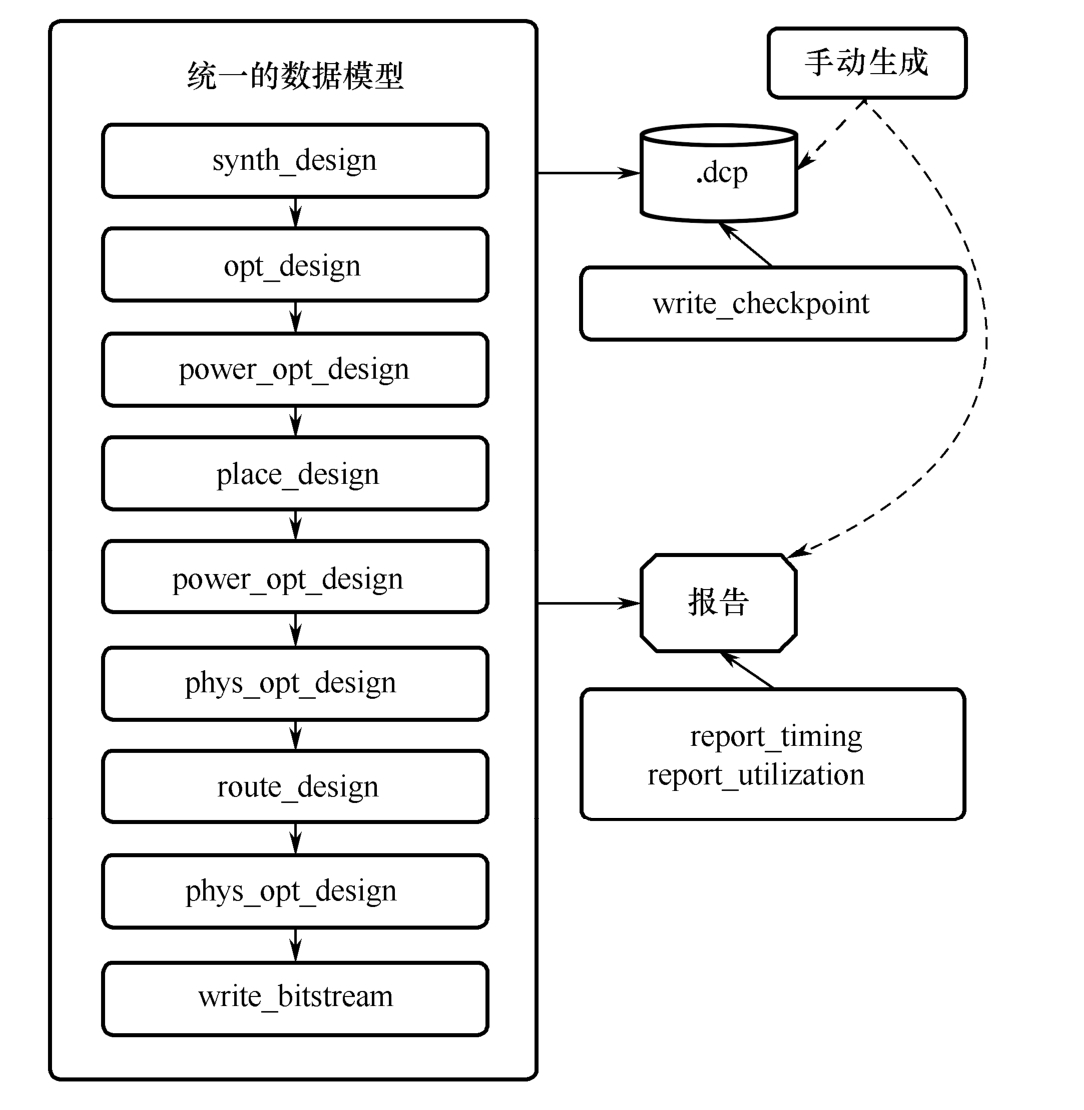

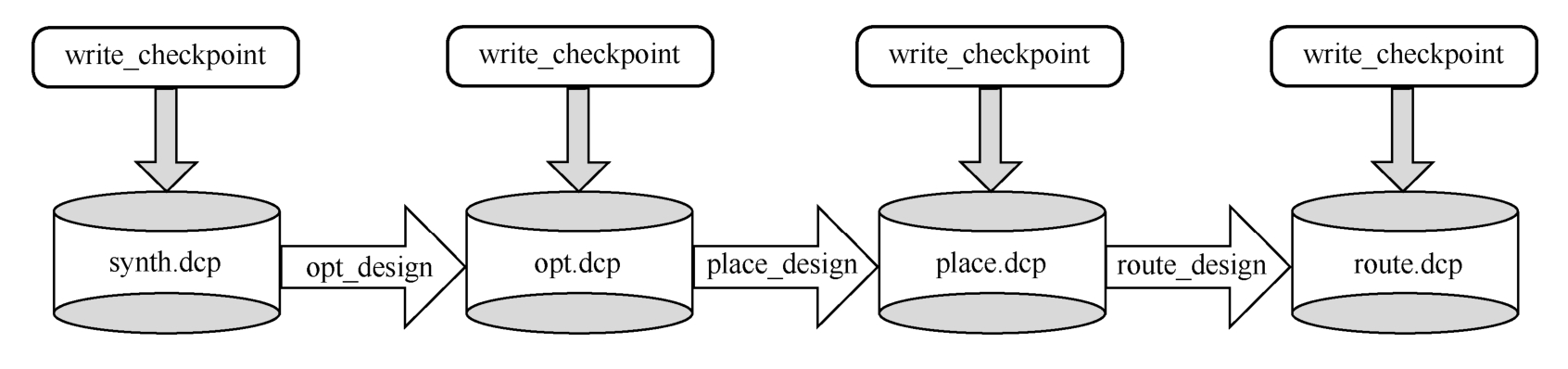

在ISE中,综合后的网表文件为.ngc,Translate之后的网表文件为.ngd,布局、布线之后的网表文件为.ncd;在Vivado下,综合和实现之后的网表文件均为.dcp。DCP成为统一的数据模型,如图1.31所示。

图1.31 统一的数据模型DCP

在Vivado中,约束采用XDC描述,它是在SDC的基础上进行了扩展,添加了Xilinx特定的物理约束。相比ISE中UCF描述的约束方式,XDC更为灵活。

Vivado融合了Tcl脚本,几乎所有的菜单操作都有相应的Tcl命令,而且用Tcl可以实现菜单无法操作的功能,如编辑综合后的网表文件。事实上,XDC本身就是Tcl命令。除此之外,用户也可以编写自己的Tcl命令嵌入Vivado中。Vivado提供了Tcl控制台(Tcl Console)和Tcl Shell用来运行Tcl脚本。

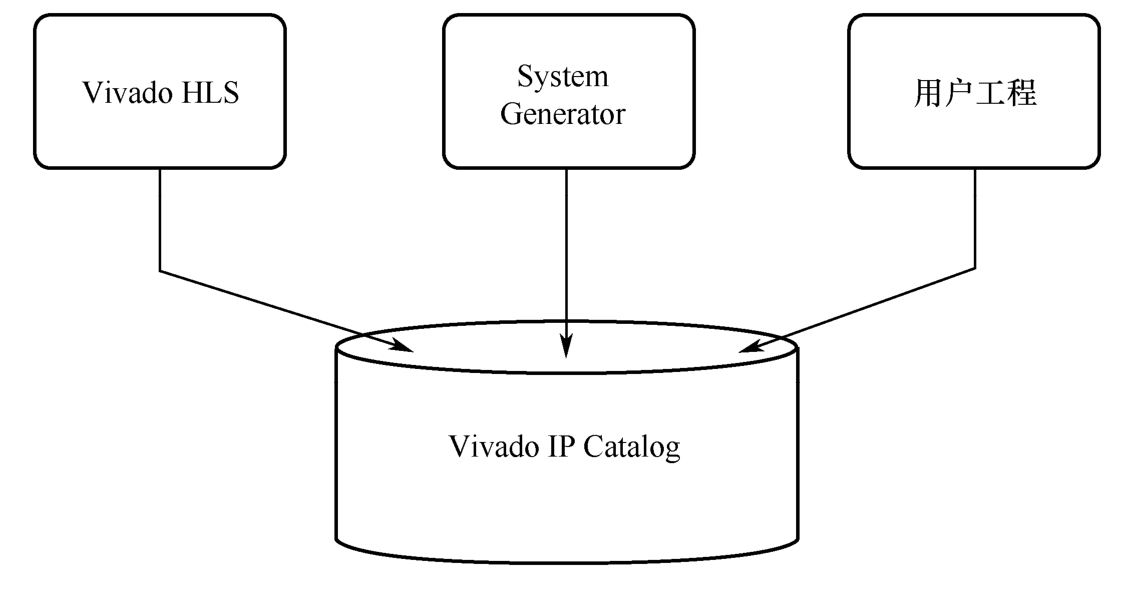

Vivado提供了以IP为核心的设计理念,以实现最大化的设计复用,如图1.32所示。Vivado HLS和System Generator两个工具都可以将自身设计封装为IP嵌入Vivado IP Catalog中。此外,用户自己的工程也可以通过Vivado下的IP Packager封装为IP嵌入Vivado IP Catalog中。

Xilinx提出的UltraFast设计方法学其根本宗旨是将问题尽可能地放在设计初期解决,而不要等到设计实现阶段才着手解决。因为在设计初期解决问题的方式更为灵活,措施也更为多样;而到后期,往往只能在局部小范围内修正,常会出现调试好了A模块,B模块又出问题的情况,甚至面临不得不返工的窘境。Vivado将这一方法学贯穿其中,在RTL设计分析阶段可以进行设计检查,检查内容包括代码风格和时序约束。在综合后可以分析时序,发现潜在的布线拥塞问题。与ISE不同,Vivado综合后的时序报告是可信任的。

图1.32 Vivado以IP为核心的设计理念