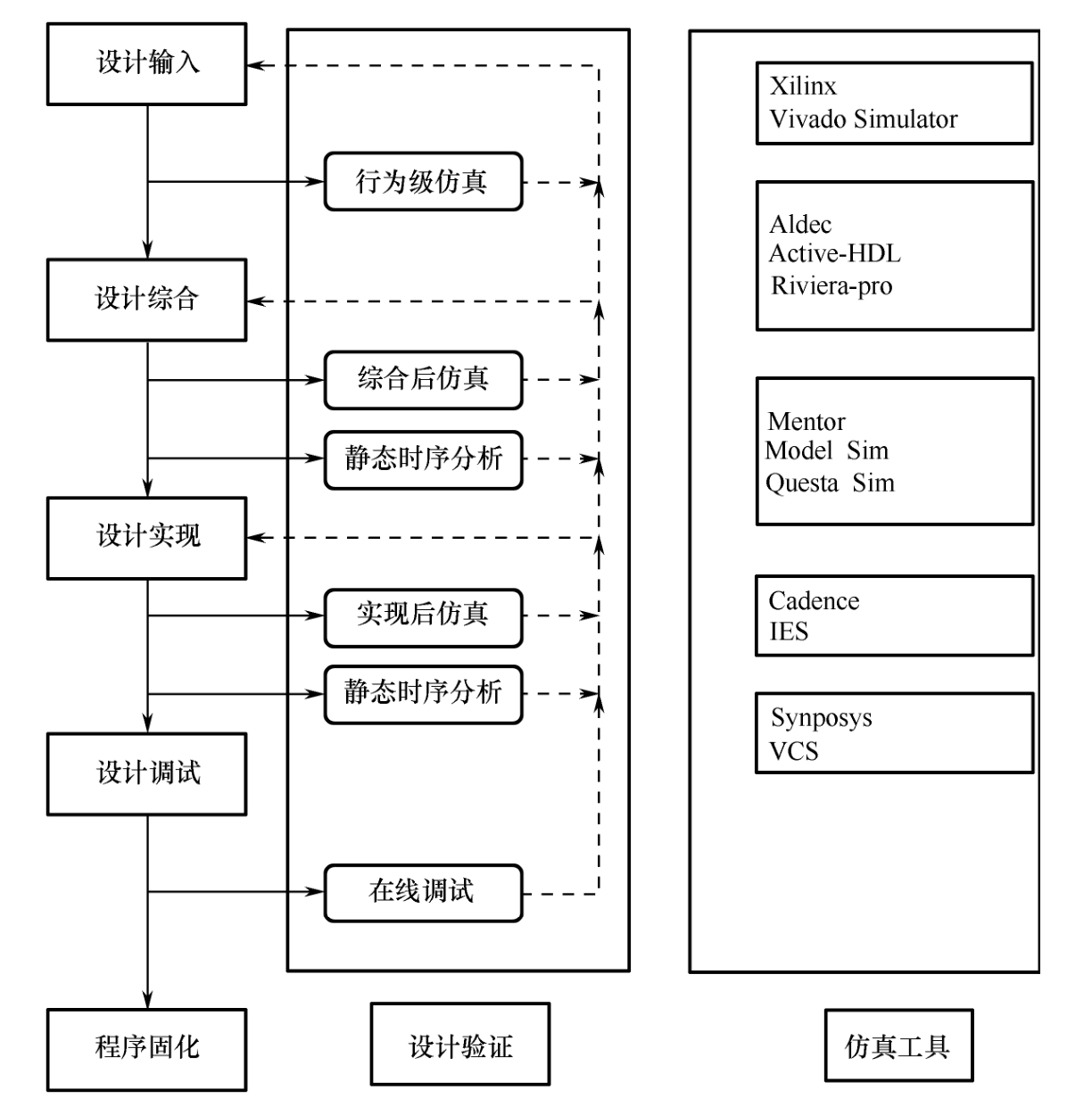

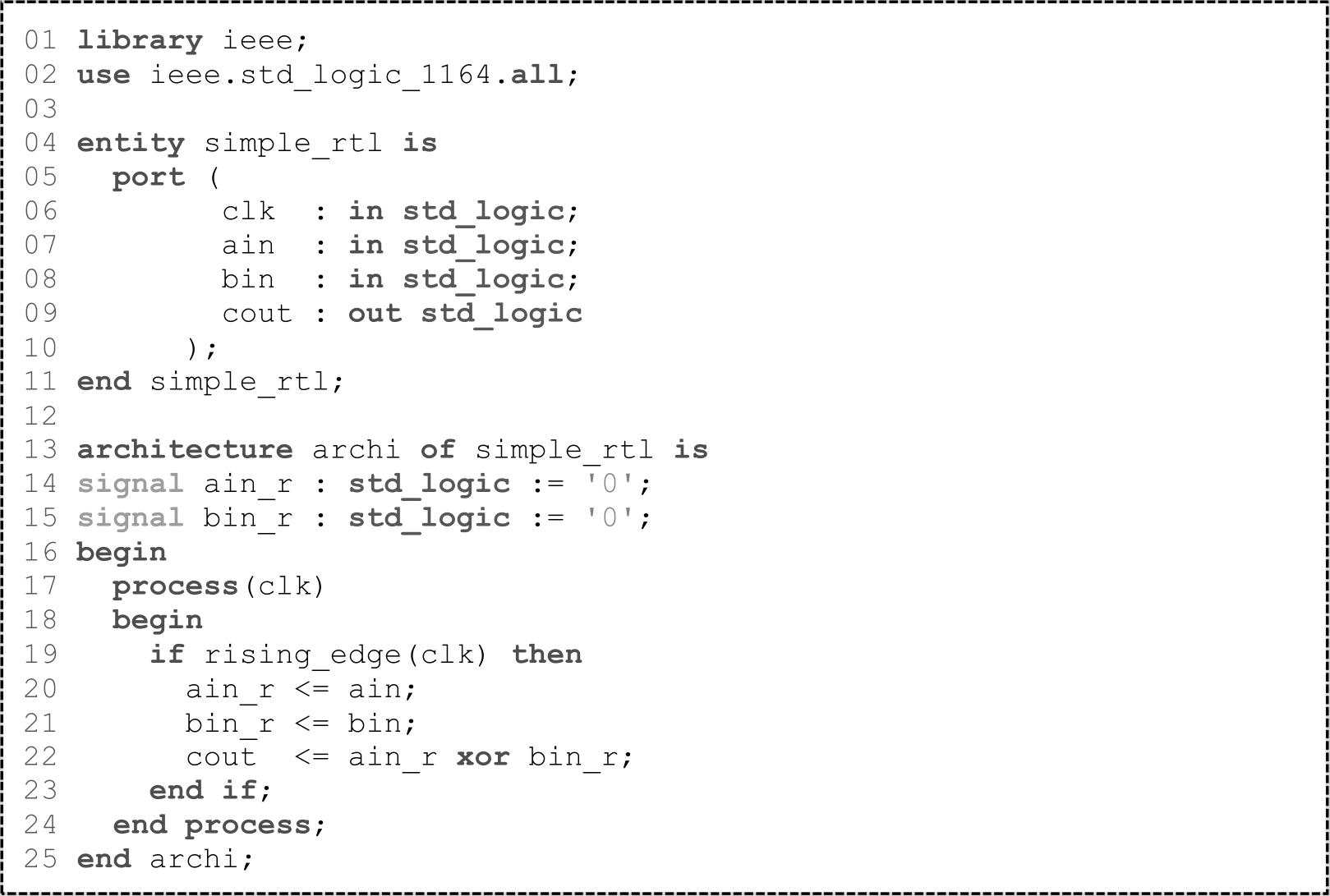

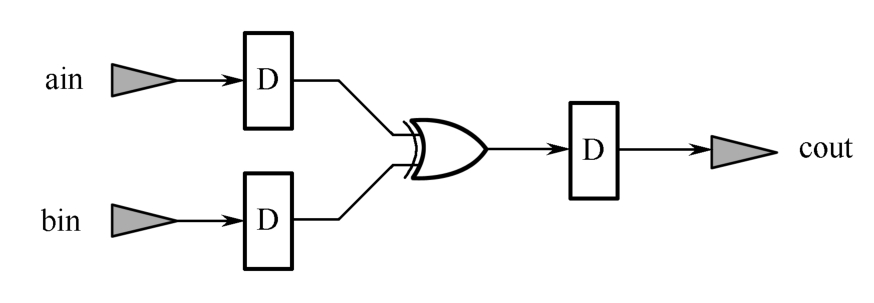

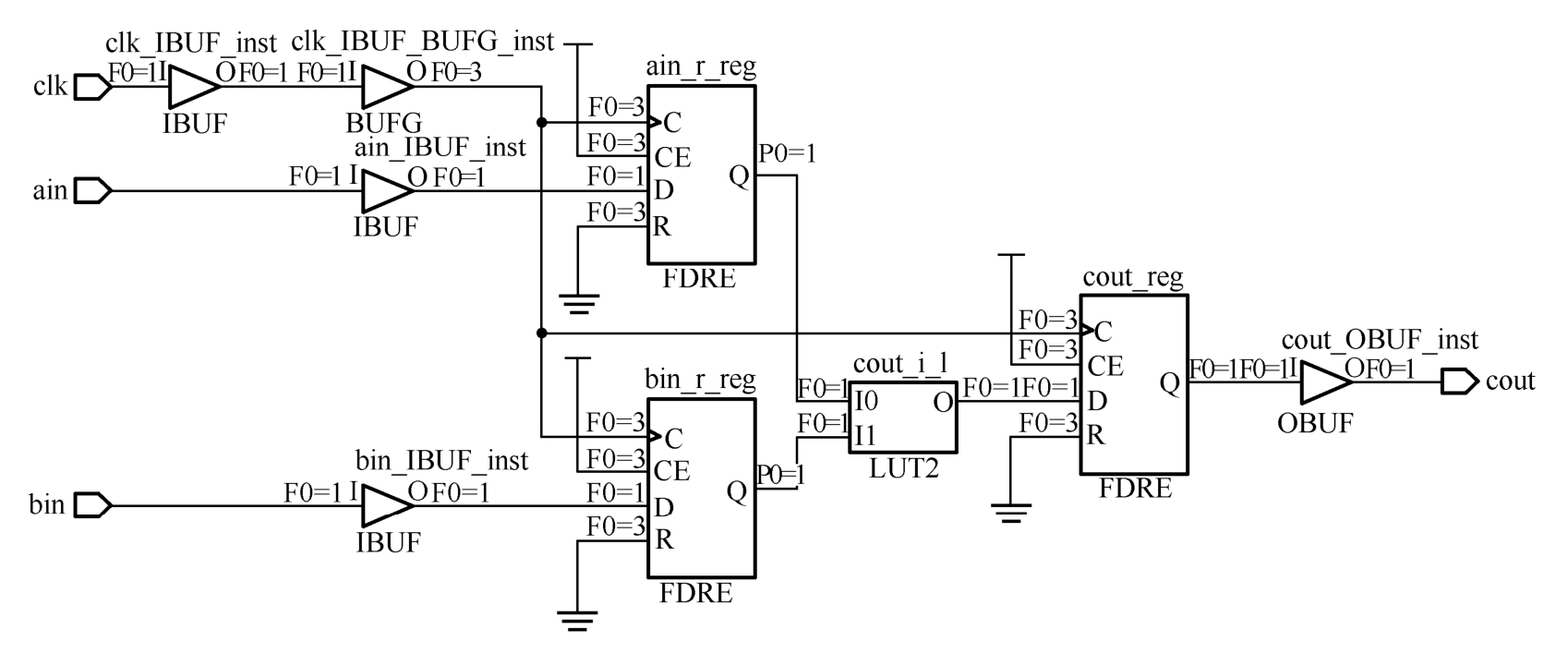

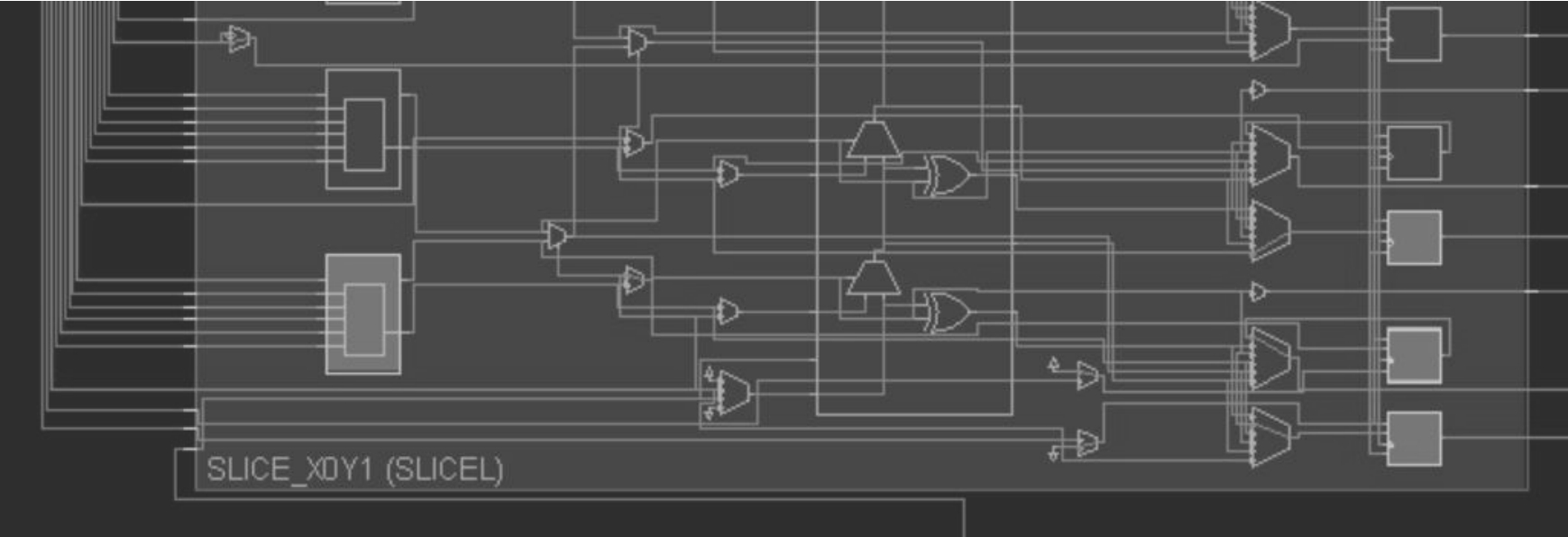

传统的FPGA设计流程如图1.19所示。设计输入支持HDL代码,如VHDL、Verilog和System Verilog,也支持厂商提供的IP,同时还应提供FPGA工程约束文件,如引脚分配、时序约束。设计综合(Synthesis)则完成HDL代码到硬件电路的转化与映射并生成网表文件。这一步与FPGA内部结构密切相关。为了便于说明,以VHDL代码1.17为例,其对应的电路结构如图1.20所示。采用Kintex-7作为目标芯片,综合后的结果如图1.21所示。可见,此时D触发器被映射为FDRE,异或运算映射为查找表。设计实现(Implementation)阶段主要完成布局和布线(Place and Route)。布局是将综合后的各个电路元件根据约束放置在FPGA内部。布线则是完成元件之间的走线。布局、布线后的结果如图1.22所示。设计调试则是将程序下载到FPGA中,借助测试仪器对设计进行分析。由于SRAM工艺的FPGA在掉电后程序会消失,因此需要将生成的下载程序转换为厂商要求的文件存储在片外Flash中,这即是程序固化。

图1.19 传统的FPGA设计流程

设计验证贯穿于FPGA设计的整个过程,包括两个部分:仿真和静态时序分析(Static Timing Analysis,STA)。设计输入阶段除了提供可综合的HDL代码外,还应提供用于仿真的测试文件(Testbench)。测试文件有两个功能:一是提供输入激励;二是对测试结果进行对比分析。其中将两个功能均具备的测试文件称为具有自我检查功能的测试文件。设计输入完成后即可进行行为级仿真(Behavioral Simulation),该阶段的仿真没有延时信息,只是功能上的验证,但在FPGA设计验证环节至关重要。综合后仿真分为功能仿真和时序仿真两种。前者的目的是验证综合后的电路与原本HDL所描述电路功能是否保持一致;后者则加入了门级延时信息,可进一步分析设计时序。实现后仿真也分为功能仿真和时序仿真,其目的与综合后仿真一致,只是实现后的时序仿真不仅加入了门级延时信息,还包含了走线延时信息,使得仿真与FPGA本身的运行状态保持一致。仿真工具既可以选用FPGA厂商自己的工具,也可以选用第三方仿真工具。静态时序分析建立在约束(时序约束和物理约束,如面积约束、位置约束等)的基础上,对设计进行时序检查和分析。之所以进行时序分析,是因为FPGA本身存在固有延时,而综合和布局布线又会引入门级延时和走线延时,这些延时可能导致时序违例(建立时间或保持时间不能满足FPGA要求)。因此,只有仿真通过且没有时序违例的设计才可能在FPGA中正常运行。图1.19中的虚线还表明FPGA设计是一个反复迭代的过程,如在设计实现后发现时序违例,那么首先可能需要修改实现策略,也可能需要返回设计输入阶段优化HDL代码,然后重新综合、实现。

图1.20 VHDL代码1.17对应的电路结构

图1.21 VHDL代码1.17综合后的结果

图1.22 VHDL代码1.17布局、布线后的结果