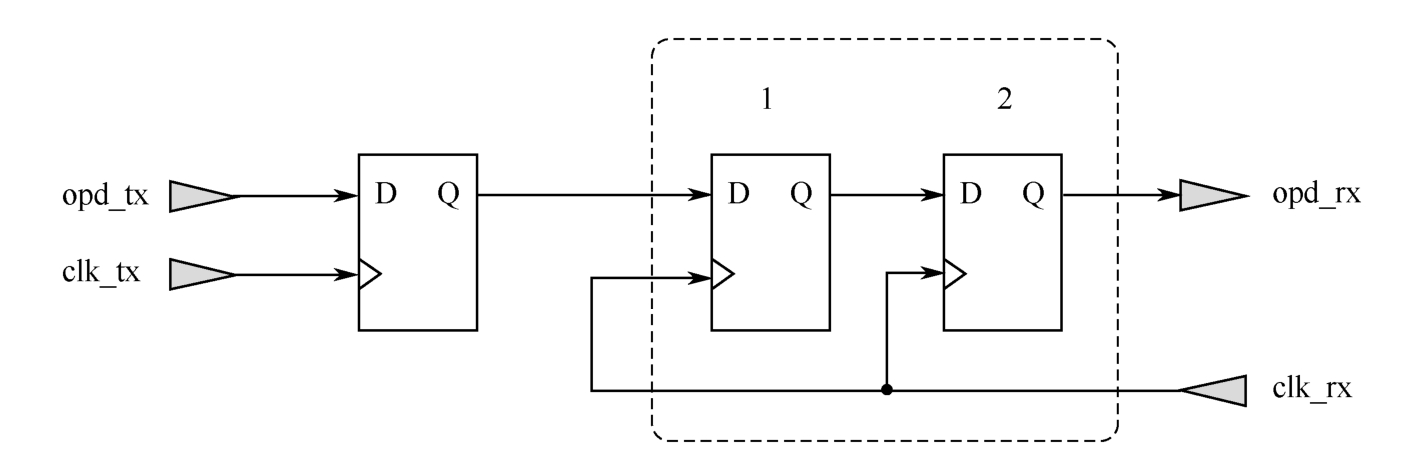

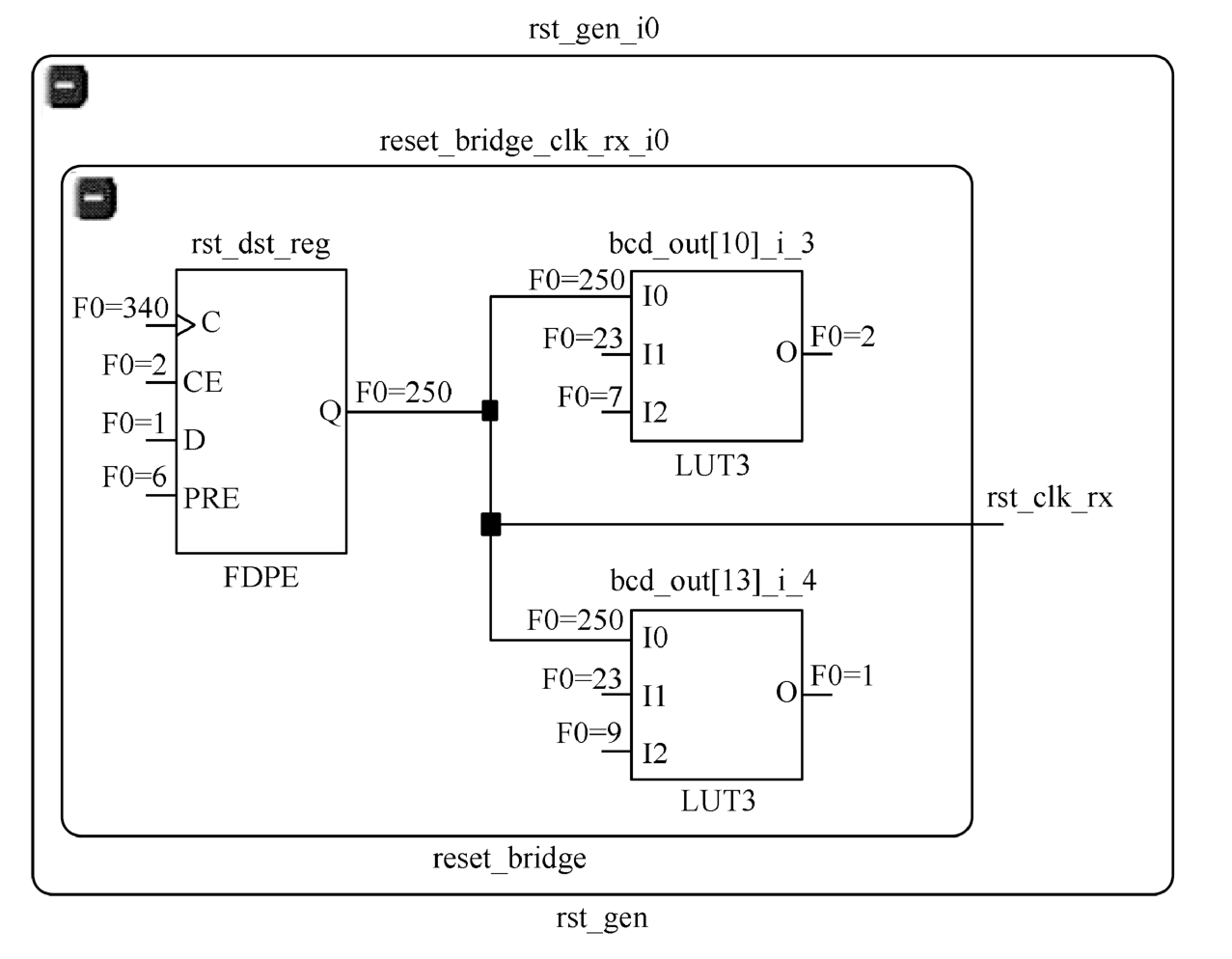

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器方法完成跨时钟域操作,如图2.21所示。此时对于图中标记的1号触发器需要使用综合属性async_reg,有以下两个目的:

(1)表明1号触发器接收的数据是来自与接收时钟异步的时钟域;

(2)表明2号触发器是同步链路上的触发器。

从而,保证1号、2号触发器在布局时会被放置在同一个SLICE内,减少线延迟对时序的影响。

图2.21 双触发器方法

async_reg的使用方法如VHDL代码2.10所示。

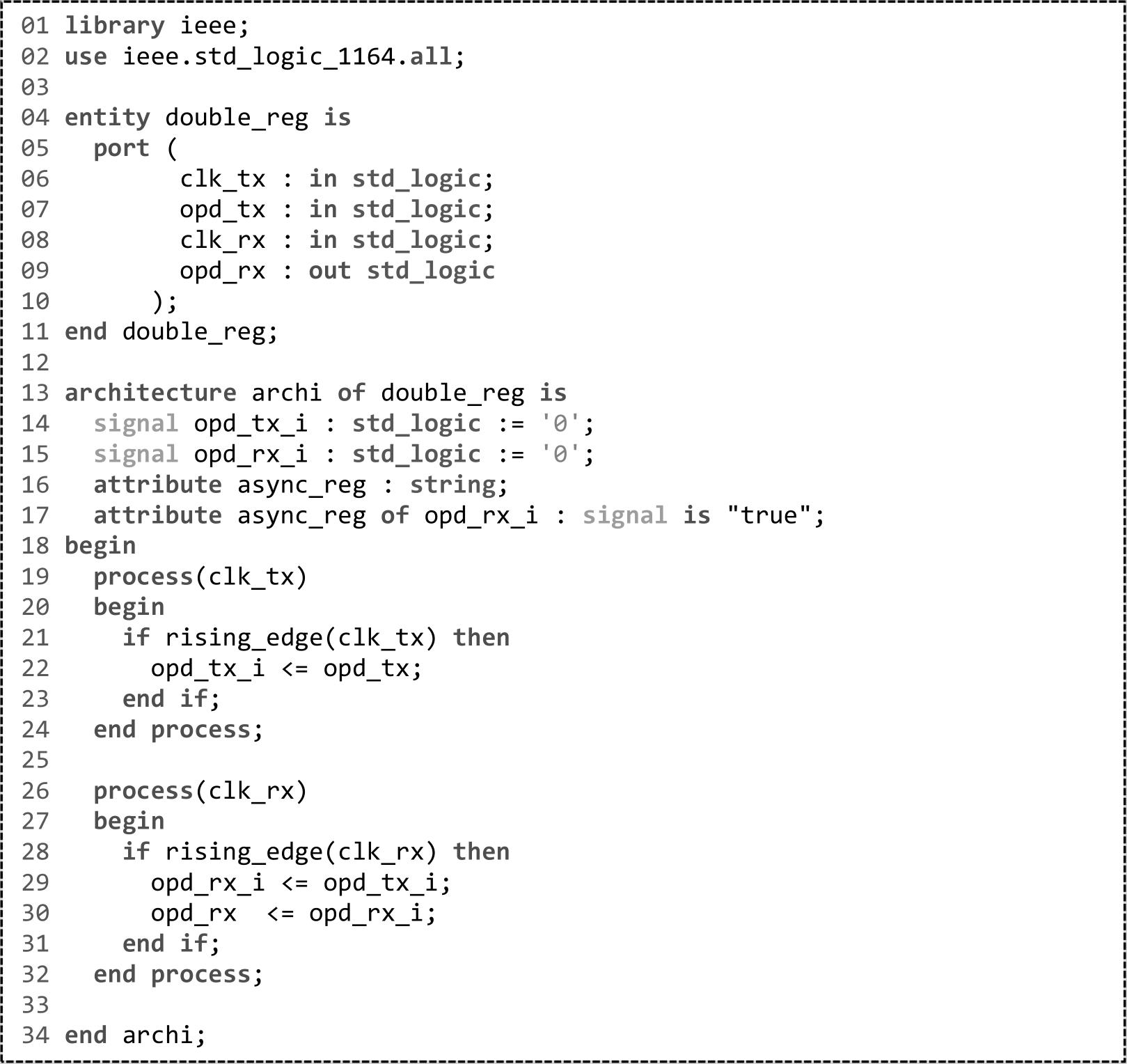

高扇出信号可能会因为布线拥塞而导致时序问题,常用的处理方法是通过寄存器复制以降低扇出。一种方法是可以手工采用HDL代码复制寄存器,但此时要注意确保综合时复制的等效寄存器不会被优化掉;另一种方法则是通过综合属性max_fanout实现寄存器复制。

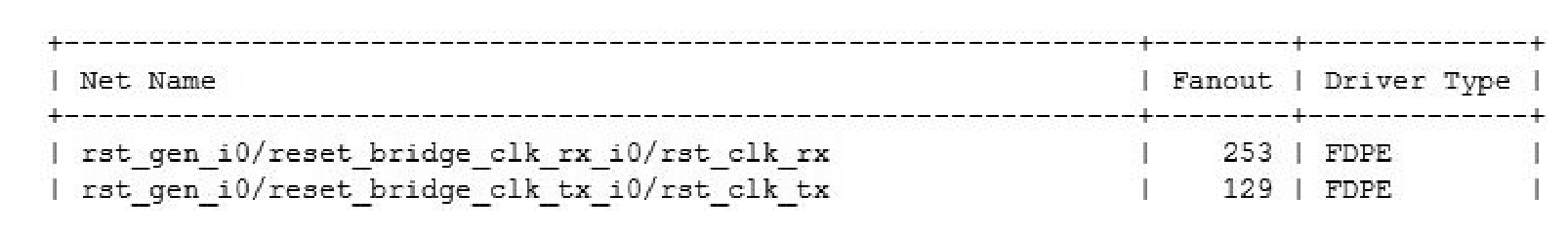

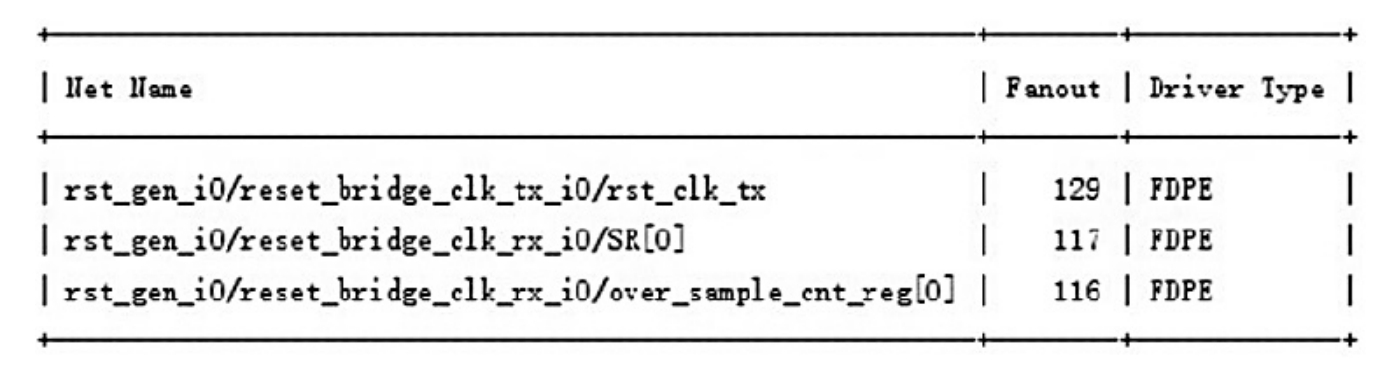

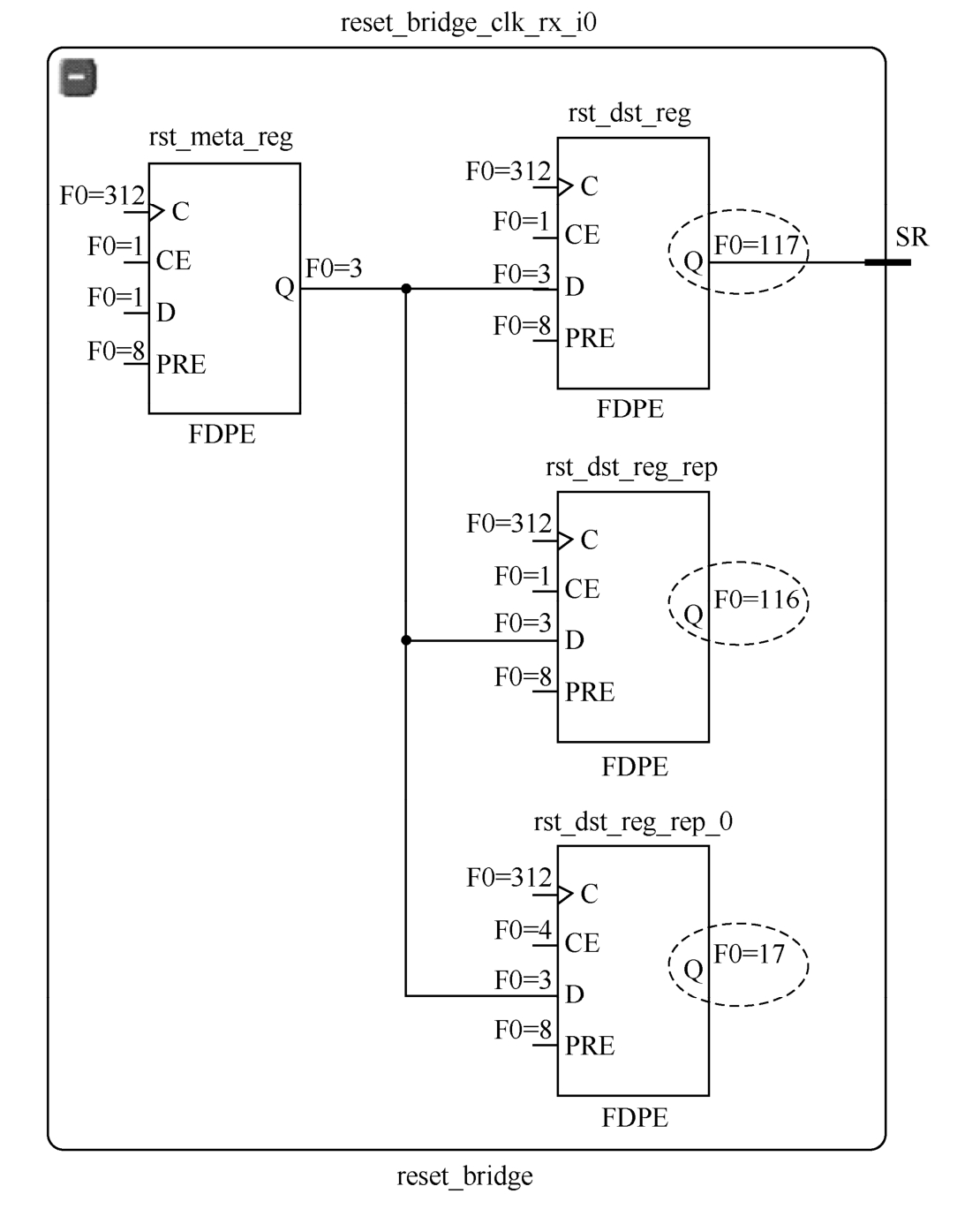

仍以Vivado自带的例子工程Wavegen为例,综合后通过report_high_fanout_nets可以找到该设计中的高扇出网线,如图2.22所示,该网线的Schematic视图如图2.23所示。

图2.22 高扇出信号列表

图2.23 rst_clk_rx的Schematic视图

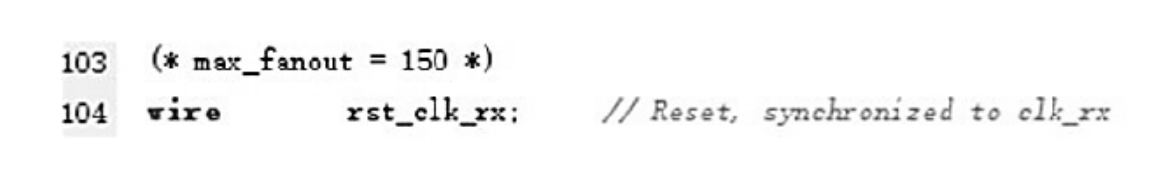

为了将rst_clk_rx的扇出降低到150,在原始的HDL代码中使用max_fanout(注意,括号和星号之间没有空格),如图2.24所示。

图2.24 在HDL代码中使用max_fanout

综合后再次通过report_high_fanout_nets命令找到扇出较大的网线,如图2.25所示,可以看到,此时rst_clk_rx的扇出已经降低。为了进一步确定,可观察其Schematic视图,如图2.26所示。显然,此时rst_clk_rx已经被赋值为3个寄存器,每个寄存器的扇出分别为117、116和17,总扇出保持不变。

使用max_fanout时,不用勾选综合选项中的-keep_equivalent_registers,因为本身max_fanout的作用就是复制寄存器,而且被复制的等效寄存器在后续实现时也不会被优化掉。

图2.25 使用max_fanout后显示的大扇出网线

图2.26 使用max_fanout后rst_clk_rx被复制之后的Schematic视图

尽管在Vivado综合选项中由-fanout_limit来控制扇出,但它是全局指导,对于局部某个网线,max_fanout的优先级要高于-fanout_limit。

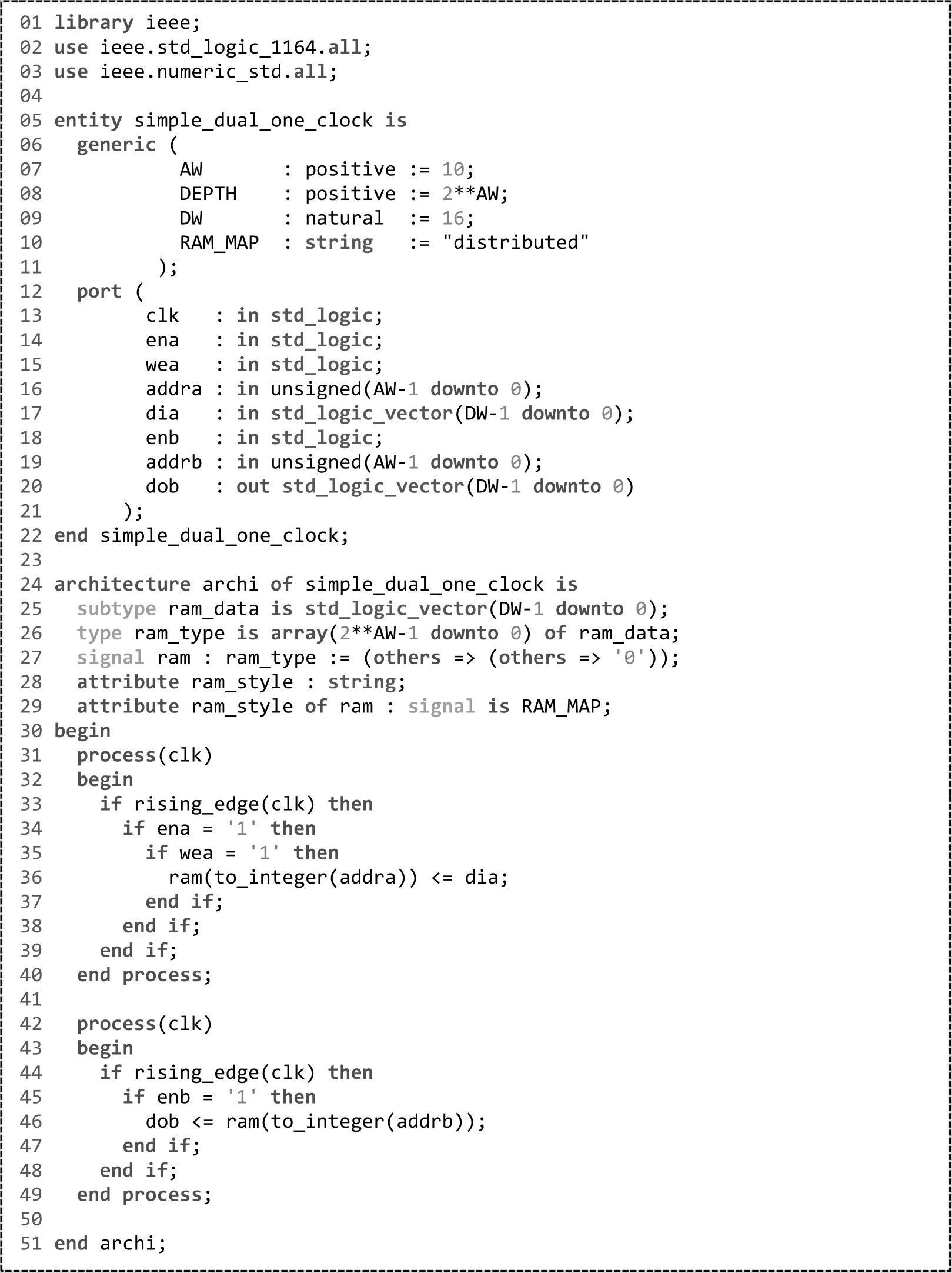

在Xilinx FPGA中,既可以采用分布式资源(查找表)也可以采用BRAM实现RAM。对于手工编写的HDL代码所描述的RAM,在默认情况下,Vivado会通过内部算法给出最优结果。此外,也可以通过ram_style指导工具推断RAM的实现方式。该属性有3个值:block(将RAM映射为BRAM)、distributed(将RAM映射为分布式资源)和registers(指导工具推断为寄存器而非RAM)。

VHDL代码2.11描述的是一个时钟的简单双端口RAM可以通过ram_style映射为分布式资源,其中RAM_MAP(在generic中声明)的值为distributed,采用这种方法是为了实现综合属性的参数化管理。

对于两个时钟的简单双端口RAM,也可以通过ram_style映射为分布式资源,但是对于真正的双端口RAM,即便将ram_style设置为distributed,RAM仍将通过BRAM实现。

rom_style与ram_style有同样的功能,只是它针对的是ROM,且只有两个值block和distributed。

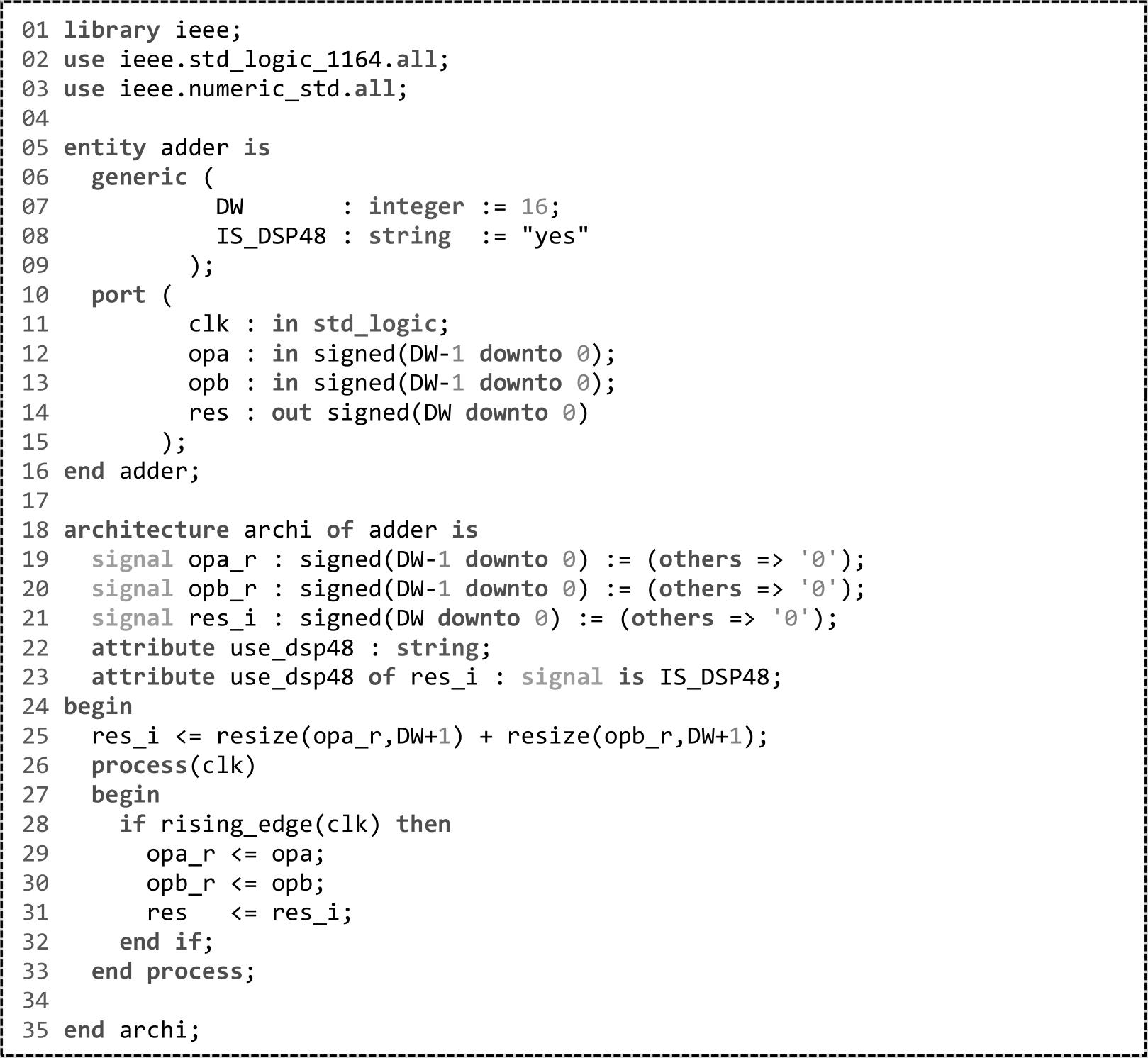

在Vivado中,默认情况下用HDL描述的乘法、乘加、乘减、乘累加及预加相乘最终都会映射到DSP48中,但是加法、减法和累加运算会用常规的逻辑资源,即查找表、进位链等来实现。相比查找表,DSP48在功耗和速度上都有优势。如果期望加法运算也能映射到DSP48中,就要用到综合属性use_dsp48。该属性可作用于entity/module、architecture、component、signal。

采用VHDL描述加法运算并使用该属性的相应代码,如VHDL代码2.12所示。综合后,该模块只占用了一个DSP48E1(目标芯片为7系列FPGA),其中的寄存器也一并被吸收到DSP48E1内部。

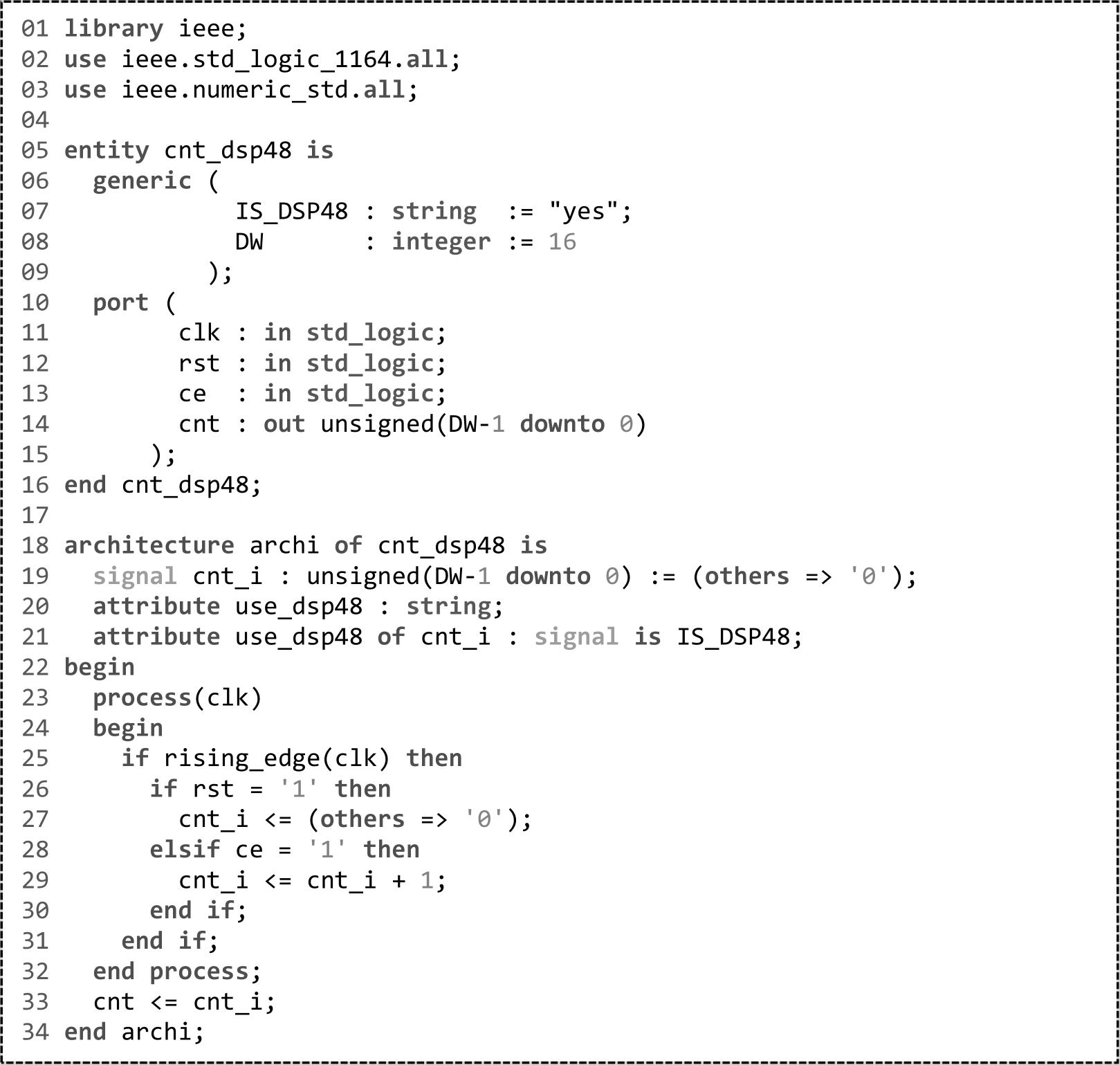

对于FPGA设计中常用的计数器,也可以采用use_dsp48属性使其映射到DSP48上,如VHDL代码2.13所示。代码中IS_DSP48的值为yes。

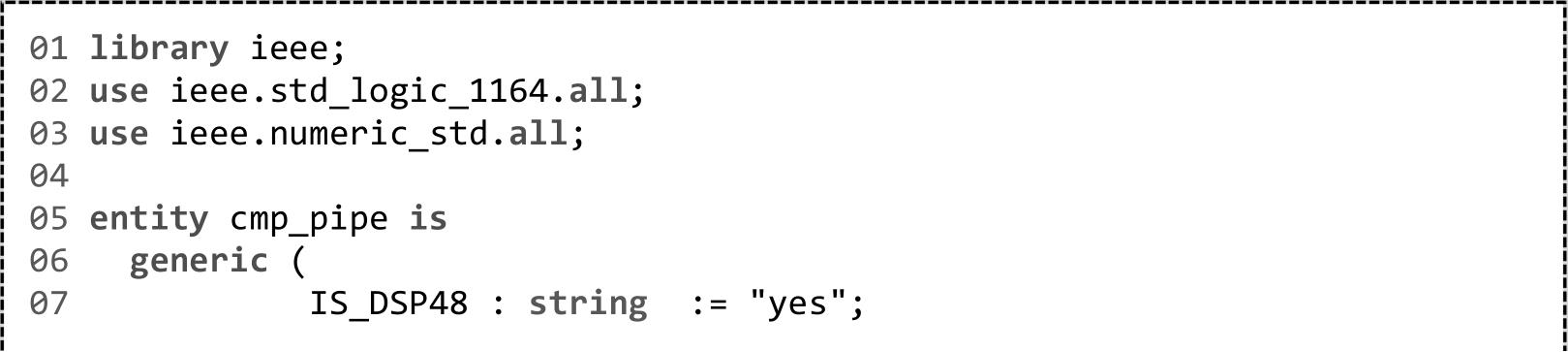

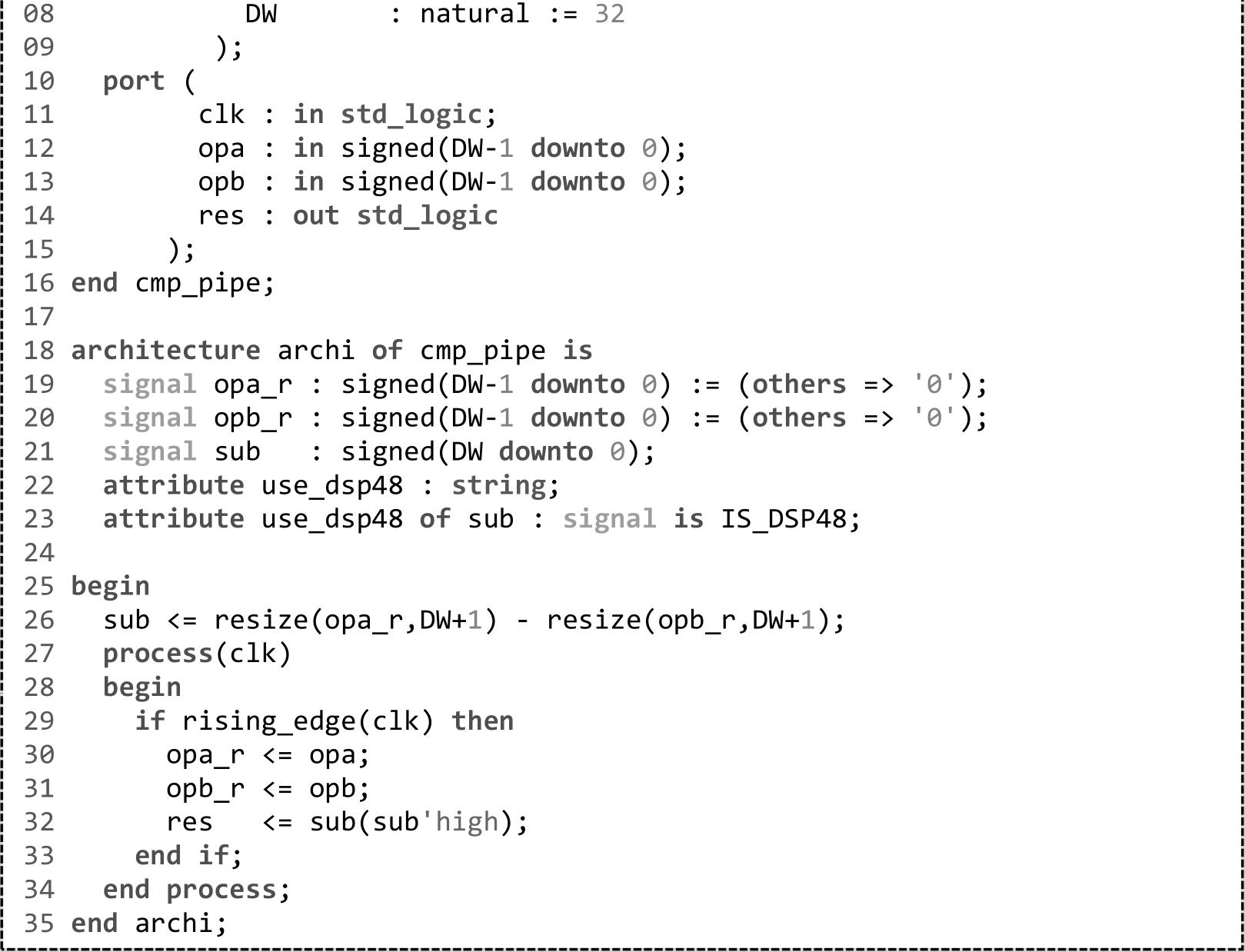

对于关系运算,也可以转换成算术运算通过DSP48实现。例如,opa<opb意味着opa-opb<0,这时只需取opa-opb结果的最高位,即符号位进行判断,若符号位为1,则表明opa<opb,相应的代码如VHDL代码2.14所示。

当该属性作用于entity/module时,该模块内的所有加法/减法运算都将采用DSP48实现。