原理图输入(schematic entry)是模拟集成电路设计的第一步,包括原理图设计和符号图设计两个环节,下面对操作流程进行具体介绍。

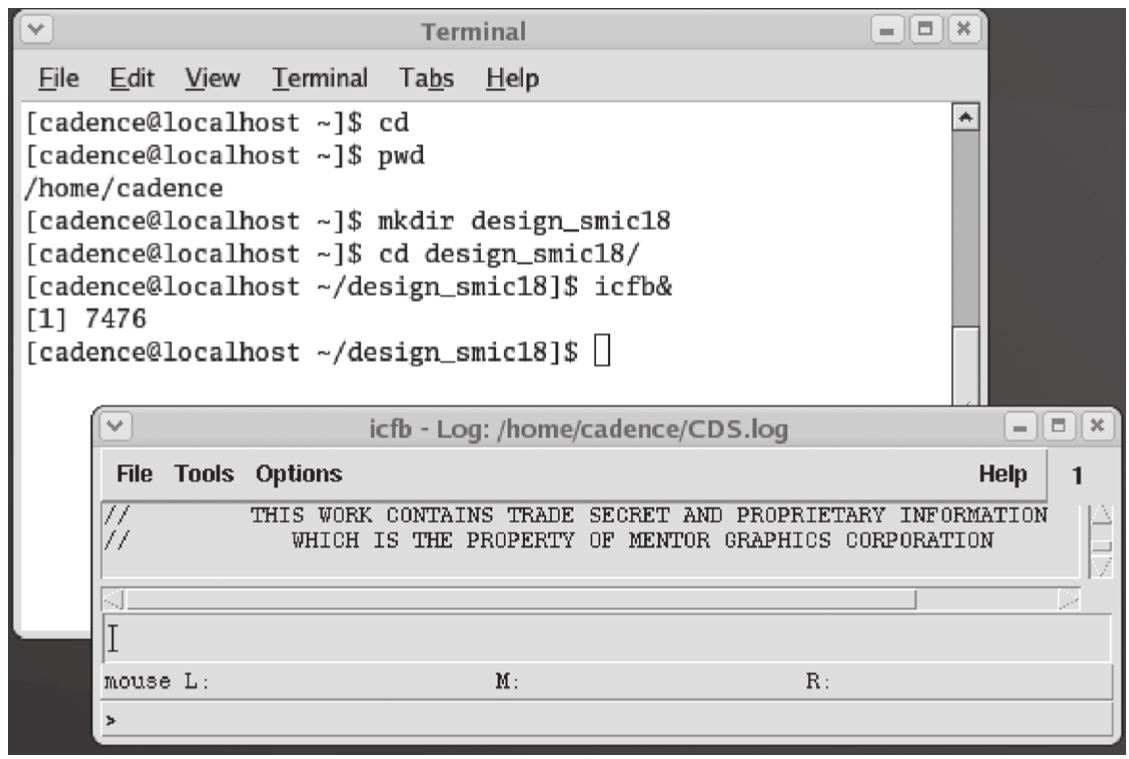

通过终端窗口输入命令,在自己的home目录下新建一个文件夹design_smic18,然后进入这个文件夹,输入命令icfb&来启动Cadence,或者输入virtuoso&来启动617版。图2.44所示为相应的shell命令和启动的Cadence主窗口(Command Interpreter Window,CIW)。

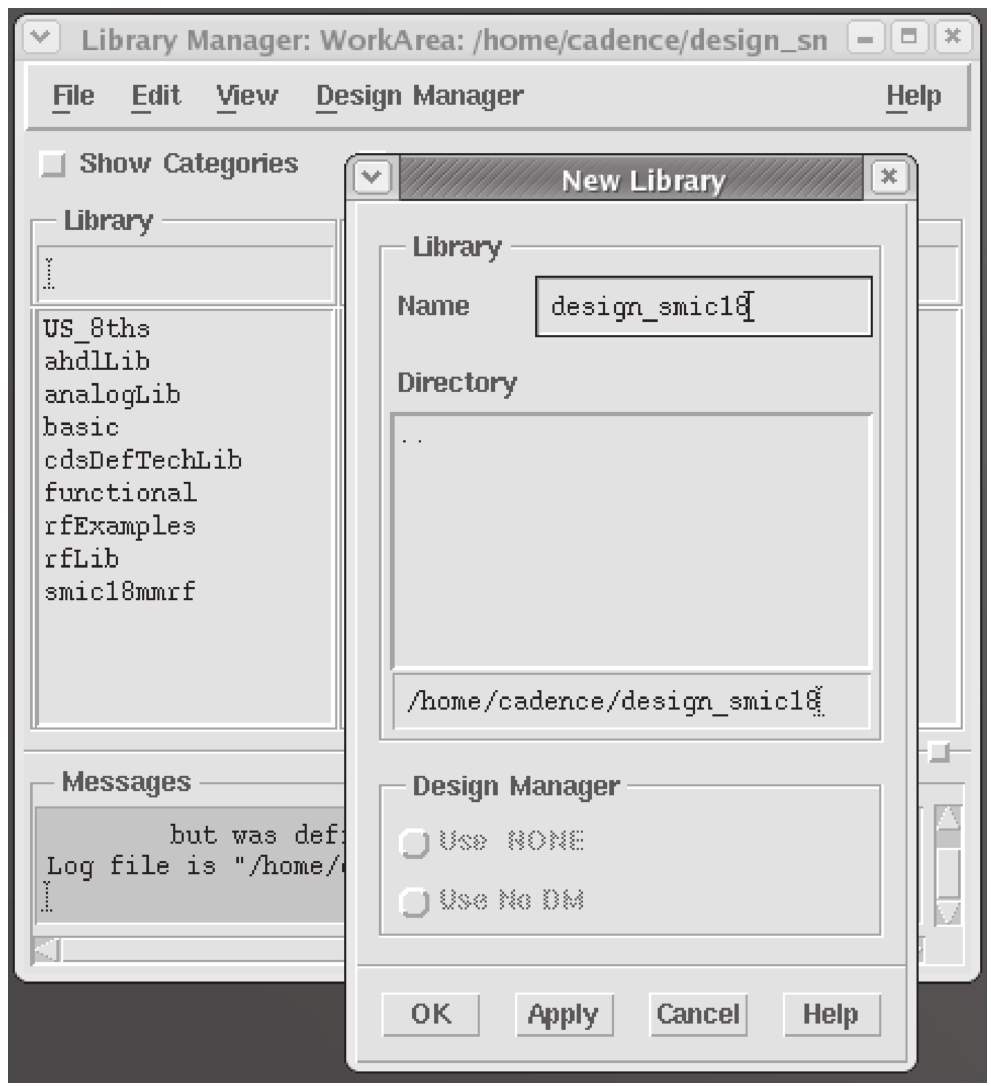

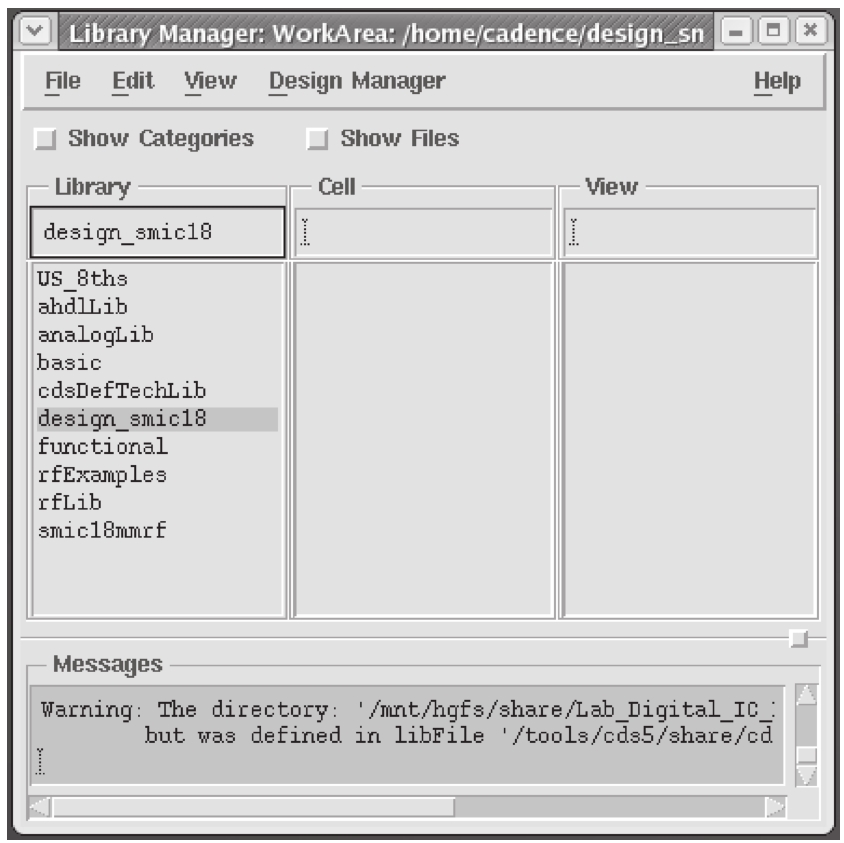

通过Cadence主菜单的Tools→Library Manager...打开Library Manager窗口,选择Library Manager菜单的File→New→Library...打开New Library对话框,输入库名字design_smic18后单击OK按钮,如图2.45所示。

图2.44 shell命令和Cadence主窗口

图2.45 New Library对话框

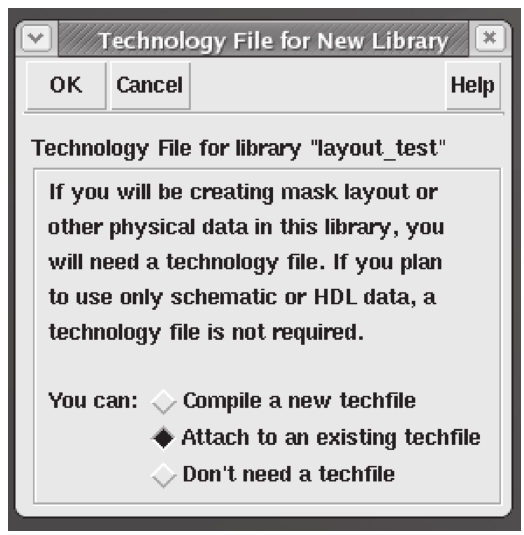

在弹出的Technology File for New Library对话框中,选择中间的Attach to an existing techfile选项,单击OK按钮,如图2.46所示。

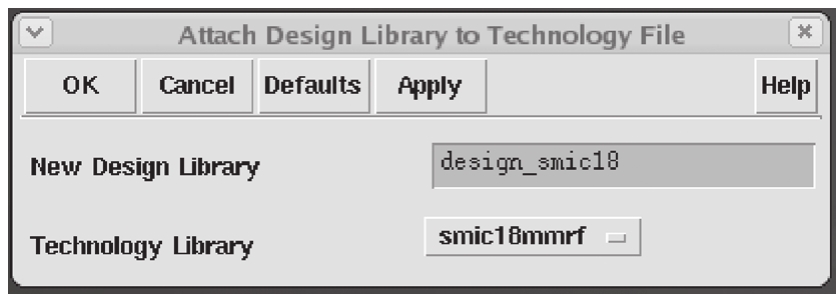

在弹出的Attach Design Library to Technology File对话框中,选择smic18mmrf,然后单击OK按钮,如图2.47所示。这样就建成一个关联了SMIC 0.18μm CMOS工艺的设计库,在Library Manager窗口中可以查看到它,此时这个库是空的,在Cell和View栏中都没有内容,如图2.48所示。

图2.46 Technology File for New Library对话框

图2.47 Attach Design Library to Technology File对话框

图2.48 在Library栏中查看design_smic18库

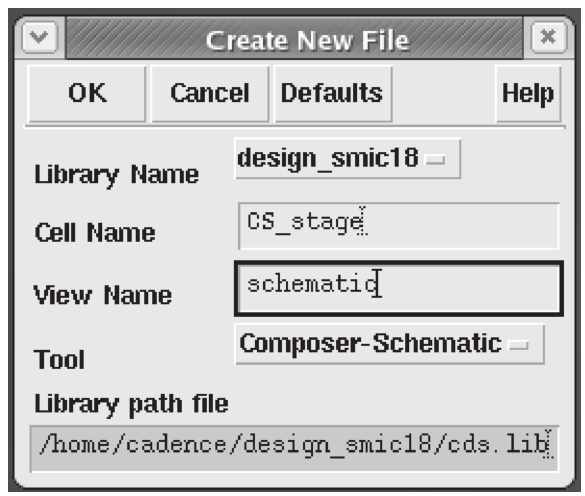

在Library Manager窗口选中design_smic18库,通过菜单File→New→Cell View...打开Create New File对话框,在Cell Name栏中输入CS_stage,即Common-Source Stage的缩写,然后在Tool栏中选择Composer-Schematic,此时View Name栏会自动变成schematic(不能手动输入),如图2.49所示,然后单击OK按钮。

图2.49 Create New File对话框

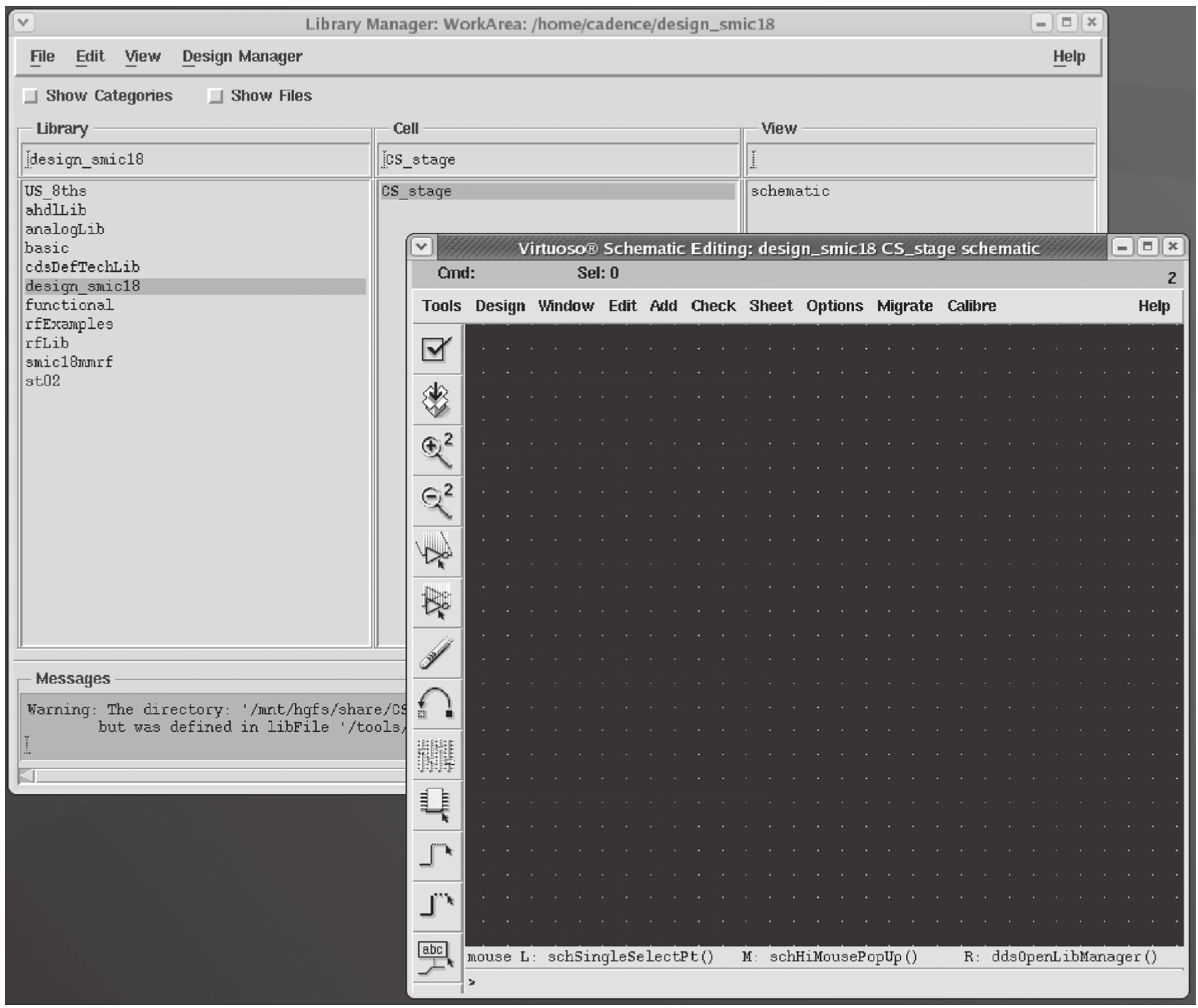

单击OK按钮后得到如图2.50所示的Virtuoso Schematic Editing窗口,原理图设计将在这个窗口中进行。另外,design_smic18库的Cell栏中增加了CS_stage,View栏中增加了schematic。

图2.50 Virtuoso Schematic Editing窗口

下面将要进行具体的设计,在设计过程中间难免会出现操作失误或错误,一旦发现错误请立刻按U键,这样可以撤回一步。5141版默认设置只能撤回一步,而617版默认设置可以撤回多步。

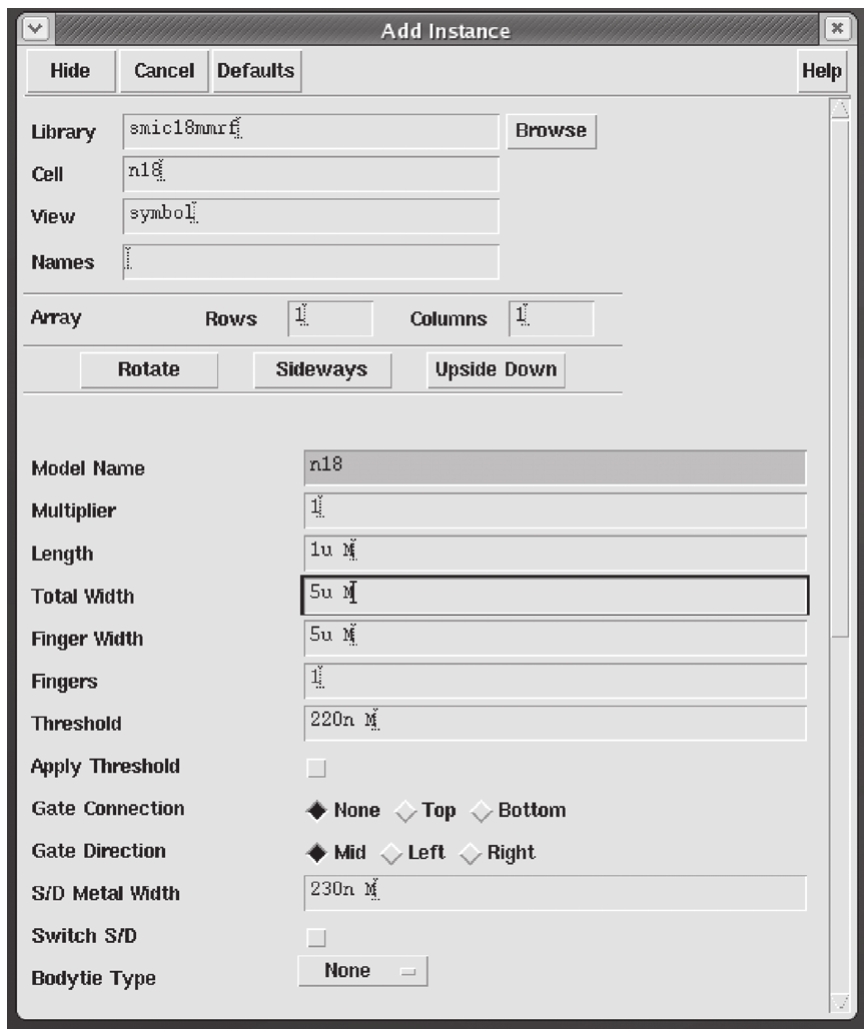

元件例化就是从目标工艺库中选择器件,并将其摆放到原理图窗口中的过程,本例的目标工艺库是smic18mmrf。放到原理图中的器件一般都是Pcell(参数化的器件),例化Pcell时需要填写它的主要参数。

本例的原理图需要从smic18mmrf库中挑选n18(NMOS管)和p18(PMOS管),它们都是工作电压为1.8V的MOS管,将n18的宽长比设置为 W / L =5μ/1μ,p18的宽长比设置为 W / L =15μ/1μ,现在主要是为了学习设计流程和EDA工具的使用,所设置的宽长比可能不是最优的。

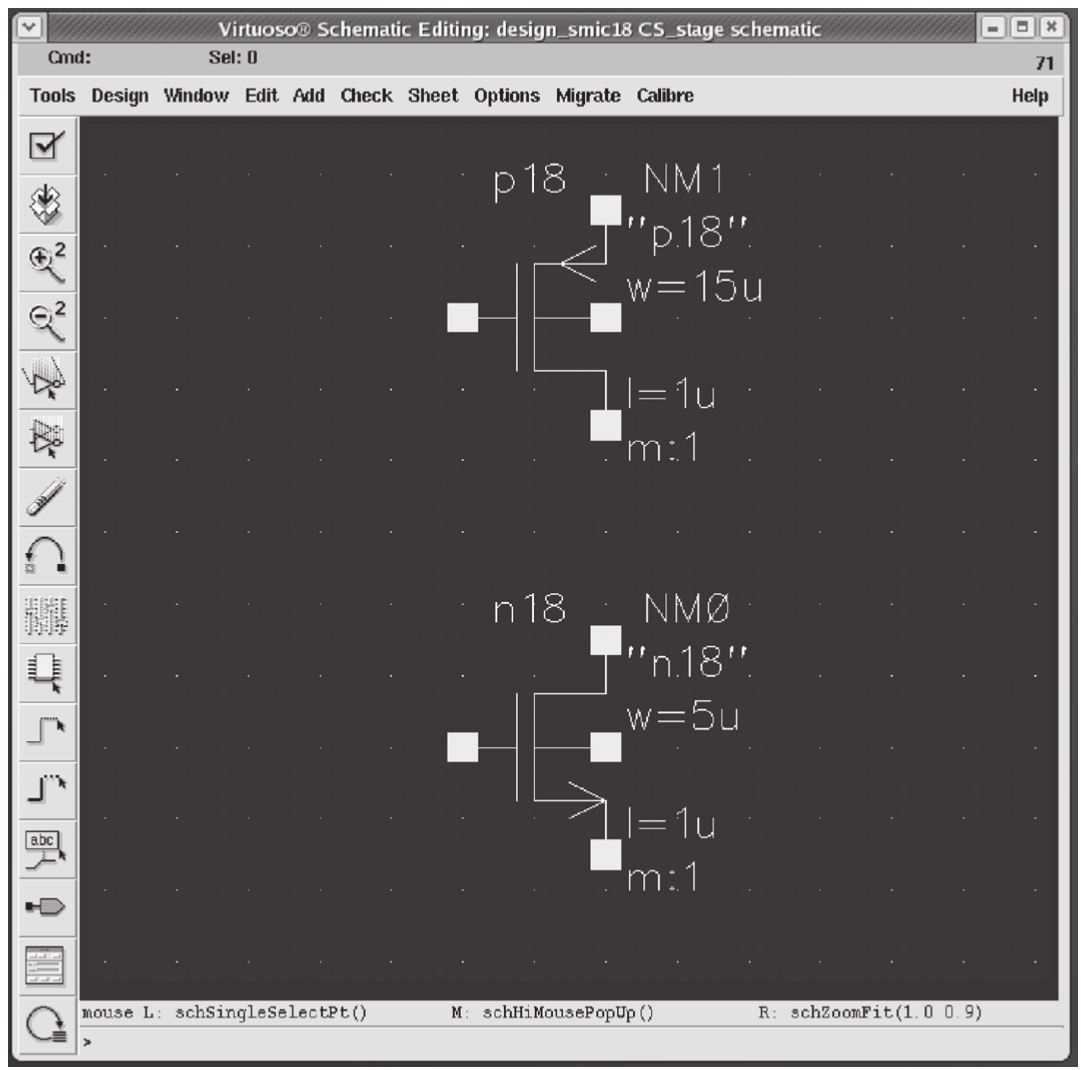

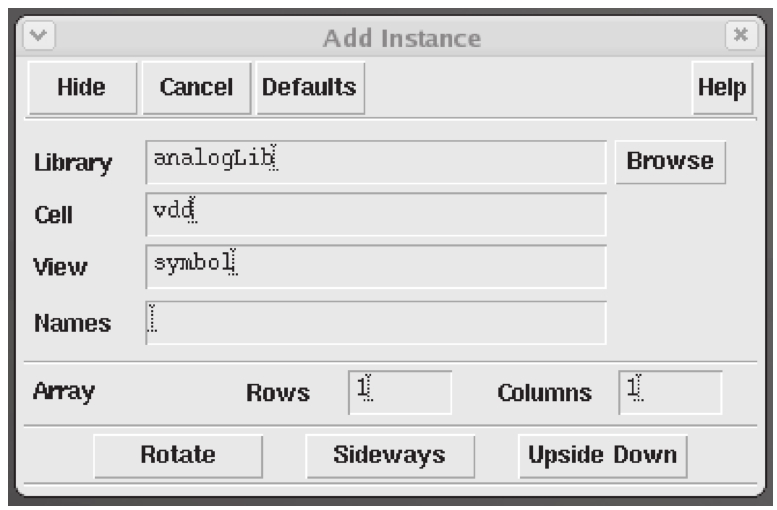

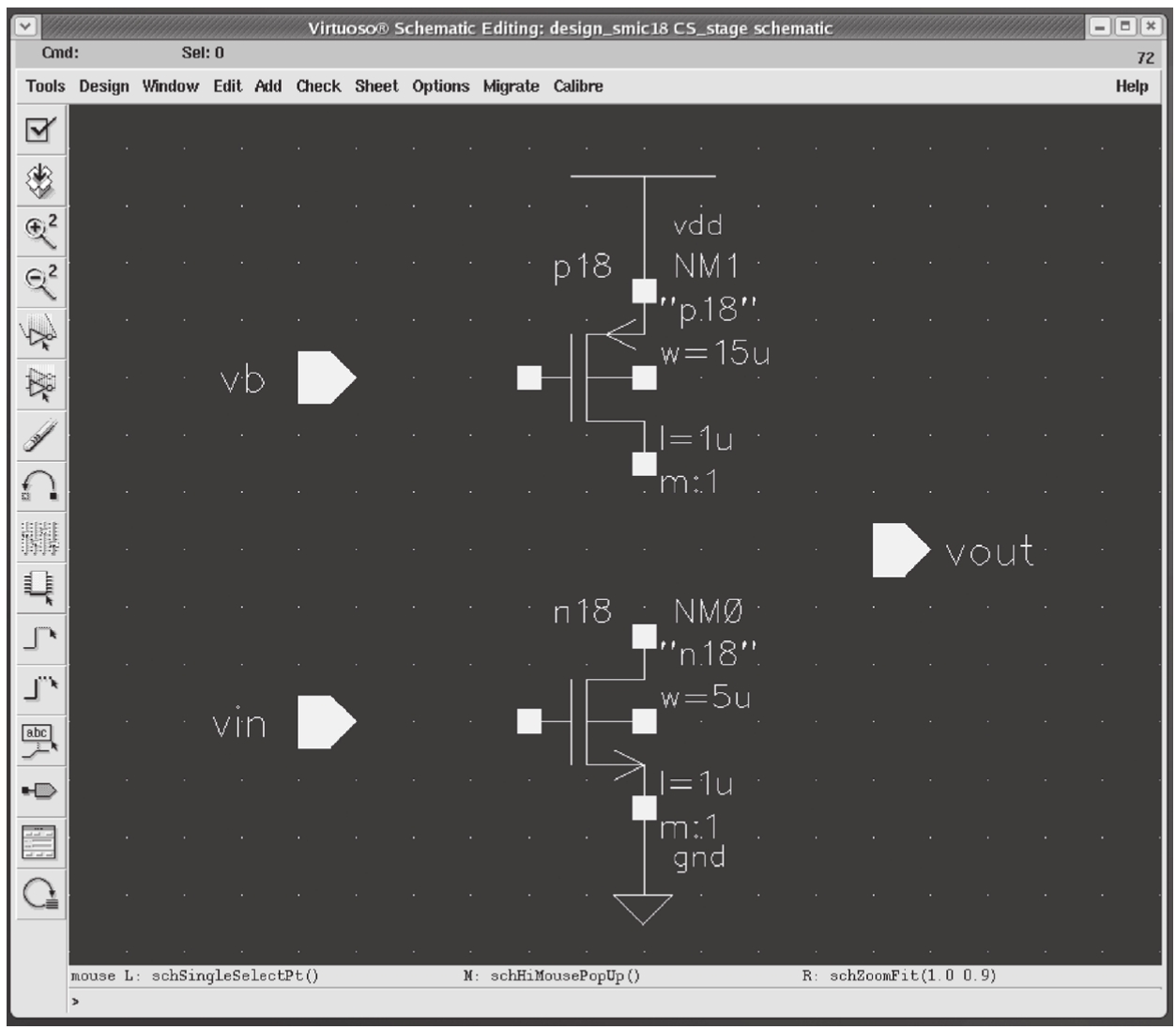

按I键弹出如图2.51所示的Add Instance对话框,单击Browse选择Library为smic18mmrf,Cell为n18,View为symbol,并填写Length为1μ,Finger Width为5μ,Fingers为1,然后单击Hide并将鼠标移到原理图窗口上,这时就可以看到一个MOS管符号图随鼠标移动,单击鼠标即可放下,这样就完成了NMOS管的例化。照此方法再例化PMOS管,使用p18管,注意要设置Finger Width为15μ,完成后的效果如图2.52所示(按F键可全屏显示)。

图2.51 Add Instance对话框

图2.52 元件例化的效果图

每个电路模块都需要电源、地和输入输出端口,其中电源和地属于全局(global)端口,不必单独引出(如果一定要引出,则需要将它们的属性设置为inout)。本例的输入端口为vin(信号输入)和vb(有源负载管的栅极偏压),输出端口为vout。

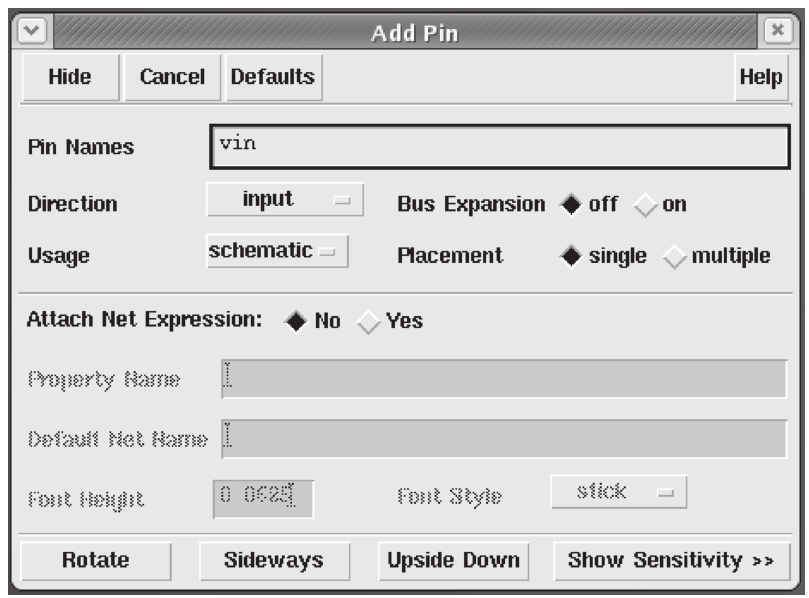

按P键弹出如图2.53所示的Add Pin对话框,在Pin Names栏中输入vin,Direction选择input,Attach Net Expression选择No,其他选项要与图中保持一致。然后单击Hide,端口vin就会随鼠标光标在原理图窗口中移动,单击鼠标左键即可放下。用同样方法再放置输入端口vb和输出端口vout,注意别忘了把vout的Direction设置为output,初学者经常会忘记设置Direction,最终结果如图2.54所示。

图2.53 Add Pin对话框

图2.54 放置端口后的效果图

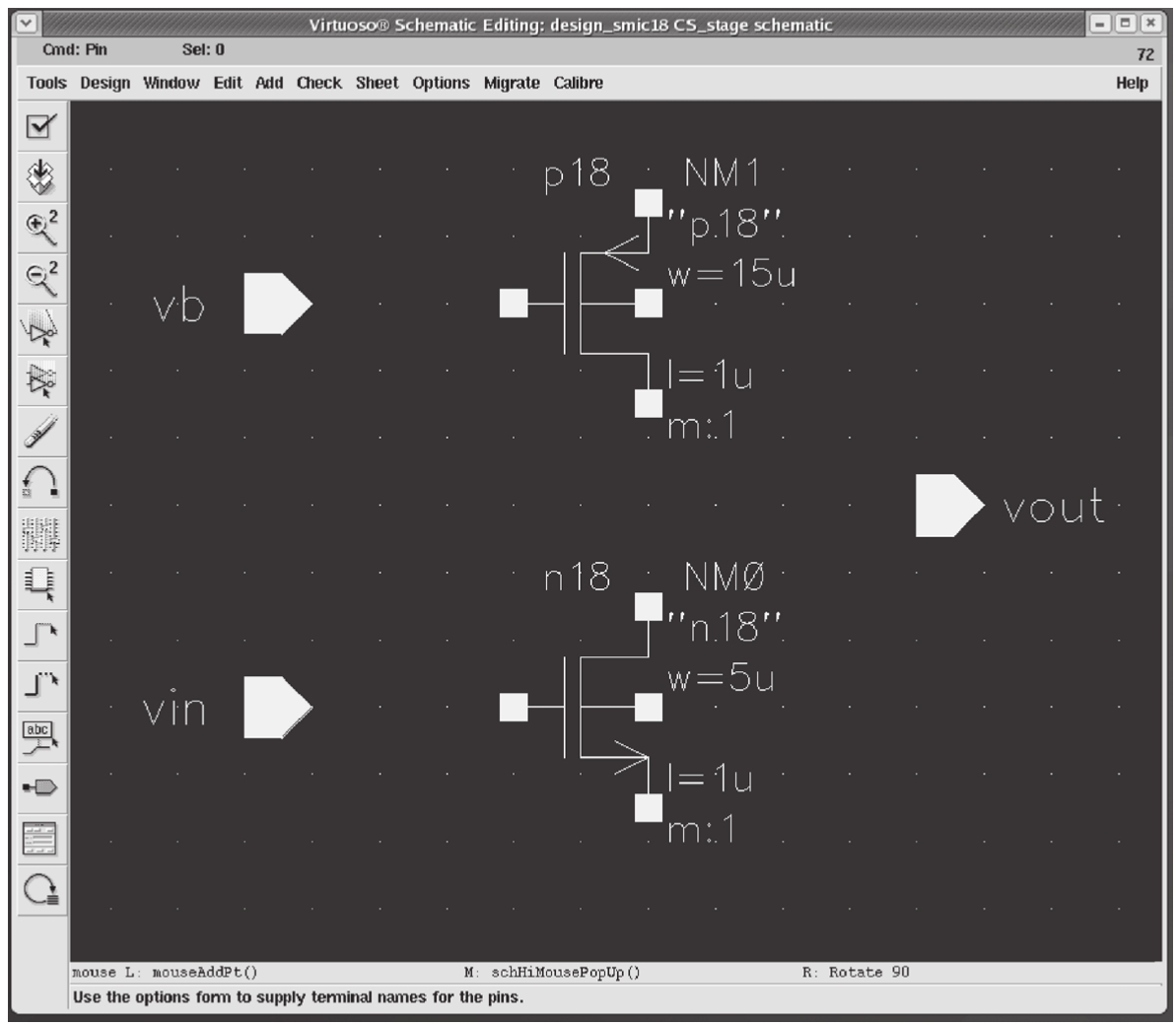

接下来放置电源和地,注意它们是全局端口。按I键弹出Add Instance对话框(见图2.55),单击Browse选择analogLib,之后勾选左上角的Show Categories,在Category栏中选择Sources的Globals,在Cell栏中选择vdd,在View栏中选择symbol,然后单击Hide,将vdd放在原理图中,用相同方法再放置gnd,完成后的总效果如图2.56所示。

图2.55 放置全局端口

图2.56 放置电源和地端口后的效果图

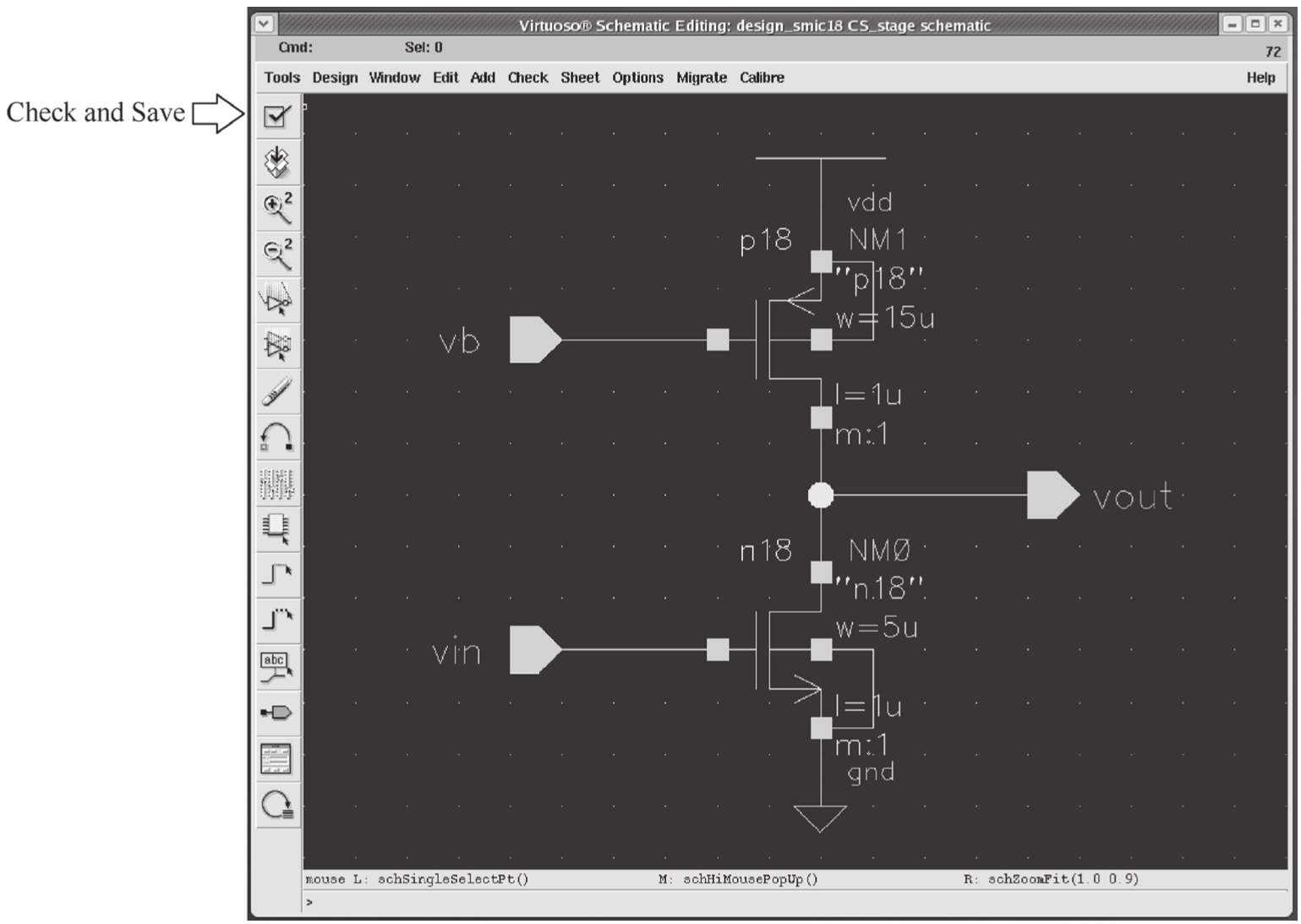

按W键进入布线状态,MOS管属于4端口器件(栅、源、漏和衬底),其中PMOS管的衬底是N阱,它必须接vdd,而NMOS管的衬底必须接gnd。根据有源负载共源极放大器的电路原理,按照图2.57的样子完成布线。按Esc键退出布线状态,单击左边最上面带有对勾的图标(Check and Save)保存。如果弹出warning或error对话框,一定要仔细检查分析,否则会影响后续的设计步骤。这样就完成了原理图设计,下面设计它的符号图。

图2.57 完成布线后的原理图

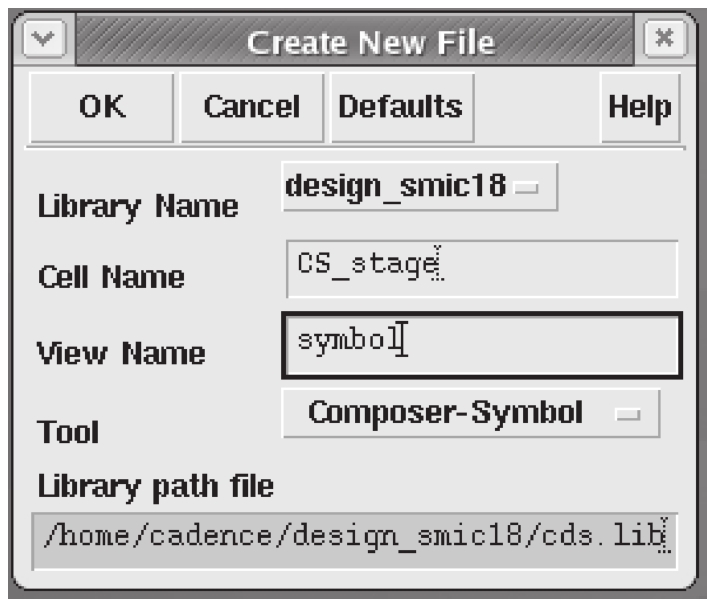

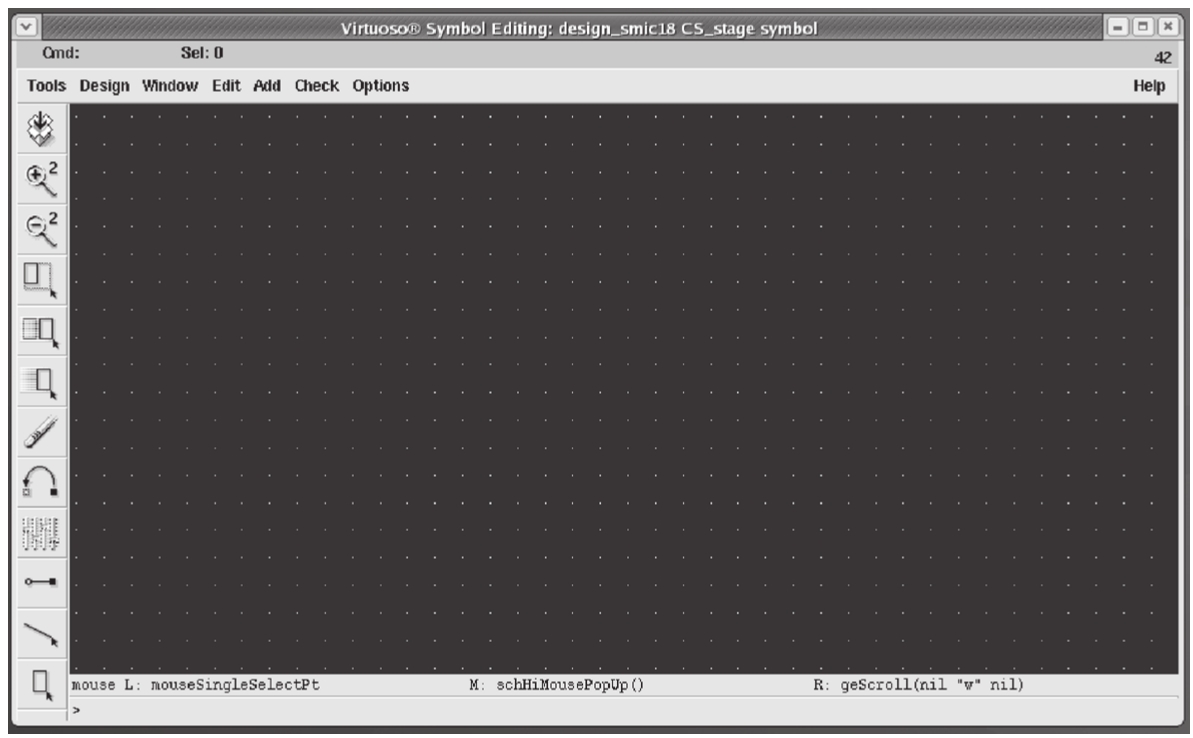

在Library Manager窗口的Cell栏中选择CS_stage,然后在菜单中选择File→New→Cell View...弹出Create New File对话框(见图2.58),在Tool栏中选中Composer-Symbol,View Name栏会自动变成symbol,然后单击OK按钮,弹出Virtuoso Symbol Editing窗口,并且CS_stage又增加了symbol view,总效果如图2.59所示。

图2.58 Create New File对话框

图2.59 Virtuoso Symbol Editing窗口

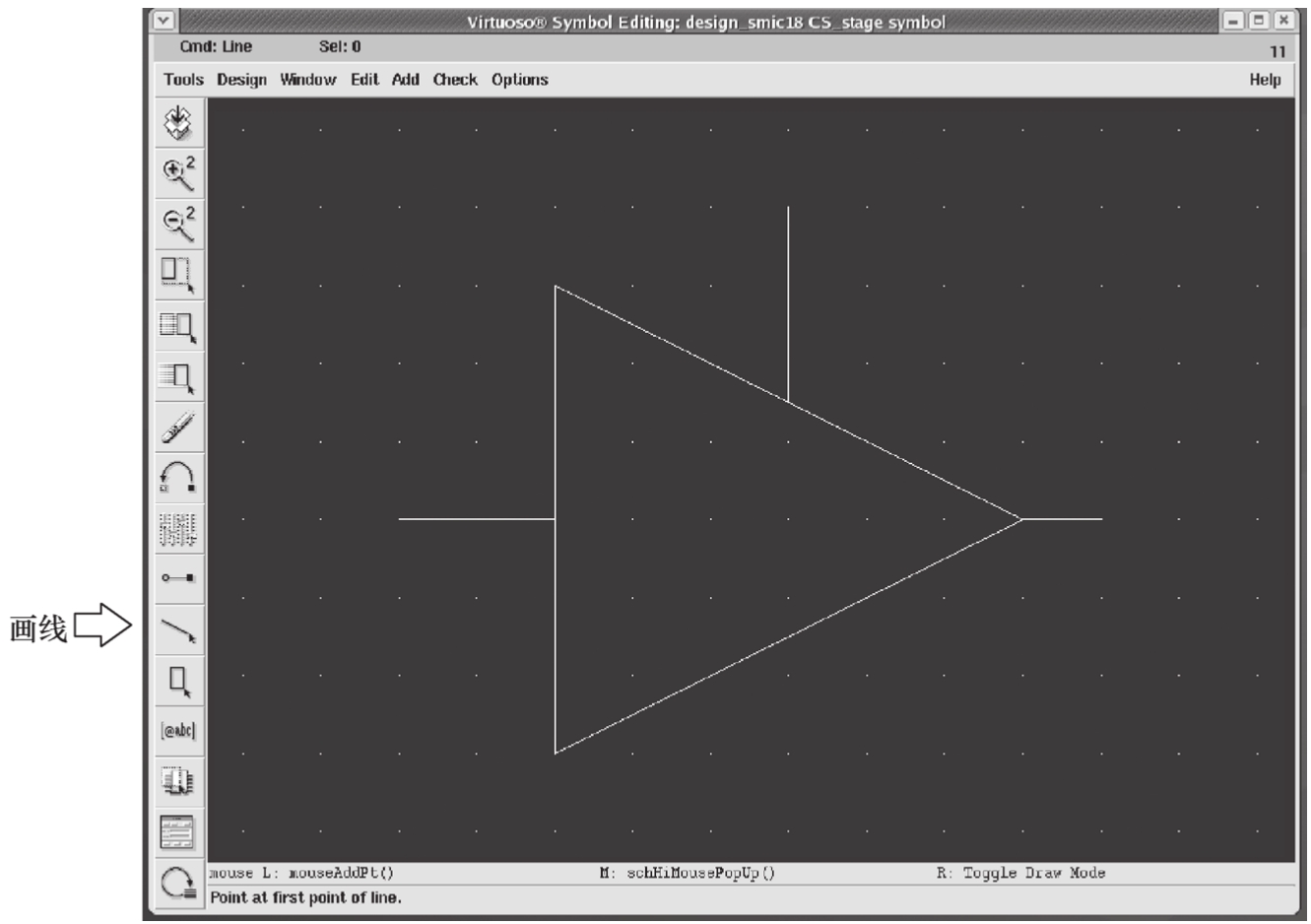

通常放大器的符号图是一个三角形,而直接用工具生成的都是矩形,所以这里最好用手工绘制符号图。如图2.60所示为画线后的效果图,单击图中箭头所指的画直线图标,可画出三角形和短线,如果不能画出斜线,则可以单击鼠标右键进行画线模式切换。端口线的外端要放置在格点上,将来这里要放置端口。注意,符号图要大小适中,三角形横纵方向以6个格点为宜,不可太大,否则与其他符号图放在一起时会显得十分巨大。

图2.60 画线后的效果图

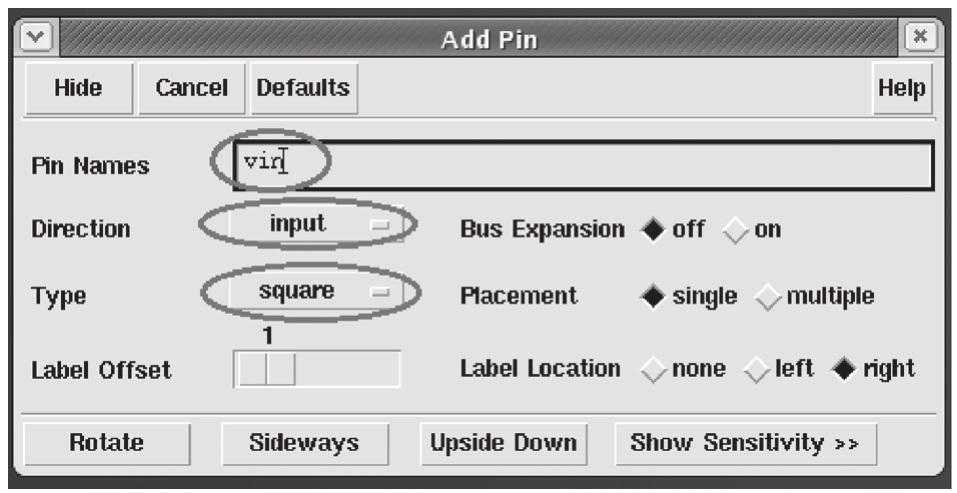

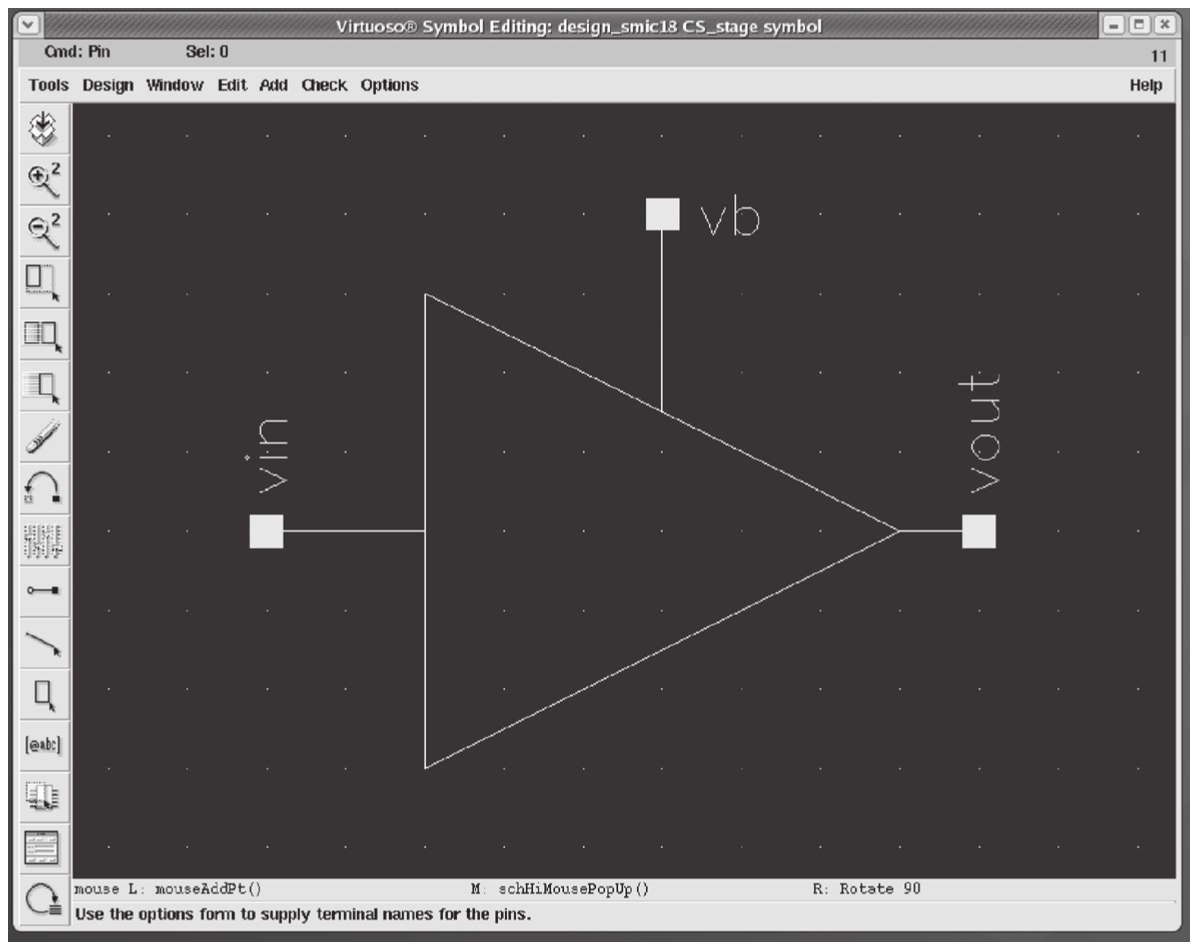

原理图与符号图的端口必须严格一致,端口的数量、名称、大小写和属性等都要相同,否则会报错。按P键弹出如图2.61所示的Add Pin对话框,在Pin Names栏输入vin,在Direction栏选择input,在Type栏选择square,单击Hide,放置前可以单击右键进行必要的旋转(617版取消了这个功能,需要到Edit窗口中进行旋转操作),将端口vin放置到符号图中。注意,端口一定要放置在格点上,端口名字不要超出符号图范围,否则会给将来的使用带来不便。用相同的操作放置输入端口vb和输出端口vout,注意vout的Direction是output,完成后的效果图如图2.62所示。

图2.61 Add Pin对话框

图2.62 放置端口后的效果图

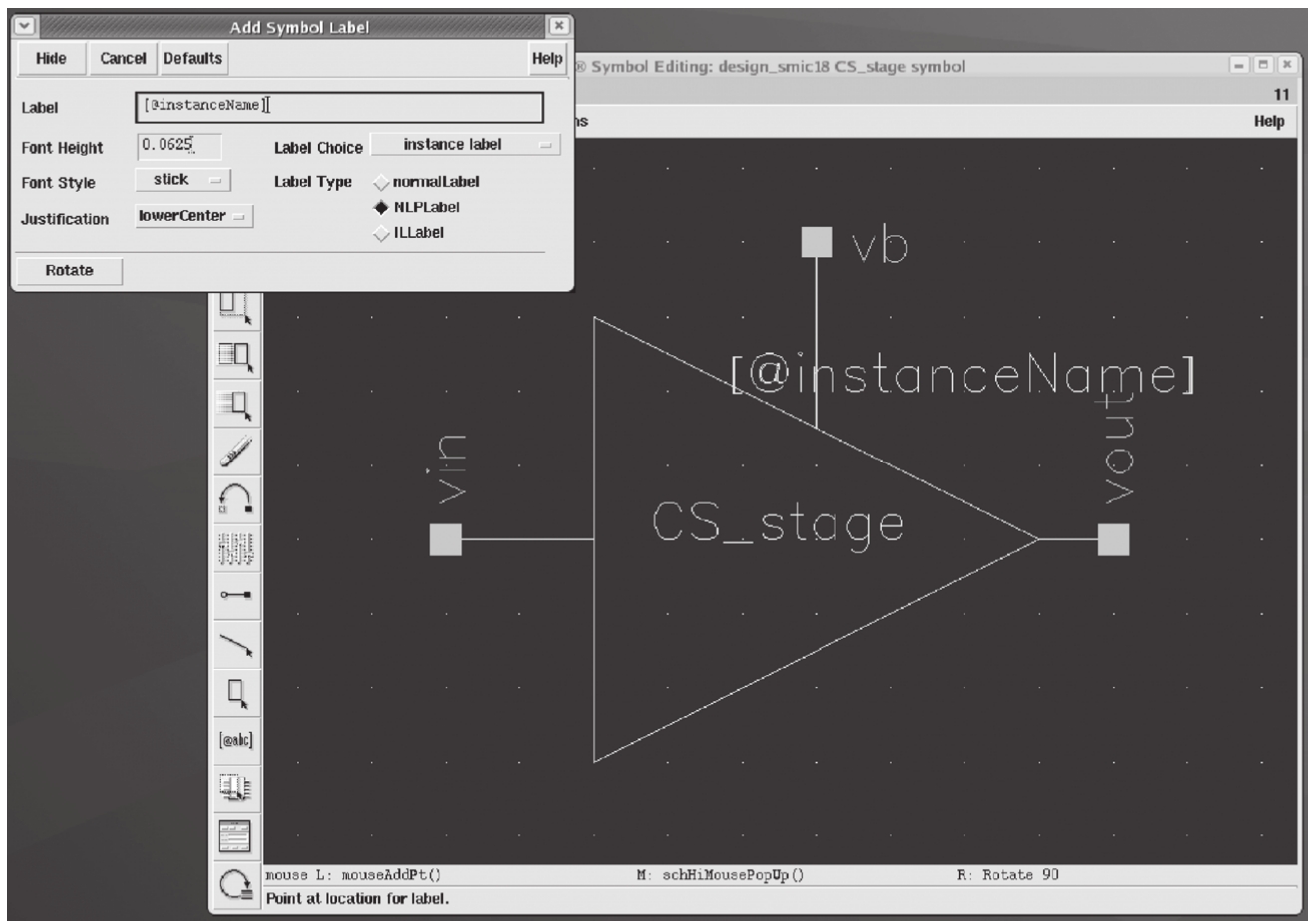

在符号图上放一些文字,例如模块名字和必要的提示或说明等,可以使符号图更实用,这就需要添加Label。放大器的符号图基本上都是一个三角形,为了在调用后能够区分出这是本例设计的放大器,可以在符号图上添加Label,例如写出CS_stage放在符号图上。另外还需要在符号图上放置一个默认的Label,即[@instanceName],有了这个默认的Label,在重复例化时就可以自动编号。

首先添加[@instanceName],按L键(Label的首字母)可弹出Add Symbol Label对话框,单击Defaults可使Label栏变为[@instanceName],移动光标到符号图窗口,将[@instanceName]放置到符号图上,并且要将光标(即[@instanceName]的中间点)放置在符号图区域的内部,不要超出符号图中其他元素的范围,否则将来也会给调用带来不必要的麻烦。最后在Label栏内填写CS_stage,单击Hide完成放置,完成后的效果如图2.63所示。

图2.63 添加Label后的效果图

symbol设计完成之后,需要将schematic与symbol进行比对,要保证两者的端口完全一致,包括名称、大小写及输入输出属性。比对的方法很简单,只要打开schematic view再Check and Save一下即可(Cadence 617版在保存符号图时也会进行比对,不用专门去打开原理图)。如果有端口不一致,或者有其他错误,就会出现warning或error,具体的错误信息都会显示在Cadence的主窗口(CIW)上。一定要仔细分析错误信息并进行改正,直到warning或error消失为止,到此就完成了原理图与符号图的输入工作。

其实symbol view也可以自动生成,下面将介绍其中两种最常用的方法,在介绍之前有必要先讨论一下Cadence的Library、Cell和View的概念,以及Library Manager工具的使用方法,对它有一定了解有助于解决很多有关Cadence使用时遇到的实际问题。