电阻是电路中的重要元件,CMOS工艺可以制作多种电阻,长条形的扩散区、N阱和多晶硅栅等都可以制作成电阻,中高端工艺中很细的金属线条也可以制作成电阻。版图设计者需要了解不同类型电阻的版图结构和电学特性,为合理选型和优化版图做好准备。

方块电阻 R □ :由于CMOS工艺是平面工艺,所以电阻率用方块电阻(sheet resistance,薄层电阻) R □ 来表征,这是描述电阻导电特性的重要概念。 R □ 就是正方形平面对边之间的电阻值,根据电阻的串并联关系可知, R □ 与正方形的边长无关。CMOS电阻通常制作成长条形,EDA工具只需要提取出电阻包含的正方形个数,然后乘以 R □ 就能算出电阻值。不同类型的CMOS电阻具有不同的 R □ 、温度系数、电压系数和噪声特性,这些特性对器件选型非常重要,下面对常见的CMOS电阻类型进行讨论。

扩散区可以制作扩散电阻,其由长条形的扩散区构成,两端通过接触孔引出电极连接到金属,分为N型和P型两类。为了实现器件隔离,N型扩散电阻要制作在P型衬底上,P型扩散电阻要制作在N型衬底上。对于N阱CMOS工艺,N型扩散电阻可以直接制作在P型衬底上,而P型扩散电阻必须制作在N阱里,并且为了保证电阻与衬底之间的二极管隔离,要求P型衬底必须接地,N阱接电源。

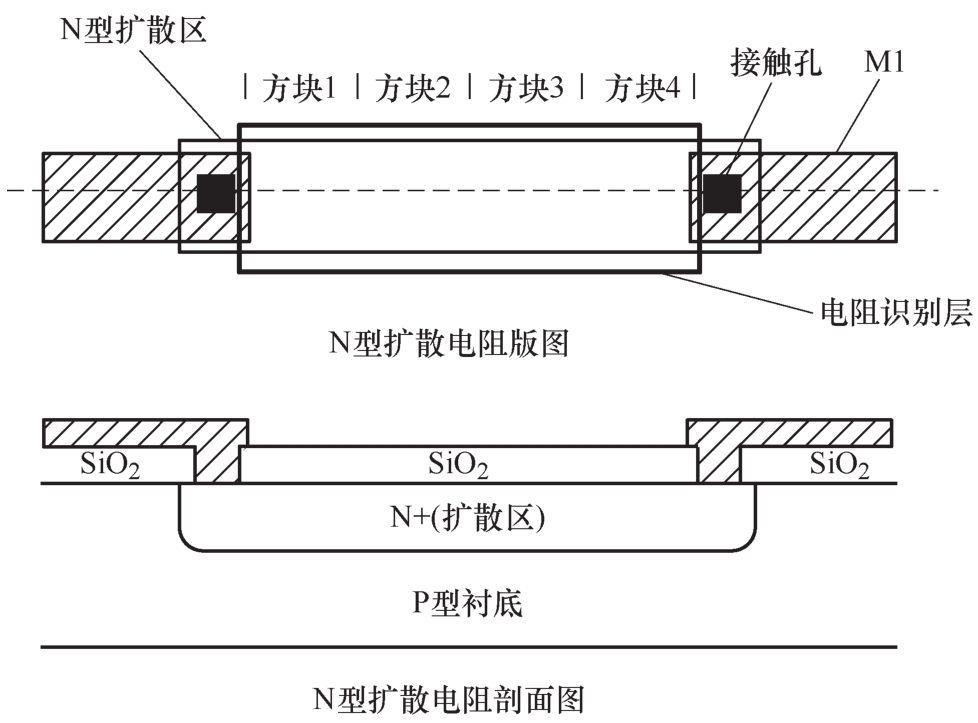

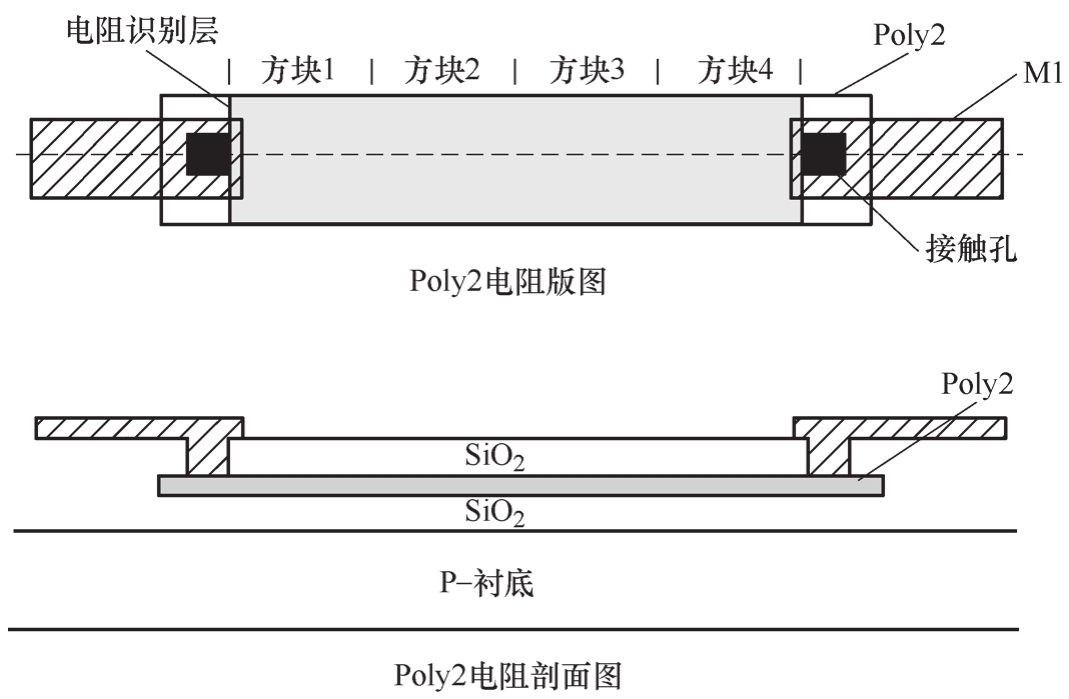

图2.16是N型扩散电阻版图和剖面图,由于N阱CMOS工艺已经将P型衬底接地,所以N型扩散电阻与衬底之间已经天然地形成了二极管隔离。图中长条形的N型扩散区是电阻的主体,两个接触孔打在长条形扩散区的两端用于连接金属。由于接触孔处的扩散区不属于电阻的识别区域,所以需要在版图中划出电阻识别层,EDA工具将根据电阻识别层内包含的方块个数和扩散区的 R □ 来计算总电阻值,本例中有4个方块。

图2.16 N型扩散电阻版图和剖面图

硅化(salicide):为了可以与扩散区、N阱和多晶硅栅等表面形成导体般(conductor-like)的接触,CMOS工艺会将它们的表面进行硅化处理 [3] 。硅化可以在表面形成一个低电阻层,能够减小MOS管电极的引出电阻,常用的硅化材料有TiSi 2 、CoSi 2 和NiSi等。因此,根据是否对扩散区进行硅化,可以把扩散电阻分为硅化(salicide)电阻和非硅化(nonsalicide)电阻两类。为了隔离多晶硅栅与源漏扩散区,硅化前要在多晶硅栅的边缘生长氧化隔离带,然后再进行硅化物淀积(the deposition of the silicide),由于这个工艺过程具有自对准(self-aligned)特性,所以salicide(硅化)一词是由“ s elf -a ligned sil icide ”组合而成的。

由于硅化扩散电阻是与源漏区同时进行离子注入和硅化的,所以其方块电阻既不可选也不可调,硅化扩散电阻的 R □ 较小,大概是几欧到十几欧;非硅化扩散电阻需要加入硅化阻挡层(SAlicide Block,SAB),将非硅化区域挡住。非硅化扩散电阻的 R □ 是硅化扩散电阻的 R □ 的十几倍,能够用来制作中阻值电阻。

N阱中的P+扩散区也可以制作扩散电阻,由于N阱接连 Ⅴ DD ,P型扩散电阻也能实现二极管隔离,它的版图结构与N型扩散电阻版图结构基本相同,这里不再赘述。

扩散电阻的误差通常在10%~20%之间,温度系数在500~1000ppm/℃之间,并且电压系数也很大。由于扩散电阻的精度低,寄生参数大,温度特性和电压特性也不好,所以只能用在低精度的电路中,作为保护或限流电阻使用比较合适。

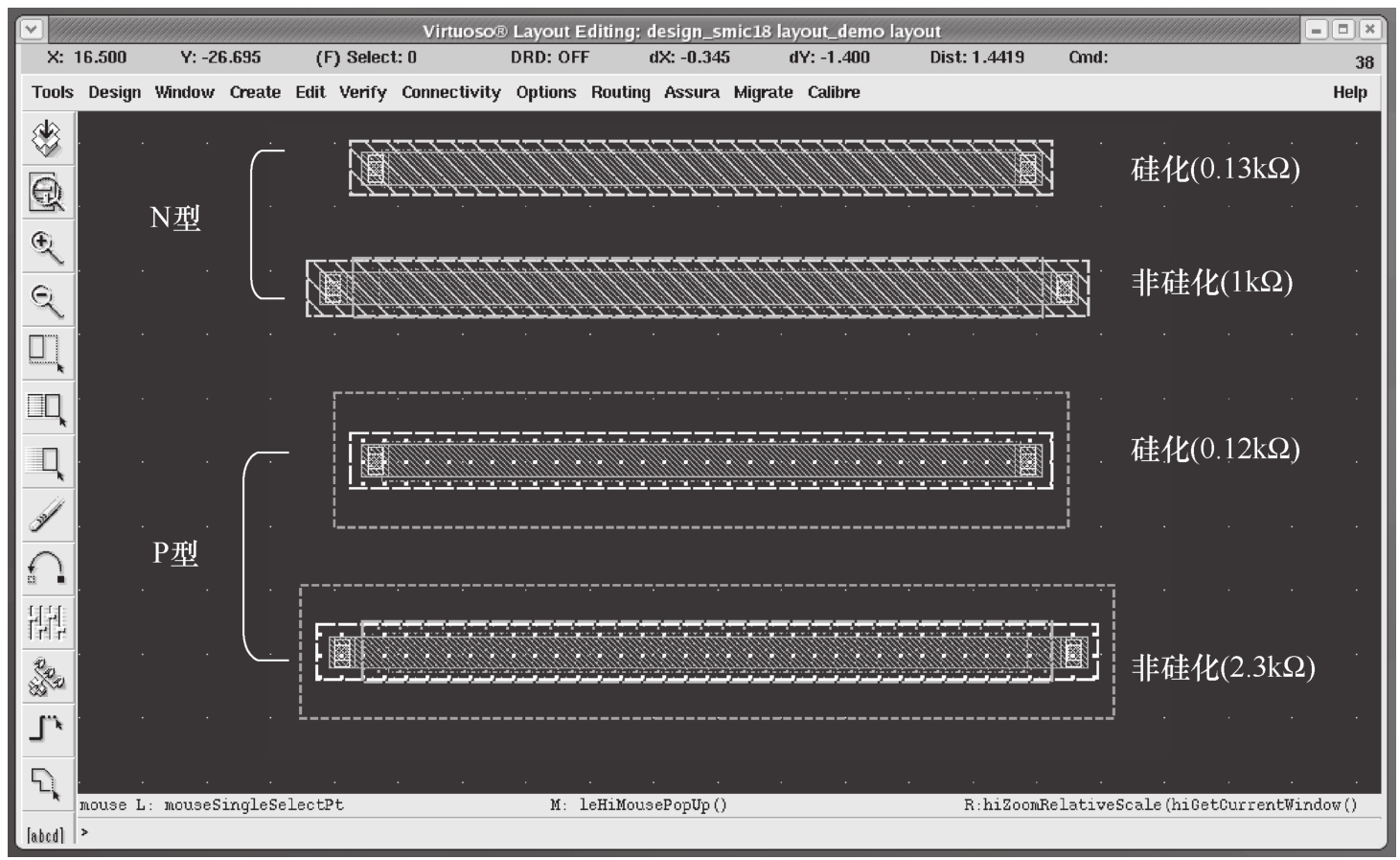

图2.17所示为扩散电阻版图,上边两个为N型扩散电阻,下边两个为P型扩散电阻。图中的电阻都是20个有效方块,每种电阻都分为硅化和非硅化两类,其中N型和P型硅化电阻的阻值较小,其方块电阻主要由硅化物决定,所以基本相同,其总阻值分别为130Ω和120Ω;而两个非硅化电阻的阻值都比较大,N型为1kΩ,P型为2.3kΩ,可见与硅化电阻相比,非硅化电阻是硅化电阻的10~20倍。

图2.17 扩散电阻版图

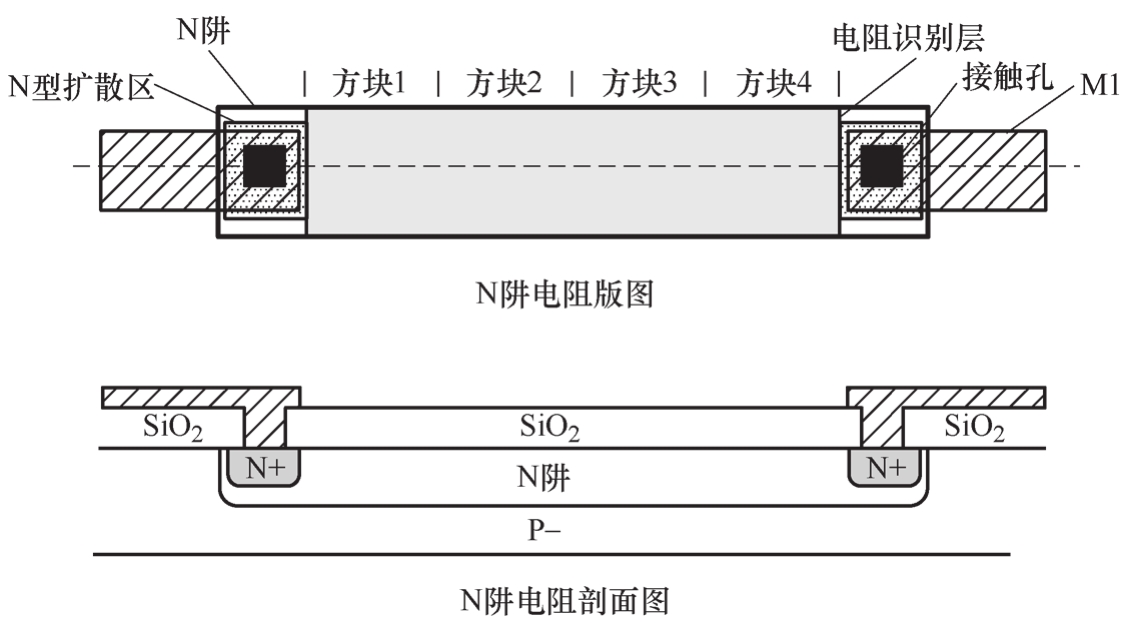

用N阱也可以制作电阻,如图2.18所示为N阱电阻版图和剖面图,在长条形N阱两端制作了N型扩散区,N型扩散区上有接触孔可连接金属引出电极。N阱的离子注入浓度由工艺决定,它比N型扩散区的浓度低很多,因此方块电阻在kΩ量级,远远大于非硅化的N型扩散电阻,适合制作大阻值电阻。N阱电阻的精度很低,误差在70%左右,温度系数高达几千ppm/℃,与衬底的寄生电容也很大,在电路中常作为保护电阻或限流电阻使用。

图2.18 N阱电阻版图和剖面图

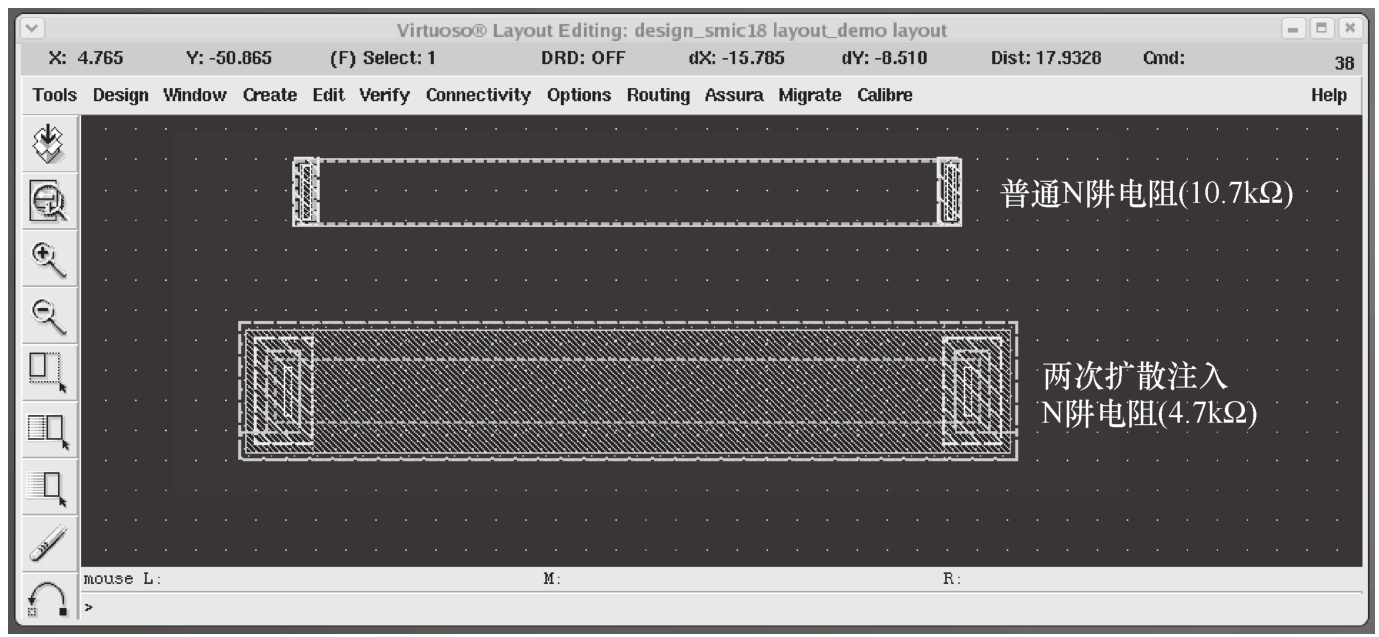

为了减小方块电阻,利用N+离子浓度大于P+离子浓度的特点,在N阱中进行N+和P+两次离子扩散注入,N+浓度超出的部分可以用于减小N阱的方块电阻,这样在不用特殊工艺步骤的情况下,就能有效地减小N阱的方块电阻。图2.19所示为N阱电阻版图,上面是普通N阱电阻,下面是进行了N+和P+两次离子注入的N阱电阻。两个电阻都是20个方块,其中普通N阱电阻的阻值是10.7kΩ,而进行N+和P+两次离子扩散注入的N阱电阻的阻值是4.7kΩ,方块电阻减小了一半以上。

图2.19 N阱电阻版图

CMOS数模混合信号工艺通常有两层多晶硅,即Poly1和Poly2,它们都可以制作Poly电阻,其中Poly1主要用于制作MOS管的栅,但也可以制作电阻,在不额外增加工艺步骤的情况下,它的方块电阻较小且不可变,因此只适合制作小阻值电阻。Poly2主要用于制作电阻和电容,电阻的性能比扩散电阻和N阱电阻都好,是中低端混合信号工艺的首选电阻。

在CMOS自对准工艺中,用没有掺杂的多晶硅制作栅,未掺杂的多晶硅栅基本不导电,需要与源漏同时掺杂(离子注入)才能具有导电性,因此用Poly1制作的电阻有N型和P型之分。硅化后Poly1电阻的方块电阻较小,在几欧到十几欧的量级,误差在35%左右,温度系数大约为1000 ppm/℃,适合作为低阻值低精度电阻。

Poly2进行独立的离子注入,可以通过调整工艺得到不同的方块电阻,使用比较灵活,很多CMOS混合信号工艺都提供几种Poly2方块电阻供用户选择。Poly2方块电阻的正常阻值是几百欧,可制作中阻值电阻,如果增加一些高电阻识别层,Poly2方块电阻可以达到几千欧,能够用于制作高阻值电阻。

Poly1电阻和Poly2电阻在版图结构上是基本相同的,图2.20所示为Poly2电阻版图和剖面图,图中可以看出接触孔直接打在Poly2上与金属相连引出电极。

图2.20 Poly2电阻版图和剖面图

Poly2电阻的电压系数和温度系数都优于扩散电阻和N阱电阻,寄生参数也相对较小,同时Poly2上下都有绝缘隔离,电极电压也不受限制,因此成为中低端CMOS混合信号集成电路设计的首选电阻。虽然Poly2电阻比其他类型电阻性能优良,但是它需要额外制版和工艺流程,尤其是当需要多种Poly2方块电阻时,芯片成本会进一步提高。

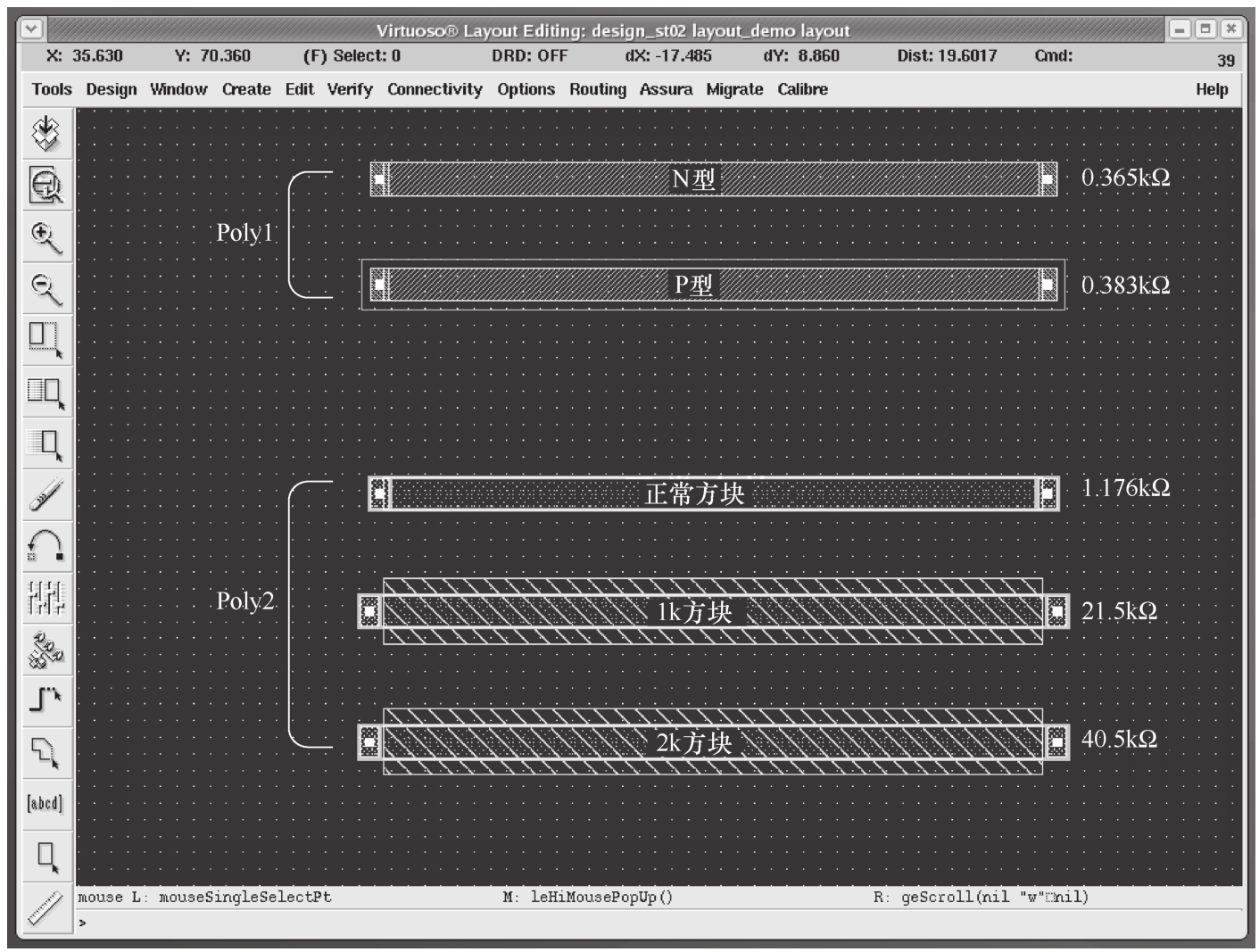

图2.21所示为Poly1和Poly2电阻版图,每个电阻都包括20个有效方块,最上面两个是Poly1硅化电阻,第一个是N型,第二个是P型。下面3个是Poly2电阻,它们的 R □ 从上到下依次是正常方块、1k方块和2k方块。从图中可以看出,两个Poly1电阻阻值相差不大,N型为365Ω,P型为383Ω, R □ 不到20Ω,其 R □ 主要由表面硅化物决定;3个Poly2电阻阻值差别很大,正常方块的阻值为1.176kΩ,1k方块的阻值为21.5kΩ,2k方块的阻值为40.5kΩ,其中正常方块的 R □ 大约为60Ω,远远小于1k和2k方块的 R □ 。

图2.21 Poly1和Poly2电阻版图

需要指出的是,Poly2最主要的功能是制作电容,如果PDK中有其他种类电容可替代,那么就尽量不使用Poly2电容,在这种情况下Poly电阻最好只用Poly1制作,以减少额外的制版和工艺步骤。在不增加额外制版和工艺步骤的情况下,只用Poly1可以制作出硅化和非硅化两类电阻,而每类电阻又都可以分为N型和P型两种。

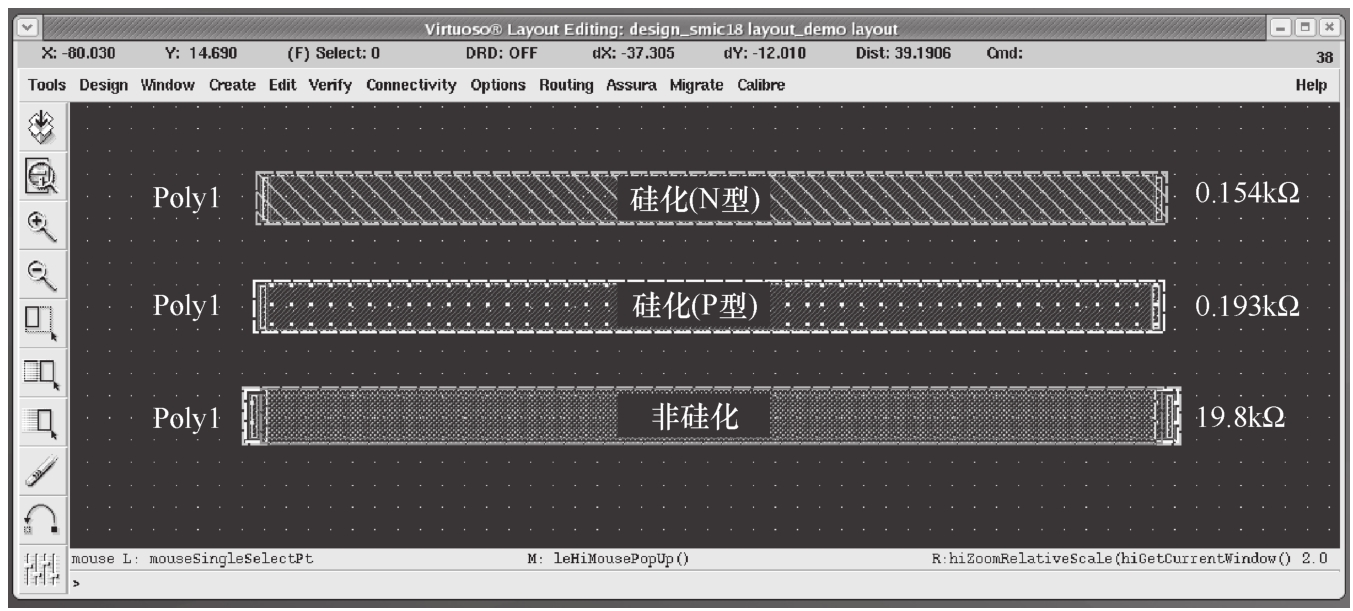

如图2.22所示,图中有3个Poly1电阻,它们都包括20个方块,上面两个是N型硅化和P型硅化的Poly1电阻,根据阻值可以算出N型硅化的Poly1电阻的 R □ 为7.5Ω,P型的为9.9Ω。下面的电阻是非硅化的Poly1电阻,其 R □ 比较大,接近1kΩ,是该工艺提供的唯一一种高阻值电阻,虽然在其图层中没有给出N型注入和P型注入的区分层,但是它一定是属于其中之一,且不能由用户制定。

还需要说明一下,图2.21中的电阻来自0.5μm工艺,图2.22的电阻来自0.18μm工艺,同样是硅化的Poly1电阻,0.5μm的方块电阻接近20Ω,而0.18μm的方块电阻不到10Ω,二者相差将近一倍。

图2.22 3种Poly1电阻版图

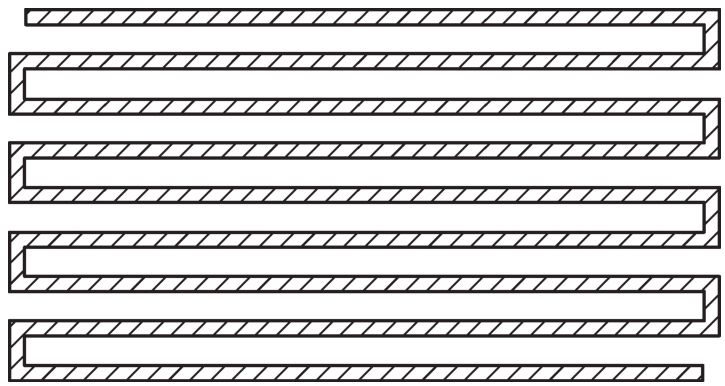

随着集成电路工艺的不断进步,金属线条越来越细,使得用细金属条制作电阻成为可能。在高端的集成电路工艺中,一般都会提供金属电阻。为了用更小的面积得到更大的电阻,金属电阻通常会做成如图2.23所示的形状。另外,虽然每层金属都可以制作电阻,但在几何尺寸相同的条件下,金属层越厚,制作的电阻阻值越小。顶层金属最厚,主要用于连接电源、地和制作电感,所以用它制作电阻时,面积效率最低。

图2.23 金属电阻版图结构示意图

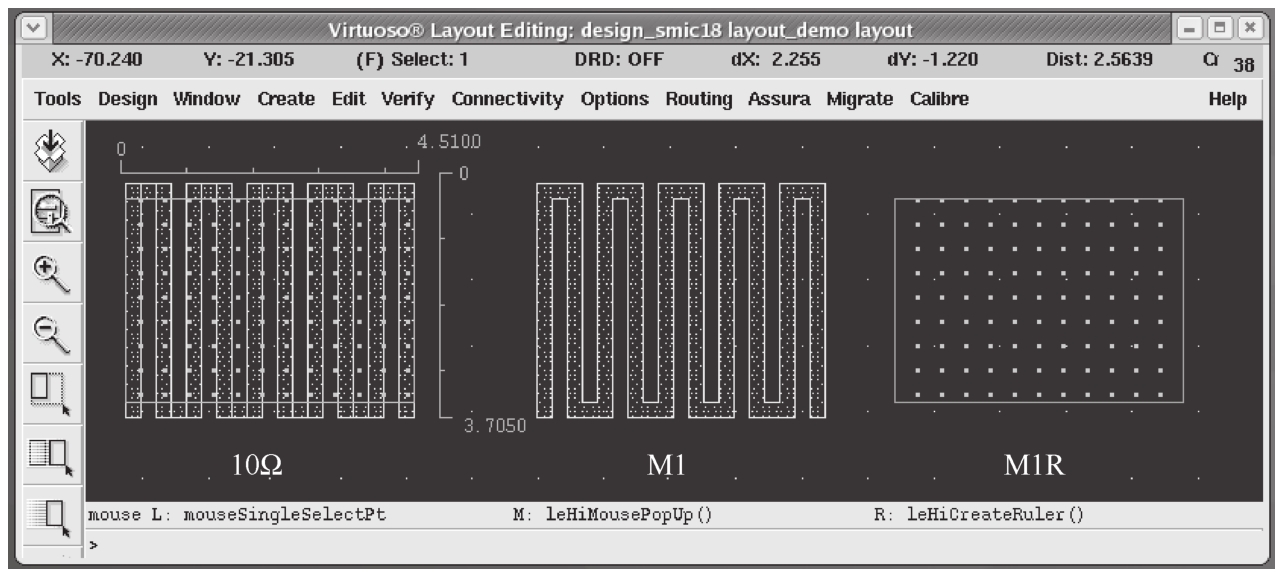

如图2.24所示为一个M1的金属电阻版图,金属线宽为230nm,阻值为10Ω,左侧为电阻版图,根据图中的尺寸可以看出,这个电阻大约占用(3.7×4.5)μm 2 的面积,中间和右侧为分解图,其中,中间为M1的线条,右侧为电阻识别层(M1R)。

图2.24 金属电阻(M1)版图