在图2.6的讨论中,MOS管的栅极用金属铝制作,因此被称为铝栅CMOS工艺。铝栅CMOS工艺需要先进行源漏扩散区注入,然后再制作铝栅,铝栅必须严格地对准沟道上方。但由于对准误差的存在,铝栅CMOS工艺只能达到微米级水平,而对于亚微米和深亚微米以上,必须采用多晶硅(polysilicon)栅自对准CMOS工艺。与铝栅CMOS工艺相比,基于多晶硅栅的自对准工艺大大提高了CMOS芯片的集成度,成为CMOS领域的主流工艺,而铝栅CMOS工艺已经基本上退出了历史舞台,目前主要应用在抗辐射等一些特殊领域。

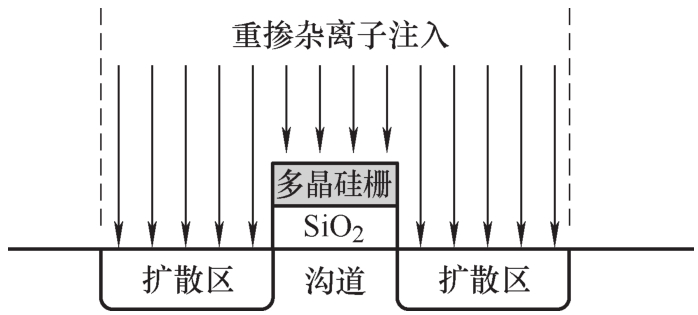

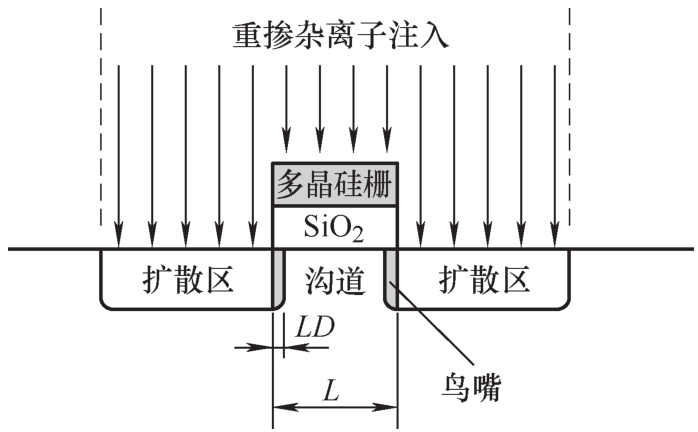

如图2.8所示为多晶硅栅自对准工艺示意图,这种工艺要先制作多晶硅栅,然后横跨多晶硅栅进行整体的扩散区离子注入,由于离子不能穿过多晶硅栅,这样就在多晶硅栅的下面天然地形成了沟道,栅的两侧形成源区和漏区,实现了栅与沟道的自对准。另外,制作栅的多晶硅本身导电性极差,而在进行源漏注入时,多晶硅栅也被进行了离子注入,进行离子注入后其导电性会大大提高。所以在自对准工艺中,对源漏扩散区注入的同时,多晶硅栅也得到了注入,天然地解决了多晶硅栅的导电性问题。需要指出的是,实际工艺中的离子注入角度与图中垂直向下不同,需要7°~9°的倾斜,有关这个问题将在第6章的倾斜角度离子注入部分进行详细说明。

图2.8 多晶硅栅自对准工艺示意图

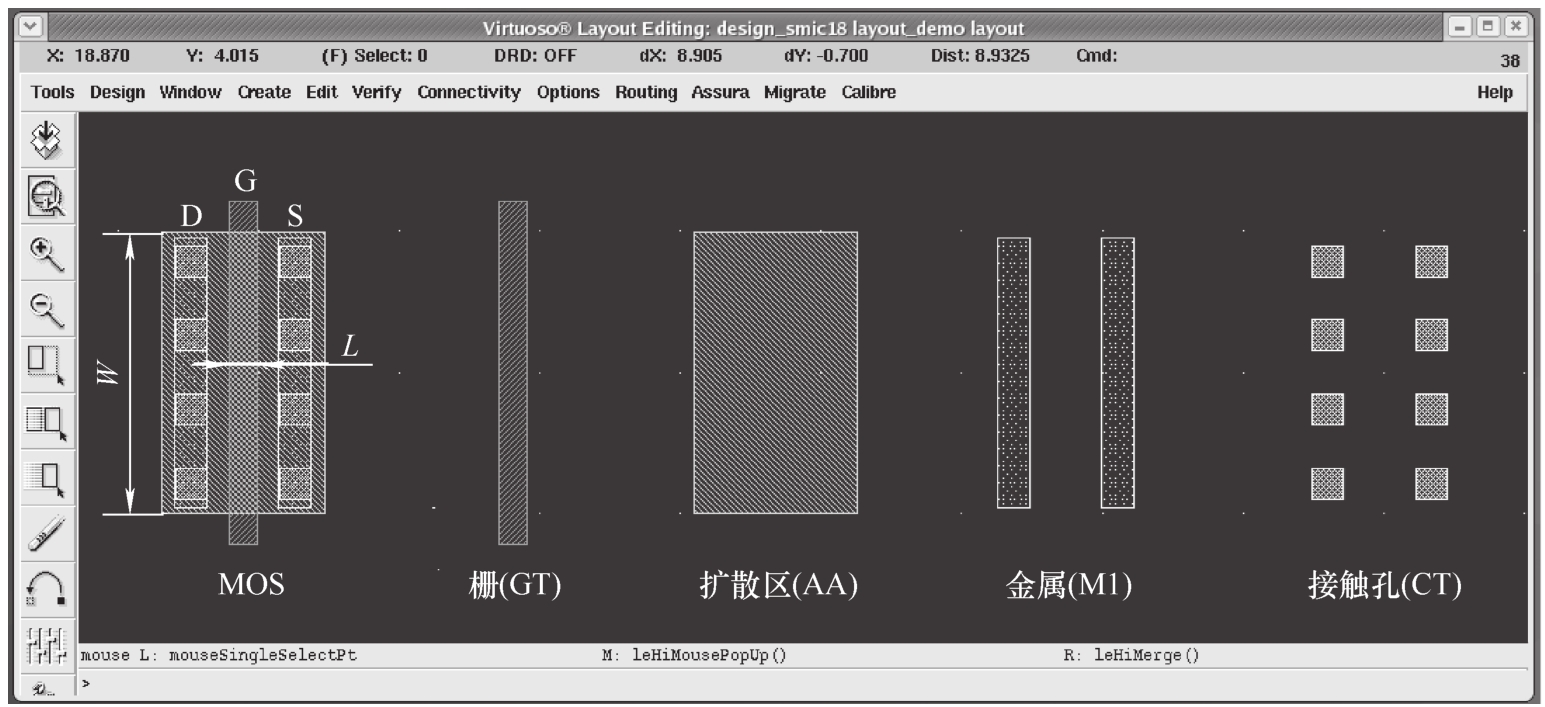

在进行集成电路工艺加工之前,需要预先设计好扩散区、栅、金属线条和接触孔等的图形,这些图形就是版图。如图2.9所示为多晶硅栅MOS管的版图,最左侧为MOS管完整版图,旁边是MOS管各个图层的分解图,包括栅(GT)、扩散区(AA)、金属(M1)和接触孔(CT)。从分解图中可以看出,扩散区(AA)是一个整体,由于多晶硅栅的遮挡,实际形成的扩散区被分成了两个独立的部分,分别为源区(S)和漏区(D),多晶硅栅与扩散区的交叠部分称为沟道,在源漏区上打接触孔,通过金属(M1)拉出电极D和S。图中MOS管源漏扩散区之间的距离定义为沟道长度 L ,扩散区的宽度定义为沟道宽度 W ,大部分情况下 L 小于 W ,这有些不太符合人们的基本认知习惯。栅伸出扩散区的部分是为了确保在一定的工艺误差下,栅极仍然能完整跨过扩散区。

图2.9 多晶硅栅MOS管的版图

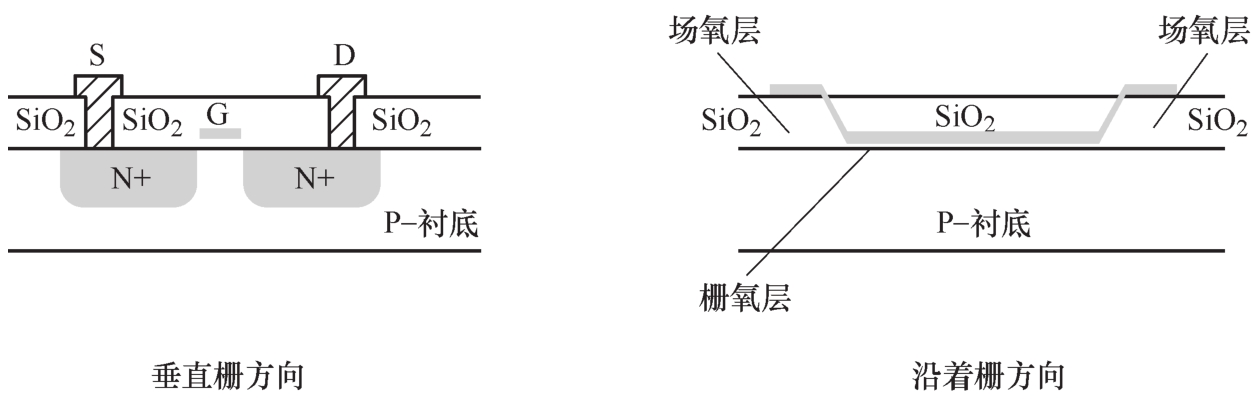

如图2.10所示为NMOS管的剖面图,左图为垂直栅方向的剖面图,右图为沿着栅方向的剖面图。垂直栅方向的剖面图比较简单,与铝栅的结构非常相似,这里不再解释,而沿着栅方向的剖面图有些特殊的地方需要说明。从图中可以看出,栅的两端高中间低,低的部分下面是沟道,高的部分是栅超出扩散区的部分。低的部分氧化层比较薄,被称为栅氧层,高的部分氧化层比较厚,被称为场氧层。栅氧越薄越好,这样可以提高栅与沟道之间的电场强度,但是太薄了又容易击穿,通常情况下为几十到几百埃(Å)的量级(1Å=0.1nm)。在一些特殊的高电压大功率工艺中,比如BCD(Bipolar CMOS DMOS)工艺,栅氧层厚度可达几千埃。

图2.10 NMOS管剖面图

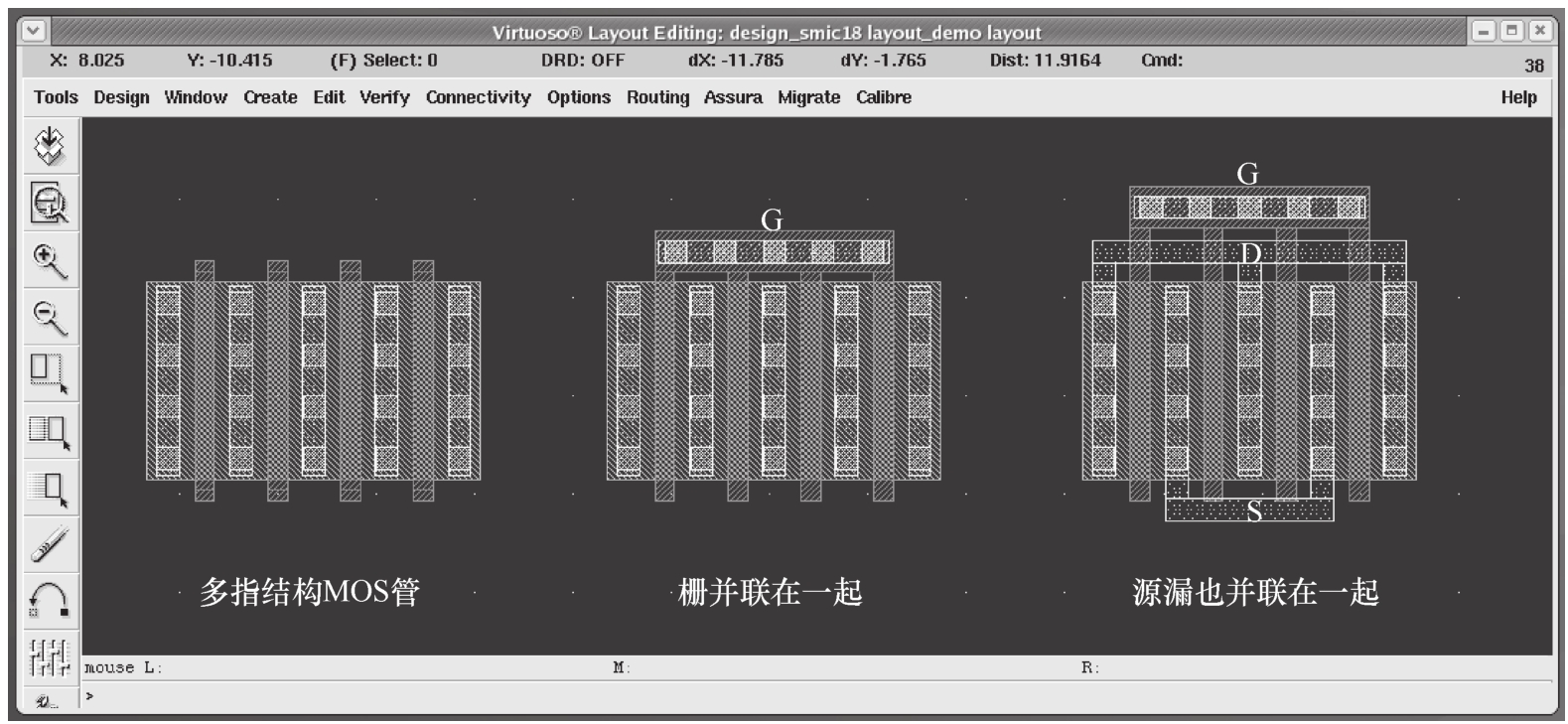

有时MOS管的宽长比( W / L )会很大,造成版图很细很长,这时需要采用多个短MOS管并联的结构,即多指结构。如图2.11所示为多指结构MOS管版图,左侧是一个4栅多指结构MOS管版图,每条栅代表一个MOS管,栅两侧为S和D扩散区,相邻MOS管共用S和D。中间是把栅并联起来的版图,可以看出,用GT层直接把各个栅连接起来,再打上接触孔,连接到M1即可。右侧是将源漏也并联在一起的版图,它是多指结构MOS管最终的版图样子。

图2.11 多指结构MOS管版图

MOS管的很多特性都与宽长比( W / L )有关,由于 W / L 是个比值,并没有规定宽和长的具体尺寸,因此就存在 W 和 L 的尺寸优化问题。由MOS管的 Ⅰ-Ⅴ 特性可知,在忽略沟道调制效应条件下,进入饱和区之后,MOS管的 Ⅰ ds 近似与 Ⅴ DS 无关,但随着 L 的减小,沟道长度调制效应会越来越明显 [3] 。为了提高恒流特性,在保持 W / L 不变的情况下,可以适当增加 L ,但这也会使 W 等比例增加,导致MOS管的版图面积和寄生效应也随之增加。因此,优化MOS管的宽长比需要综合考虑多方面的因素。

由表2.1可知,Si的电子迁移率几乎是空穴迁移率的3倍,所以在相同尺寸下NMOS管的驱动能力也几乎是PMOS管的3倍。由于CMOS逻辑门的输出通常由NMOS管作为下拉管,由PMOS管作为上拉管,为了平衡逻辑门的上拉和下拉能力,在 L 相同的情况下,通常会将PMOS管的 W 设置为NMOS管的3倍。

如图2.12所示,在进行离子注入时,离子除了纵向扩散之外,还会横向扩散,横向扩散部分被称为鸟嘴,在Spice模型中用参数 LD 描述。鸟嘴不仅使有效栅长 L eff ( L eff = L -2 LD )减小,而且还会增加栅极与源极、漏极之间的交叠电容,不仅影响器件的高频特性,而且还会在采样保持电路中造成时钟馈通(Clock Feedthrough)。

图2.12 离子横向扩散产生鸟嘴

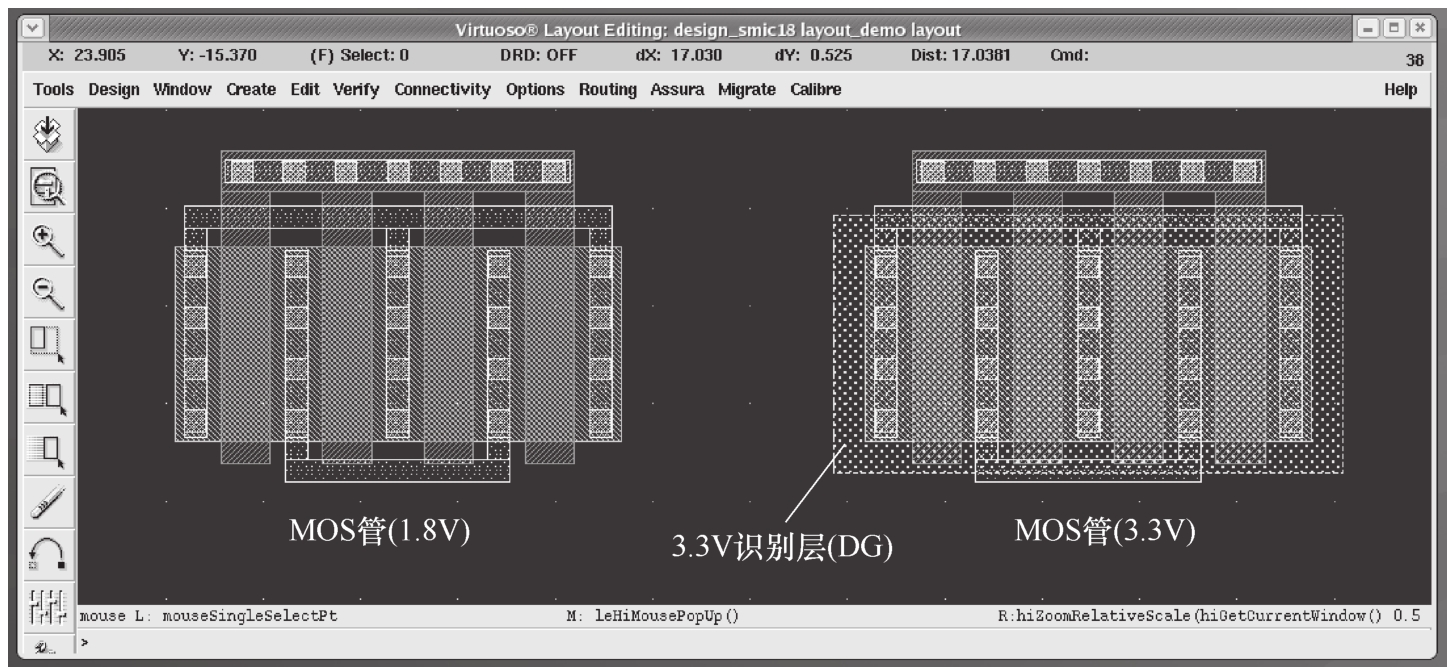

随着CMOS工艺的不断发展,MOS管的栅氧层厚度也越来越薄,击穿电压也越来越低,而且同一个工艺可以支持多种电压的MOS管。以0.18μm工艺为例,其核心电路电源电压为1.8V,为了支持3.3V的电路设计,0.18μm工艺也提供3.3V的MOS管,1.8V与3.3V的MOS管在版图结构上基本相同,主要区别在于栅氧层厚度不同。图2.13是1.8V和3.3V的MOS管版图对比,左边是1.8V的MOS管,右边是3.3V的MOS管,每个MOS管都由4个MOS管并联构成。这两种MOS管的版图结构基本相同,差别在于3.3V的MOS管额外增加了3.3V识别层,这个识别层用于指导工艺流程,将它所覆盖的栅氧层生长得厚一些。

图2.13 1.8V和3.3V MOS管版图

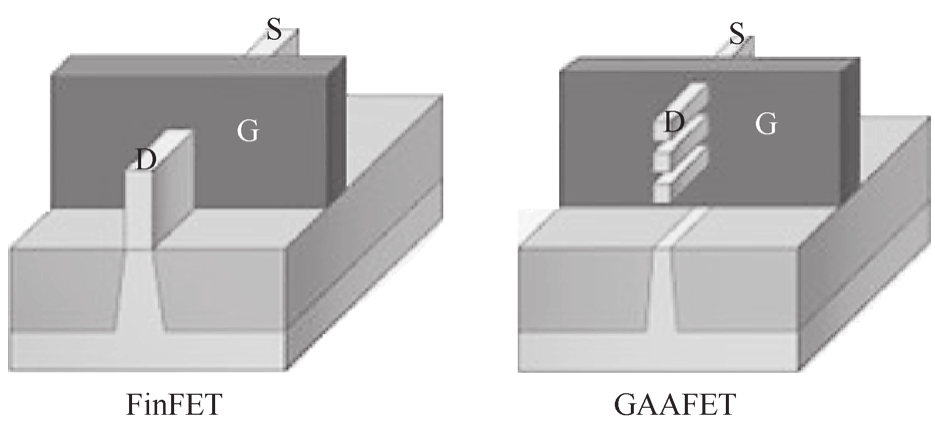

基于多晶硅栅的自对准工艺有力地推进了摩尔定律的发展,使CMOS工艺从微米级开始,经历了亚微米、深亚微米到几十纳米的发展阶段。在几十纳米之后,多晶硅栅MOS管遇到了越来越多的困难,给MOS管的新结构带来了挑战。FinFET和GAAFET就是两种典型的MOS管新结构(见图2.14),它们为摩尔定律能够延续到几纳米奠定了基础。

图2.14 FinFET和GAAFET结构示意图

鳍式场效应晶体管(Fin Field-Effect Transistor,FinFET)的结构由加州大学伯克利分校胡正明教授团队于1999年提出 [10] ,2011年Intel公司首先在其22nm工艺节点上实现商用。Fin是鱼鳍的意思,FinFET是根据晶体管的形状与鱼鳍相似而得名。

从FinFET的三维结构可以看出,FinFET的栅极像城墙,而沟道就是城门洞,FinFET的源极和漏极分别在城门的内外两侧。如果把普通CMOS看成2D平面器件,那FinFET就相当于一个3D立体器件,它把平面沟道变成立体沟道,利用高度增加沟道截面积,减小了MOS管的平面面积。FinFET为摩尔定律在几十纳米后继续向前推进创造了条件,成为目前高端芯片的主流器件。

随着FinFET尺寸的缩小,单鳍FinFET的电流驱动能力不断下降,短沟效应和衬底电流泄漏也变得越来越严重,当工艺推进到5nm以下时,单鳍FinFET的电流驱动能力明显不足,使FinFET工艺无法继续前进,正在逐步被全包围栅极场效应晶体管(Gate-All-Around FET,GAAFET)所取代。

GAAFET的沟道完全被栅隔离包围,这样不仅可以提高栅的控制能力,而且衬底电流泄漏也比FinFET少很多 [11] 。为了提高驱动能力,GAAFET只需要在平面的垂直方向多堆叠几个沟道(纳米薄片)即可,不会占用更多平面资源,而多鳍FinFET则需要占用更多的平面面积,在3nm、2nm及以下的工艺中,GAAFET几乎是唯一的选择。

CMOS工艺能加工的最小栅长 L 通常定义为工艺的特征尺寸,即多晶硅栅线条的最小宽度。CMOS工艺按照摩尔定律发展,特征尺寸也从最初的十几微米发展到现在的几纳米,后面的路将越走越难,摩尔定律什么时候终结也是业界正在探讨的问题。就连Intel公司这样的IDM(Integrated Device Manufacture,可简单理解为设计和制造一体)公司也感到力不从心,打算放弃追求最小线宽,而把重点放到芯片的3D封装上,以便从另一个角度提升单颗芯片的计算能力和系统集成度。

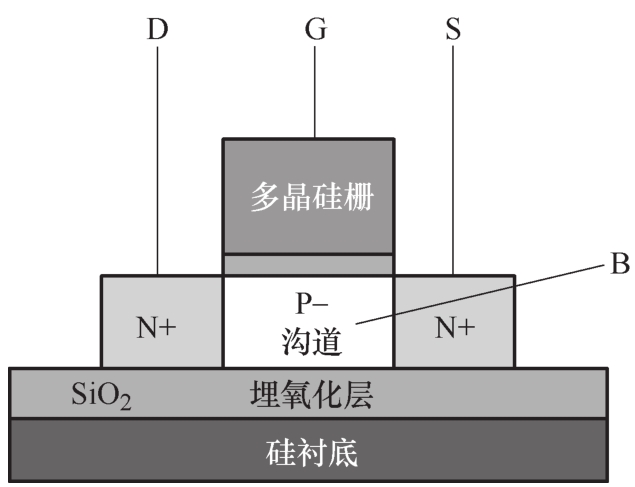

绝缘体上硅(Silicon On Insulator,SOI)是另外一种比较重要的CMOS工艺,该工艺是在硅衬底和背衬底之间引入了一层埋氧化层,将MOS管与衬底进行了绝缘隔离,其结构如图2.15所示。SOI消除了MOS器件与衬底的寄生结电容,其工作速度快,电路功耗低 [12] 。由于它比普通CMOS工艺复杂,集成度也相对较低,所以主要应用于高速、超低功耗和抗电离辐射等领域。

图2.15 SOI结构示意图

除了MOS管外,CMOS工艺还可以制造电阻、电容和晶体管等其他类型的器件,它们也是构成CMOS模拟集成电路的重要器件,下面进行介绍。