能变成电路的Verilog表达叫作可综合,在设计电路时,只能使用可综合的语法表述,而在仿真时,由于只在计算机上运行,不流片,可使用不能综合的高级语法,以增加语言表达的灵活度和复杂度。

本节主要向大家介绍可综合的设计语法,对于不可综合的语法,将在第3章的仿真中介绍。

可综合语法中,常用的电路表述只有两种,一种assign,另一种是always。在表2—1中可以找到这两种表述的例子,其中,与门的表述如下:

assign z = a & b;

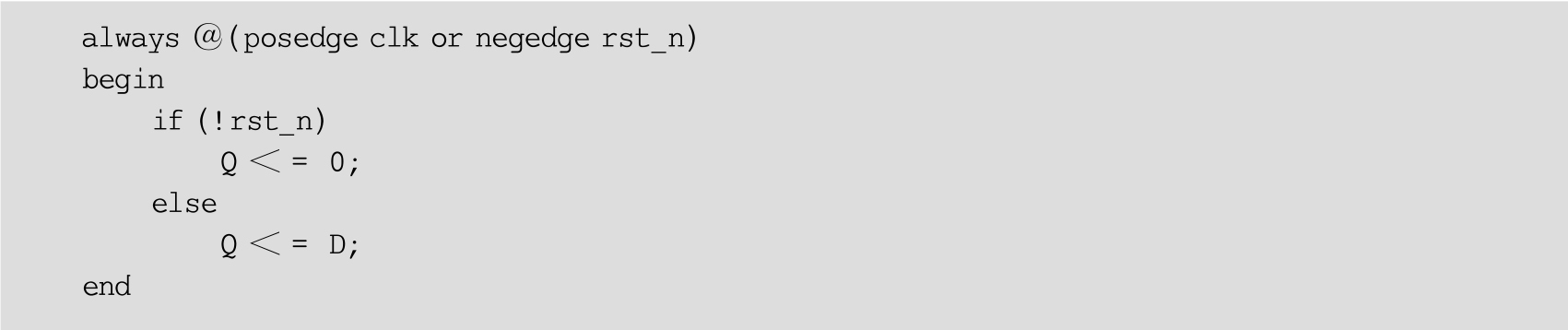

触发器的表述如下,称为always块。注意,时序逻辑的语法中等号用的是“

=”,叫非阻塞赋值,而组合逻辑中的赋值用“=”,叫阻塞赋值。@括号中的列表叫敏感列表,意思是always块输出的Q对列表中的信号保持敏感,如果敏感信号动,则Q也会动。posedge clk意思是时钟的上升沿,negedge rst_n意思是复位信号的下降沿。将这两个沿写在敏感列表中,意思是最终的输出Q对两个沿敏感,而不是对电平敏感,这体现了时序逻辑的本质。语法中,begin和end,相当于C语言中的“{”和“}”,if(!rst_n)后面跟着Q

=”,叫非阻塞赋值,而组合逻辑中的赋值用“=”,叫阻塞赋值。@括号中的列表叫敏感列表,意思是always块输出的Q对列表中的信号保持敏感,如果敏感信号动,则Q也会动。posedge clk意思是时钟的上升沿,negedge rst_n意思是复位信号的下降沿。将这两个沿写在敏感列表中,意思是最终的输出Q对两个沿敏感,而不是对电平敏感,这体现了时序逻辑的本质。语法中,begin和end,相当于C语言中的“{”和“}”,if(!rst_n)后面跟着Q

=0,此句可以用begin和end括起来,也可以不用,就像C语言中,if后面的句子,如果只有一句话,则可以不用大括号。

=0,此句可以用begin和end括起来,也可以不用,就像C语言中,if后面的句子,如果只有一句话,则可以不用大括号。

always块不仅可以用来表示时序逻辑,也可以用来表示组合逻辑,如下例所示,它是与门逻辑的另一种表述方式。注意,这里仍然用阻塞赋值。初学者会误认为凡是always块,都是时序逻辑,实则不然,但是可以确定的是,凡是组合逻辑,都用阻塞赋值,凡是时序逻辑,都用非阻塞赋值。下例中,@后面也有敏感列表,但用*代替了,*在这里表示省略描述。综合器在看到这种省略描述后,会自动在always块中寻找与输出 z 相关的输入信号,自动填入敏感列表中。在本例中,工具会自动将 a 和 b 作为输入填进去。当逻辑较大、输入信号很多时,人工填写可能会遗漏,完全依靠人工是没必要的,用工具自己寻找的方式最保险,所以写Verilog时,对于这种always块组合逻辑,敏感列表都填*。

always@( * )

begin

z = a & b;

end

从上述3个例子中可以总结出Verilog的语法规律:

(1)时序逻辑,必须使用always块,并同时使用“

=”非阻塞赋值。在其敏感列表中,必须出现时钟信号的边沿和复位信号的边沿。

=”非阻塞赋值。在其敏感列表中,必须出现时钟信号的边沿和复位信号的边沿。

(2)组合逻辑,可以使用assign,也可以使用always块,但它们的赋值都是“=”阻塞赋值。若使用always块,则敏感列表中使用*。如果遇到always块的敏感列表带*,则可以直接判定为组合逻辑。

上述两个关键词assign和always,以及3个例子代表的3种不同表达,可以看作可综合Verilog的全部语法,读者可以简单记忆为“两词三例”。本书后面的内容,凡是可综合的电路,都只使用两词三例来描述。虽然Verilog语法中会给使用者提供多种选择,笔者也见过组合逻辑用“

=”的例子,但目前正规设计,基本只使用两词三例,其他复杂的语法现象几乎不使用。在这里需要强调的是,Verilog中的语法表达,描述的全部是电路,因此,例子里面的

z

、

a

、

b

、clk、rst_n、Q、D都称为信号,在电路中都是实实在在的金属连线,切勿按照C语言的习惯,误将其称为变量。

=”的例子,但目前正规设计,基本只使用两词三例,其他复杂的语法现象几乎不使用。在这里需要强调的是,Verilog中的语法表达,描述的全部是电路,因此,例子里面的

z

、

a

、

b

、clk、rst_n、Q、D都称为信号,在电路中都是实实在在的金属连线,切勿按照C语言的习惯,误将其称为变量。