数字前端编写RTL很简单,只要是个文本编辑器都能写,例如Windows上的记事本、写字板、Word等,但工程师一般用Vim,或其图形化增强版Gvim,因为该工具有很多特性适合RTL编写,该工具在Linux和Windows上都能用,而且是免费的。

要了解设计中主要的电子设计自动化(Electronic Design Automation,EDA)工具,必须先了解EDA软件的市场格局和相关开发商。世界三大EDA巨头分别是铿腾(Cadence)、新思(Synopsys)和明导(Mentor)。粗略地说,数字设计较常用Synopsys,而模拟设计常用Cadence。实际上,Synopsys和Cadence都有完整的设计工具链,只是有用户认可度和市场占有率的区别。Mentor在一些细分领域有优势。

在数字IC设计方面,首先需要对RTL进行仿真。最常用工具是Synopsys的VCS,Cadence的仿真工具叫Insicive,也叫irun。这些工具可以胜任前仿、后仿、UVM架构的仿真等。Cadence的irun与模拟设计工具Virtuoso中集成的AMS仿真工具相结合,支持数字模拟电路混合仿真。

数字设计离不开波形查看工具。看波形的软件一般会集成在仿真工具中,随仿真软件一同安装。VCS的波形软件叫DVE,而Insicive也可以用SimVision来查看波形,但是,在这个领域,一家名为Novas的公司所编写的软件,以其明快的界面、方便的功能、快捷的操作,异军突起,得到了广泛认可,它就是Verdi(以音乐家威尔第的名字命名,其前身叫Debussy,以音乐家德彪西的名字命名)。Verdi现已被Synopsys收购,成为其工具链家族的一员。Mentor的仿真和看波形软件叫ModelSim,该软件主要用于FPGA功能的仿真。

编译C语言时有语法检查,RTL同样需要检查语法的工具。最常用的是Atrenta公司开发的Spyglass,它不仅能检查单纯的语法错误,还能进行跨时钟域处理方案的可靠性检查,该软件甚至可以在内部执行综合、功耗评估和简单的布局布线,使它能全方位地给出设计建议。该工具也已被Synopsys收购。Cadence相对应的检查工具是nLint。

综合工具,即将RTL转换为实际电路的工具,最常用的是Synopsys的Design Compiler(DC)。该工具内部还带有一些Synopsys开发的库,能够帮助设计者减小面积,提高性能,例如加法器、乘法器等,这些设计好的子模块在DC中被称为DesignWare(DW)。可以是让工具自动从RTL中识别出可用DW替换的代码,也可以是设计者手动例化DW模块。Cadence相应的工具叫Genus(原名为RTL Compiler)。

版图自动布局布线的软件,Synopsys有ICC2(旧版为ICC),Cadence有Innovus(原名Encounter),两个软件都被广泛使用。由于两个软件的操作命令不同,后端工程师往往只掌握其中一种。Synopsys为了增强客户的黏性,开发了一个银河(MilkyWay)流程,从前端到后端,通过专用的二进制文件格式(db)传输,占用空间小,处理效率高,但也有许多公司使用DC综合,再将网表导入Innovus进行布局布线。

当版图完成后,需要对整个设计的时序、功耗进行评估,即SignOff步骤。对应的工具是Synopsys的Prime Time(PT)和Cadence的Tempus。目前,PT已成为业内SignOff的标准。实际上,时序分析在DC中也能做,但两者在分析方法、细节考虑全面度、分析速度等方面存在差异。在综合时使用DC检查,而在SignOff时,使用PT检查。

从RTL到综合网表的过程,以及从综合网表到后端网表的过程,可能意外地改变原有功能和设计意图。为了检查出此类风险,需要一种形式验证工具,也称为逻辑等效性检查(Logic Equivalence Check,LEC),将RTL和网表进行一一对照。Synopsys开发的工具是Formality,Cadence开发的工具是Conformal。

进入设计版图阶段,可以确定走线的延迟。该值受到信号负载、线路长短、粗细、周围线路等多重影响,需要用模型和查表进行计算才可以得到确切的值。该过程称为寄生参数的提取,一般使用Synopsys的工具StarRC。提取出来的信息可用于PT进行SignOff,也可以输入VCS中进行后仿。

上述工具,最主要的控制语法是TCL语言。EDA工具大多以该语言为基础,扩展出各种专用命令,因此,TCL基本语法的掌握是必不可少的。

以上是数字设计的基本工具,还有一些更加细分的工具类型,如仿真加速器等,本书不再赘述。EDA厂商也不只有3家,例如国内的华大九天等厂商也开发了一些性能优异的工具软件,读者可以在今后的工作中慢慢探索。总体而言,数字芯片的设计工具繁多,步骤复杂,因而入行的门槛也比较高,但希望读者不要被繁杂奇怪的工具名称和专业术语所吓倒,工具终归是工具,设计芯片最重要的是设计思想,验证芯片最重要的是案例设计和环境仿真,这些人类智慧是工具很难代替的。只要读者抓住重点,通过熟悉前人的脚本,结合查询芯片论坛的讨论,学会基本的工具使用方法还是比较容易的。切不可被EDA厂商的各种概念宣传所左右,而忘记了芯片设计和验证的真正初衷。

模拟IC设计常用的EDA工具比较简单,主要是Cadence公司的Virtuoso。与数字设计中繁多的工具不同,Virtuoso能满足大部分设计需求,例如绘制并仿真原理图、绘制并仿真版图、数模混合仿真等。实际上,Virtuoso更像集成开发环境(Integrated Development Environment,IDE),它包含很多独立的设计工具,如仿真工具Spectre等。Mentor的Calibre可以用来提取寄生参数、进行DRC和LVS检查,是比较公认的模拟SignOff工具。最终的模拟版图必须用Calibre检查通过后才能放心流片。

新人往往会有一个误区,认为EDA软件是单纯的软件,普通软件公司也可以进行EDA开发。实际上,EDA软件是芯片制造技术和软件技术结合的产物。EDA厂商需要与Foundry厂商紧密合作,才能获得有关的生产细节数据,从而帮助用户进行更加准确的仿真、寄生参数的提取、规则的检查。不同EDA工具抽取的寄生参数可能不同,仿真结果也可能不一样,原因可能是不同的工具获得的工艺数据不同。可见,EDA和Foundry是相辅相成的,具有很强的互利性和垄断性。国内EDA厂商若想打破国际巨头的垄断,不能仅靠软件技术,还要与各大Foundry厂达成战略合作,共享工艺数据,这样才能做出有实用价值的EDA工具。

人们通常习惯于静态思维,误以为设计方法、设计工具是长期不变的,设计EDA的公司也是长期存在的。从上文介绍的EDA工具链中可以看到,芯片行业是一个经常发生变化的行业,企业间的收购与合并、产品线的搭建与裁撤是常有的。像Atrenta和Novas这样的名字,曾经为芯片设计者所熟知,如今也渐渐地消失在历史长河之中,只在一些公司服务器的EDA安装目录中偶尔会出现,这也算是一种时代的印记吧。

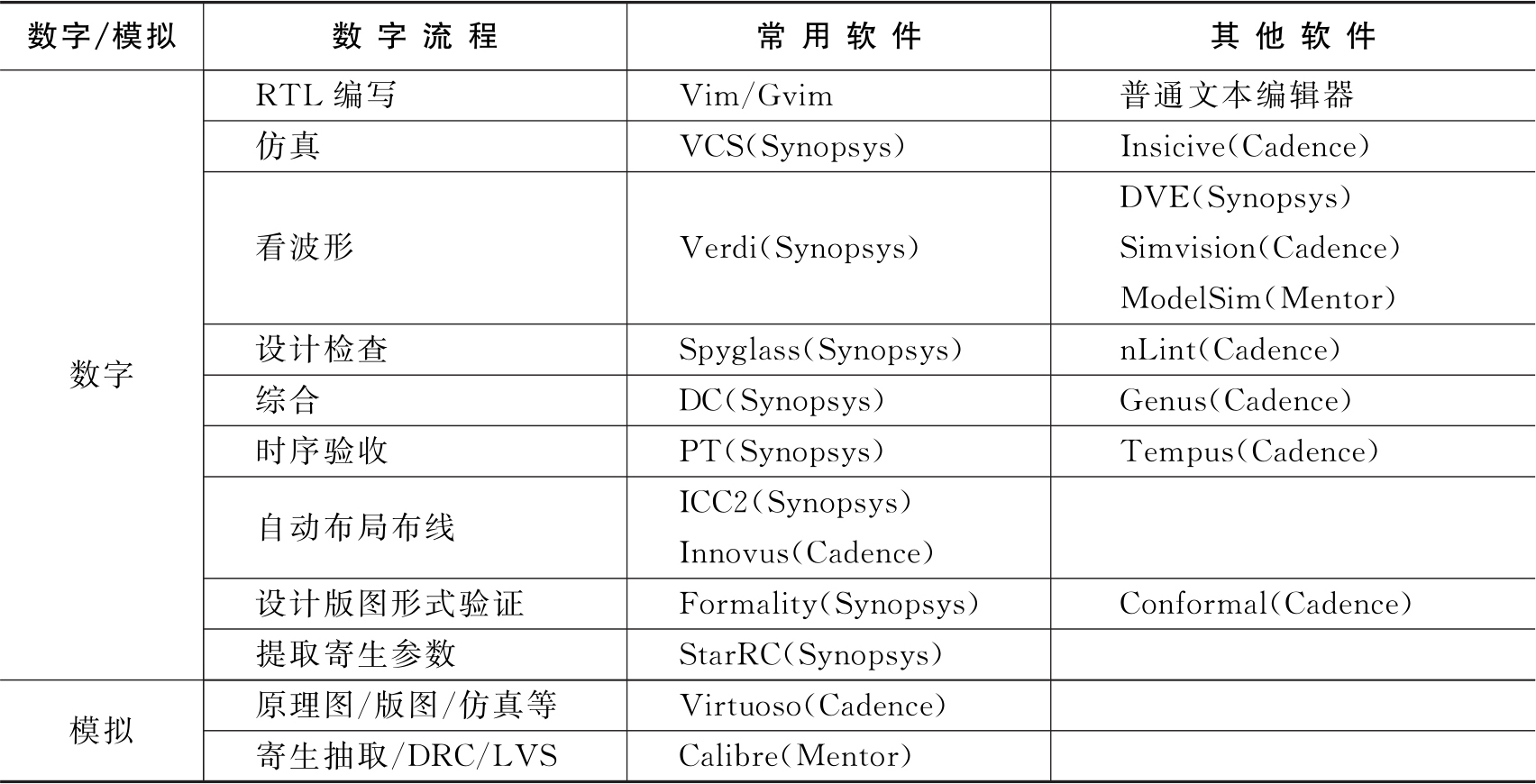

IC设计中常用的EDA软件见表1—1,括号中为公司名。

表1—1 常用的EDA软件(括号中为公司名)