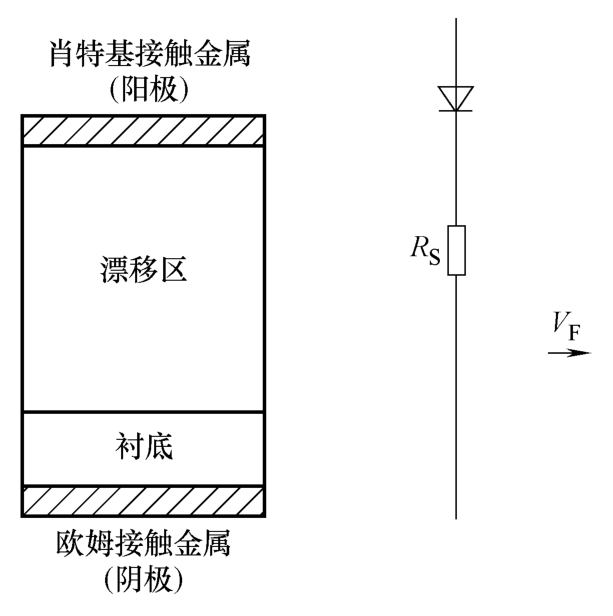

单极型功率二极管为肖特基整流二极管,利用金属-半导体势垒实现整流。功率肖特基二极管的结构还包含漂移区,如图1.4所示。由于漂移区的电阻随着反向电压的增加而迅速增加,所以商用的硅肖特基二极管的阻断电压一般在100V以下。对于实际应用而言,当超过该值时,硅肖特基二极管的通态压降变大。对于硅PiN二极管,尽管其开关速度较慢,但其通态压降低,可以用来设计具有较大击穿电压的器件。

图1.4 功率肖特基势垒整流器结构及其等效电路

硅肖特基二极管遇到的基本问题之一是,虽然通态压降可以设计得较小(对于耐压较低的肖特基二极管),但反向漏电流较大。这与肖特基势垒降低效应和击穿前雪崩倍增现象有关,当反向电压从零增加到工作电压时,漏电流增加一个数量级。

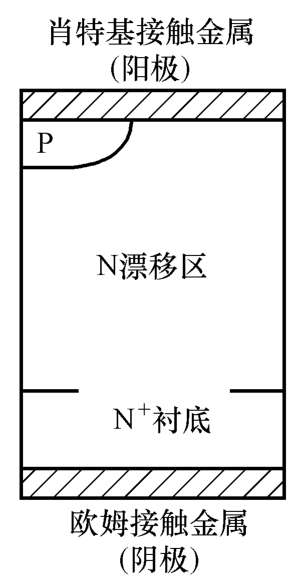

减小功率肖特基二极管漏电流的一种方法是通过加入如图1.5所示的PN结。这种结构被称为结势垒控制肖特基(JBS)二极管,它已经有效地用于提高低压硅器件和高压碳化硅器件的性能。

图1.5 结势垒控制肖特基(JBS)整流器结构

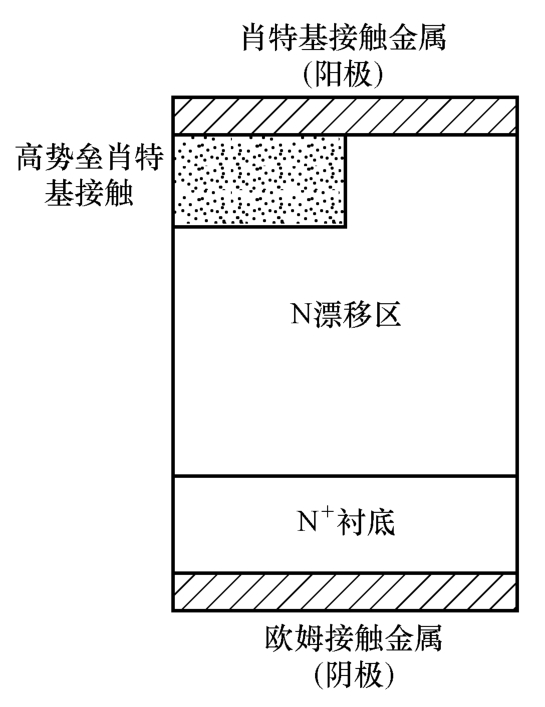

另一种屏蔽阳极肖特基接触高电场强度的方法是使另一个肖特基接触具有较大的势垒高度。将具有较大势垒高度的肖特基接触放置在沟槽内可以增强屏蔽效果,如图1.6所示。因此,这种结构也被称为沟槽肖特基势垒控制肖特基(TSBS)整流器。尽管这种结构首先提出来是用于改善硅器件的,但由于宽禁带半导体具有较大的势垒高度,所以这种结构更适用于碳化硅器件。

图1.6 沟槽肖特基势垒控制肖特基(TSBS)整流器结构

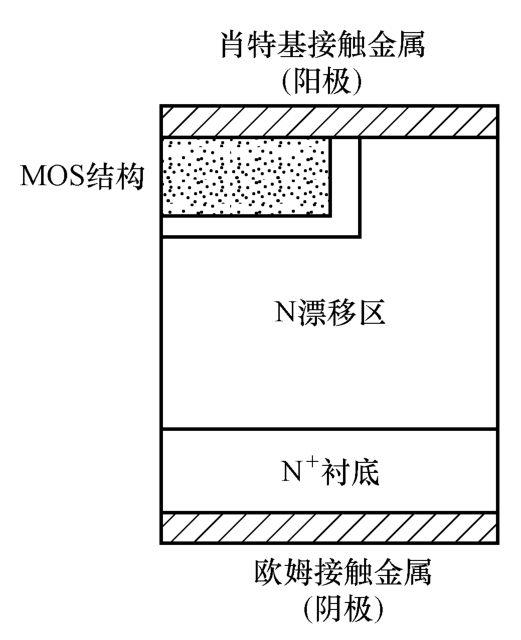

原则上,还可以通过加入MOS结构来屏蔽阳极肖特基接触,如图1.7所示。在沟槽内形成MOS结构能够提高屏蔽效果。这种方法对于具有成熟MOS技术的硅器件是可行的。但在碳化硅结构中,这种方法是不可取的,因为在氧化物中会产生非常高的电场强度,从而会导致器件失效。在硅器件中,这个想法已经与电荷耦合现象结合,以此来减小漂移区的电阻。

图1.7 MOS势垒控制肖特基(MBS)整流器结构