当前的FPGA设计规模越来越大,好在FPGA芯片的规模也越来越大,但设计的复杂度也越来越高,体现在较多的输入/输出引脚、较高的总线位宽、较大的扇出及较高的逻辑级数。带来的直接后果是编译时间过长、资源利用率过高、次优布局、布线资源消耗太多、时序收敛较为困难等,这也是目前FPGA设计面临的一些挑战。另外,有些FPGA设计要求时钟运行在300MHz甚至400MHz以上,这样面临的挑战将会更多。

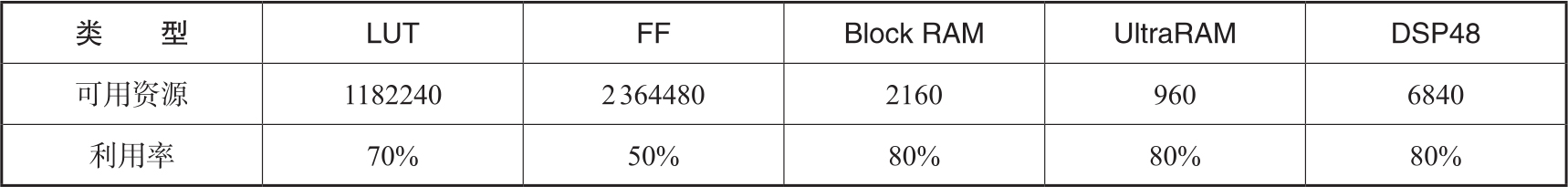

以VU9P为例,其可用资源及某设计中的资源利用率如表1—6所示。Vivado版本为2018.3,服务器操作系统为Linux 64位,完成一次编译(从综合到生成.bit文件)至少需要十几个小时。当设计的时钟频率为400MHz时,完成一次编译就需要二十多个小时甚至更长,而有时还无法实现时序收敛,导致反复迭代,消耗更多时间。

表1—6

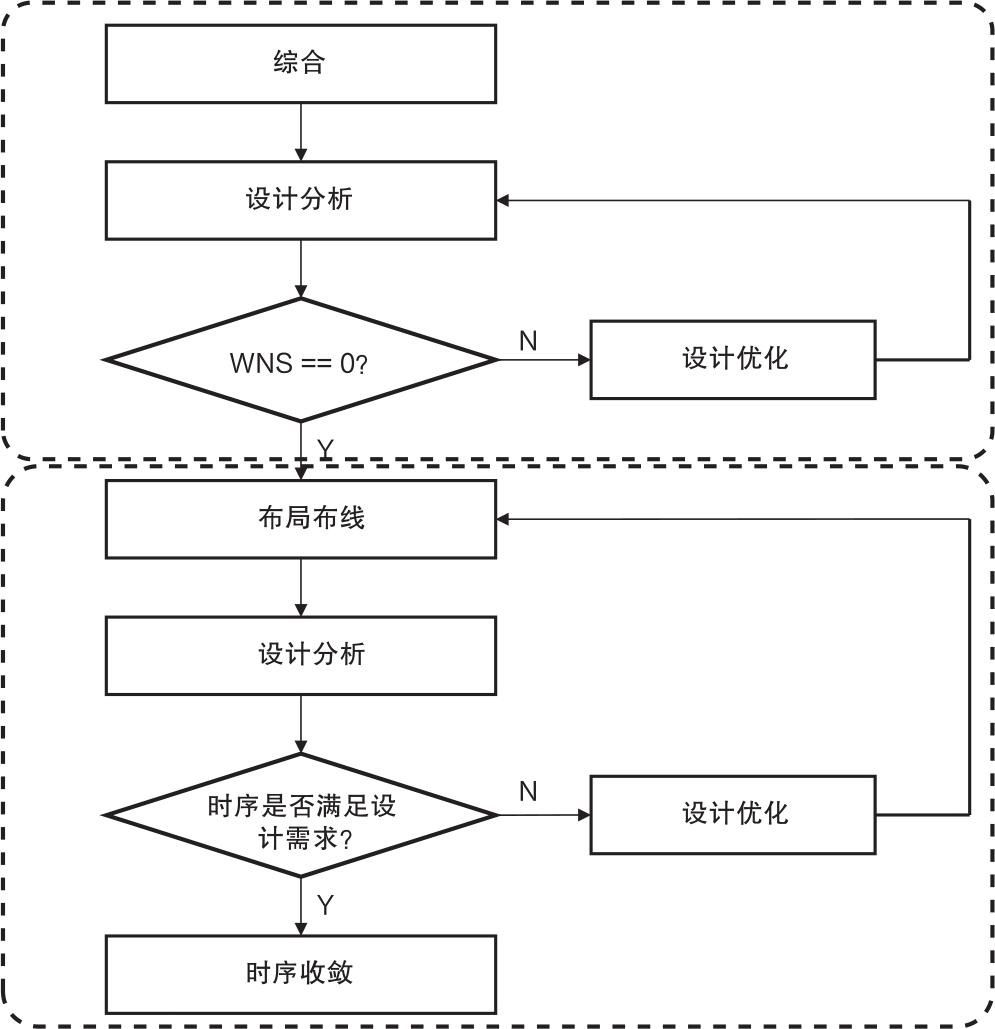

在这些挑战中,时序收敛在多数情况下是设计者面临的最大挑战。传统的时序收敛流程如图1—31所示,分为两大阶段:综合阶段和布局布线阶段。综合阶段只要满足WNS等于0即可进行布局布线,这个目标通常比较容易实现;而布局布线阶段的时序收敛往往牵涉多方因素,需要设计者对工具特性、设计本身都有深入理解,同时有一定的经验积累。因此,这个过程有可能出现反复迭代。

图1—31

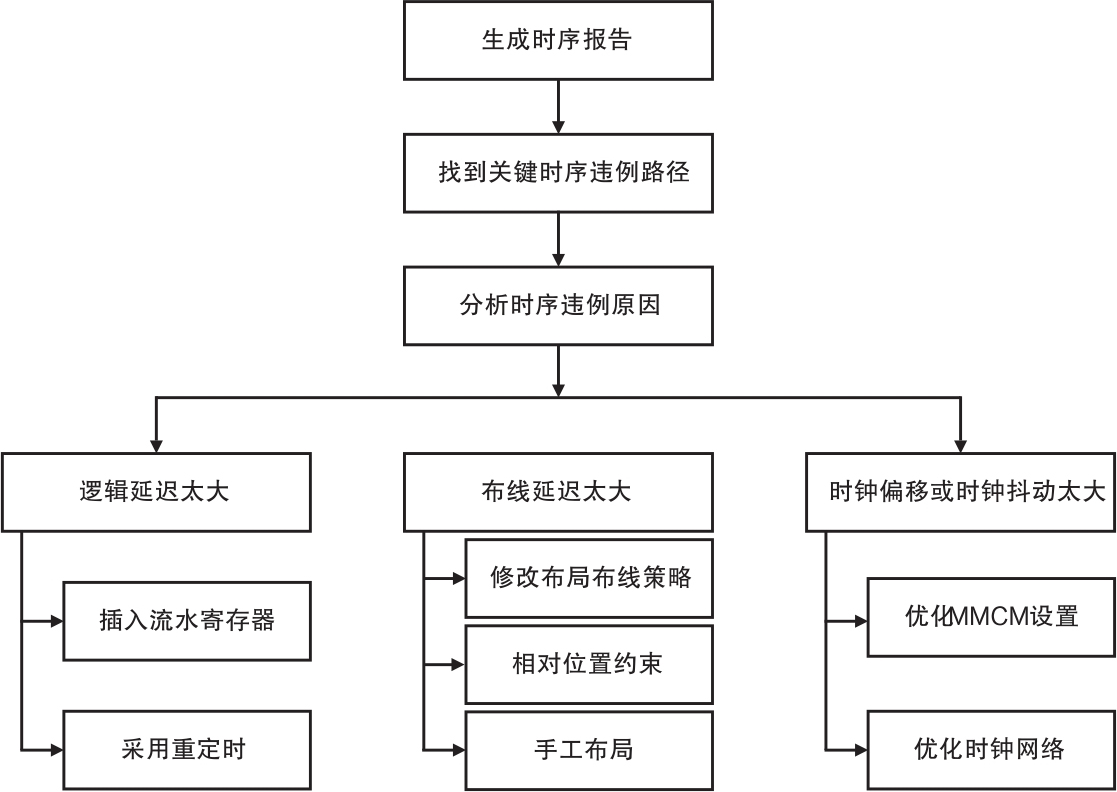

针对布局布线阶段的时序收敛,通常需要采用图1—32所示流程。这个流程的关键点是分析时序违例原因,分析的对象并不是所有的时序违例路径,而是最为关键的几条违例路径。实践表明,往往只需要修复这些关键的违例路径,工具会自动修复其他违例路径。找到原因之后才能有的放矢找到解决办法。一般情况下,建立时间违例原因包括:逻辑延迟太大、布线延迟太大、时钟偏移或时钟抖动太大。若确定原因是逻辑延迟太大,那么可能的解决办法有两种:插入流水寄存器和采用重定时。前者需要修改代码,由于增加流水寄存器会导致从输入到输出所需的时钟周期个数发生改变,涉及多条路径的数据需要重新对齐,改动量可能会比较大;后者无须改动代码,但需要确定是在综合阶段设置重定时还是在布局布线阶段设置重定时,是全局设置(使用全局设置选项)还是局部设置(使用模块化综合技术)。两种解决办法到底哪个是最优解,这些都需要尝试,也都需要设计者积累足够的经验,同时还比较耗时。尤其是多个解决办法无法并行执行时,耗时最为明显。

为了应对这些挑战,我们不仅要从设计本身入手,还要从EDA工具这个角度入手,以期望工具能够帮助我们缩短编译时间、提高编译质量。这就要提到Vivado ML(Machine Learning)版本。

图1—32

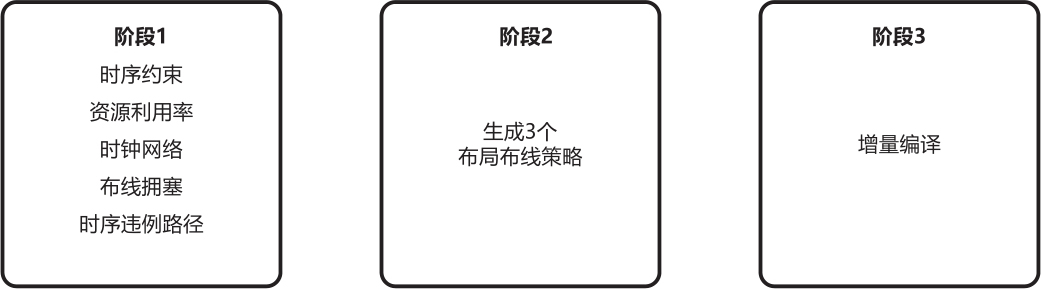

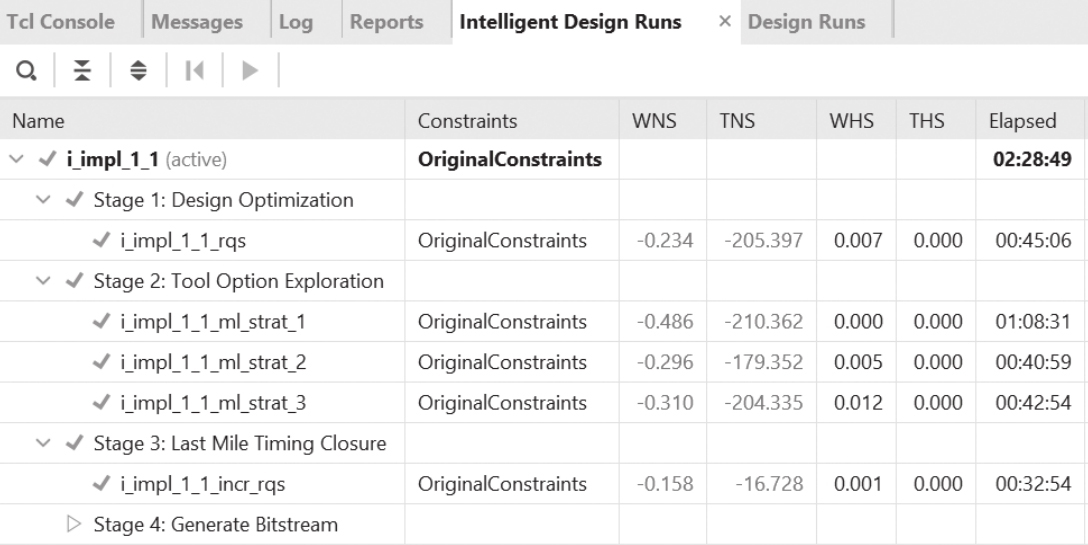

Vivado ML的首个版本是2021.1,其在设计的多个阶段引入了机器学习算法。例如,在综合阶段,引入了基于机器学习算法的门级优化,从而大大提高了综合质量并且将综合时间平均缩短了30%;在布局布线阶段,引入了基于机器学习算法的拥塞评估和延迟评估,从而有效减少了迭代次数并且将布局布线时间平均缩短了20%;最大亮点在于引入了智能设计流程IDR(Intelligent Design Run)。该设计流程专门为时序收敛服务,共包含3个阶段,如图1—33所示。第一阶段,工具会从5个方面即时序约束、资源利用率、时钟网络、布线拥塞和关键路径进行优化,生成相应的优化建议(通常以Tcl脚本方式呈现),并自动将这些建议施加到对应的子步骤(实现阶段的4个子步骤,对应的Tcl命令分别为opt_design、place_design、phys_opt_design和route_design)中。该阶段结束后,工具会将所有的布线后的网表进行比较,选取WNS(Worst Negative Slack,最差建立时间裕量)最大者,获取其中有效的优化建议供第二阶段或第三阶段使用。第二阶段在第一阶段的基础上(继承了第一阶段的结果,即继承有效的优化建议),工具会采用机器学习算法生成3个布局布线策略。第三阶段为增量编译阶段。实验数据表明,IDR可以给设计带来平均10%的收益,即 F max (设计可运行的最高时钟频率)可提升10%。

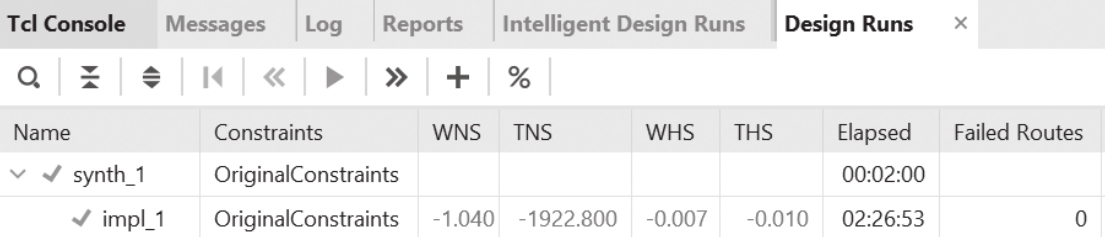

IDR有单独的窗口,如图1—34所示,采用一键式操作,中间过程无须人工干预。从这个角度而言,IDR对设计者的经验积累要求并不高。图1—35显示了未使用IDR时最终的时序性能。与图1—34对比,可以看到IDR将WNS从-1.040ns提升到-0.158ns,同时也修复了保持时间违例。

图1—33

图1—34

图1—35