20世纪80年代,美国斯坦福大学John L.Hennessy研究团队决定创建一套新的CPU指令集,以获取业界最高的效率(比如性能相对于面积和功耗的函数)。不久之后,他们成立了MIPS计算机系统公司,并发布了首批商用微处理器架构:MIPS Ⅰ和MIPS Ⅱ。MIPS指令集迅速成为RISC的标杆。最初许多MIPS实现瞄准计算机类应用,比如工作站和服务器。最近几年来,MIPS CPU很大程度上销售于嵌入式应用中,包括移动平台、可穿戴、家庭娱乐、网络和物联网等。1991年MIPS Ⅲ指令集发布,首次加入了64位整数和地址。MIPS Ⅳ和MIPS Ⅴ指令集加入了改进浮点操作和一套用于提升生成代码和数据移动效率的指令。2002年,MIPS 32和MIPS 64两套指令集发布,这标志着32位和64位MIPS CPU同时得到了越来越多的使用。

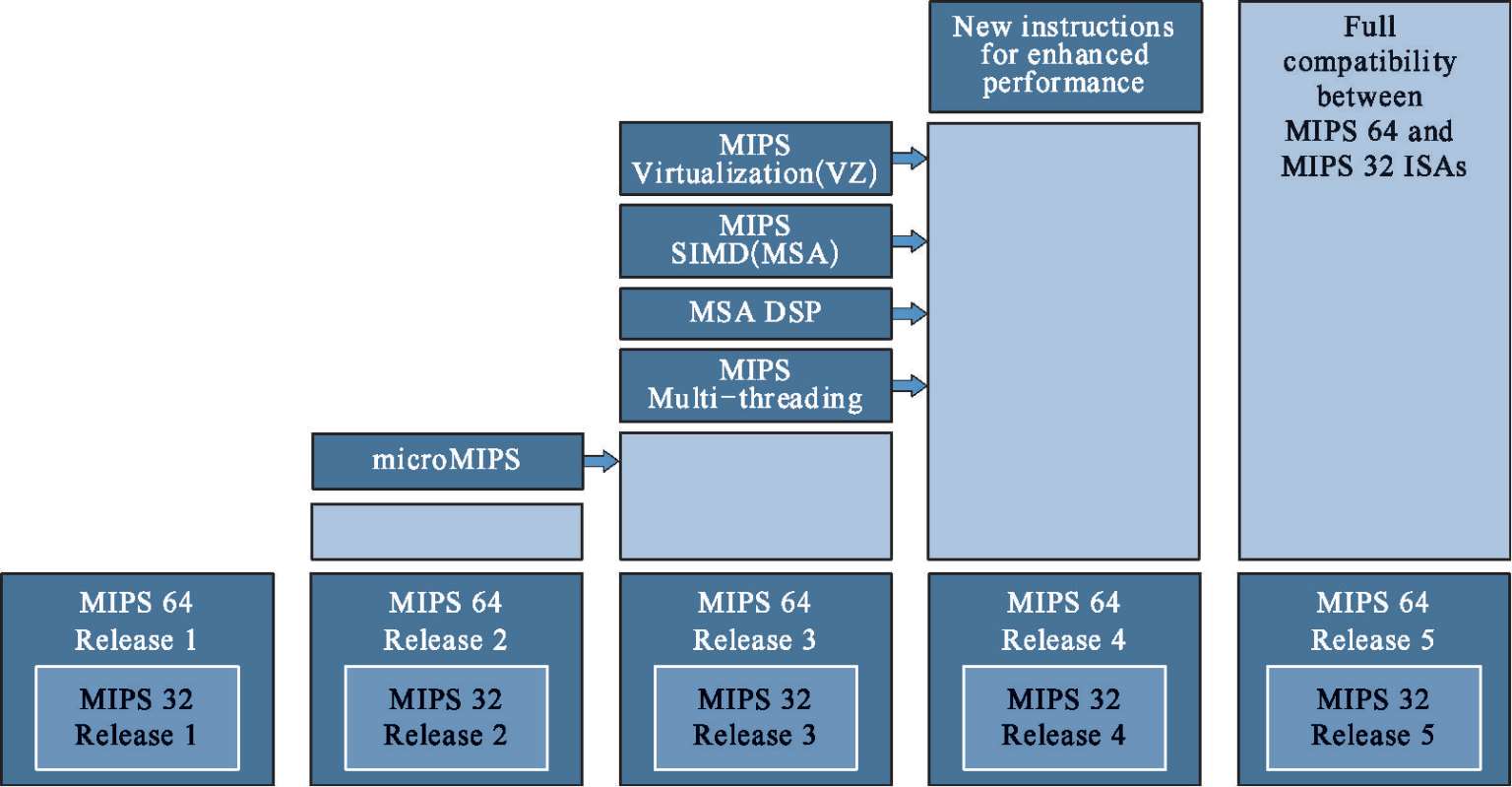

截至目前,MIPS 32和MIPS 64架构相对于竞争处理器架构,拥有显著的性能、功耗和面积优势。这些优势源于下列原则中的持续进步:微体系结构改进,系统级更好的集成,移动领域更低工艺节点的迅速引进,以及操作系统和编译器设计的惊人演化。MIPS 32架构基于MIPS Ⅱ指令集,加入了MIPS Ⅲ、MIPS Ⅳ和MIPS Ⅴ中少数的精选指令,以提升生成代码和数据移动的效率。MIPS架构演变如图3-14所示。

图3-14 MIPS架构演变

MIPS 64架构基于MIPS Ⅴ指令集,并与MIPS 32架构向后兼容。此外,同时贯穿于两个架构的演化中,每个新MIPS指令集都与前代指令集向后兼容。MIPS 32和MIPS 64架构同时用于解决成本敏感型广泛应用的高性能和低功耗需求。

32位MIPS处理器采用五级流水线结构,支持中断处理,提供可选的配置,观察并控制系统缓存或时钟、虚实地址转换等操作,指令执行速度接近每个时钟周期执行一条指令,是RISC架构中的经典之作。

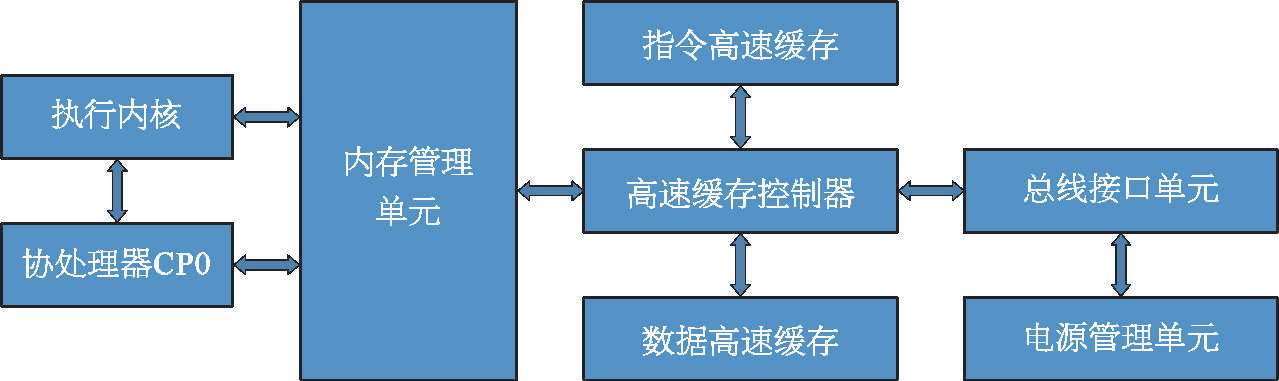

MIPS处理器中与内存管理单元(MMU)有关的各功能模块的连接如图3-15所示,其中包括执行内核、协处理器CP0、高速缓存Cache。执行内核的作用是执行指令,采用load-store结构,在运算过程中,需要将存储器上的数据提前读取到其内部的寄存器堆中,而其内部的寄存器堆包括32个32位的通用寄存器。通常执行内核需要MMU进行虚实地址转换后,使用转换得来的物理地址访问缓存或内存,然后与外部的功能单元进行交互。协处理器CP0用作系统控制,通过配置内部的一系列寄存器来完成配置CPU的工作状态、高速缓存控制、异常控制和MMU控制等工作。总线接口单元负责将经过MMU转换后的地址送到内存中进行指令或数据访问。电源管理单元负责为整个系统供电。MIPS是业界最典型的RISC架构,其指令格式十分简单,按照指令格式可划分为三类,即寄存器类型(R-type)指令、立即数类型(I-type)指令和跳转类型(J-type)指令。

图3-15 MIPS处理器系统框图

龙芯1E300(简称“LS1E300”)芯片是以龙芯GS232E处理器为运行计算中心的高性能应用处理器SoC,提供中断控制器、定时器、RS-232串口控制器、浮点处理器、PCI、I2C、SPI、SpaceWire和存储器等接口(存储器接口支持SDRAM、Flash及ROM)。可靠性计算以龙芯处理器、外围IP为基础,同时对各子模块进行结构级可靠性加固。

GS232E处理器核提供核心运行计算能力,通过串口、GPIO等外设提供IO处理能力,通过PCI接口提供扩展的IO处理能力,在处理器和外设之间通过两级互连结构进行高速连接。

LS1E300芯片互连由高速互连和低速互连两级构成,同时兼顾高速设备和低速设备的性能和功耗需求,两者之间通过桥接实现协同和数据传递。存储控制器提供增强ECC校验,支持SDRAM、ROM、Flash等航天系统常用的主流存储器。

LS1E300芯片基于ASIC方法和商用工艺,采用定制的单元库、IO库和片上存储器。具体特点如下:

(1)64位RISC CPU。

(2)MIPS 32R2标准体系结构兼容。

(3)一个全流水线的64位双精度浮点乘加部件。

(4)16 KB两路组相连指令Cache。

(5)16 KB两路组相连数据Cache。

(6)支持非阻塞的访存。

(7)支持定点多媒体指令。

(8)支持定点DSP指令。

(9)最大支持256 MBSDRAM。

(10)支持SDRAMECC校验功能。

(11)NORFlash最大支持64 MB。

(12)NANDFlash最大支持128 GB。

(13)PCI2.2兼容,32位总线宽度,支持33 MHz总线频率。

(14)SpaceWire接口数据传输速度在2~200 Mbit/s之间。

MIPS寄存器主要包括通用寄存器、特殊寄存器、浮点寄存器。MIPS 32体系结构实现了32个32位的通用寄存器,为第0号寄存器到第31号寄存器,这些寄存器可供指令使用,其中两个寄存器较为特殊:第0号通用寄存器不论指令向里面写入什么值,读出的总是0;而第31号通用寄存器通常被子程序调用指令用来存储返回地址。

尽管除了第0号寄存器外,硬件并没有对寄存器的使用方法进行规定,但是在实际应用时还是需要约定一些规则。硬件并不关心这些规则,不过,如果需要移植其他子程序、编译器或操作系统,那么最好遵循这些惯例。

MIPS体系结构定义了以下3个特殊寄存器:

(1)PC:程序计数器,保存当前执行程序的地址。

(2)LO:保存乘法指令低位结果或除法指令的商。

(3)HI:保存乘法指令高位结果或除法指令的余数。

MIPS体系结构还定义了以下3种浮点寄存器:

(1)32个32位浮点寄存器(FPR)。

(2)5个FPU控制寄存器,用于识别和控制FPU。

(3)8个浮点条件代码,它们是FCSR寄存器中的一部分。

除了32个通用寄存器、3个特殊寄存器、45个浮点寄存器外,在系统控制协处理器中也有很多特权寄存器,用于高速缓存、例外中断情况处理等方面。

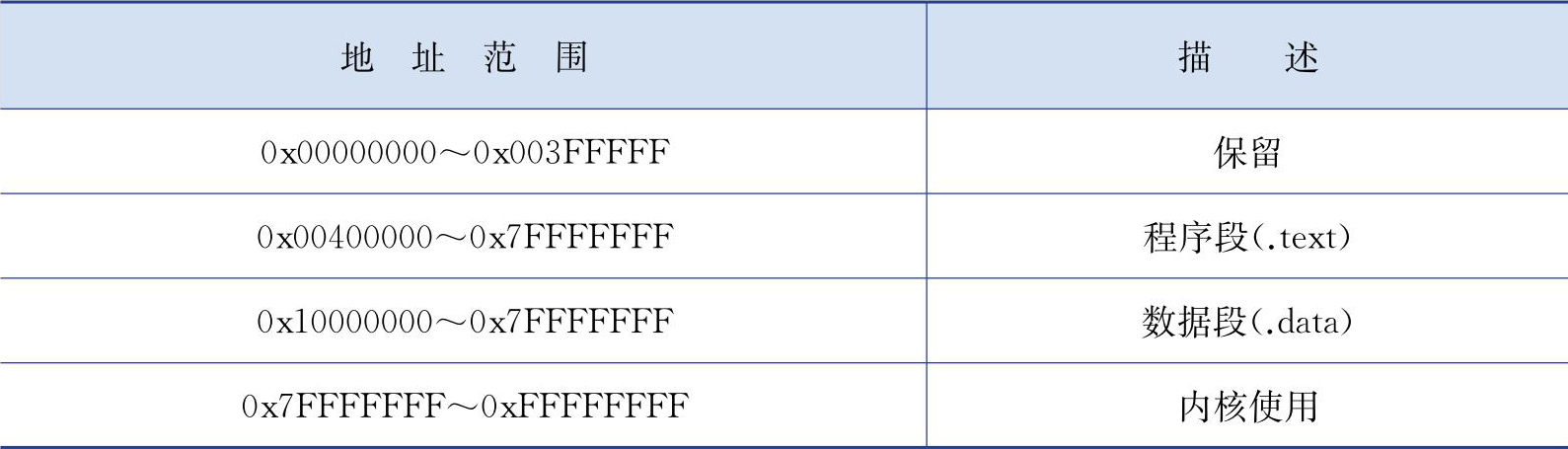

MIPS 32TM支持数据在存储器中可以小端格式或大端格式进行存储,在MIPS 32TM体系结构中,用户可访问的存储空间地址范围从0x00000000~0x7FFFFFFF,共计2 GB。0x7FFFFFFF向下增长至0x10000000,可作为堆栈段。具体见表3-5。

表3-5 MIPS 32TM地址空间划分

数据段又分为静态存储区和动态存储区,分别用于存储全局变量和动态分配的变量。一般而言,取$gp=0x10008000,位于0x1000000~0x10007FFF的一段32 KB空间用作静态存储区,动态存储区从0x10008000向上增长,最高可达0x7FFFFFFF。当以$gp为基地址时,lw和sw指令可向上或向下各寻址32 KB的空间,共计64 KB。堆栈段从0x7FFFFFFF开始向下增长,最低可增长至0x10000000,用于存储。对于MIPS而言,使用Havard架构,默认程序总是0x00000000启动,数据总是从0x00040000开始存储,而且所有外设(如串口)均映射在数据存储空间,即使用存储器映射IO的形式。配置程序段和数据段的地址是通过设置链接器(linker)的脚本(script)完成的。

(1)MIPS的异常机制。MIPS对异常处理的方法是给异常分配一些类型,由软件给它们定义一些优先级,然后由同一个入口进入异常分配程序,在分配程序中根据类型及优先级确定该执行哪个对应的函数。这种机制对两个或几个异常同时出现的情况也是适合的。

异常处理函数执行完成后,会回到异常分配函数那里。异常分配函数中有一个eret指令,用于回归原来被中断的程序继续执行;eret指令会把中断响应打开,并把状态级由kernel转到user级,并返回原地址继续执行。

(2)中断。MIPS CPU有8个独立的中断位(在Cause寄存器中),其中,6个为外部中断、2个为内部中断(可由软件访问)。一般来说,片上的时钟计数/定时器,会连接到一个硬件位上去。在软件中实现中断优先级的方案,给各种中断定优先级;CPU在运行时总是处于某个优先级(即定义一个全局变量);中断发生时,只有等于高于CPU优先级的中断优先级才能执行(如果CPU优先级处于最低,那么所有的中断都可以执行);同时有多个中断发生时,优先执行优先级最高的那个中断程序。