STC32G12K128单片机所有的I/O端口均有4种工作模式:准双向端口/弱上拉(标准8051输出端口模式)、推挽输出/强上拉、高阻输入(电流既不能流入也不能流出)、开漏输出。可使用软件对I/O端口的工作模式进行配置。与并行I/O端口相关的SFR和XFR如表3.23和表3.24所示,学习时,应重点掌握端口数据寄存器与端口配置寄存器。

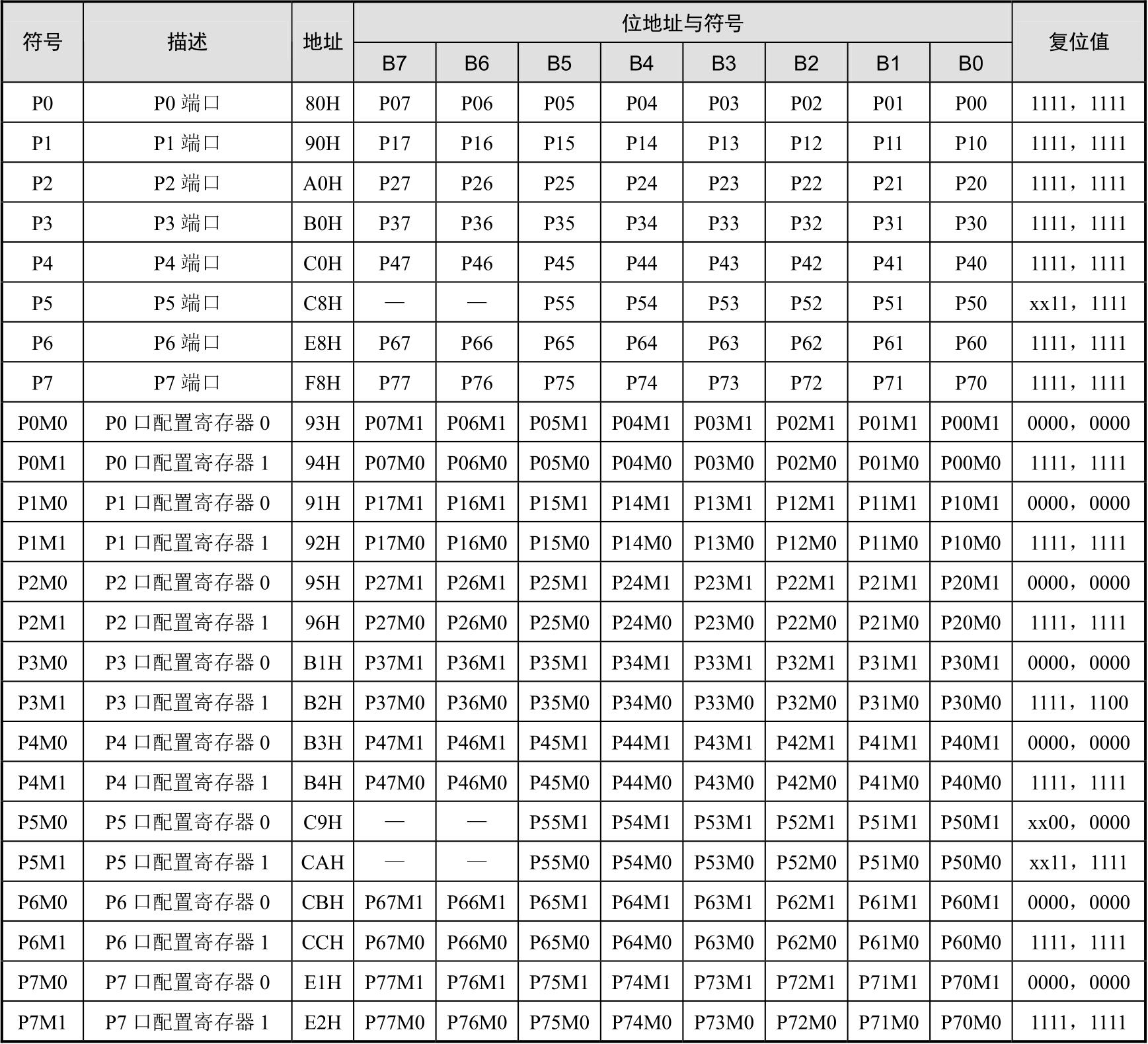

表3.23 与并行I/O端口相关的SFR

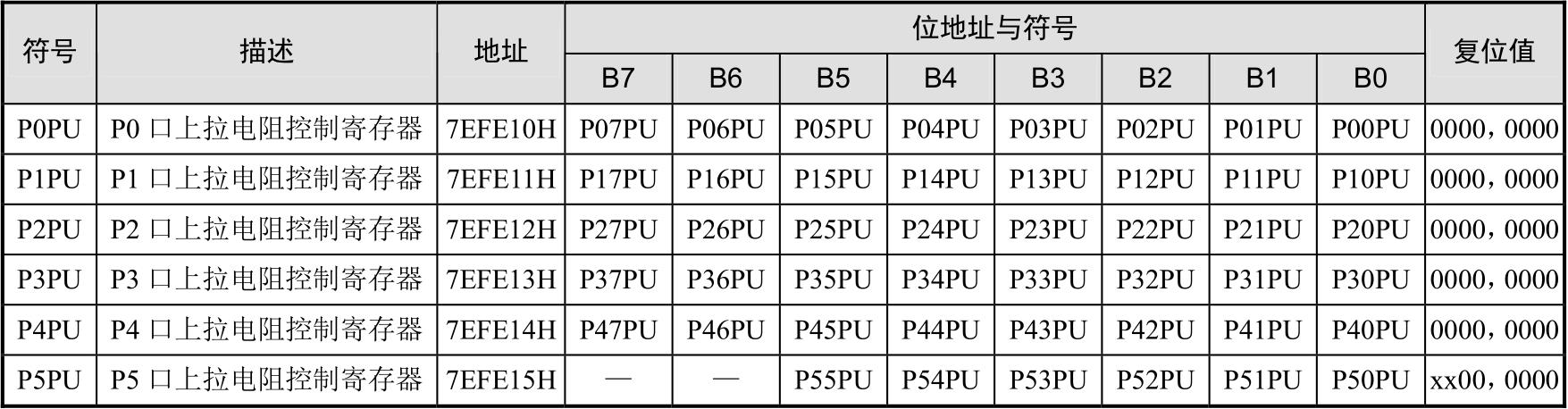

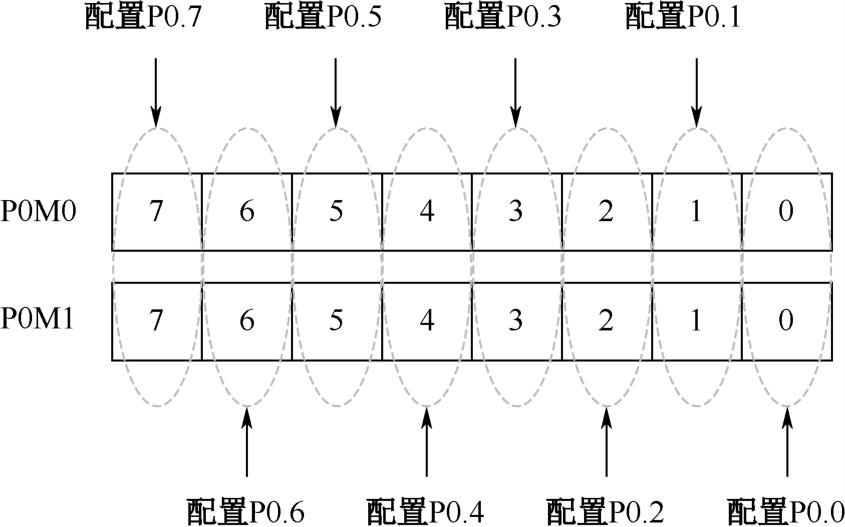

表3.24 与并行I/O端口相关的XFR

续表

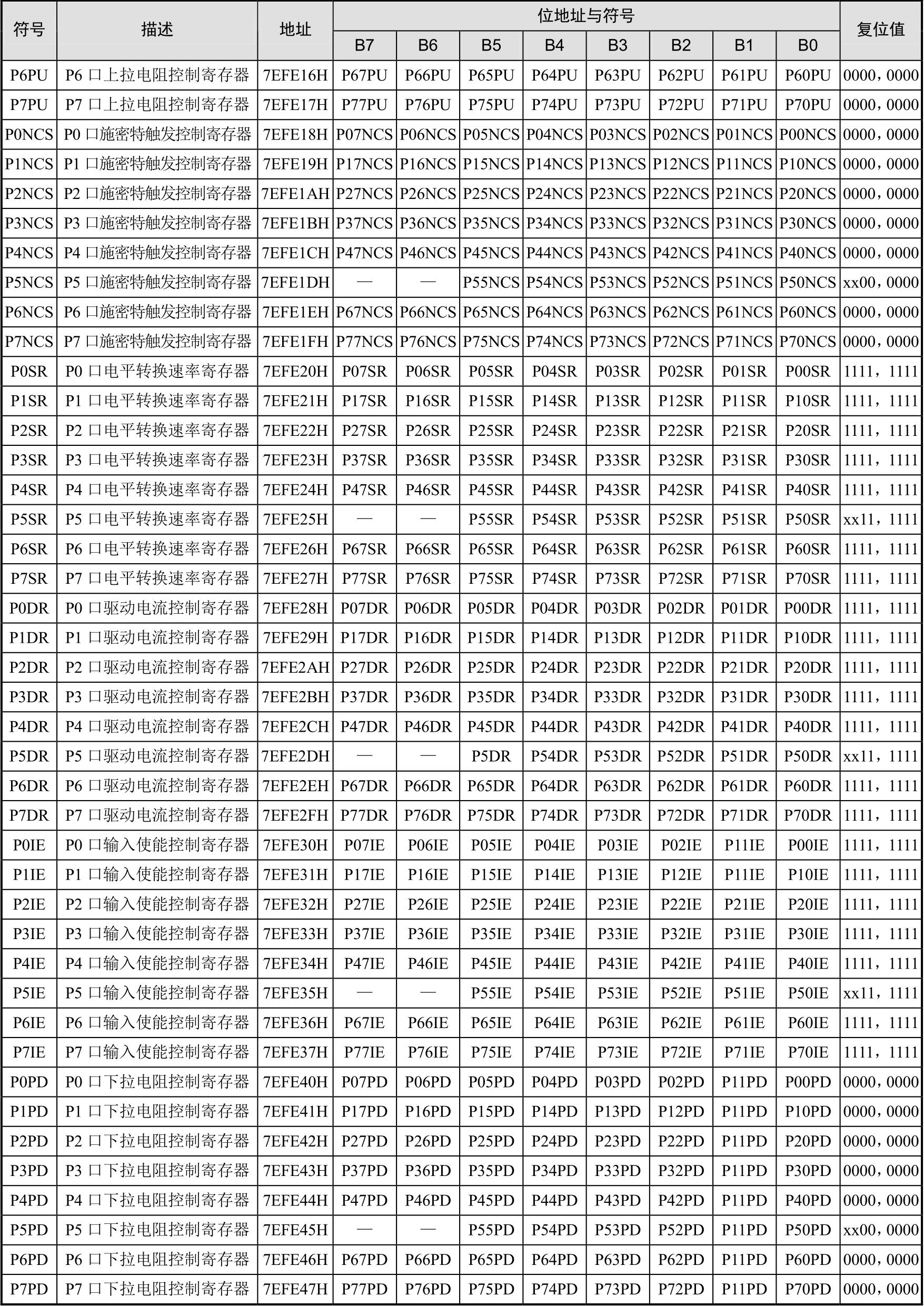

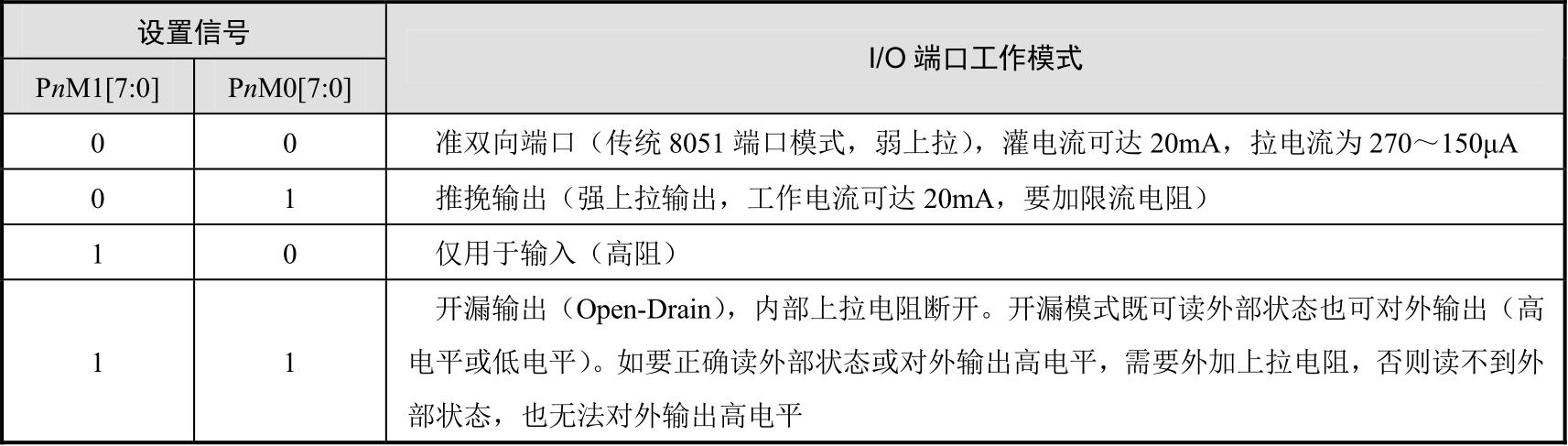

每个I/O端口的工作模式都需要使用两个寄存器进行设置,P n 端口就由P n M1和P n M0来进行设置,其中 n =0~7。以P0口为例,设置P0口需要通过P0M1和P0M0两个寄存器进行,设置关系如图3.10所示,P0M1.7和P0M0.7用于设置P0.7的工作模式。STC32G12K128单片机I/O端口工作模式的设置如表3.25所示。

图3.10 P0口工作模式的设置

表3.25 I/O端口工作模式的设置

注意:

(1)虽然每个I/O端口在弱上拉(准双向端口)/推挽输出/开漏输出模式时都能承受20mA的灌电流(还是要加限流电阻,如1kΩ、560Ω、472Ω等),在推挽输出时能输出20mA的拉电流(也要加限流电阻),但是整个单片机的工作电流不推荐超过90mA,即从电源流入的电流不要超过90mA,从GND流出的电流建议不要超过90mA,即整体流入/流出电流建议都不要超过90mA。

(2)当有I/O端口被选择为A/D转换器输入通道时,必须设置P

n

M0/P

n

M1寄存器将I/O端口模式设置为输入模式。另外,如果单片机进入掉电模式/时钟停振模式后仍需要使能A/D转换器通道,则需要设置P

n

IE寄存器关闭数字输入,这样才能保证不会有额外的耗电。

1.准双向端口(弱上拉)输出

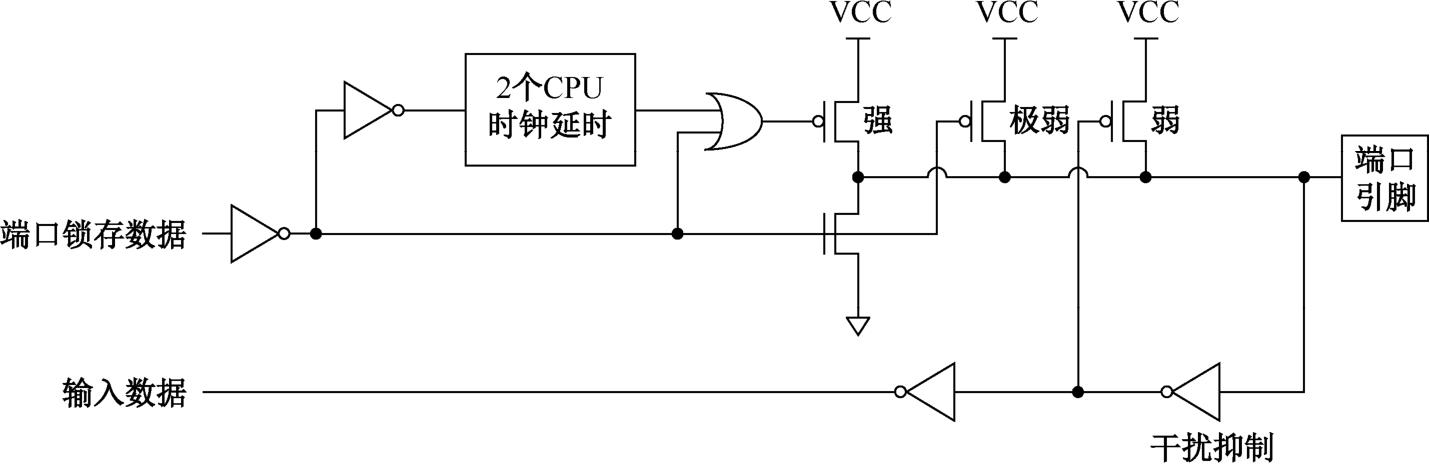

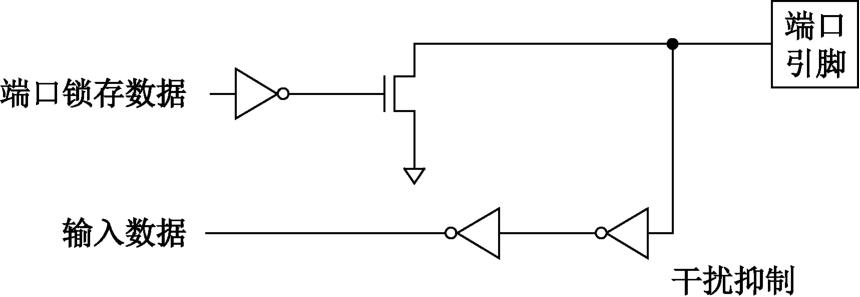

准双向端口(弱上拉)输出的结构如图3.11所示。

准双向端口(弱上拉)输出可用作输出和输入功能而不需要重新配置端口的输出状态。这是因为当端口输出高电平时,驱动能力很弱,允许外部将其拉低;当输出低电平时,它的驱动能力很强,可吸收相当大的电流。准双向端口有3个上拉晶体管,适应不同的需要。

第1个上拉晶体管称为“弱上拉”晶体管,当端口寄存器中的数值为1且引脚本身也为高电平时导通。此上拉晶体管提供基本驱动电流,使准双向端口输出为1。如果引脚本身为高电平而由外部装置下拉到低电平时,此上拉晶体管截止而“极弱上拉”晶体管维持导通状态,为了将这个引脚的电平强拉为低,外部装置必须有足够的灌电流能力使引脚上的电平降到门槛电压以下。对于工作电压为5V的单片机,“弱上拉”晶体管的电流约为250μA;对于工作电压为3.3V的单片机,“弱上拉”晶体管的电流约为150μA。

图3.11 准双向端口(弱上拉)输出的结构

第2个上拉晶体管称为“极弱上拉”晶体管,当端口数据锁存为1时导通。当引脚悬空时,“极弱上拉”晶体管产生很弱的上拉电流将引脚上拉为高电平。对于工作电压为5V的单片机,“极弱上拉”晶体管的电流约为18μA;对于工作电压为3.3V的单片机,“极弱上拉”晶体管的电流约为5μA。

第3个上拉晶体管称为“强上拉”晶体管,当端口锁存数据由0到1跳变时,“强上拉”晶体管用来加快准双向端口由低电平到高电平的转换。当发生这种情况时,“强上拉”晶体管导通约2个时钟周期,以迅速上拉高电平。

准双向端口(弱上拉)带有一个施密特触发输入电路及一个干扰抑制电路。准双向端口(弱上拉)读外部状态前,要先置锁存器中的数据为1,这样才可读到外部正确的状态。

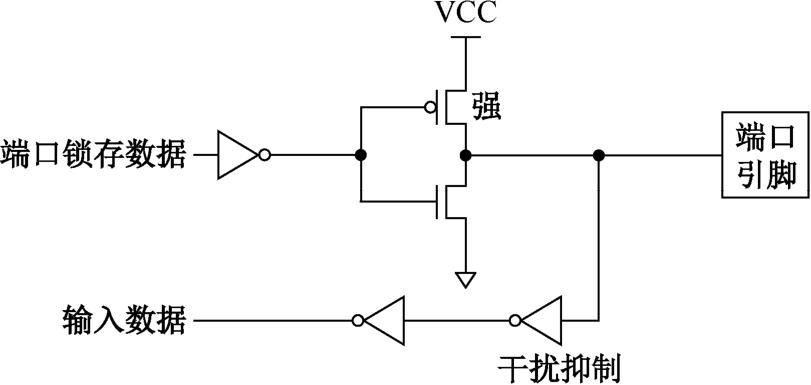

2.推挽输出

推挽输出模式配置的下拉结构与开漏输出及准双向端口的下拉结构相同,但当锁存器中的数据为1时提供持续的强上拉电流。推挽输出模式一般用于需要更大驱动电流的情况。推挽输出模式的结构如图3.12所示。

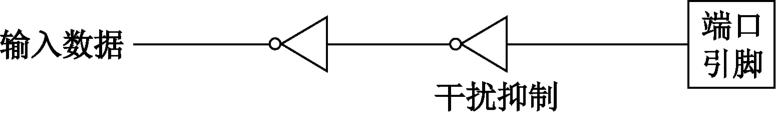

3.高阻输入

在高阻输入模式下,电流既不能流入也不能流出。高阻输入模式带有一个施密特触发输入电路及一个干扰抑制电路。高阻输入模式的结构如图3.13所示。

图3.12 推挽输出模式的结构

图3.13 高阻输入模式的结构

4.开漏输出

开漏输出模式既可读外部状态也可对外输出(高电平或低电平)。如要正确读外部状态或需要对外输出高电平,需要外加上拉电阻。当端口锁存器中的数据为0时,开漏输出模式将使所有上拉晶体管截止。当作为一个逻辑端口输出高电平时,采用此模式必须配有外部上拉电阻,一般通过外部上拉电阻接到电源。如果外部有上拉电阻,采用开漏输出模式的I/O端口还可读外部状态,即此时被配置为开漏模式的I/O端口还可作为输入I/O端口。这种方式的电平下拉原理与准双向端口(弱上拉)模式相同。

开漏输出模式带有一个施密特触发输入电路及一个干扰抑制电路,其结构如图3.14所示。

图3.14 开漏输出模式的结构

1.内部上拉电阻的设置

I/O端口内部可使能一个阻值大约为4.1kΩ的上拉电阻,由P n PU( n =0~7)寄存器来控制,如P1.7内部上拉电阻的使能就由P1PU.7来控制,“0”禁止,“1”使能。

2.施密特触发器的设置

I/O端口输入通道均可使能一个施密特触发器,由P n NCS( n =0~7)寄存器来控制,如P1.7内部施密特触发器的使能就由P1PNCS.7来控制,“0”使能,“1”禁止。

3.电平转换速度的设置

电平的转换速度由P n SR( n =0~7)寄存器来控制,如P1.7电平的转换速度就由P1SR.7来控制,当设置为“0”时,电平的转换速度快,但相应的上下冲击会比较大;当设置为“1”时,电平的转换速度慢,但相应的上下冲击会比较小。

4.电流驱动能力的设置

电流的驱动能力由P n DR( n =0~7)寄存器来控制,如P1.7的电流驱动能力就由P1DR.7来控制,当设置为“1”时,电流的驱动能力为一般驱动能力;当设置为“0”时,增强端口的电流驱动能力。

5.数字信号输入使能的设置

I/O端口的数字信号输入由P n IE( n =0~7)寄存器来控制,如P1.7的数字信号输入就由P1IE.7来控制,“0”禁止,“1”使能。

注意: 若I/O端口被当作比较器输入端口、A/D转换器输入端口或者触摸按键输入端口等模拟端口时,进入时钟停振模式前,必须将P n IE设置为0,否则会有额外的耗电。

6.下拉电阻设置寄存器(P n PD)

STC32G12K128单片机所有的I/O端口内部均可使能一个下拉电阻,由寄存器P n PD( n =0~7)来控制,如P1.7是否使能下拉电阻就由P1PD.7来控制,“0”禁止,“1”使能。

(1)P3.0和P3.0上电后的状态为准双向端口(弱上拉)模式。

(2)除P3.0和P3.1外,其余所有I/O端口上电后的状态均为高阻输入模式,用户在使用I/O端口前必须先设置I/O端口模式。

(3)单片机上电时如果不需要使用USB进行ISP下载,那么P3.0、P3.1、P3.2不能同时为低电平,否则单片机会进入USB下载模式而无法运行用户代码。

(4)单片机上电时,若P3.0和P3.1同时为低电平,P3.2会在很短的时间内由高阻输入模式切换到双向口模式,用以读取P3.2外部状态来判断是否需要进入USB下载模式。

(5)当使用P5.4作为复位引脚时,其内部的4kΩ上拉电阻会保持使能状态;但P5.4作为普通I/O端口引脚时,基于共享引脚的特殊考量,P5.4内部的4kΩ上拉电阻依然会保持使能状态大约6.5ms,再自动关闭(当用户的电路设计需要使用P5.4驱动外部电路时,请务必考虑上电瞬间会有6.5ms时间的高电平这一情况)。