下载掌阅APP,畅读海量书库

立即打开

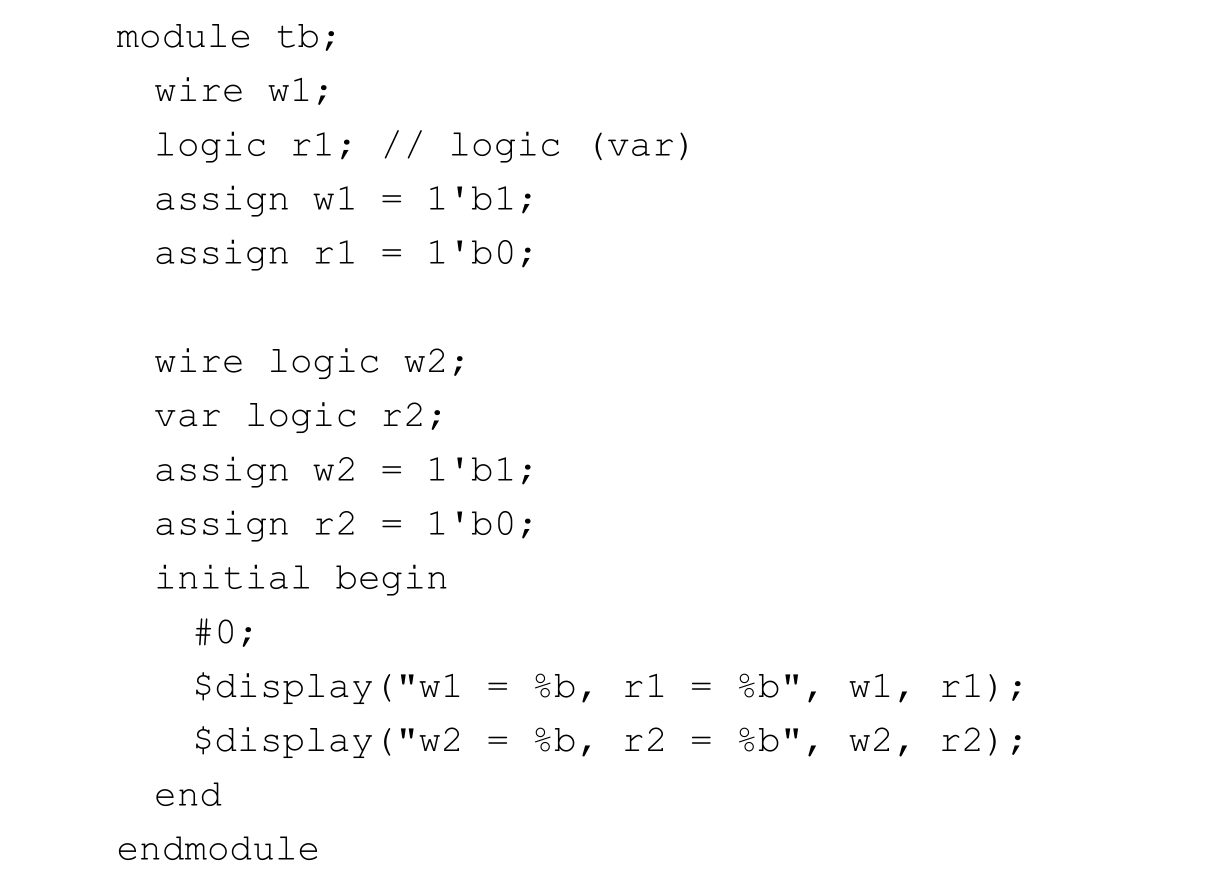

首先要明白,在SV中,类型可以分为线网(net)和变量(variable)。线网的赋值设定与Verilog的要求相同,即线网赋值需要使用连续赋值语句(assign),而不应出现在过程块(initial、always)中;相比于线网驱动的限制,变量(var)类型的驱动要求就没那么多了,如 logic[3:0]a ,该变量默认类型是var(变量),对它可以使用连续赋值或过程赋值。

关键词:

assign,logic,var,net,wire

避坑指南:

简而言之,可以在testbench(module)中的数值存储和线网连接,多数情况下使用logic类型变量,而很少有只能使用wire的情况。那么什么时候需要使用wire呢?例如,当出现多于一个驱动源的时候,或设计模块端口是双向(inout)的时候,都需要使用wire来完成线网连接。

参考代码: sv_assign_wire_var.sv

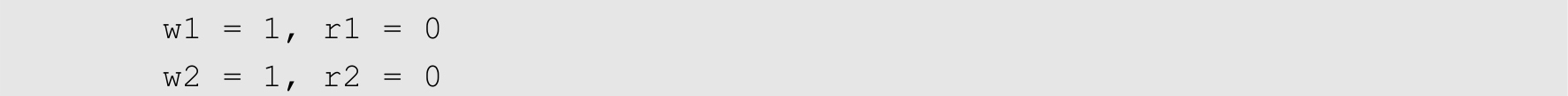

仿真结果:

阅读手记: