在IEEE-754规范(32位和64位)和IEEE-854(可变宽度)规范中,都对浮点数进行了定义。很多年前,在处理器和IP中就开始使用浮点数了,且浮点格式是一种很容易理解的格式,它是一个符号幅度系统,其中对符号的处理不同于对幅度的处理。

注 :(1 )对于Quartus Prime Pro集成开发环境的Analysis&Synthesis而言,需要将定点运算库的声明语句设置为

library ieee;

use ieee.float_pkg.all;

(2)对于ModelSim-INTEL FPGA STARTR EDITION 2019.2仿真工具而言,需要在设计文件和测试文件中同时将定点运算库的声明语句设置为

Library floatfixlib;

use floatfixlib.float_pkg.all;

且在ModelSim仿真工具命令行中,输入命令

vlib floatfixlib

对于VHDL而言,不同精度的浮点数的范围表示如下所示。

(1)对于32位的浮点数而言,范围为(8 downto-23),声明数据类型为float32;

其中:

① 8表示符号位;

② 7 downto 0表示指数部分,即8位宽度;

③ (-1 downto-23)表示小数部分,即23位宽度。

(2)对于64位的浮点数而言,范围为(11 downto-52),声明数据类型为float64;

其中:

① 11表示符号位;

② 10 downto 0表示指数部分,即11位宽度;

③-1 downto-52表示小数部分,即52位宽度。

(3)对于128位的浮点数而言,范围为(15 downto-112),声明数据类型为float128;

其中:

① 15表示符号位;

② 14 downto 0表示指数部分,即15位宽度;

③-1 downto-112表示小数部分,即112位宽度。

(4)对于可变长度的浮点数而言,范围为( m downto n )。

其中:

① m 为正整数, n 为负整数;

② m 表示符号位;

③ m -1 downto 0表示指数部分,即 m 位宽度;

④-1 downto n 表示小数部分,即 n 位宽度。

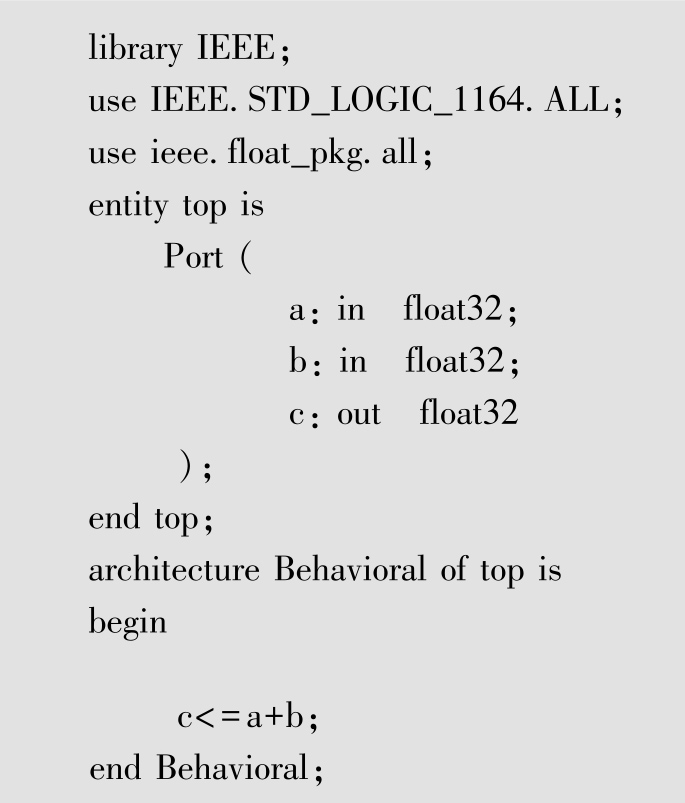

本小节给出了单精度浮点数加法运算的VHDL描述,如代码清单3-25所示。

代码清单3-25 top.vhd

注 :(1 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_33路径下,用Quartus P rime P ro 2019.4集成开发环境打开该设计。特别要注意所引用的库!

(2)在Quartus Prime Pro 2019.4集成开发环境的“Settings”对话框中,将“VHDL version”设置为“VHDL 2008”。

(3 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_34路径下,使用ModelSim-INTEL FPGA STARTER EDITION 2019.2仿真工具打开该设计。特别要注意所引用的库!

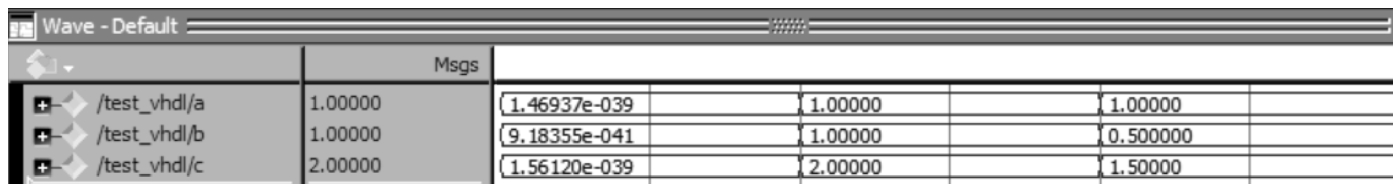

使用ModelSim-INTEL FPGA STARTER EDITITON 2019.2仿真工具对单精度浮点数的加法运算进行仿真,其结果如图3.40 所示。

图3.40 单精度浮点数加法运算的仿真结果(反色显示)

思考与练习3-30 :请分析单精度浮点数加法运算的仿真结果,验证设计的正确性。

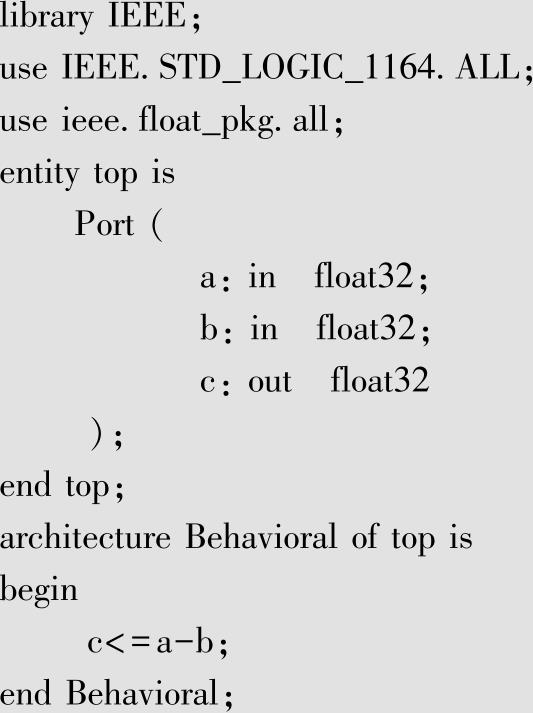

本小节给出了单精度浮点数减法运算的VHDL描述,如代码清单3-26所示。

代码清单3-26 top.vhd

注 :(1 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_35路径下,用Quartus P rime P ro 2019.4集成开发环境打开该设计。特别要注意所引用的库!

(2 )在Quartus Prime Pro 2019.4集成开发环境的 “Settings”对话框中,将 “VHDL version”设置为 “VHDL 2008”。

(3 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_36路径下,使用ModelSim-INTEL FPGA STARTER EDITION 2019.2仿真工具打开该设计。特别要注意所引用的库!

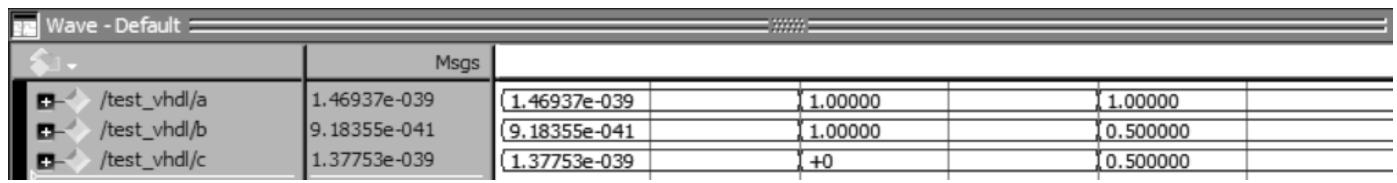

使用ModelSim-INTEL FPGA STARTER EDITITON 2019.2仿真工具对单精度浮点数的减法运算进行仿真,其结果如图3.41所示。

图3.41 单精度浮点数减法运算的仿真结果(反色显示)

思考与练习3-31 :请分析单精度浮点数减法运算的仿真结果,验证设计的正确性。

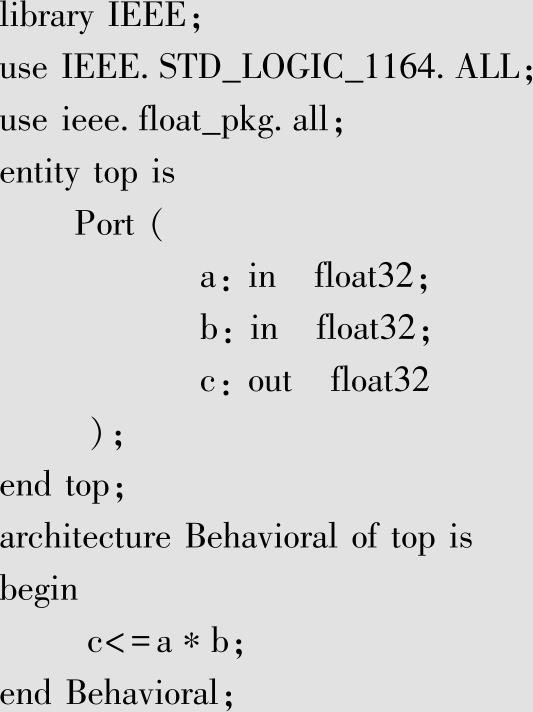

本小节给出了单精度浮点数乘法运算的VHDL描述,如代码清单3-27所示。

代码清单3-27 top.vhd

注 :(1 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_37路径下,用Quartus P rime P ro 2019.4集成开发环境打开该设计。特别要注意所引用的库!

(2)在Quartus Prime Pro 2019.4集成开发环境的“Settings”对话框中,将“VHDL version”设置为“VHDL 2008”。

(3 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_38路径下,使用ModelSim-INTEL FPGA STARTER EDITION 2019.2仿真工具打开该设计。特别要注意所引用的库!

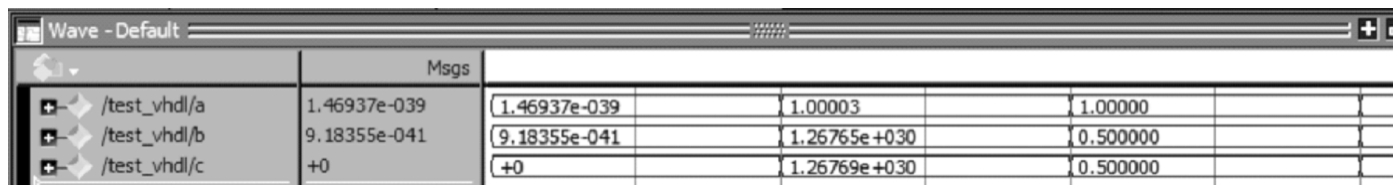

使用ModelSim-INTEL FPGA STARTER EDITITON 2019.2仿真工具对单精度浮点数的乘法运算进行仿真,其结果如图3.42所示。

思考与练习3-32 :请分析单精度浮点数乘法运算的仿真结果,验证设计的正确性。

图3.42 单精度浮点数乘法运算的仿真结果

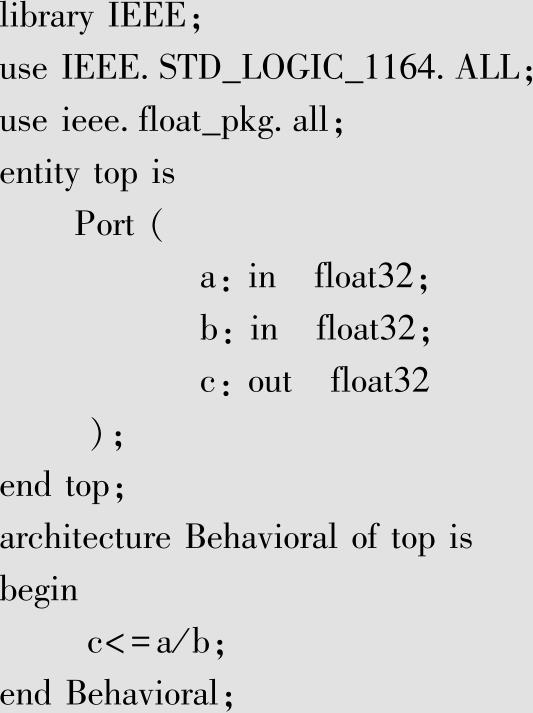

本小节给出了单精度浮点数除法运算的VHDL描述,如代码清单3-28所示。

代码清单3-28 top.vhd

注 :(1 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_39路径下,用Quartus P rime P ro 2019.4集成开发环境打开该设计。特别要注意所引用的库!

(2 )在Quartus Prime Pro 2019.4集成开发环境的 “Settings”对话框中,将 “VHDL version”设置为 “VHDL 2008”。

(3 )读者可以定位到本书所提供资料的\intel_dsp_example\example_3_40路径下,使用ModelSim-INTEL FPGA STARTER EDITION 2019.2仿真工具打开该设计。特别要注意所引用的库!

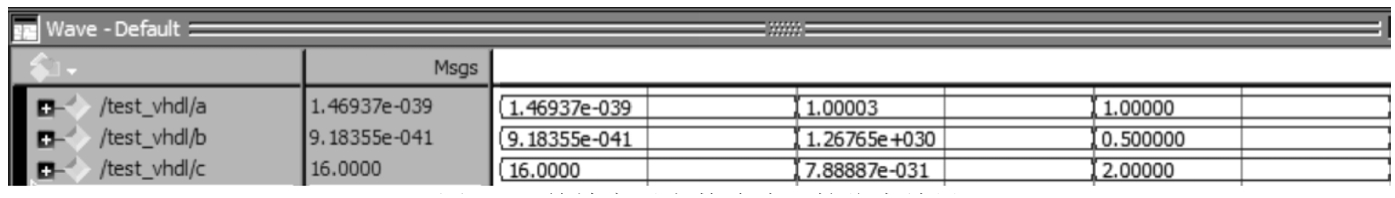

使用ModelSim-INTEL FPGA STARTER EDITITON 2019.2仿真工具对单精度浮点数的除法运算进行仿真,其结果如图3.43所示。

图3.43 单精度浮点数除法运算的仿真结果

思考与练习3-33 :请分析单精度浮点数除法运算的仿真结果,验证设计的正确性。