AArch64执行状态支持31个64位的通用寄存器,分别是X0~X30寄存器,而AArch32状态支持16个32位的通用寄存器。

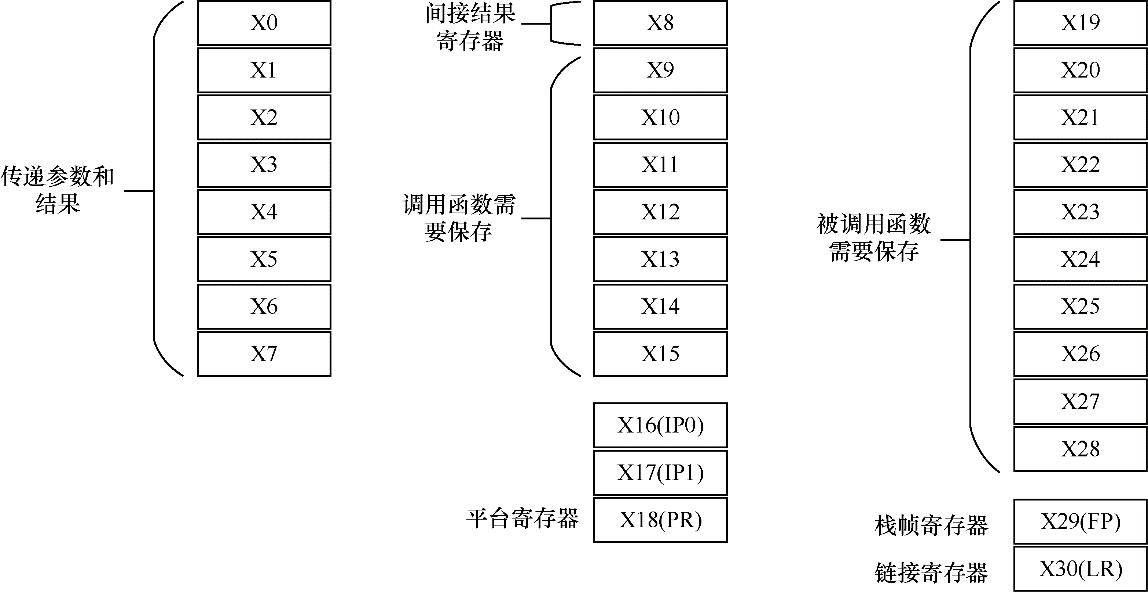

除用于数据运算和存储之外,通用寄存器还可以在函数调用过程中起到特殊作用,ARM64体系结构的函数调用标准和规范对此有所约定,如图1.2所示。

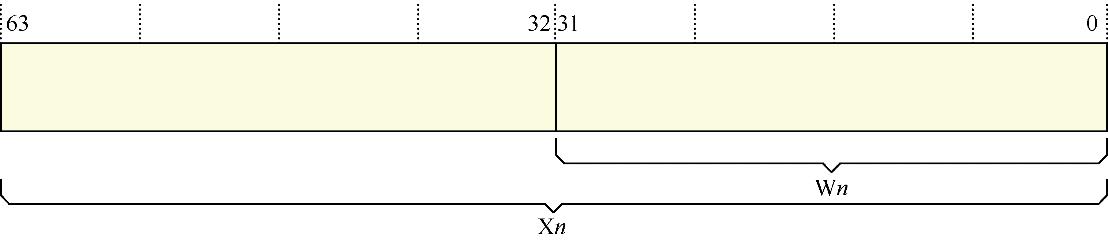

在AArch64状态下,使用X(如X0、X30等)表示64位通用寄存器。另外,还可以使用W来表示低32位的数据,如W0表示X0寄存器的低32位数据,W1表示X1寄存器的低32位数据,如图1.3所示。

▲图1.2 AArch64状态的31个通用寄存器

▲图1.3 64位通用寄存器和低32位数据

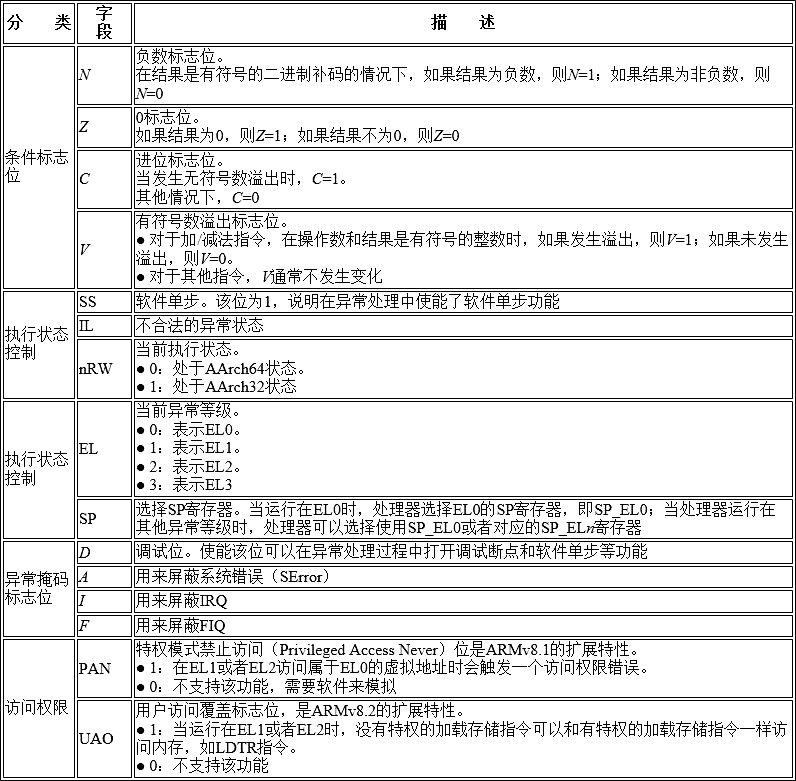

AArch64体系结构使用PSTATE寄存器来表示当前处理器状态(processor state),如表1.3所示。

表1.3 PSTATE寄存器

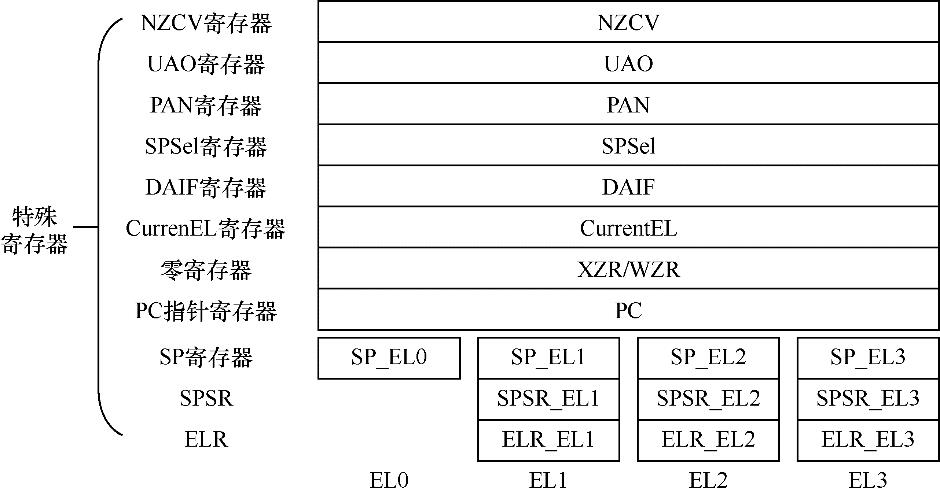

ARMv8体系结构除支持31个通用寄存器之外,还提供多个特殊的寄存器,如图1.4所示。

▲图1.4 特殊寄存器

ARMv8体系结构提供两个零寄存器(zero register),这些寄存器的内容全是0,可以用作源寄存器,也可以用作目标寄存器。WZR是32位的零寄存器,XZR是64位的零寄存器。

PC指针寄存器通常用来指向当前运行指令的下一条指令的地址,用于控制程序中指令的运行顺序,但是编程人员不能通过指令来直接访问它。

ARMv8体系结构支持4个异常等级,每一个异常等级都有一个专门的SP寄存器SP_EL n ,如处理器运行在EL1时选择SP_EL1寄存器作为SP寄存器。

●SP_EL0:EL0下的SP寄存器。

●SP_EL1:EL1下的SP寄存器。

●SP_EL2:EL2下的SP寄存器。

●SP_EL3:EL3下的SP寄存器。

当处理器运行在比EL0高的异常等级时,处理器可以访问如下寄存器。

●当前异常等级对应的SP寄存器SP_EL n 。

●EL0对应的SP寄存器SP_EL0可以当作一个临时寄存器,如Linux内核使用该寄存器存放进程中task_struct数据结构的指针。

当处理器运行在EL0时,它只能访问SP_EL0,而不能访问其他高级的SP寄存器。

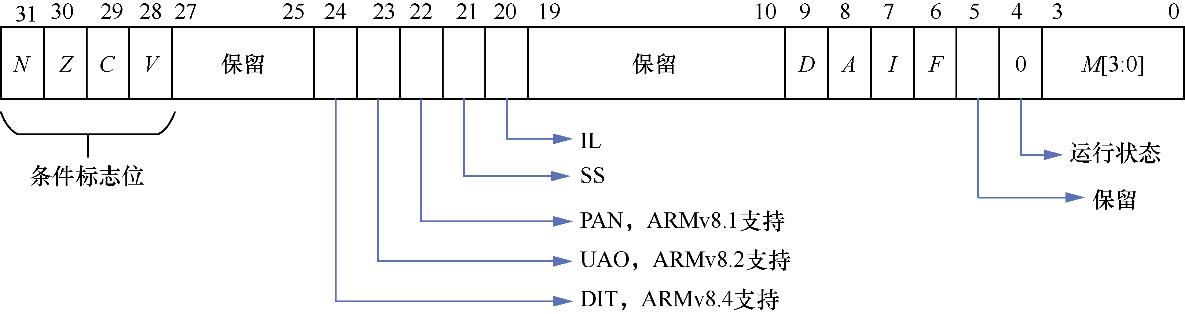

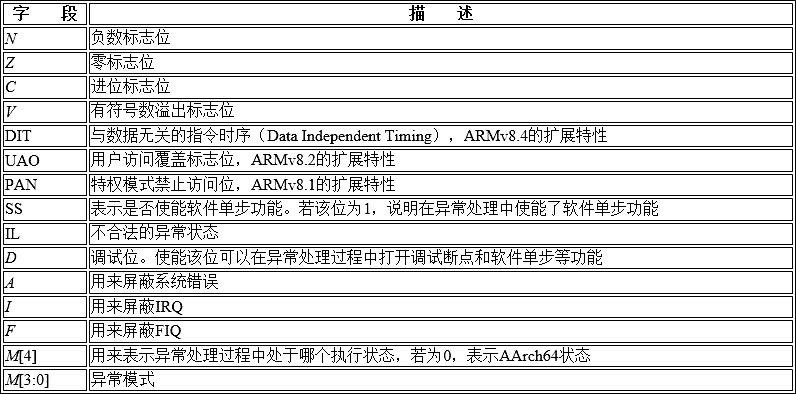

当我们运行一个异常处理程序时,处理器的备份程序会保存到备份程序状态寄存器(Saved Program Status Register,SPSR)里。当异常将要发生时,处理器会把PSTATE寄存器的值暂时保存到SPSR里;当异常处理完成并返回时,再把SPSR的值恢复到PSTATE寄存器。SPSR的格式如图1.5所示。SPSR的重要字段如表1.4所示。

▲图1.5 SPSR的格式

表1.4 SPSR的重要字段

ELR存放了异常返回地址。

该寄存器表示PSTATE寄存器中的EL字段,其中保存了当前异常等级。使用MRS指令可以读取当前异常等级。

●0:表示EL0。

●1:表示EL1。

●2:表示EL2。

●3:表示EL3。

该寄存器表示PSTATE寄存器中的{ D , A , I , F }字段。

该寄存器表示PSTATE寄存器中的SP字段,用于在SP_EL0和SP_EL n 中选择SP寄存器。

PAN寄存器表示PSTATE寄存器中的PAN(Privileged Access Never,特权禁止访问)字段。可以通过MSR和MRS指令来设置PAN寄存器。当内核态拥有访问用户态内存或者执行用户态程序的能力时,攻击者就可以利用漏洞轻松地执行用户的恶意程序。为了修复这个漏洞,在ARMv8.1中新增了PAN特性,防止内核态恶意访问用户态内存。如果内核态需要访问用户态内存,那么需要主动调用内核提供的接口,例如copy_from_user()或者copy_from_user()函数。

PAN寄存器的值如下。

●0:表示在内核态可以访问用户态内存。

●1:表示在内核态访问用户态内存会触发一个访问权限异常。

该寄存器表示PSTATE寄存器中的UAO(User Access Override,用户访问覆盖)字段。我们可以通过MSR和MRS指令设置UAO寄存器。UAO为1表示在EL1和EL2执行这非特权指令(例如LDTR、STTR)的效果与特权指令(例如LDR、STR)是一样的。

该寄存器表示PSTATE寄存器中的{ N , Z , C , V }字段。

除上面介绍的通用寄存器和特殊寄存器之外,ARMv8体系结构还定义了很多的系统寄存器,通过访问和设置这些系统寄存器来完成对处理器不同的功能配置。在ARMv7体系结构中,我们需要通过访问CP15协处理器来间接访问这些系统寄存器,而在ARMv8体系结构中没有协处理器,可直接访问系统寄存器。ARMv8体系结构支持如下7类系统寄存器:

●通用系统控制寄存器;

●调试寄存器;

●性能监控寄存器;

●活动监控寄存器;

●统计扩展寄存器;

●RAS寄存器;

●通用定时器寄存器。

系统寄存器支持不同的异常等级的访问,通常系统寄存器会使用“Reg_EL n ”的方式来表示。

●Reg_EL1:处理器处于EL1、EL2以及EL3时可以访问该寄存器。

●Reg_EL2:处理器处于EL2和EL3时可以访问该寄存器。

●大部分系统寄存器不支持处理器处于EL0时访问,但也有一些例外,如CTR_EL0。

程序可以通过MSR和MRS指令访问系统寄存器。

mrs X0, TTBR0_EL1 //把TTBR0_EL1的值复制到X0寄存器 msr TTBR0_EL1, X0 //把X0寄存器的值复制到TTBR0_EL1