理想的时钟、频率或者周期是一个常数;而在实际的应用场景中,频率和周期是时间的函数 f ( t ),晶体需要匹配电路才能够输出,晶体和外围电路的参数都是包含误差的。温度和时间等变化对电气参数也会存在影响。晶体或晶振应用中,还需关注标称频率、频率容差、负载电容值、寄生电容值、时漂、温漂、工作温度等参数和细节。

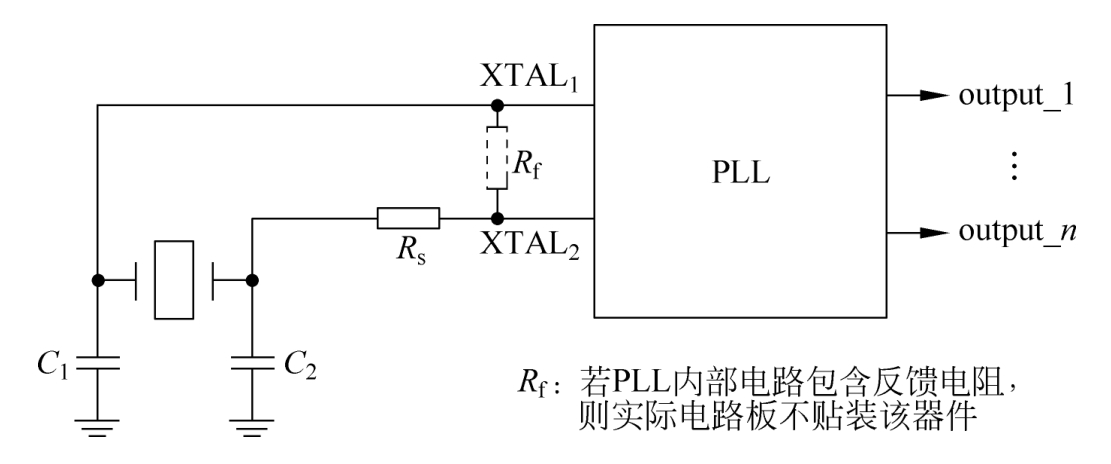

本案例中,单板电路设计应用一款包含多路输出、多频点时钟的锁相环(Phase Locked Loop,下文简称PLL)。该时钟芯片PLL输出8路不同频点的时钟,图2.1是该PLL电路框图。

图2.1 PLL电路框图

该PLL采用外部晶体作为本地时钟(本振),输出多路、不同频率的时钟。电容 C 1 、 C 2 作为匹配晶体的起振电容,图2.1中的XTAL 1 与XTAL 2 引脚间保留反馈电阻的位置 R f (一般为MΩ级,该PLL内部已包含反馈,因此图2.1中 R f 不贴装),端接 R s 电阻防止时钟对晶体产生电流过驱动。这是一个非常经典的时钟晶体电路连接原理图。

测试过程中发现,多片单板的输出时钟(output_1~output_ n )频率普遍偏慢,并超出设计的额定参数范围。

本案例中PLL输出频率异常,时钟电路模块仅包含晶体电路和PLL电路两部分,因此可以从这两个角度切入。一方面思考PLL固件参数配置是否存在失误,另一方面思考本振晶体相关的参数是否存在异常,下面对这两方面进行验证。

目前计算机或通信单板中部分PLL芯片的参数配置是驳杂的,包含分频、倍频、环路滤波器带宽、增益系数等锁相环相关参数;还包含参考时钟源及参数的选择、驱动电平、输出路由等配置。

PLL厂商通常提供图形用户界面(Graphical User Interface,GUI)配置工具,能够方便地生成配置参数固件。值得注意的是,图形化界面是常规的PLL功能参数,而完整固件的部分参数可能未在图形化配置流程中体现,用户关注的部分参数仍需要深入研读寄存器手册,并与PLL厂商做技术沟通。故本案例需要对PLL的配置固件参数予以核准。

晶体输出频率包含精度范围,例如本案例中,晶体频率容差为±20ppm,另外晶体振荡频率参数也和时间、温度等相关联。

时钟源精度会对PLL的输出时钟精度造成影响,故本案例亦需对本振的频率精度进行测量。

本案例中,首先检查PLL的常规配置参数,未见异常。

通常情况下,若常规的PLL分频、倍频、输入源、输出电平、路由等参数出现错误,则影响较大,而非微小的频率偏差。其次,测量本批次单板时钟晶体的频率,标称频率输出正常,其频率偏差符合额定范围±20ppm,并未出现一致偏慢(频偏为负)的情况。

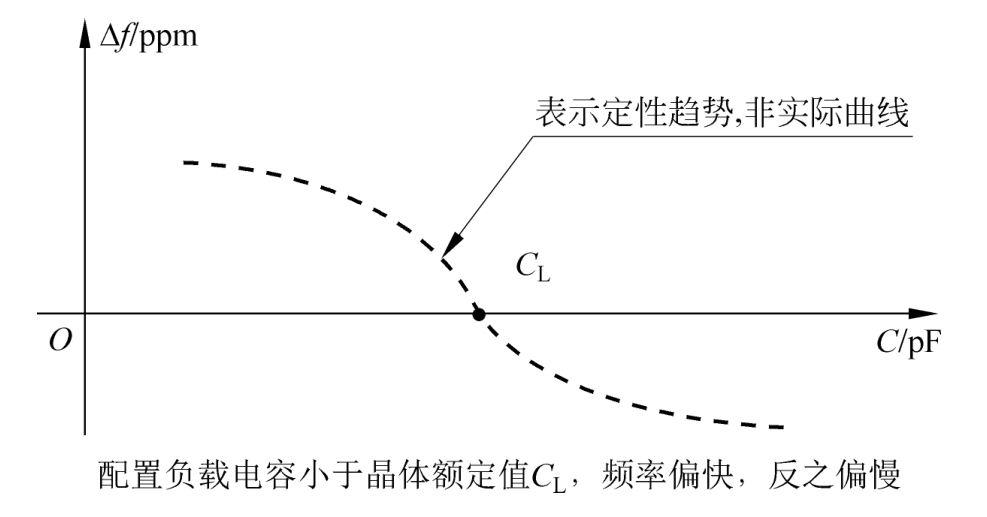

多片单板的时钟频率普遍偏慢的现象是故障排查的重要切入点。思考该时钟电路模块中哪些参数可能引发频率偏慢,在前文的论述中,已经排查了PLL参数配置和晶体标称频率参数。在剩余参数中还存在一个影响晶体频率偏差的参数——晶体的负载电容 C L ,这是晶体的固有参数,晶体的振荡频率偏差与晶体电路的负载电容值存在关系(这个关系是非线性的)。晶体实际带载的负载电容等于其额定值时,发生频率偏差最小。实际带载电容较小时,频率偏快;带载电容较大时,频率会偏慢,其定性趋势如图2.2所示。

图2.2 晶体负载电容与频率偏差的关系

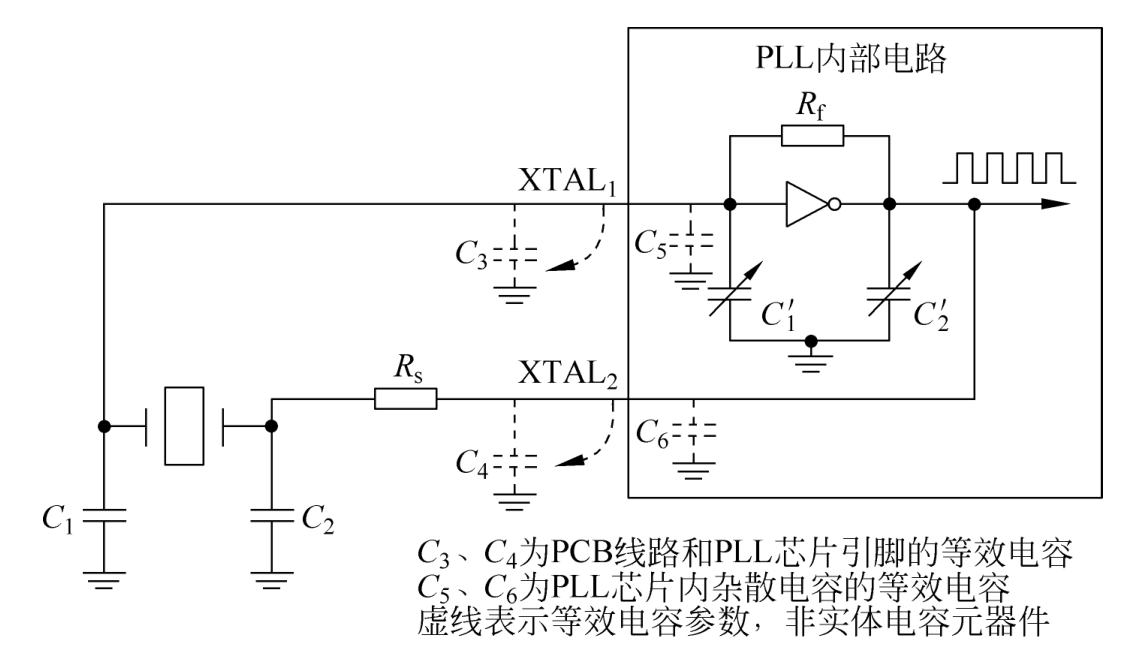

在案例中,晶体的负载电容是如何发生偏差的呢?经分析,发现是晶体电路匹配电容出现错误。图2.3所示为晶体外部电路与PLL内部电路组合,为PLL提供本振时钟的电路框图。

图2.3 晶体与PLL原理框图

其中 C 1 、 C 2 为晶体起振的匹配电容。

C 3 、 C 4 视作PCB线路和PLL芯片引脚的等效电容,例如1in的PCB线路等效成2.5~3.5pF容值的电容。芯片引脚也存在容性效应,根据芯片封装的差异,引脚存在几皮法的容性效应。

C 5 、 C 6 视作PLL芯片内部的杂散电容,该电气参数需要查看芯片手册,一般存在几皮法的容值。

和

和

是本案例中锁相环的可选或可调配置。芯片内部电路包含两个可调电容,可替代外部匹配电容

C

1

、

C

2

。

是本案例中锁相环的可选或可调配置。芯片内部电路包含两个可调电容,可替代外部匹配电容

C

1

、

C

2

。

本案例中,因

C

1

、

C

2

与

的重复配置,晶体的负载电容增加,最终导致PLL输出频率偏慢。

的重复配置,晶体的负载电容增加,最终导致PLL输出频率偏慢。

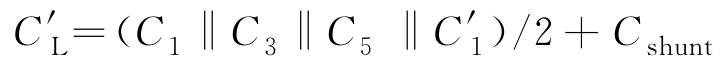

在本案例设计中,晶体的负载电容 C L 应满足:晶体两端电容分别并联后再串联,并添加晶体本身等效寄生电容 C shunt 的总和。一般的设计中,尽可能保持晶体两端电容的对称一致(例如两端匹配电容值一致,PCB走线对称一致),可以假设:

C 1 =C 2

C 3 =C 4

C 5 =C 6

因此,( C 1 ‖ C 3 ‖ C 5 )与( C 2 ‖ C 4 ‖ C 6 )串联的电容值为( C 1 ‖ C 3 ‖ C 5 )/2,满足

C L =( C 1 ‖ C 3 ‖ C 5 )/2 +C shunt

本案例中晶体 C L =18pF, C shunt =5pF,PCB布线和芯片引脚的等效电容 C 3 约为3pF,芯片内杂散电容 C 5 经查找芯片手册确认约为2.7pF,故计算得出晶体匹配电容 C 1 约为20pF,常规的配置18~22pF的起振电容是符合设计要求的。

由于电路设计人员与芯片厂商固件配置人员的沟通误会,芯片内部将

的可变电容配置为18pF,以代替晶体外部匹配电容,而硬件设计人员同时将外部电路电容

C

1

、

C

2

计入物料清单(Bill of Material,BOM),这样晶体的实际带载电容增至:

的可变电容配置为18pF,以代替晶体外部匹配电容,而硬件设计人员同时将外部电路电容

C

1

、

C

2

计入物料清单(Bill of Material,BOM),这样晶体的实际带载电容增至:

增加约9pF,锁相环输入时钟普遍变慢,最终导致锁相环输出频率普遍偏慢。

增加约9pF,锁相环输入时钟普遍变慢,最终导致锁相环输出频率普遍偏慢。

拆除外部匹配电容 C 1 、 C 2 后,故障消除。