CPU是数字电路最综合的应用技术之一。本实验课程的目的是用数字逻辑电路,设计一个最简单的CPU。要求设计的CPU应具各种必需的部分,又力求简单,使学生能通过本实验,在数字逻辑电路的基础上了解CPU的基本工作原理。

一位串行CPU,是指每个时钟周期,只能对一个比特(bit)的数据进行运算的CPU。

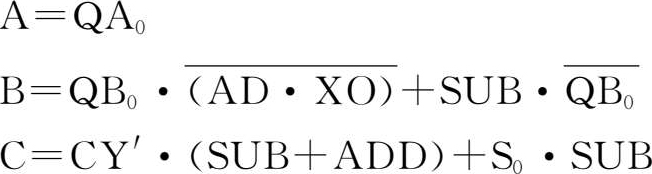

本实验设计采用一位全加器的 8 位串行计算CPU,能够完成 8 位二进制的加法(ADD)、减法(SUB)、异或(XOR)和移位(SHR)四条指令功能。该一位CPU由两个八位移位寄存器、指令译码器、时钟节拍寄存器和控制逻辑(在计算机中称为微操作电路)等部分组成,指令寄存器、数据存储器等采用置数开关实现。指令寄存器也采用两位开关实现。此外,数据读入和时钟脉冲也各采用一开关。本CPU组成框图如图1-1所示。

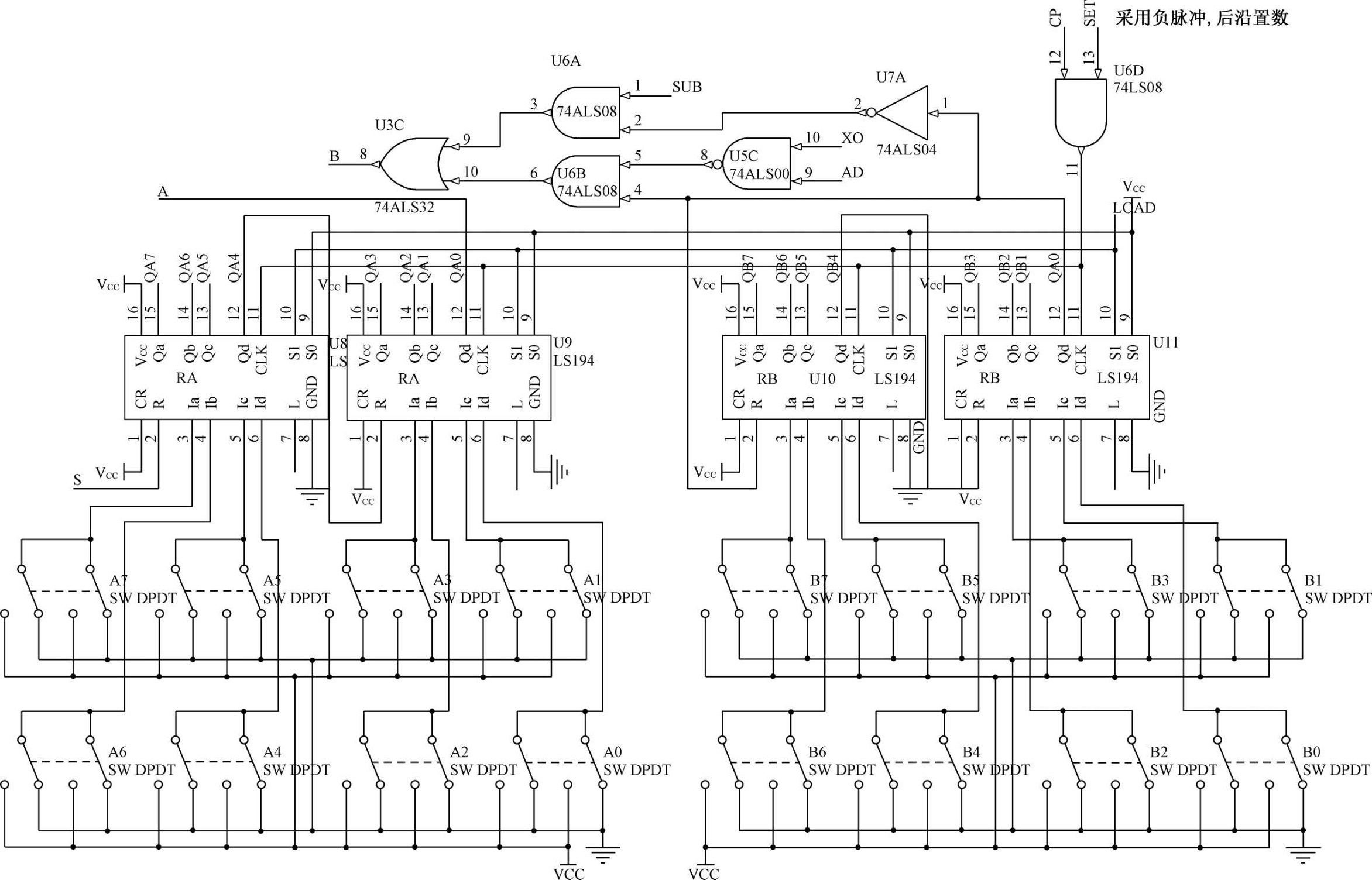

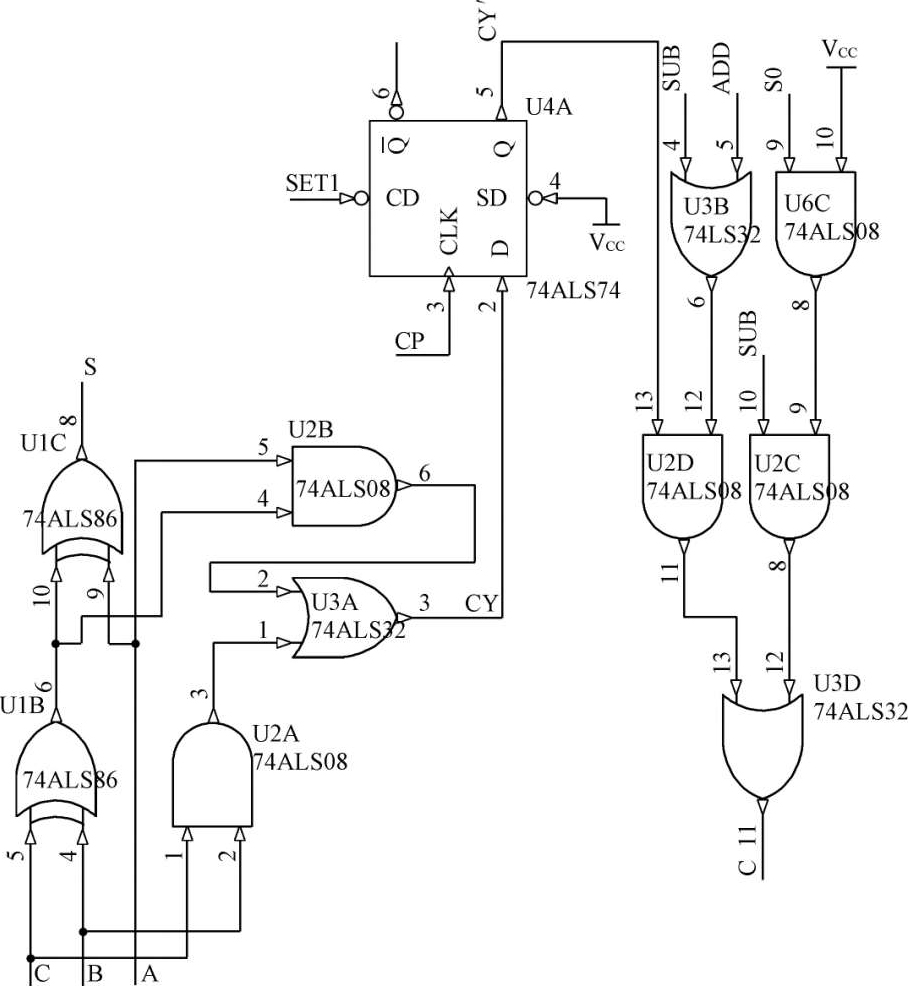

1.微操作电路和运算器

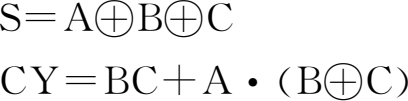

本CPU的运算器为一位二进制全加器,运算表达式为

S为运算结果,A、B、C分别为根据执行指令经微操作电路传来的运算数据。A为被加数,B为加数,C为上一个时钟周期执行指令的进位(借位)位,在本CPU中,全加器的三个输入端的运算表达式为别为

其中,ADD、SUB、XOR分别为译码电路输出的加、减、异或指令信号(AD、XO分别为ADD、XOR的非信号),QA 0 、QB 0 分别为A、B的最低位,CY为全加器向上进位的结果,CY′为经过C寄存器锁存的前一时钟周期的进位(CY)信号,S 0 为指令执行周期的第一个时钟周期,用于实现减法指令的取补功能。每一时钟周期得到的一位结果S,在该时钟周期末移入A的最高位(同时A寄存器中数据也右移一位),本位运算的进位CY存入C寄存器,作为下一时钟周期全加器的C输入端数据。微操作电路是CPU中实现指令功能的关键逻辑电路,它根据执行指令,确定每一时钟周期的逻辑条件,将要求的数据送全加器的输入端(A、B、C)。如果要设计更多的指令,实际上就是根据指令设计相应的微操作电路。

图1-1 CPU结构框图

2.寄存器和数据存储开关

本CPU中的两个8位移位寄存器,分别称为A寄存器、B寄存器,各由2片74LS194串联组成。其中A寄存器相当于CPU中的累加寄存器,在运算中作为源操作数(被加数、被减数等)和运算结果存储寄存器。B寄存器提供另一源操作数(加数、减数等)。C寄存器为进位位寄存器,仅为一位。

A寄存器与全加器逻辑电路,组成右循环移位寄存器,相当于CPU中的累加器。B寄存器组成右循环移位寄存器。数据存储器采用16个带自锁的开关实现,通过Load信号将数据存储开关状态(即数据)并行读入寄存器A和寄存器B,读数据的同时初始化指令执行时序计数器。

每一条指令执行过程由8个时钟周期组成,分别为S0~S7,指令执行过程中,每个时钟周期将A、B中数据右移一位,即最低位分别移入微操作电路。其中,A寄存器的最低位送全加器一输入端A,全加器一步运算结果(本位和)S移入最高位,进位CY送C寄存器;B寄存器的最低位在送全加器另一输入端的同时,移入B寄存器最高位。指令执行结束后,A中保存运算结果,B中数据不变。

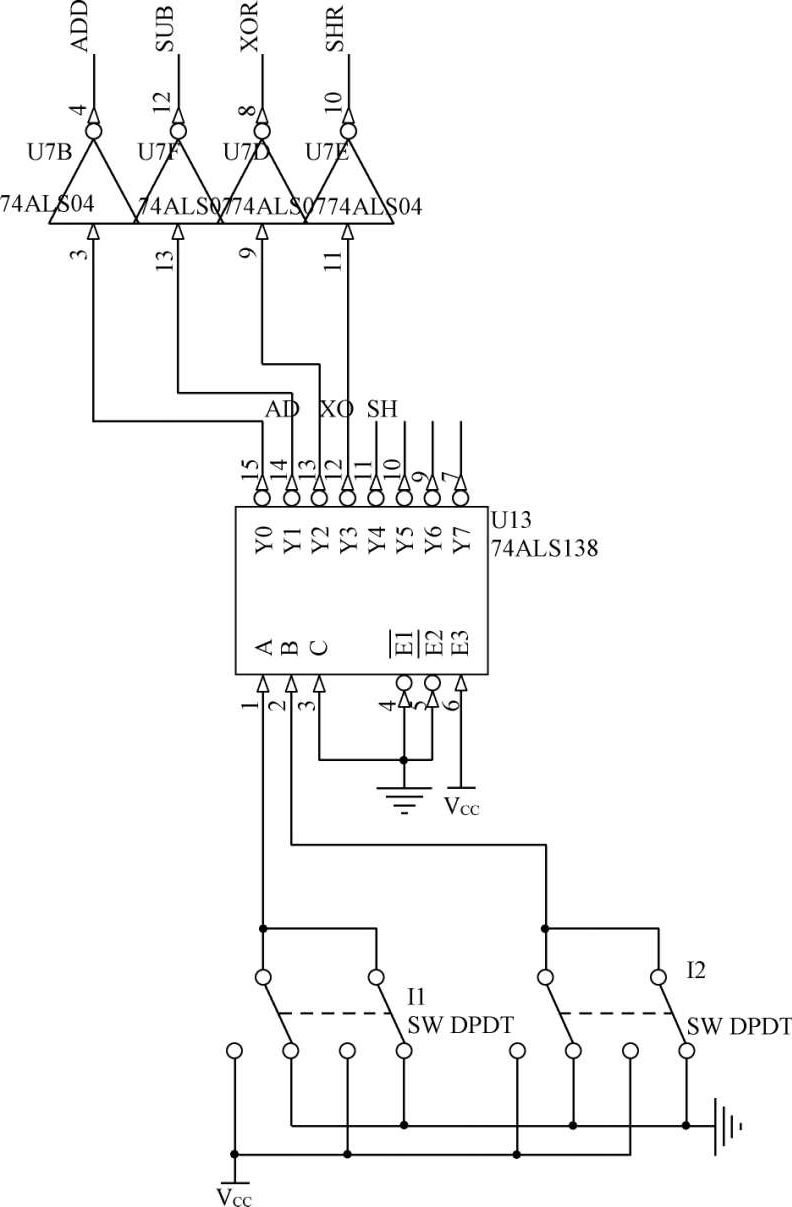

3.指令寄存器和指令译码器

为了尽量减少数字逻辑电路,本CPU的指令寄存器由两个带自锁开关组成,开关的四个状态00、01、10、11分别表示加(ADD)、减(SUB)、异或(XOR)和循环右移(SHR)四条指令。指令译码器采用一片74LS138译码芯片。此部分电路比较简单,不再赘述。

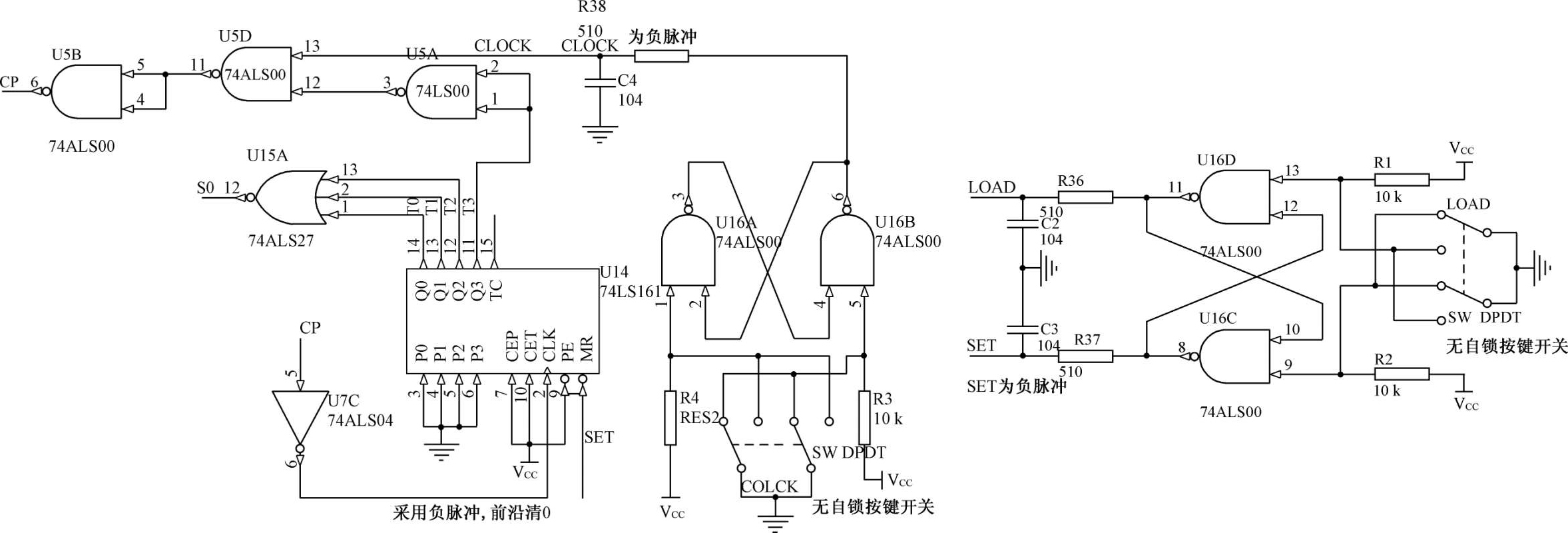

4.时钟周期电路

本串行CPU实现8位二进制数的运算。由于运算器为一位二进制全加器,所以,每条指令执行周期需要8个时钟周期,时钟周期电路采用74LS161。时钟(Clock)采用不带自锁的按键开关实现。每按一次开关,产生一个时钟脉冲,作为累加器、寄存器等的时钟信号,另一方面该脉冲接74LS161的clk引脚,作为时钟周期电路的计数信号。当每次指令执行完成时,封锁Clock信号。Load信号在载入运算数据的同时,清零74LS161计数值,初始化指令执行。

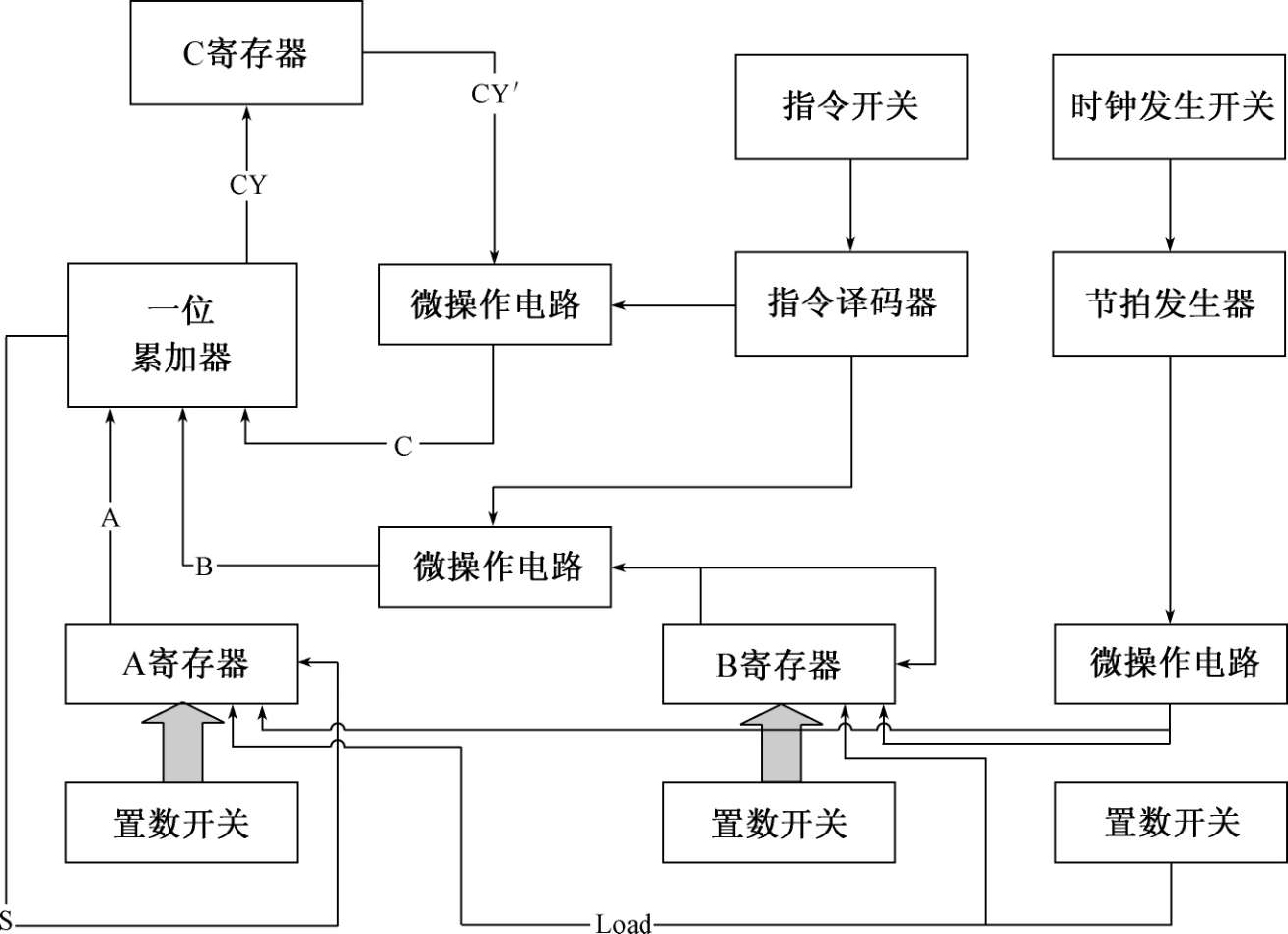

第一步 按照实验框图设计实验原理图,在Altium Designer 09中画出实验原理图。参考电路如图1-2~图1-6所示。

第二步 按所设计的原理图,选择合适的芯片和器件,以数字电路实验箱为实验平台,搭建实物电路。

第三步 分别输入“加法”、“减法”、“异或”、“右移”指令,并输入不同的操作数据,验证所设计的电路,观察结果寄存器和系统输出是否正确。

1.上述原理图中,微操做电路有哪些?分别起到什么作用。

2.根据上述原理图,增加其他指令,如“左移”、“赋值”等指令。

3.设计该电路的PCB版图。

图1-2 累加器电路

图1-3 全加器电路

图1-4 指令译码电路

图1-5 时钟节拍发生电路

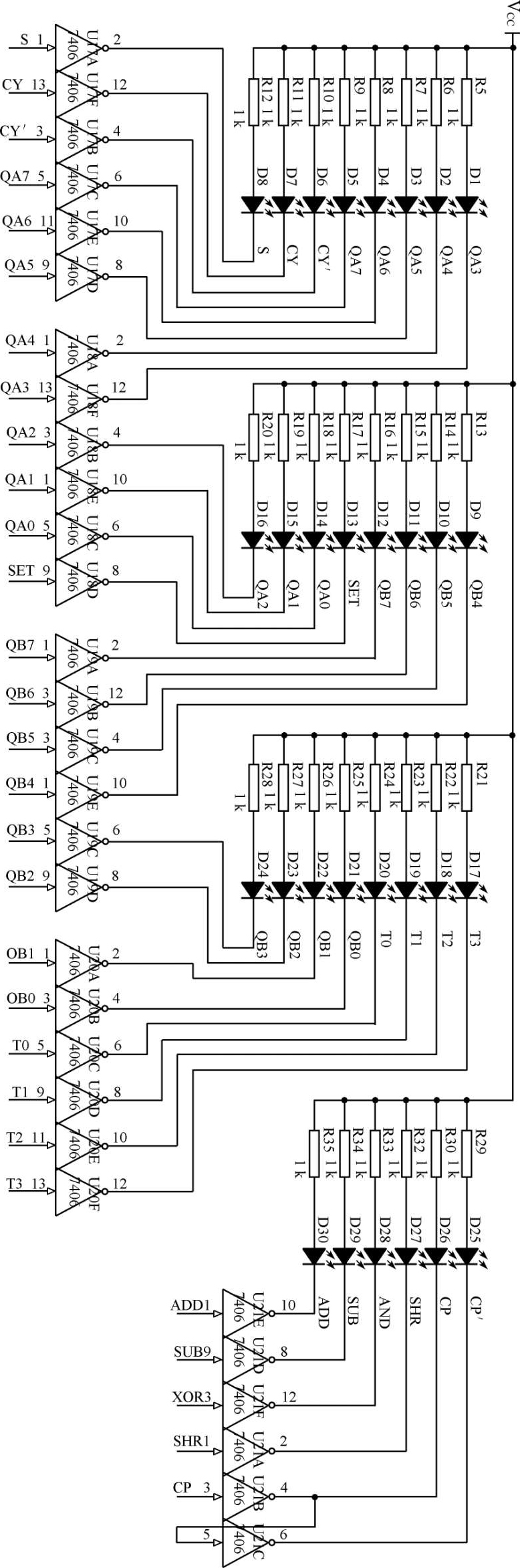

图1-6 系统输出指示电路