本节主要讲述SoC芯片设计整体流程、并行处理的数字芯片设计流程和模拟芯片设计流程3个方面的内容,。

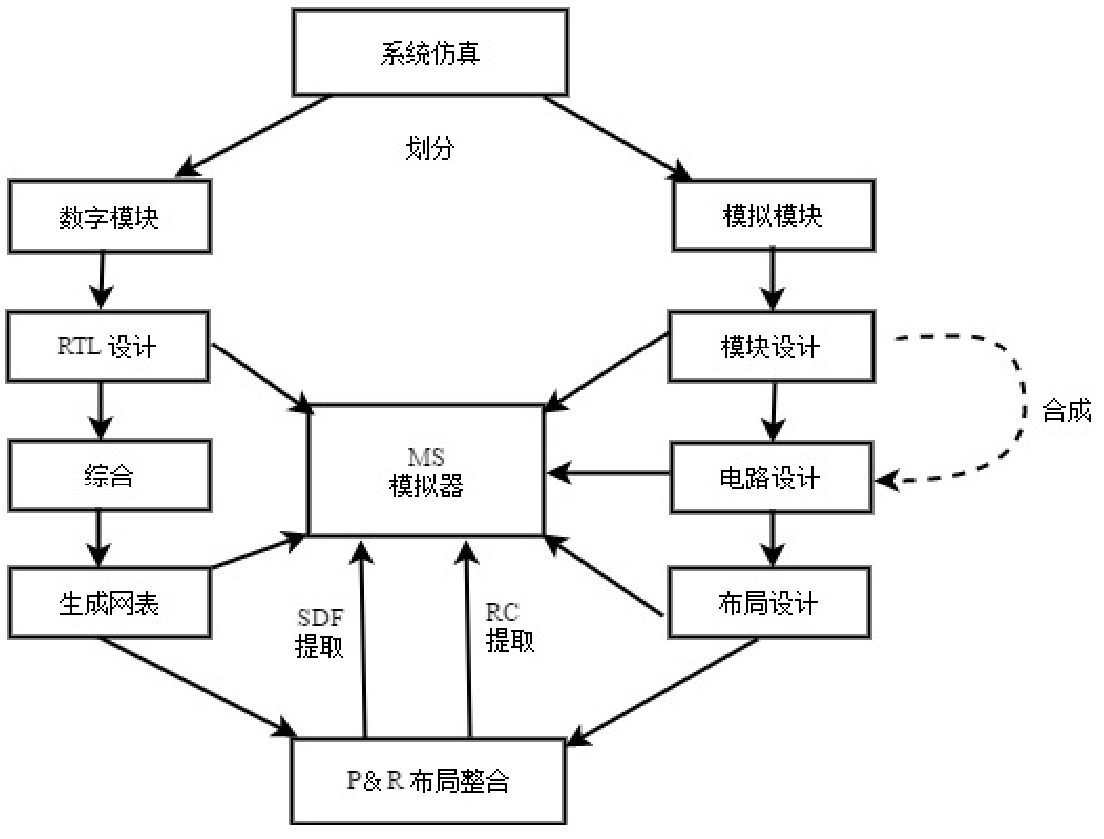

一般而言,SoC设计流程即首先分析系统需求,分割出模块来。其中,模块又分数字模块和模拟模块。数字模块需要经过RTL设计、综合、生成网表,模拟模块则需要经过模块设计、电路设计、布局设计等环节。最后,两者进行布局整合。

具体流程如图4-1所示。

图4-1 SoC设计流程

前端设计(也称逻辑设计)和后端设计(也称物理设计)并没有统一严格的界限,涉及与工艺有关的设计就是后端设计。

数字前端以设计架构为起点,以生成可以布局布线的网表为终点,主要包括基本的RTL编程和仿真,前端设计还可以包括IC系统设计、验证(verification)、综合、STA、逻辑等值验证(equivalence check)。其中IC系统设计最难掌握,它需要多年的IC设计经验并熟悉相应的应用领域,就像软件行业的系统架构设计一样,而RTL编程和软件编程难度相当。

数字后端以布局布线为起点,以生成可以送交芯片代工厂进行流片的GDS2文件为终点;是将设计的电路制造出来,在工艺上实现想法。

后端设计简单说是P&R(Place&Route),但是包括的东西不少,像芯片封装和引脚设计、Floorplan、电源布线和功率验证、线间干扰的预防和修正、时序收敛、静态时序分析(STA)、DRC(设计规划检查)、LVS(电路布局验证)等,要求掌握和熟悉多种EDA工具以及IC生产厂家的具体要求。

术语:

□ Tape-out——提交最终GDS2文件做加工。

□ Foundry——芯片代工厂,如中芯国际等。

数字前端设计的一般流程如下。

1.规格制定

芯片规格也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。

2.详细设计

Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。目前架构的验证一般基于System C语言,对架构模型的仿真可以使用System C的仿真工具。其中,典型的例子是Synopsys公司的CoCentric和Summit公司的Visual Elite等。

3.HDL编码

使用硬件描述语言(VHDL、Verilog HDL,业界公司一般都使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。

设计输入工具:具有强大的文本编辑功能、多种输入方法(VHDL、Verilog、状态转移图、模块图等)、语法模板、语法检查、自动生产代码和文档等功能,如Active-HDL、Visual VHDL/Verilog等。

RTL分析检查工具:Synopsys LEDA。

4.仿真验证

仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格,即检查设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切不符合规格要求的,都需要重新修改设计和编码。

设计和仿真验证是反复迭代的过程,直到验证结果完全符合规格标准。

仿真验证工具有Synopsys的VCS、Mentor Graphics的ModelSim、Cadence的Verilog-XL、Cadence的NC-Verilog。

5.逻辑综合——Design Compiler

仿真验证通过后即可进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表(gate netlist)。逻辑综合需要设定约束条件,就是你希望综合出来的电路在面积、时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积、时序参数是不一样的。所以选用的综合库不一样,综合出来的电路在时序、面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)。

逻辑综合工具有Synopsys的Design Compiler(DC)、Cadence的PKS、Synplicity的Synplify等。另外和综合工具配合使用的还有很多其他工具,如静态时间分析工具、等效性检查工具等。Synopsys公司和Cadence公司都提供了完整的工具包,具体如下。

□ STA

STA(Static Timing Analysis,静态时序分析),属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。一个寄存器一旦出现这两个时序违例,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。STA工具有Synopsys的Prime Time。

□ 形式验证

这也是验证范畴,它从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(equivalence check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,看它们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。形式验证工具有Synopsys的Formality。

前端设计的流程暂时写到这里。从设计程度上来讲,前端设计的结果就是得到芯片的门级网表电路。

一个IC芯片的设计开发大致包括如下8个步骤。

1.挖掘潜在市场

一款IC产品,投入巨大,没有巨大的潜在市场或者收益回报是很难想象的。这就要求公司的决策者要有超前的眼光,发掘潜在的应用点。比如AI时代,所有的手机都会集成AI加速器,以提高手机处理图片的速度。如果设计公司早期能在这方面积累一定的经验,则可以在国内的行业中领先一步。

2.设定IC初期的规格

用途范围不同,规格肯定不同,如车载的和一般家用的,还有军用的。各个用途对IC的耐性能度要求也不同,像ESD耐压、温度变化等。当然最重要的,还是根据协议标准来制定IC产品的规格,如GSM中频处LPF的cut-off量就要达到50 dBc以上,另外,数字移动电视如果是OFDM的64QAM变调,则一般要求锁相环(PLL)的相位噪声积分值要在1 degrms以下。

3.确定总体架构

根据成本、工艺、设计难易度、人力等,来确定到底采用哪种结构,每种架构都有其优缺点。例如,零中频接收器、混频器(mixer)不用考虑镜像干扰,不需要LPF,设计难度降低,但是同时也面临直流偏置(DC offset)的问题,用经过适当设计的DC server电路可以解决问题,但是挑战性较大。

4.设计阶段

根据公司现有人力、物力资源,项目管理者制定好各模块具体设计目标后,工程师同时进行设计。项目管理者必须对系统性能有充分的熟悉程度,并且要使各单元电路分配到合理的设计目标,如压控振荡器(VCO),一般相位噪声和Kv是折中的关系,所以相位噪声要求高时,一般都牺牲面积和功耗,同时Kv保持一定的值,来满足相位噪声的高要求。

个别模块(block)电路设计,在要求设计者有一定经验水平的基础上,一般选用常用的结构,采用新颖的结构时,特别要注意对其元件参数变动、温度、电压变动的仿真(corner simulation)。

5.布线(layout)设计

这时,先要基本确定IC引脚(Pin)的数目、封装(PKG)的类型(这也是需要项目管理者确定的),然后布线(layout)设计者可以根据引脚的配置,确定block的位置。关于个别的block设计,主要包括差分信号的地方要对称配置,信号线、地线(GND)、电源线先要合理配置等,这里主要谈一下总的布线(layout)设计。

□ 本振(LO)和射频(RF)要分开,VCO、xtal都是主要的噪声源,这些模块(block)不能靠射频(RF)、中频(IF)太近。

□ 要设计测试(test block)电路,以便能在测试阶段,对每个关键的block电路性能进行测试。

□ 信号的流向要自然,如射频(RF)信号从左到右、本振(LO)信号从下到上等。

□ Block之间的线(line)应根据要求来选择,如LO的block,对损耗要求不是很高,则可以用metal1、metal2等线节约面积。

6.后期仿真

这里根据CAD资源,每个block的反标仿真(back annotation sim)是必不可少的,block串接起来,局部系统的仿真现在随着CAD工具的发展也可以实现,比如用Agilent的Goldengate小信号高速仿真器,大大加快了仿真时间,提高了设计精度。

7.封装

对于流片,这里不做具体介绍,一般部件的变化浮动都已经考虑进设计过程了。关于封装,如果是高功耗的IC,则一定要进行热阻抗测试。关于热阻抗,以后作者再具体谈。对于一些小的封装公司,热阻抗的测试往往不是很完善,这最终可能会导致使用保存温度范围的要求达不到规格。

8.测试

测试包括block测试、系统测试、ESD、选别测试等多个环节。每个环节都很重要,第一次流片时,测试越具体,越容易发现设计过程中没有考虑到的东西。例如,在block设计中只考虑了P1 dB、IP3等,其实如果是数字电视接收IC,还要考虑CTO、CBO等参数,还有附近频带的干扰,如模拟电视信号的干扰等。

另外,在测试时,如果PCB板也是自己设计的,用Protel、Allegro等带DRC check的软件要比AutoCAD更好;主要电压线设计成可以分离的类型,尽量避免平行临近走线;在关键部位,多考虑设计些预备pad,以增加测试的灵活度。