现代无线移动通信的飞速发展促进了固体功率器件的进步,已经浪涌产生用于基站功率放大器中的具有价格效应、高增益、超线性和高功率输出的RF功率晶体管。巨大的需求、广阔的市场、竞争的指标、潜在的利润,这一切都是动力。传统的RF功率晶体管是建立在BJT技术基础上的,虽然GaAs功率晶体管也有被使用。最近,横向扩散金属—氧化物半导体晶体管(LDMOS)已经被证明非常适合这些应用。与BJT相比较,它们有优良的RF性能,与对应的GaAs功率晶体管相比较,它们具有高的价格效应。因此,这里对LDMOSRF功率晶体管的发展概况及它们在移动通信中的应用做简单扼要的介绍,对LDMOS工作的物理过程也做一定的描绘。重点讨论LDMOS功率晶体管在高线性功率放大器中的应用,以及MOS技术在设计稳定的宽度放大器电路中的考虑。

2.5.1 LDMOSFET与垂直MOSFET的比较

2.5.1 LDMOSFET与垂直MOSFET的比较

与BJT相比较,FET RF功率晶体管的优点已经在前面详细讨论过。这一节将详细讨论LDMOS与垂直MOSFET的比较,及LDMOS的优点。

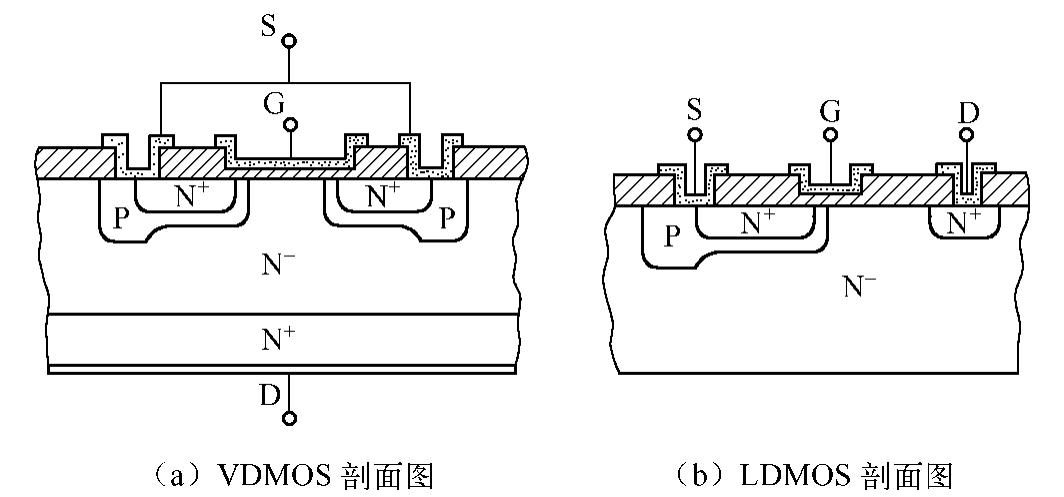

在射频子系统中,使用两种基本的MOSFET结构:垂直双扩散晶体管(VDMOSFET)和横向扩散晶体管(LDMOSFET)结构。如图2-31所示为典型的VDMOSFET和LDMOSFET晶体管的剖面图。这两类晶体管的特性依赖形成它们沟道区域的相反极性杂质连续扩散分布曲线。LDMOSFET利用晶体管的块体来支撑所加的电压,芯片表面有源极和栅极,芯片背面块体是漏极,与横向器件相比较,具有更大的装填密度。换句话说,LDMOSFET由于其电极都在表面,容易与其他元件简单的集成。另外,在较低电压应用中的LDMOSFET的栅极可通过薄的栅极氧化物,在各个方向延伸到漏极N + 区域,在表面积累电荷载流子,栅极的电势大大地降低了N - 漂移区的电阻。这种机理不会发生在垂直结构中,使LDMOSFET单位面积的电流大为增加。这两种结构中,重掺杂N + 源极区域,栅极氧化物和它有直接的重叠。这对栅极—源极电容有贡献,恶化了这些器件的“开关”速度。在金属—栅极技术中,N - 和N + 整个区域使用了微分氧化速率后,这个电容可以大幅度的降低。在高电压应用中,N - 漂移区决定了器件块体的导通电阻。

图2-31 MOS晶体管剖面图

LDMOS的精细布局可使栅极—漏极电容最小,因此减小了反馈电容(C rss ),这是LDMOS在射频无线子系统应用中的主要优点。在一个LDMOS器件中,电流几乎直接从源极流到漏极,与垂直器件相比较,减小了电流堆积。结果,LDMOS器件的导通电阻比垂直型器件低得多。

上述所有LDMOS晶体管的优点,都使它成为现在蜂窝通信中构建超线性功率放大器的最好选择。

2.5.2 LDMOS器件设计

2.5.2 LDMOS器件设计

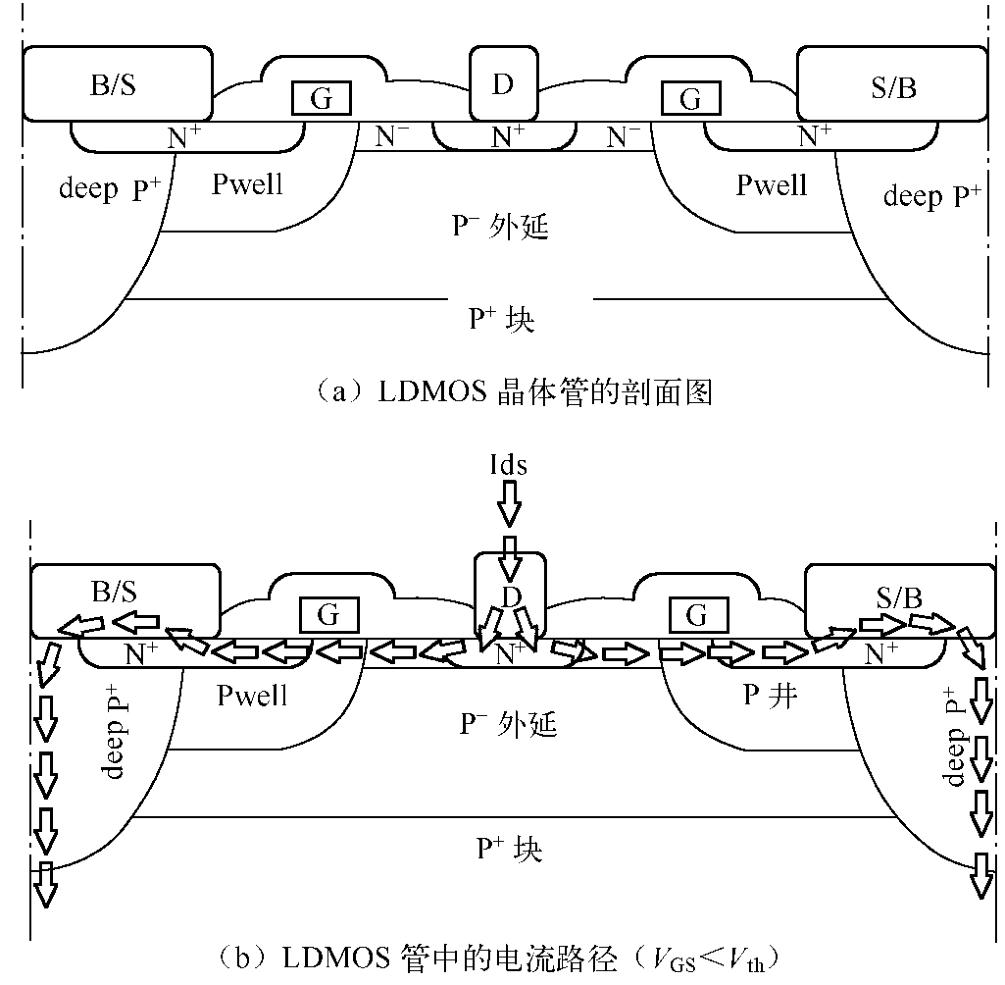

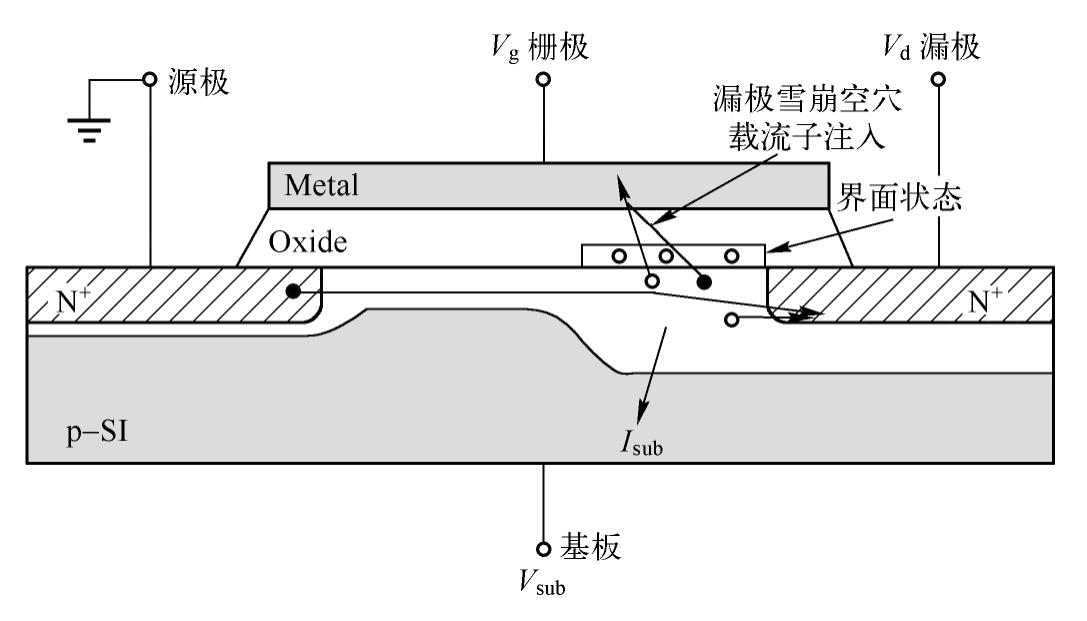

典型的LDMOS晶体管的剖面图见图2-32(a)。器件具有高掺杂P型向下扩散,使用源极对基片的接地。这样就去除了源极到地的额外连接,减小了公共电感,增大了增益。栅极底下的P型区域构成沟道。已经进入工业领域的LDMOS晶体管的漏极电压为3~48V。由轻掺杂(LDD)漏极区可实现LDMOS晶体管较高的击穿电压,这个轻掺杂的漏极区也被称为漂移区。在不存在LDD区的情况下,大部分施加的电压出现在栅极氧化层上,由于碰撞发生,而导致基片区域的击穿。这样,在规定氧化层厚度条件下的击穿电压是一个确定的值。因此,LDMOS晶体管中采用漏极后撤,使其离开栅极,让栅极和漏极边缘之间形成轻掺杂区域。轻掺杂区域要仔细设计,保证在击穿期间的电场是均匀的。如图2-32(b)所示为施加的偏置电压高于阈值电压时电流的流动路径。可以看到,电流流动的方向是横向,因此在沟道区域无大的电流堆积。

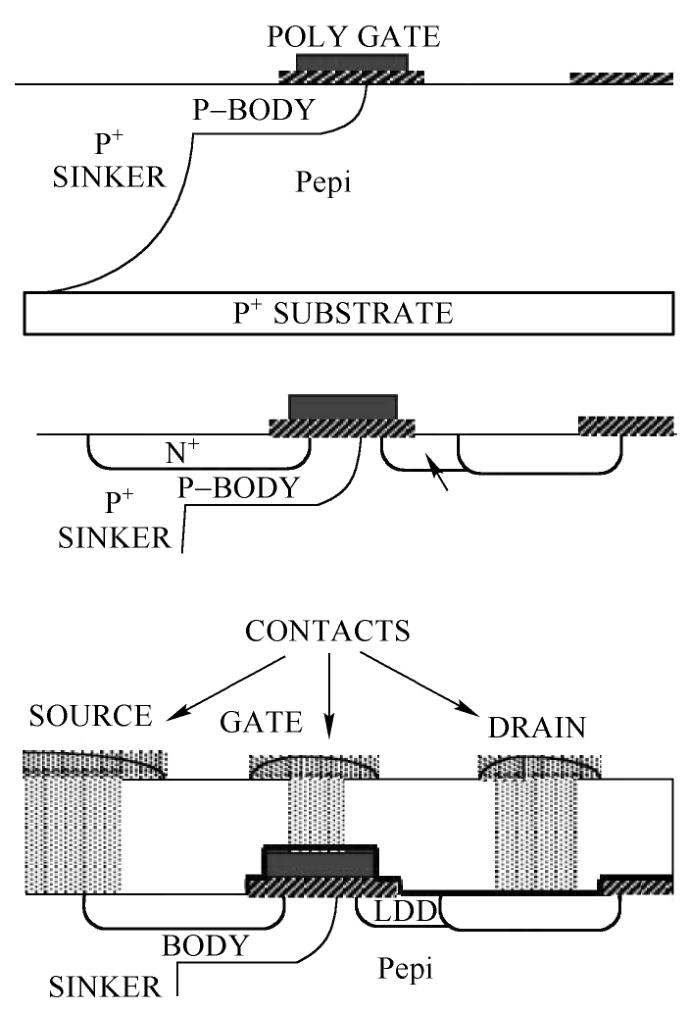

1. LDMOS处理流程

LDMOS晶体管的制造过程如图2-33所示。流程开始于重掺杂P + 基片,在此区上面形成轻掺杂外延区,典型的是生长范围是9~10μm厚,定义有源层。然后,进行高剂量向下注入,向下注入使扩散进入基片区,由注入和多硅结构构成栅极区域。电流发生型RELDMOS晶体管的典型栅极长度范围是0.6~1.0μm。接着使用P—井掩模形成沟道区域;使用掩盖LDD注入和接下来的激活构成器件的漂移区。然后使用掩盖和扩散进入器件的有源区,从而形成源极/漏极区。LDD区的横向扩散和漏/源激活同时完成。整个晶片表面使用屏蔽掩模沉淀TiSi 2 ,这样可以减小栅极和内连接电阻。然后,栅极形成了聚硅化物接触,无源区域生长氧化物,使用接触掩模来腐蚀氧化物。最后,使用单或多层金属化构成电极的接触面。

图2-32 LDMOS晶体管剖面与电流路径

图2-33 LDMOS晶体管的制造过程

2.单元布局设计

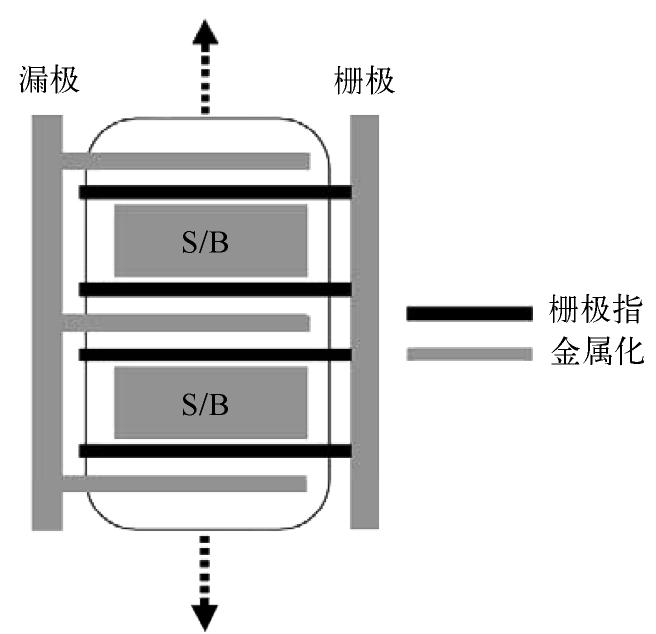

图2-34 单个LDMOS单元布局

如图2-34所示为典型的LDMOS晶体管单元,作为指状布局的平面图,连接每个独立的栅极指形成芯片的一边,连接每个漏极金属化形成相对方向的另外一边,芯片的背面是源极的连接面。顶部源极的金属化面仅是一个很短的N + 源区,它通过深度P + 扩散连接到基片的源极。

有两个因素决定单元最大宽度:

(1)沿栅极指的电压降开始恶化RF性能,这就是为什么再生的硅化物常常被用于减小栅极的电阻率。

(2)漏极的金属化必须有足够大的截面积,这样能够维持每个指分流的漏极电流。

2.5.3 LDMOS的特性

2.5.3 LDMOS的特性

1.直流特性

LDMOS晶体管的直流特性类似于横向DMOS晶体管的特性。LDMOS的典型特性可以通过查阅有关资料获得。

2.静态电容特性

有3个端口电容是FET共有的: C iss 、C oss 和C rss 。这些电容是当晶体管的沟道没有被激活(即无偏置电流)时测量的。对这3个电容的描述如下。

(1)反馈电容(C rss )。这是栅极—漏极之间构成的电容,主要是由于栅极氧化物和器件的漂移区重叠而形成的,因此也用C GD 表示。

与BJT和垂直FET结构相比较,单个LDMOS单元对反馈电容的最大贡献是非常小的。大多数情况下,LDMOS晶体管的反馈电容仅仅只有DMOS晶体管的四分之一。

器件技术的重大改进,如使用亚微米栅极,芯片内部使用特殊的屏蔽技术,已经大大地减小了LDMOS晶体管的反馈电容。现在,RF LDMOS晶体管的反馈电容典型值的范围为15Ff/栅围,栅围的单位为mm。

(2)输出电容(C oss )。这个电容主要是器件中P型块体与外延区之间的结电容。它具有P-N结特性,零偏置时有最大电容值,随漏极—源极电压的增加而下降。C oss 的值由下面的公式给出:

(3)输入电容(C iss )。这个电容中的大部分是在源极金属化的内连接和栅极材料之间形成的。栅极氧化物厚度对这个电容有重大的影响。高频应用下,希望尽可能地减小这个电容。可是,栅极氧化物的厚度不能增加太多,因为厚度越大,晶体管的增益越小,电流的驱动能力越低。C iss 的值由下式给出:

其他对C iss 有贡献的是栅极—源极重叠电容和栅极—沟道电容。

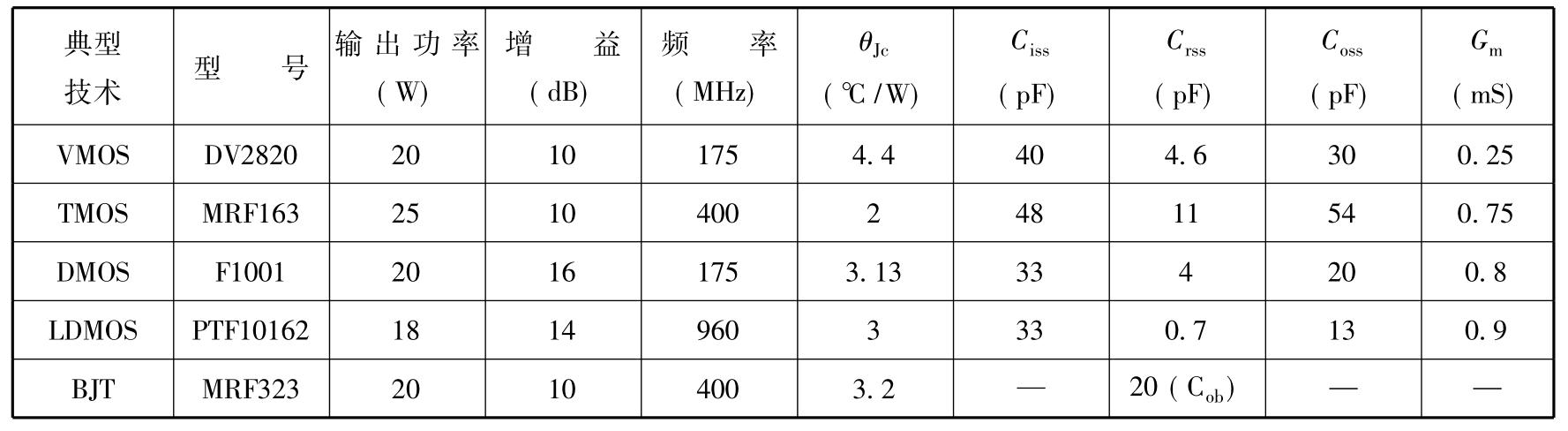

表2-4给出了采用不同技术的RF功率晶体管的典型性能指标的比较。虽然比较不是在同样的晶体管条件下进行的,但是表文提供的是重要的直流和RF参数典型值的一种理解,使人了解每种技术指标的局限性。

表2-4 建立在不同技术上的晶体管直流和射频性能比较(来源于制造厂商的Data Sheets)

从表2-4可以证明: RF DMOS和LDMOS晶体管由于较低的寄生参数,对晶体管的射频性能有重大的改进。

3.动态特性

RF LDMOS晶体管与BJT相比较具有一个主要优点,即对“热的流动路径”不敏感。芯片的稳定增加引起源电阻增加,因此减小了电流流动。

所有的MOSFET对瞬态变化过程都是敏感的,这是因为高的栅极电阻和栅极氧化物被击穿而有失效的可能性。这个问题随着为增加跨导而使栅极氧化层变薄而变得更加严重。

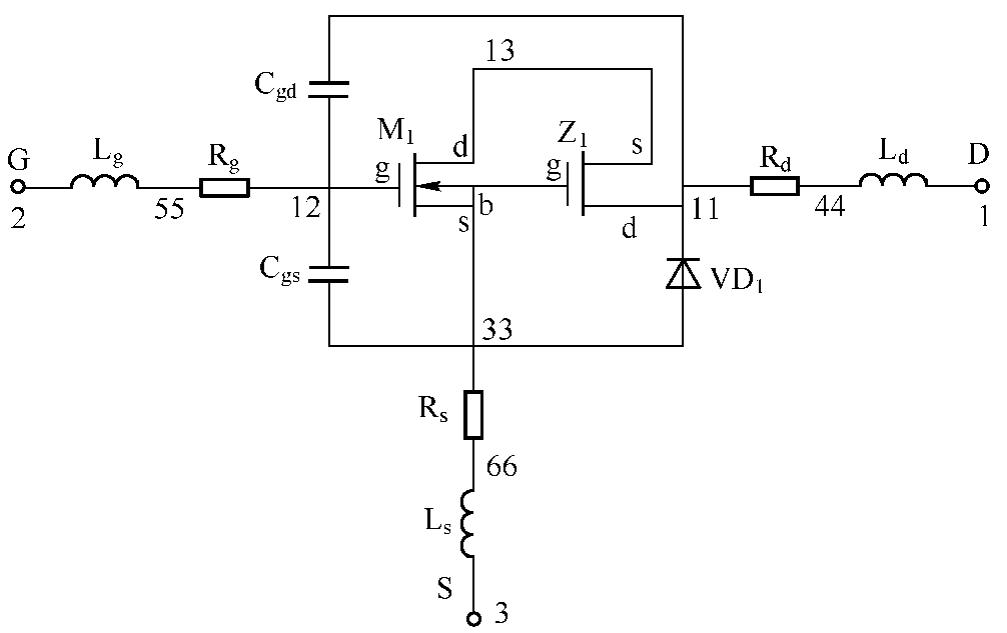

热载流子感应(性能)退化是经过一段时间后的参数漂移。现在的LDMOS器件用了亚微米栅极几何形状,并工作在高电压下。例如,典型基站的LDMOS晶体管的工作电压为24~30V。这样的高电压将引起晶体管沟道中高的电场。离子化产生的热电子和热空穴注入栅极氧化层中,如图2-35所示。一些热载流子,在深栅极偏置电压区被俘获,引起阈值电压和跨导产生实质性的漂移。这个问题当器件用于宽频带线性场合时,如CDMA系统中,变得更加严重。此时,线性度在很大程度上依赖静态偏置工作点。

图2-35 热载流子的注入

这种效应的表现:在固定栅极直流偏置下,晶体管本身的漏极静态电流I DQ ,随时间做对数性延迟变化。这样,为了保证LDMOS晶体管的常数静态电流,偏置电压要做日常性的调整。因此,这种现象也特别地用V GS 的漂移来表征。可以通过合适地修正漂移区掺杂分布曲线,改善Si/SiO 2 的界面质量来减小这种漂移。现在,已经做到经过20年的使用时间后,V GS 仅漂移5%~10%。V GS 的漂移可以考虑用电路来约束,这将强迫晶体管设计者在一些射频性能和提高长期稳定性之间做一些折中。

已经证明: V GS 漂移的主要变化发生在器件“寿命”最初的几个小时之内,而且漂移随漏极偏置电压的增加而增加。因此,减小晶体管特性漂移影响的一种方法是让器件在制造过程结束以后,经过10小时左右的“老化”,然后再测量器件的参数,优化偏置条件,并记录在数据表上。克服这个问题的另外一个方法:现场预先调整晶体管,让其偏置高于应用下的最佳偏置。在决定预先调整量之前,必须正确的知道晶体管随时间的漂移性能。

随着LDMOS晶体管的漂移接近最小值5%或更低时,这种不稳定机理的问题不用再考虑。因为V GS 的漂移已经基本上被系统的其他元件,如电压稳压器和开关等的漂移所遮盖。

4. LDMOS晶体管的封装

LDMOS晶体管的背部源极连接的最大优点是RF功率晶体管封装的法兰用于构成电接地和对散热片的热界面。BJT和DMOSFET晶体管需要电绝缘,这个电绝缘层也是热传导层。这个热传导层一般使用BeO,但是它很昂贵而且有毒。最近使用AIN,它的热性能不如BeO,但是也很昂贵。

5. LDMOS晶体管的RF功率应用

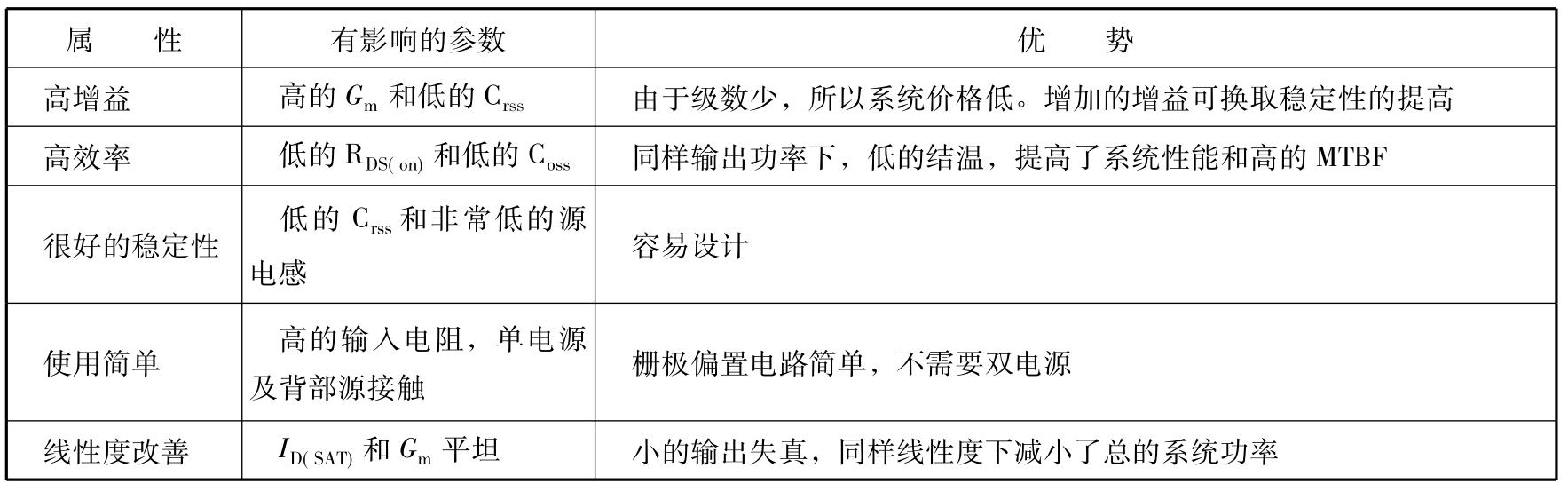

表2-5总结了LDMOS管的特性,使之成为当今射频高功率线性应用晶体管的首选技术。

表2-5 LDMOS晶体管的特性

2.5.4 FET的一些近似设计考虑

2.5.4 FET的一些近似设计考虑

1.电路组态

在下面有关C iss 、C rss 和C dss 的讨论中,只着眼于共源组态,共栅和共漏组态不予考虑,因为这两种组态的输入、输出隔离如此之差,电路是不稳定的。

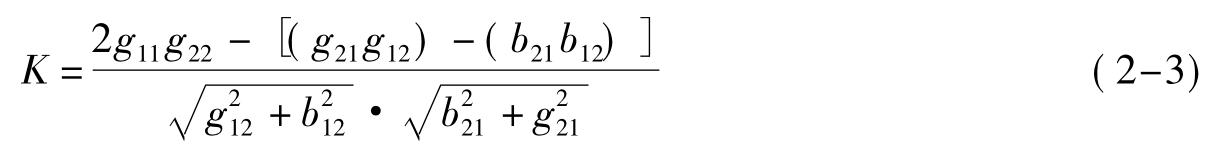

很多种固体放大器稳定性的测度,大多数都用Linvill稳定性因子C或Rollett稳定性因子K表示,K=1/C。

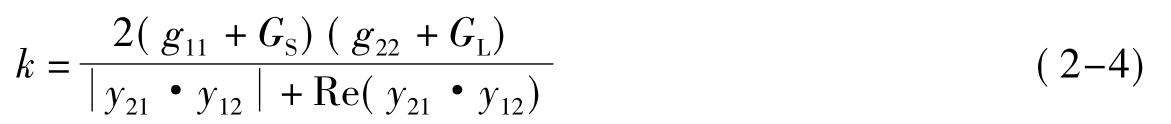

可以看到,C rss 是对稳定性的关键贡献者(反映在b 12 中)。如果C小于1,器件被认为无条件温度,实数和正的负载电阻不会通过反馈产生负的实数输入阻抗。类似的,一个正的实数源阻抗不会产生负的实数输出阻抗。还有一种稳定性因子,被称为Stern稳定性因子k,它包含了器件周围电路的影响,这种稳定性因子的定义为

式中,G S 是源电导,G L 是负载电导。

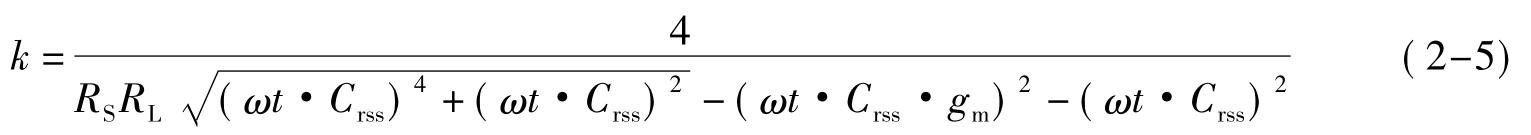

式(2-4)做一些简化假设后可得到一阶近似公式,假设:

(1) g 22 《G L ;

(2)源电阻等于输入电阻;

(3) y 12 的实部或反馈电阻与反馈电抗相比是非常大的;

(4) G m =ΔI D /ΔV G ;

(5) R S 和R L 分别是源电阻和负载电阻。

这样,k可近似为

这个表达式对线性有源器件是正确的,器件可以是FET或BJT。在这种情况下,k>1被认为是稳定的。式(2-5)中的参数不包括外部寄生参数,如公用引线电感和电阻。有些书籍文献把LDMOS管作为无公用引线电感,因为芯片的背面直接附在封装的法兰上。

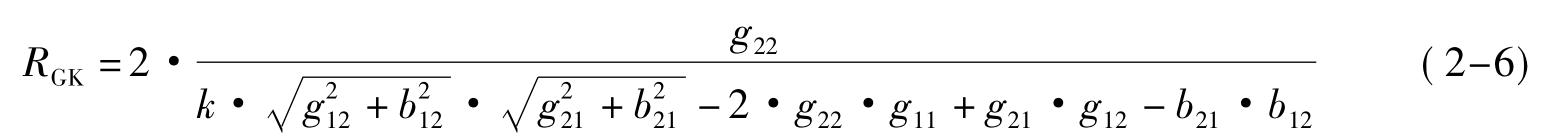

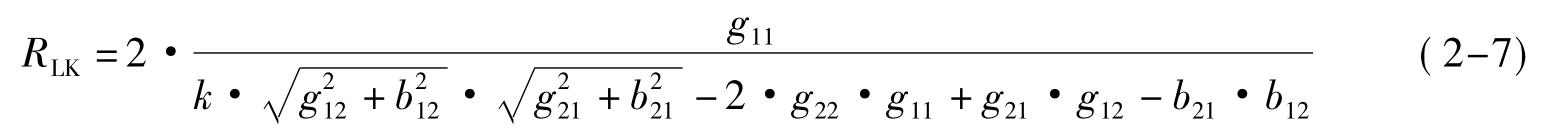

2.稳定性设计

强制有源器件稳定的方法有许多种,其中一个实现方法是,输入电路加阻性负载,或输出电路加上阻性负载,或者输入、输出都加,这时表达式可写为

式中,R GK 是并联在输入与地之间的电阻的阻值。这样可得到所需要的k值。

式中,R LK 是并联在输出与地之间的电阻的阻值,这样可得到所需要的k值。

如果转变成Y参数或Z参数,仍应用这些表达式,那么必须把得到的电阻值与输入或输出阻抗并联。

3. C in 和C out

C rss 对放大器的输入电容有重大的贡献,这里

和

式中,(1-A V )C GD 一般被看成Miller电容。

有些情况通常不在表达式中考虑,稍微修正后也可应用在输出电容表达式中。

和

考虑到增益,C rss 可被看成是一个电容倍增器,可限制频带。从这些表达式中还可以看到C rss 的值减小的优点,这是LDMOS晶体管的最大财富。

如果源引线电感较大,则C iss 、C rss 和C dss 的表达式有实质性的改变。

2.5.5 LDMOS晶体管在现代移动蜂窝技术中的应用

2.5.5 LDMOS晶体管在现代移动蜂窝技术中的应用

1.调制技术的描述

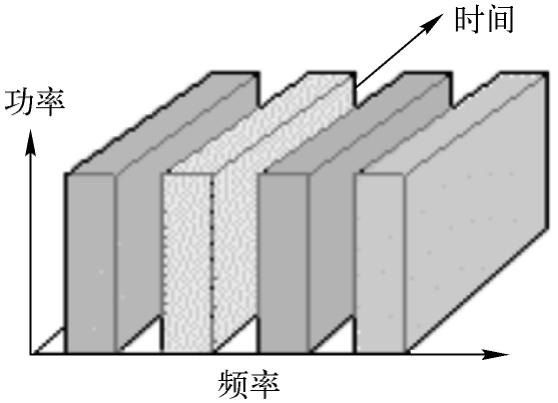

频分多址(FDMA)用于标准的模拟蜂窝通信中,每个用户分配一个RF频谱分立的片区。FDMA仅允许每个信道中有一个用户使用,这个用户可以100%的时间占据信道。因此,信道可想象为在频域“传播”,如图2-36所示。由于移动用户数目迅速增加,经营者被迫寻找有更大带宽的调制方案,增加每个信道中的用户数量,这样FDMA就成为障碍了。

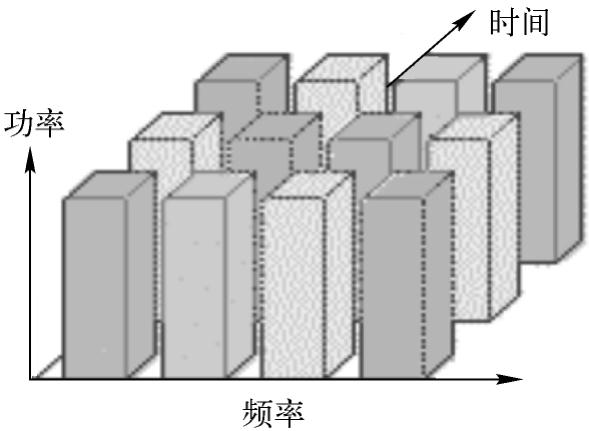

时分多址(TDMA)是多个用户在时隙基上共享RF载波,每一个用户轮流使用通道。频分仍旧使用,但是每个频道又进一步分为一定数目的时隙,如图2-37所示。用于TDMA的接入技术规定3个用户均分30kHz的载频,一个用户分配载波的一个特定时隙,仅能够送出或接收这个时隙内的信息,不管其他时隙是否被使用。对任何用户而言,信息流不是连续的,而是突发性的送出和接收。送出去的字符串在接收端口组合,最后呈现为声音。因为过程非常快,所以要做到这一点是完全可能的。

图2-36 FDMA波形

图2-37 TDMA波形

2. TDMA的优点

TDMA很容易应用于数据传输和语音通信中。一般的承载传输能力是64~128kbps,能扩展为64kbps的倍增数。它提供个人通信业务,如电报、电话、数据通信、短信服务和宽带应用、多媒体和视频会议等。

3. TDMA的缺点

TDMA的缺点之一是每个用户已经预订时隙,可是用户漫游从一个蜂窝到另外一个蜂窝时,可能会分配不到时隙,从而使通话掉线。

TDMA另外一个比较严重的问题是对多径失真敏感。一个来自于塔台到手机的信号可能从几个方向,有直接到达的,还有经过地面或建筑物一次或多次反射的,这就引起了干扰。

码分多址(CDMA)是一种扩频技术,是高级的数字无线电传输技术,代替传统的频分多址和时分多址,采用数字地址码来发现和区分多个无线用户。它使用类似噪声的载波来传播包含在感兴趣的、宽得多的带宽内的信息。但是,由于发生的通话是用数字码来区分的,所以很多用户同时分享同样的频带。商业上使用的CDMA技术的先进方法改善了其能力和声音质量。CDMA技术改变了通信的方法,这是因为:

(1)戏剧性地改进了电话的话务量(比AMPS模拟系统增加了8~10倍,是GSM系统的4~5倍)。

(2)改善了声音质量,消除了由于多径衰减引起的音响效应。

(3)减小了由于脱离控制而失效的偶然性语音变弱。

(4)为数据通信,如传真、网络交通等提供可靠的传输机制,并且增加了隐蔽性。

(5)在给定任何话务量条件下,减小了需设置的支撑点的数目。

(6)由于减少了蜂窝点,降低了配置和运营费用。

(7)降低了平均发射功率。

(8)降低了对其他电子设备的干扰。

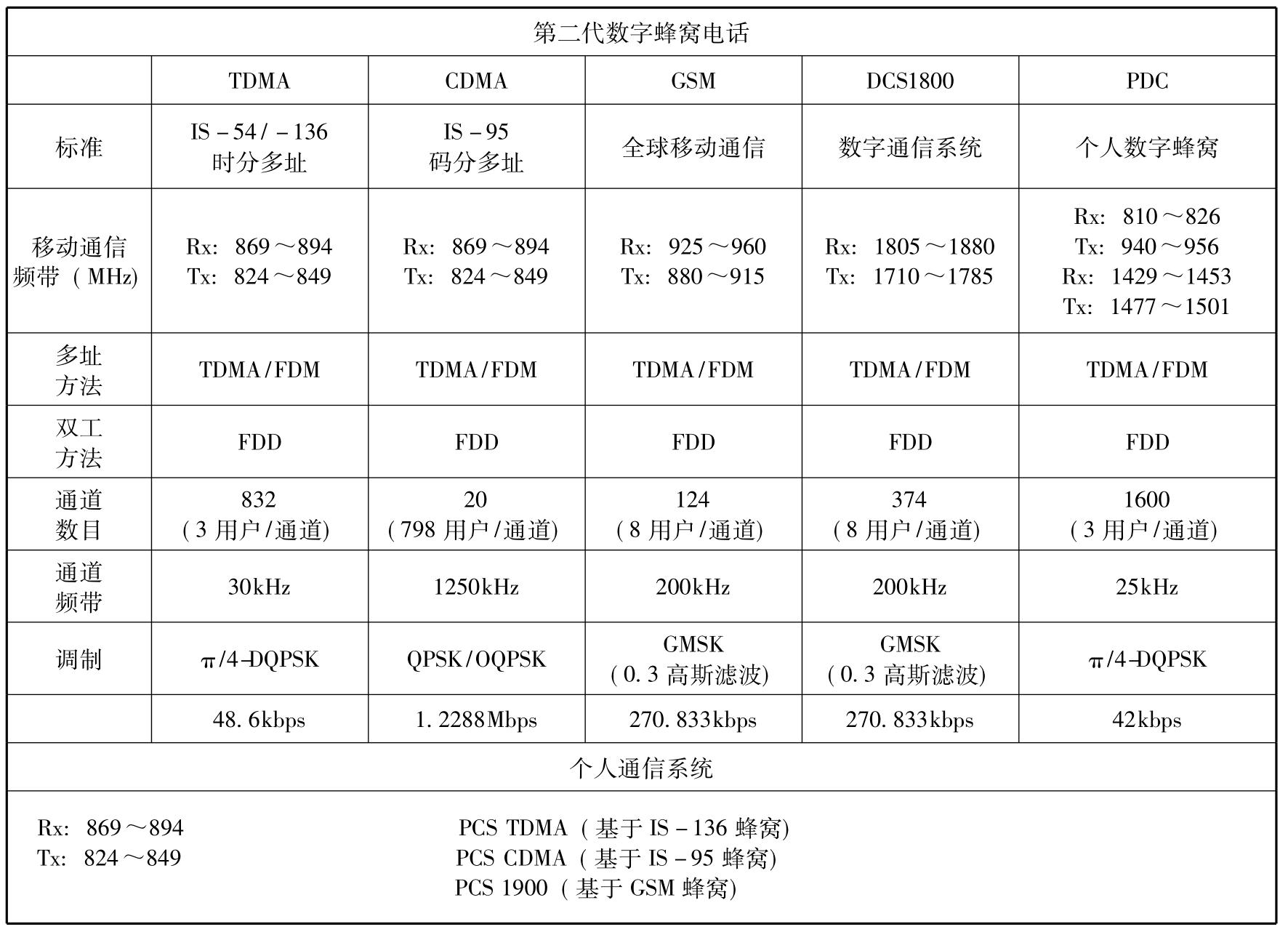

表2-6给出了各种不同用于世界各地的第二代蜂窝和PCS系统的主要特征和优点的对比。注意:所有第二代蜂窝系统面对着低数据传输速率的问题,远低于现代有线网络的传输速率。因此,第三代蜂窝通信,无论是直接产品还是中间产品(2.5G)需要努力的方向都是解决数据的速率问题。

表2-6 当今使用中的蜂窝和PCS系统的技术规范

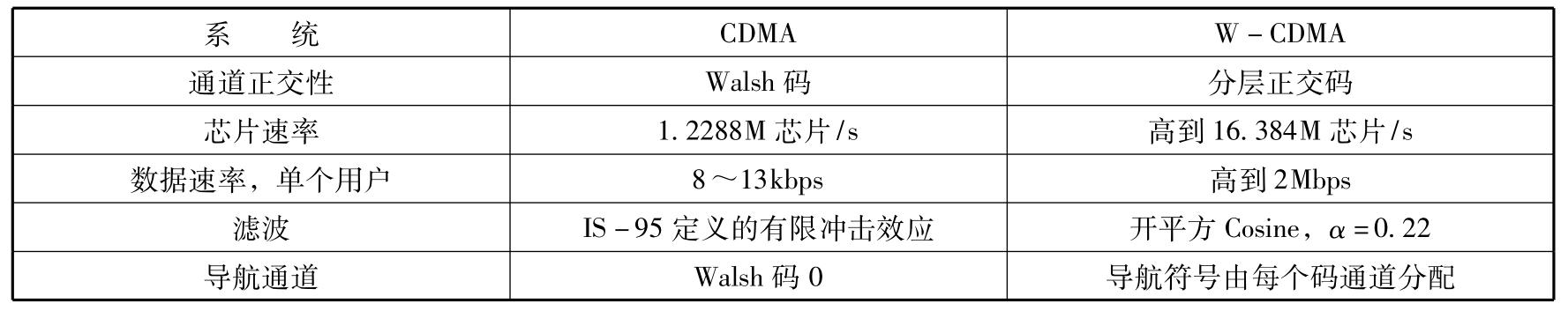

第三代移动通信,在任何由蜂窝覆盖的地方,将使人们能发射和接收语音、数据和视频信号。表2-7为CDMA(IS-95)系统与W-CDMA系统之间的特性比较。

表2-7 IS-95和W-CDMA系统特性

2.5.6 射频功率放大器的特性

2.5.6 射频功率放大器的特性

当优化规定的功率放大器设计时,设计者必须面临困难的选择。在某种情况下,设计者选择送出功率作为优化的关键参数。可是,仅优化一个参数意味着其他参数做了折中。因此,设计工程师必须考虑所有的重要参数,如增益、失真、效率、尺寸和价格。

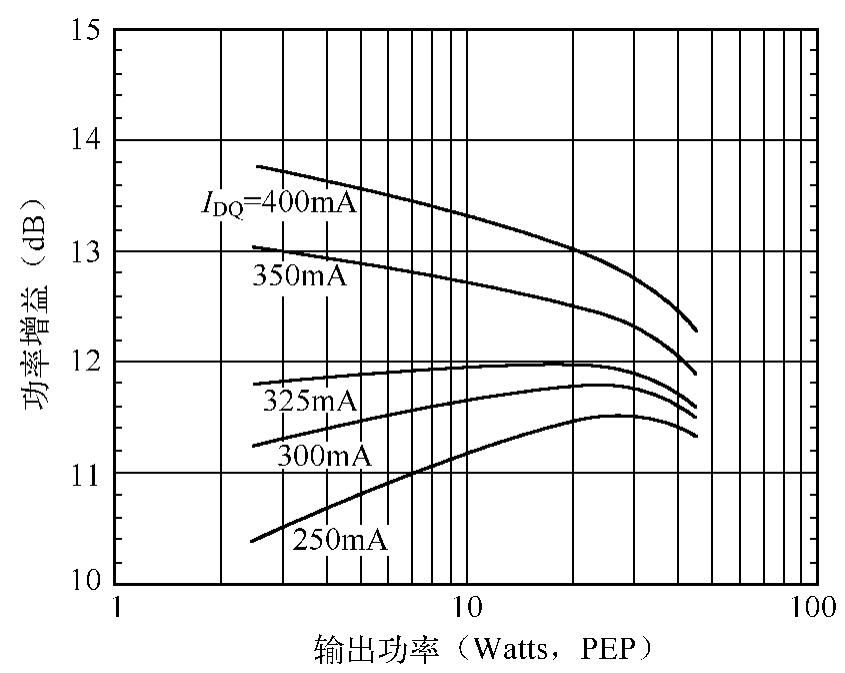

图2-38 LDMOS晶体管的增益对输出功率的关系曲线

选择晶体管的最佳工作偏置点的最快方法是进行增益对输入功率的扫描测量。首先加上晶体管漏极偏置电压,然后增加栅极电压,直到数据表上给定的规范值。设定后加上网络分析仪的输入驱动功率,调整栅极偏置,直到S 21 曲线在规定频带内最平坦。图2-38为典型的LDMOS晶体管的增益对输出功率的关系曲线。注意,曲线的斜率随栅极偏置的增加从正值到负值。最佳偏置在图2-38中为I DQ=325mA。当I DQ 从250mA变化到400mA时,曲线的斜率也在发生变化。

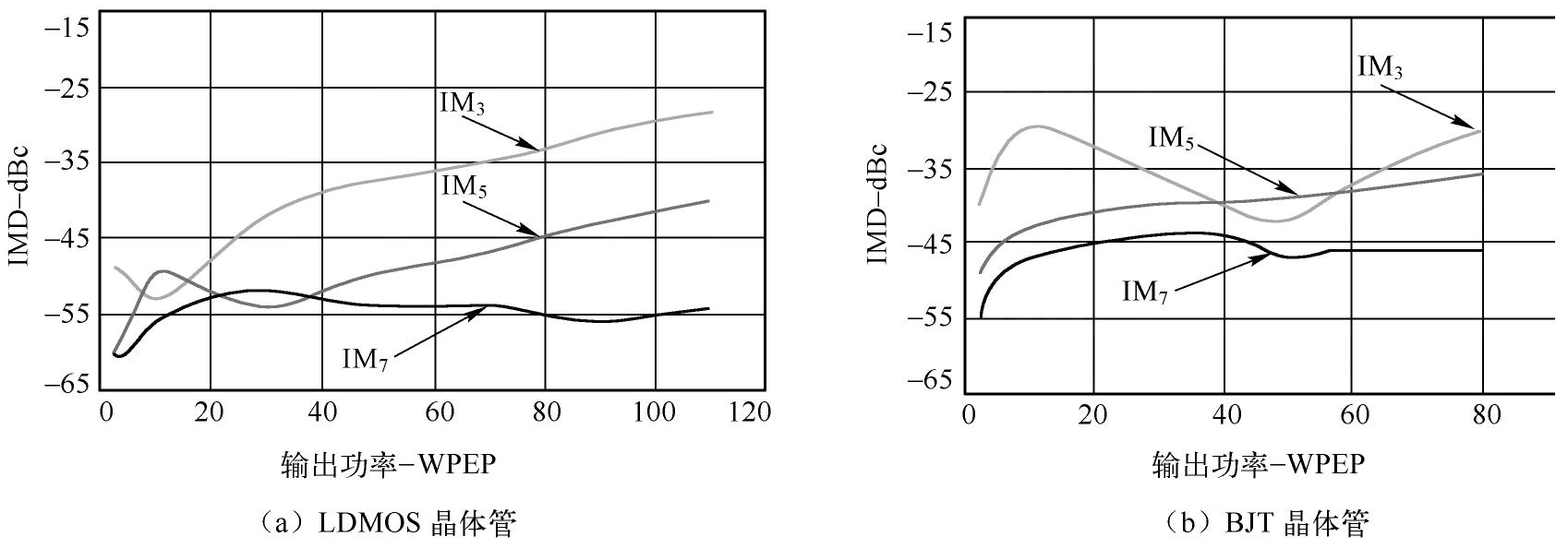

为了线性工作,基带的低阻抗偏置电路提供了优秀的宽带失真性能。使用LDMOS晶体管像DMOS晶体管一样,让放大器工作在AB类,它们的高阶失真性能好于BJT晶体管。LDMOS晶体管偏置电压设置好以后,功率减小时,双音互调失真(IMD)性能改善。使用BJT晶体管时,有一个最佳的偏置工作点,只有此时减小输入功率,双音互调失真性能才能改善。但是,随输入功率的进一步减小,双音互调失真性能反而恶化。

对于LDMOS晶体管,当偏置适当时,IMD性能一般随输出功率的降低而连续得到改善。BJT晶体管趋于一个“醒目点”,此时的输出功率范围对应于最小失真。这个差别的主要原因是LDMOS晶体管比BJT晶体管有更加线性的转移特性。图2-39为LDMOS晶体管与BJT晶体管的双音,3、4、5、7阶IMD特性的比较。

图2-39 互调失真曲线随输出功率的变化

2.5.7 线性度考虑

2.5.7 线性度考虑

1.双音测量

依赖于晶体管的实际应用,不同的设计者遵循不同的方法来确定功率放大器的线性度。最常用的方法:晶体管放大器的输入端口馈入相隔100kHz、功率电平相等的双音信号,确定其输出的互调产物。3、5、7阶互调产物的电平与信号电平相比较,单位是dBc。例如,3阶产物为-30dBc,即是3阶产物比信号电平低30dB。放大器需要调整成这个样子,在回退功率条件下,5阶、7阶、…产物逐次远低于3阶产物,这样可以实现线性宽带设计。

设计用于基站的功率放大器要满足更加严格的IMD要求,双音测试的频率间隔为5MHz或更大。双音频率间隔取决于被测试系统中独立信道的频带间隔。

随着新型测量仪器的发展,这种信号源可以产生高的峰/平功率比的信号,频谱分析仪具有较高的分辨率带宽和较低的噪声电平。使测量功率放大器的各种指标和响应成为可能。

2.邻频道功率比(ACPR)测量

用双音互调的测量来衡量固体功率放大器线性度已经在上一节讨论过了,这个方法比较简单。但是,对最终用于CDMA系统中的基站功率放大器的线性度指标用IMD来衡量存在一个困难——没有好的定量关系。

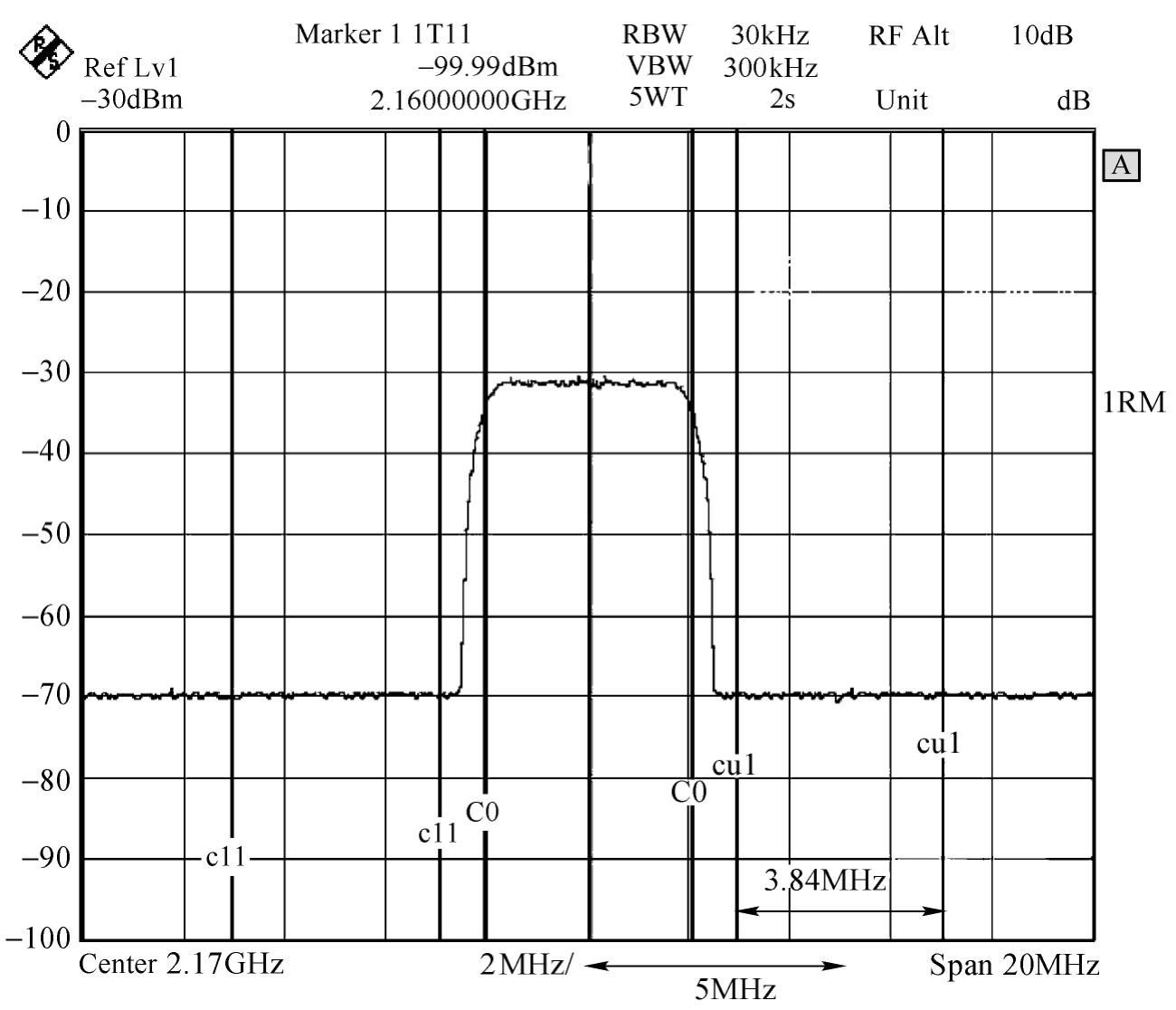

对用于CDMA系统中的基站功率放大器的线性度指标用邻频道功率比(ACPR)或频谱再生来衡量。这两种测量(ACPR或频谱再生)是测量相同的现象,但使用不同的方法。ACPR的测量需要比较射频信道的功率与某些规定频率偏移处的功率,可以表示为功率比或功率密度的比(相同的频带)。功率比的方法是比较在规定邻频道带宽内(如3.84MHz)的功率与进入载波带宽(3.84MHz)内的总功率。如图2-40所示为用R/S频谱分析仪测量2.17GHz的W-CDMA的某个瞬时的频谱图。

图2-40 W-CDMA某个瞬时的频谱图

除了比较射频信道功率与规定频率偏离处的功率密度外,还需要利用积分带宽(IBW)测量偏离处的功率。

在IS-95系统下,离开信道带宽处的偏离带宽与信道带宽是不一样的。射频信道功率的积分带宽为1.23MHz。测量偏离处的功率时,在不同的(频率)偏离下有不同的积分带宽。

工作在线性区域的CDMA功率放大器的效率是不高的,仅有部分直流功率用于产生射频功率,大部分转变成了热量,这就是为什么功率放大器工作在如此高的温度下,需要散热片或外部冷却系统。

表2-8 CDMA基站的共同要求

对最新设计的多载波功率放大器的指标要求更加严格,尽可能小的尺寸,较高的功率增益,好的增益平坦度,小的失真,较高的输出功率和效率。这些指标充分说明,对共有参数的容差更小,为此还提出一些新的指标,如群延迟和ACPR等。为了能对这些指标进行完整的测量,对测试仪器也提出了新的要求。

2.5.8 W-CDMA功率放大器设计实例

2.5.8 W-CDMA功率放大器设计实例

1.功率放大器

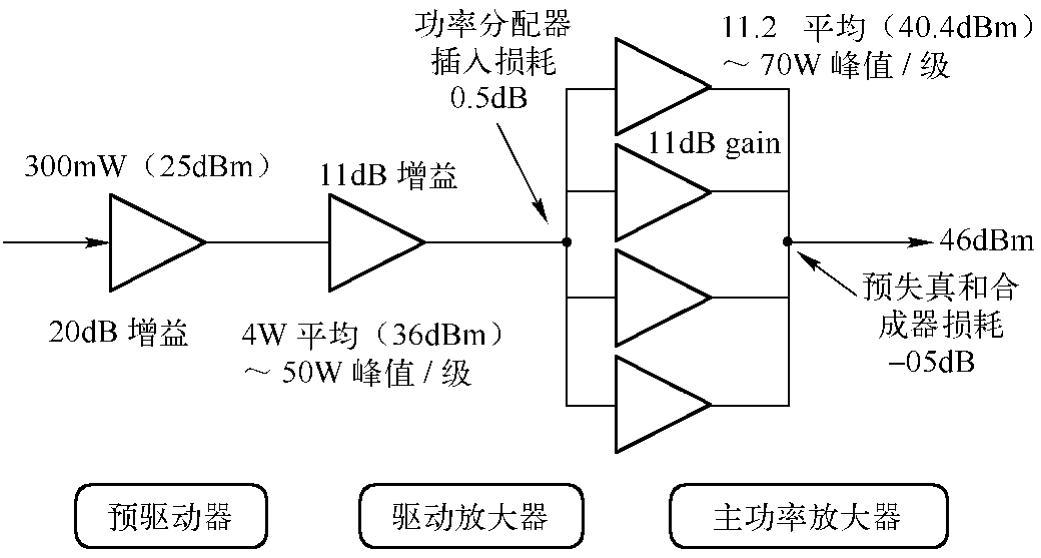

如图2-41所示是单载波、产生48dBm平均输出功率放大器的设计框图,输入信号的形式为W-CDMA,具有8dB的峰/平功率比。典型的放大链由预驱动器、驱动器和末级功率输出级组成。这些级都使用了与现代线性技术相配合的电路,如前馈或卡特生反馈系统等,这是为了获得数字调制系统所要求的线性度指标。LDMOS晶体管最适合做驱动级和功率输出级,因为它们具有较高的线性度,改善的效率和非常低的导通电阻。与老一代采用双极晶体管的系统相比较,由于LDMOS晶体管的高增益,使它在同样输出功率下放大链的级数减少。

图2-41 46d Bm输出功率的W-CDMA功率放大器的设计框图

假设图2-41中的放大器输出功率合成器的插入损耗为0.5dB左右。因此,希望末级输出总功率为46+0.5=46.5(dBm)。4个晶体管并联完成此功率输出,每个晶体管的输出功率为40.5dBm。如果每个管子的增益为11dB,则末级所需要的输入功率为46.5-11=35.5(dBm)。估计输入功率分配器的损坏为0.5dB,则驱动级的输出功率为35.5+0.5=36(dBm)。

正如后面会解释的那样,驱动级的线性要求比输出级高约4~6dB。因此,在输出级为8dB的峰/平功率比,到驱动级则假设为11dB的峰/平功率比。假设驱动级放大器的功率增益为11dB,在这个条件下放大器有足够的线性度,则驱动级需要的输入功率为36-11=25(dBm)。预驱动级一般为高增益级,用小信号晶体管做成放大器。在此情况下,增益为20dB,它可以为驱动级提供足够的输入功率。

2.正确选择线性应用的晶体管

正确选择每一级放大器的晶体管,有多个因素需要考虑。这种系统中的输出级和驱动级,典型的偏置在AB类工作,这是为了在线性度和效率之间做最好的折中。预驱动级偏置在A类工作,这是为了减小由于偏置电压小的变化对线性度的影响,从而获得相容的性能。这里还必须强调的是,预驱动级的漏极效率不像对后面二级的效率那么关心。

输出级晶体管的选择必须非常小心,有多个正确选择的方法,关于每个方法优越性的争论正在减小。决定正确选择晶体管的一种最流行的方法是看特征晶体管在功率压缩时的峰值功率。以往典型的作为放大器设计的最好依据是P -1dB (1dB压缩输出功率)。这种方法被证明适合作为GSM和TDMA系统功率放大器的设计,它们无严格的线性度指标要求。现在的系统,强调的指标已经转向线性度。当今,在规定应用下选择晶体管,已经不可避免的基于线性度要求了。

前面已经说过,用于表示晶体管放大器线性度指标的一个最普遍的方法是间隔100kHz的双音互调失真(IMD)测量。已经被证明对窄带调制系统,如IS-95(CDMA)系统,是一种非常有效的选择晶体管的依据。典型的测量是在接近晶体管的峰值功率下测量的,这个功率电平指标由数据表给出。根据经验,晶体管限定峰值功率就是由当三阶互调分量低于载波功率大约30dB时,在环境温度下传递的输出功率所决定的。

现在的调制标准使用的信号具有8~12dB的峰/平功率比。因此,用于功率放大器的晶体管必须满足当信号电平比平均功率高12dB时仍有足够的线性。当晶体管用于从它们的峰值功率电平下回退的状态,这时要考虑晶体管较低输出功率状态下的IMD特性。好的晶体管的IMD对P out 的曲线应该有大的正斜率,即使达到相当的功率能力时也是如此,这样可以得到最大的ACPR。

用于驱动级的功率晶体管应该具有与输出级晶体管相同的线性度要求。根据ACPR,它需要比输出级最大输出功率下所需驱动级的推动功率还多4dB的裕量。另外,为了保持有常数的群延迟和平坦的增益,驱动放大器的输入带宽需要比调制信号带宽宽约2~2.5倍。决定W-CDMA环境下晶体管性能的主要因素之一是增益的平坦度。当用于多载波功率放大器和使用前馈线性化技术中的放大器时,晶体管放大器的增益平坦度的要求是带宽内增益变化小于0.2dB。非常平坦的增益响应极大地简化这种线性化系统的设计。

预驱动器一般用GaAs异结,BJT(HBT)或GaAs MMIC。这些器件一般被设计成高增益模块,具有2~3级的放大。

2.5.9 CDMA放大器设计和优化的电路技术

2.5.9 CDMA放大器设计和优化的电路技术

这一节介绍一些在晶体管功率放大器电路设计者之间流行的试验、测量和调整技术,并且对宽带调制系统进行优化尝试。

1.宽带应用的偏置优化

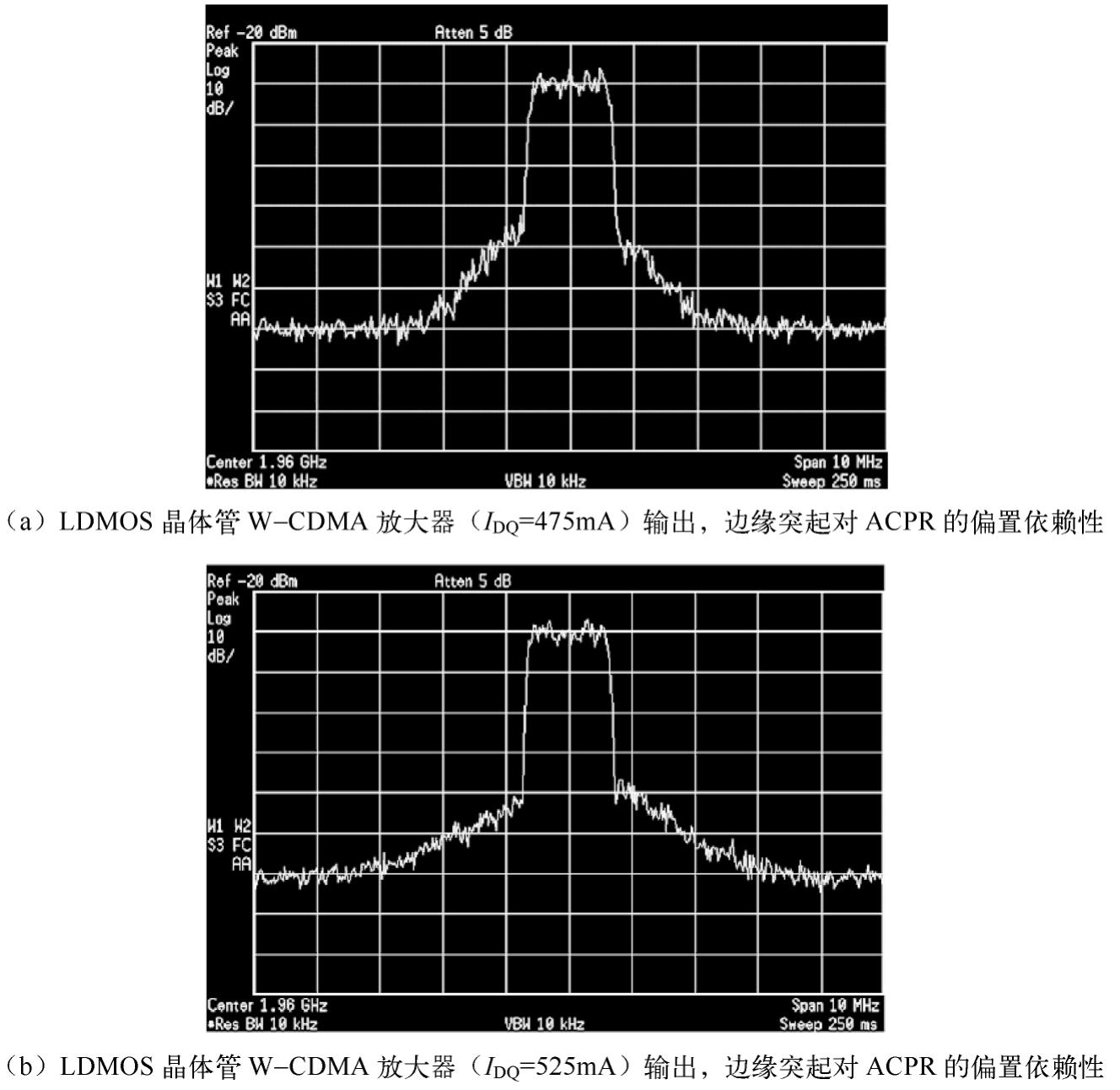

对一个已经调整到最大增益和最大效率的放大器,实现最好的双音线性度指标的办法是偏置电压围绕它的工作点做小的调整。当测试宽带下的线性度时,已经观察到偏置点需要稍微调高一些。当设计用于CDMA和W-CDMA的功率放大器时,情况更是如此。直流偏置点决定放大器输出响应低的频带,还是高的频带突起或平衡。正如图2-42所示,偏置能调节改变放大器输出响应边带的突起电平。获得最好的宽带线性响应使用的I DQ 较高,增益对P in 曲线平坦度响应所需的I DQ 较小。如图2-42(b)所示,在此情况下,ACPR是最好的,此时放大器偏置在525mA上。

图2-42 使用LDMOS晶体管的W-CDMA功率放大器的输出频谱

图2-42 使用LDMOS晶体管的W-CDMA功率放大器的输出频谱(续)

2.实现宽带信号最好线性度指标的技术

(1)双音互调测试中,奇阶失真产物在决定宽带线性度指标中扮演重要的角色。这些产物要减小到比三阶产物低得多的程度。

(2)为了得到最好的W-CDMA性能,放大器应该被证明具有好的IMD特性。在WCDMA应用中,调试放大器时,双音间隔要大到20MHz。

(3)对宽带信号,相位和增益在整个感兴趣的带宽内的平坦度对ACP性能有重大的影响。

(4)在频带边缘,增益的快速滚降引起ACPR性能的恶化。

(5)为了获得器件内在的线性度,偏置网络的3dB带宽至少应该大于调制带宽的2倍。

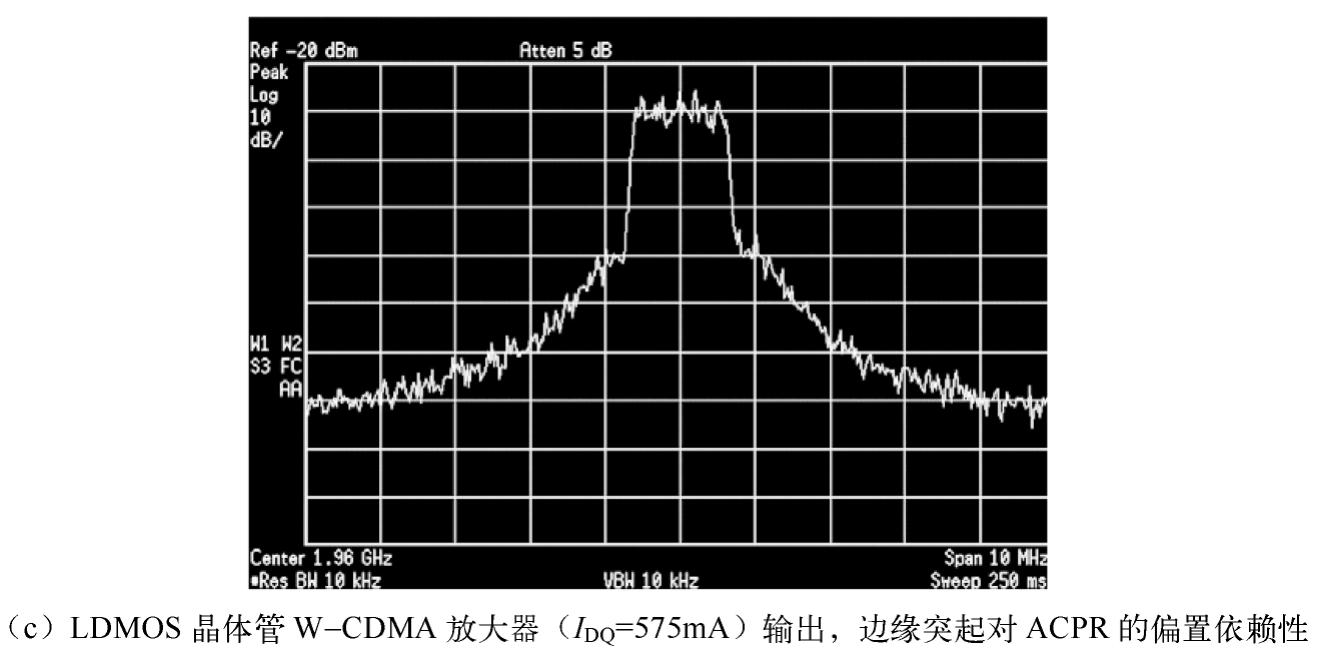

如图2-43所示为Ericsson微波电子公司的LDMOS晶体管做成的W-CDMA放大器。图中给出了输入、输出偏置和去耦网络。为了获得最好的ACPR响应,需要对漏极有优良的去耦网络,去耦合频率可低到非常小的调制频率。去耦网络中要使用质量非常好的电容,这样可以实现最大增益平坦度,在宽带应用中这个技术非常关键。

图2-43 LDMOS晶体管W-CDMA放大器

忠告:偏置网络中尽量避免使用铁氧体元件,在栅极偏置网络中可以使用串联电阻,避免不稳定性发生。

为了实现带宽内的平坦增益响应,传统的对栅极、漏极的电感馈电方法应该避免,取而代之的是使用感兴趣频率上的四分之一波长线,使用适当的芯片电容去耦。据报道已经做出了非常平坦的增益,在整个频带内的增益波动仅为0.1~0.2dB。

3.现代宽带CDMA应用中的LDMOS射频功率晶体管的典型性能

目前,大部分制造厂商的LDMOS晶体管具有典型的栅极长度为0.6~0.8μm,栅极氧化层的厚度为400~500。晶体管由低功率组件并联组合而成(典型的每个组件的P -1dB 能力为44dBm)。有关的数据表可查阅资料,也可从公司网站上下载。

2.5.10 LDMOS晶体管的模型

2.5.10 LDMOS晶体管的模型

LDMOS晶体管技术领先的制造厂商正在发展器件和电路模型,用于准确预知器件在不同工作条件下的DC和RF性能。模型提供了对器件工作过程的合适的理解,目的是容易对器件的过程参数进行优化。这就允许发展适用于不同场合下的模型。更重要的是器件模型对放大器和系统设计者是有效的工具,人们可以把这些模型与高水平仿真结合,对系统进行优化。

不同的制造厂商有不同的方法来完成这个共同的目标:发展出一种模型,能可靠的预知器件的射频性能。发展LDMOS晶体管的准确模型还没有非常成功,因为在建模时遇到的困难是器件漂移区(LDD)的特性模型。LDMOSFET的这一部分极大地影响器件的击穿电压、导通电阻、饱和电流和反馈电容。因此,在任何准确的器件模型被研发出来以前,必须强制性地理解晶体管这个区域的工作机理。

当前,有很多分析模型用于模仿LDMOS器件。在它们之中,Root模型是最流行的,这是以查表为基础的模型,依靠在整个工作条件下,用广泛的测量数据来建表,模仿晶体管的直流和电容特性。这类模型的主要缺点是:它不是以晶体管工作的物理性质为基础的,而是依赖无物理重要性的参数来建立模型,只要仿真参数与测量参数有好的一致性即可。这种模型无法模仿自热效应。一种好的模型必须具有最少的模型参数,而且这些模型参数容易从直流和小信号测量中抽取。它还应该考虑由于晶体管的自热而引起的性能恶化。

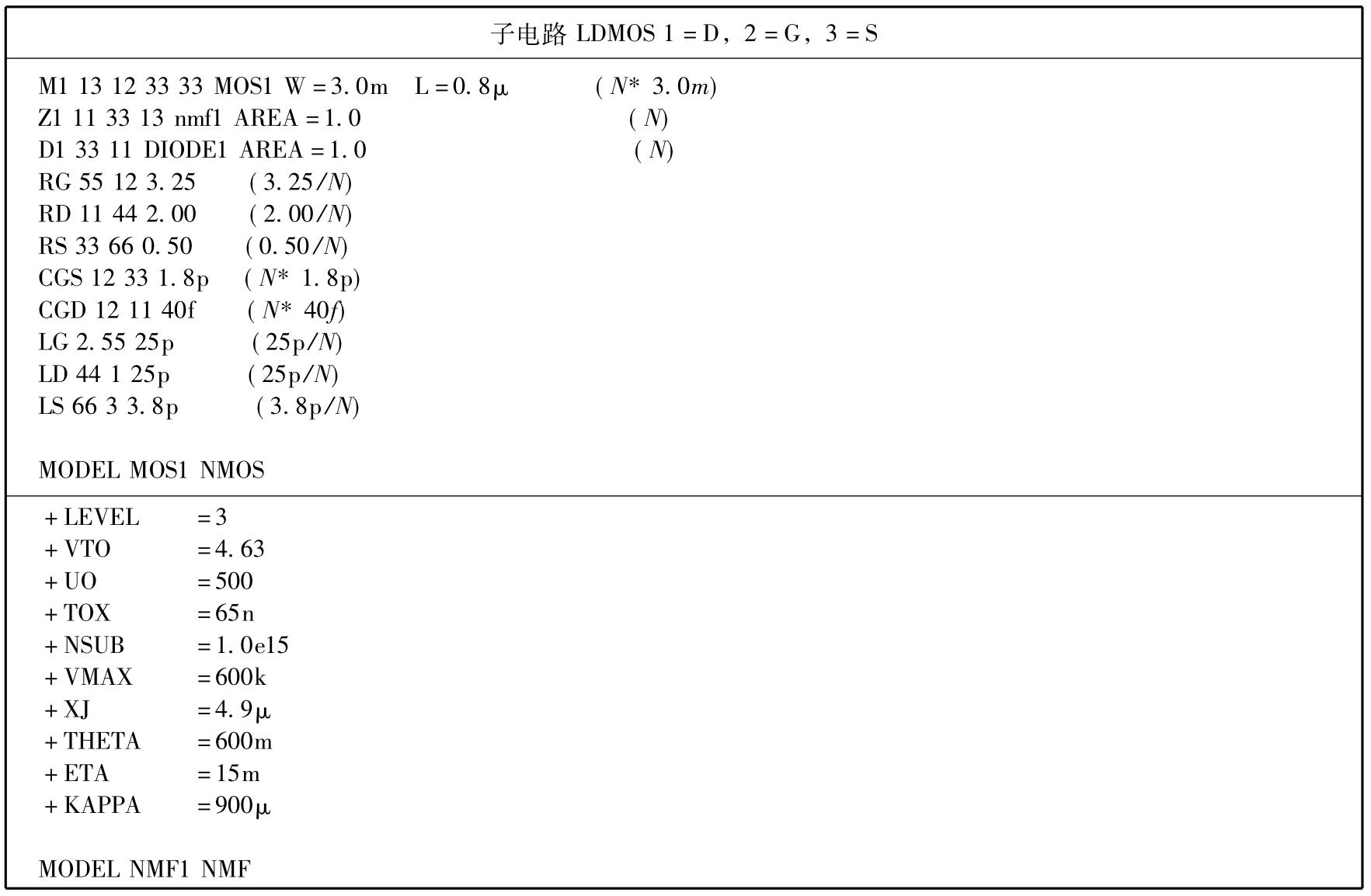

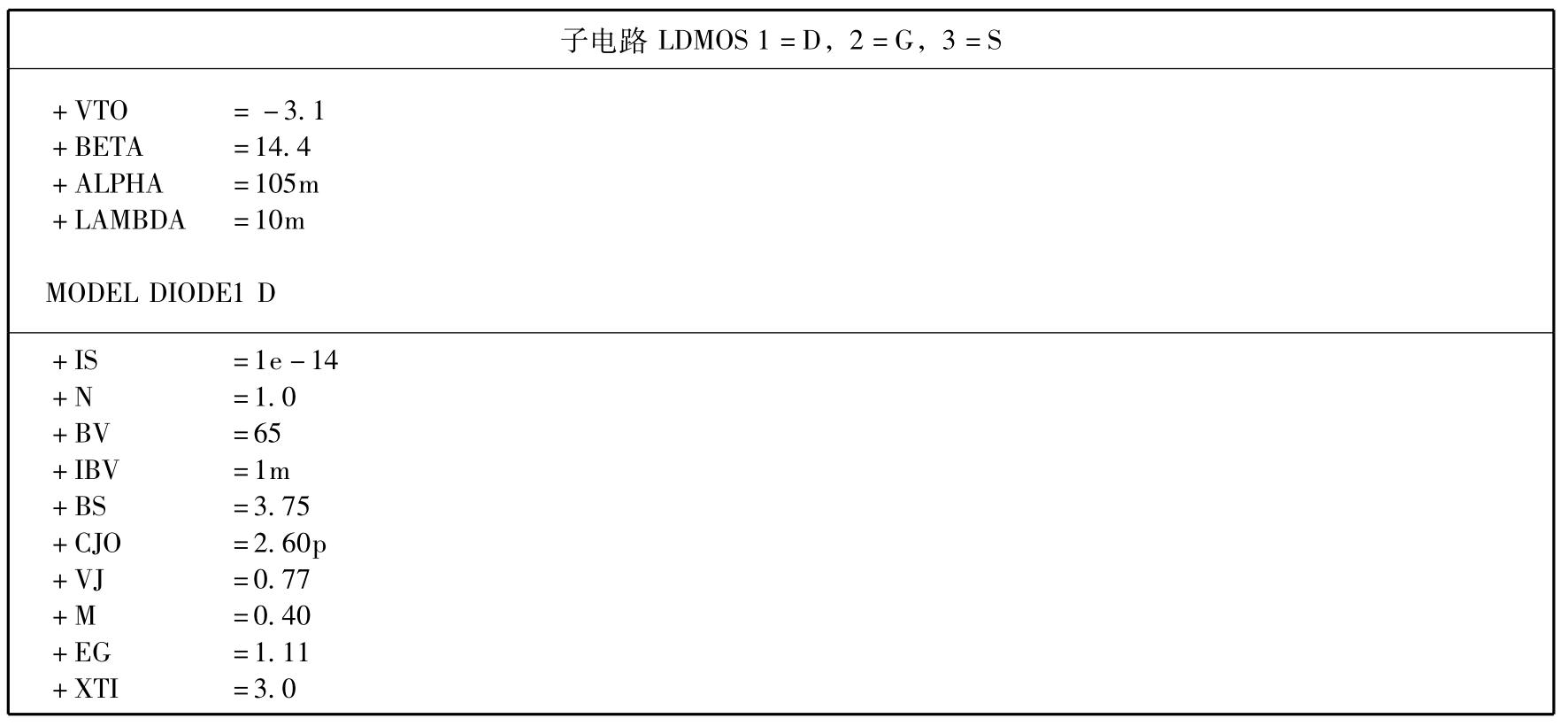

1.器件的物理基础子电路模型

这类模型使用了多个电路元件代表LDMOS晶体管不同区域的行为。它基于MOS层3模型(UCB SPICE模型)来模仿器件的沟道区域。它还有用来模仿漂移区的非线性电阻和电压依赖性电容,以及器件的其他寄生参数。这个模型已经被发展成器件工作的物理性理解的基础。在一种有限元处理/器件仿真环境中,可推导出范围广泛的电热仿真,还可以对器件进行直流仿真和小信号S参数仿真。

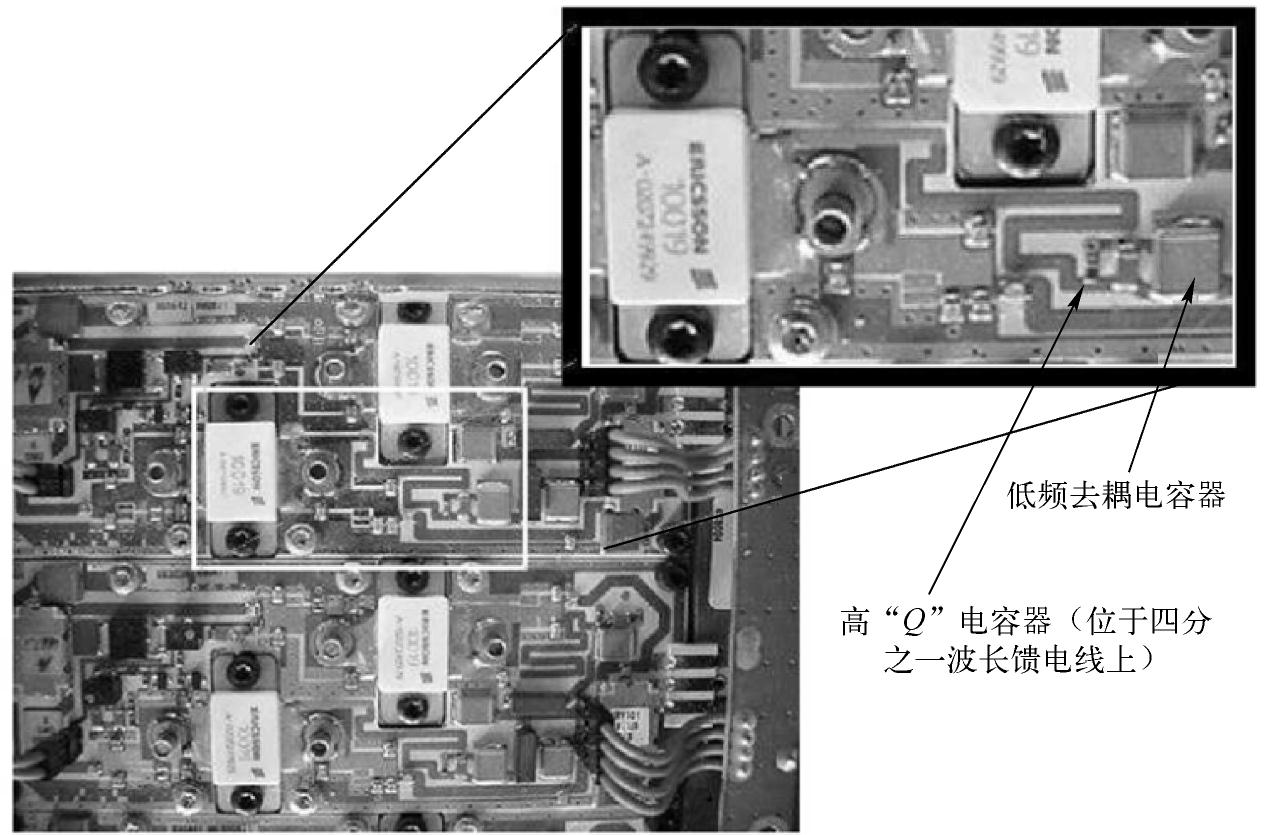

如图2-44所示为一种封闭盒子电路模型,还包含模仿内连接及由封装引起的外部寄生的元件。对硅芯片单元数目的模型参数的定标特性也在图中给出来了。已经发展出两种不同温度的模型列表,这里的温度是指芯片背面的强制温度,这个温度可能稍微不同于芯片温度。这样做的目的是给模型使用者一些关于芯片温度如何影响器件性能的概念,它可在一些假设的温度下仿真。

图2-44 用于仿真器件射频性能的包含有寄生元件的子电路模型

图2-44中每一个字母代表一个电路元件。M1是MOS LEVEL3MOSFET,代表LDMOS的沟道区。Z 1 是MESFET的Statz模型,代表LDMOS的漂移区。VD 1 是标准的二极管模型,代表漏极—基片/源极二极管和基片网络。其他符号,像使用在一般仿真中的一样,有它们习惯的意义。图2-44中的数字是用在子电路网表中的节点数目。

表2-9给出的是具有N个单元的参数定标因子。参数值用单元数目N定标的用醒目的符号和斜体表示。列在表上的参数值为一个单元(即N=1)的数值,如果N≠1,则这个值应该被同一行括号内的计算值代替。

表2-9 T=27℃下的模型参数表

续表

比较不同温度下给定晶体管由推导得到的模型参数,可以发现:仅3个模型参数有大的温度依赖性。它们是UO(迁移率)和在状态MODEL MOS1NMOS下的VTO(阈值),以及在状态MODEL DIODE1D下的RS。

采用这种方法的最大优点是模型的定标能力。这个模型能容易的为不同的栅极几何形状定标。因此,可以在研发最好的晶体管中作为设计、理解的辅助工具。

这个方法的主要缺点是不能准确的模仿晶体管的C rss 随偏置变化的特性,这就使线性度仿真与测试之间产生重大的差别。同时,这个模型没有直接的方法来考虑器件的动态自热现象。这个模型已经用于仿真,并在不同的温度下进行仿真和对比测量。

2.电热模型

由Motorola Inc.研发的电热模型是一种经验性的大信号非线性模型,它包含静态的和动态的热函数关系。这个模型描述了I-V特性和器件不同工作区域的I-V特性的导数。它使用一组方程能控制漏极—源极非线性电流特性的电热行为。这个非线性特性是在脉冲条件下,不同温度时经广泛测量而得到的。它也依靠复杂的脉冲S参数测量来抽取代表电容的模型参数。这个模型的主要缺点是模型参数太多,还包含大量的无物理意义的曲线适配系数。

3.结论

至今尚未有一个公开发表的单个模型,能够完美地预先指出LDMOS晶体管的非线性特性,所有模型几乎同样的只能给晶体管功率放大器设计者初始入门的近似设计。除此之外,调整和优化输入匹配网络和输出匹配网络的传统方法是必须遵循的。

希望在实际应用中使用这些晶体管模型来仿真设计高性能功率放大器的电路和系统设计者发现,由于涉及大量的模型参数,模型并没有足够的准确度。人们也必须认识到,系统中有很多有源器件,这样进行系统仿真,模拟高功率的FET还是不可行的。大部分晶体管制造厂商,规定了给定应用中晶体管工作的最佳源阻抗和负载阻抗。功率放大器设计者从晶体管数据表中给出的这些阻抗,开始他们的设计,然后在系统层面上进行试验、优化,最终完成系统要求的性能指标。