CPU12是一款高速16位中央处理单元(Central Processing Unit,CPU),与68HC11中央处理单元CPU11具有相同的编程模型。CPU12指令集是对68HC11指令集的扩展,68HC11程序无须修改可在CPU12运行。CPU12X指令集是对CPU12指令集的扩展,CPU12程序无须修改可在CPU12X执行,但CPU12X不支持CPU12的模糊指令集。

CPU12(X)内核主要有以下特性:

● 16位数据宽度支持高效算术运算和高速数学计算;

● 支持多字节指令,包括大量单字节指令,能更有效利用ROM空间;

● CPU12X指令运行效率更高。CPU12X能够在指令队列缓冲区中,立即存取至少3个字节的机器码;

● 强大的变址寻址能力,包括:

✧ 堆栈指针作为变址寄存器寻址;

✧ 程序计数器作为变址寄存器寻址;

✧ A、B或D累加器偏移量寻址;

✧ 自动先递增或先递减、后递增或后递减变址寻址。

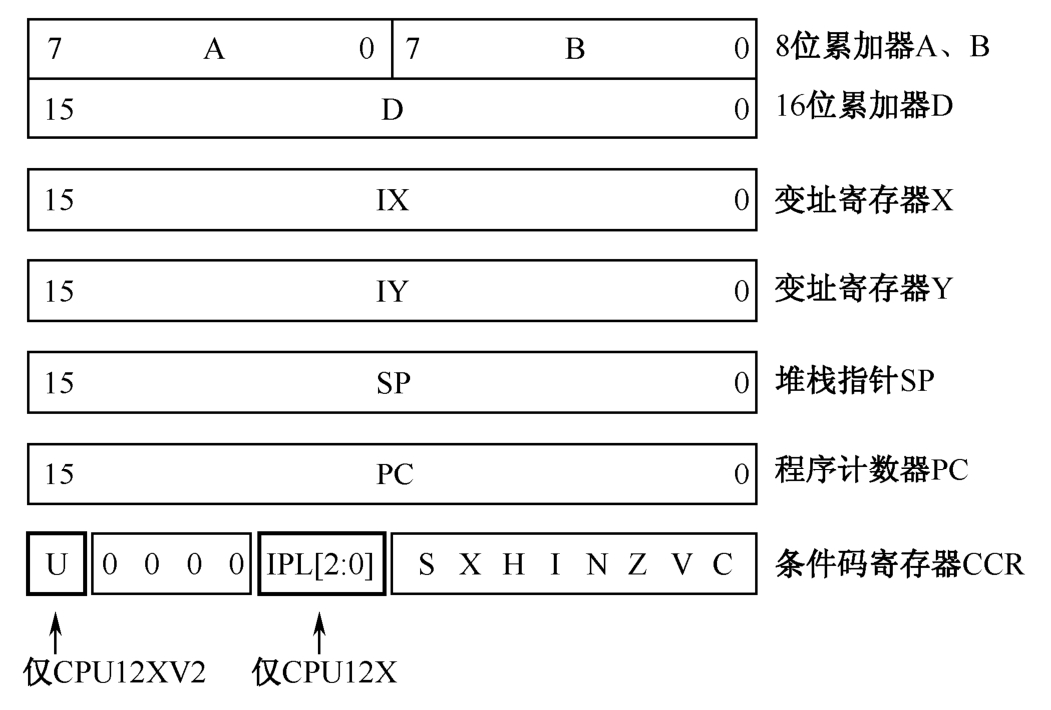

CPU12编程模型如图2.14所示。

图2.14 CPU12编程模型

CPU12编程模型包括:

● 2个8位通用累加器(A和B);对某些指令,这两个8位累加器可组合为一个16位累加器D;

● 2个变址寄存器X和Y;

● 16位堆栈指针SP;

● 16位程序计数器PC;

● 8位条件码寄存器CCR。

CPU12X编程模型在CPU12模型的CCR寄存器中增加了一个高8位条件码寄存器CCRH。CPU12X编程模型的CCR寄存器中增加的内容为:

● CPU12X为16位条件码寄存器CCRW(CCRH:CCRL);

● CPU12XV2在CCRH寄存器中增加了用户位。

1.累加器(Accumulator)A、B

累加器A、B是8位通用寄存器,用于存放操作数和运算结果。读取数据时,累加器A、B用于存放从存储器读出的数据;写入数据时,累加器A、B用于存放准备写入存储器的数据。执行算术、逻辑操作时,累加器首先存放一个操作数;执行完毕时,累加器存放操作结果。累加器A、B是指令系统中最灵活的寄存器,各种寻址方式均可对其寻址。复位时,累加器中的内容不受影响。有些指令将累加器A、B组合为一个16位累加器D使用。绝大多数指令都可使用累加器A或B,但也有一些特殊指令A和B不能交换使用(如ABA、SBA、CBA和DAA等),必须使用指定的累加器。

2.变址寄存器(Index Register)X、Y

CPU12内部有两个16位地址寄存器X和Y,称为间接寻址寄存器,简称间址寄存器或变址寄存器。一般情况下作为指针寄存器,用于多种寻址方式下的地址计算,也可用于临时存放数据或参与一些运算,只能按照16位方式访问。CPU12中,这两个变址寄存器可交替使用,而不会降低执行速度或增加程序长度。

汇编语言中,这两个寄存器进一步简称为寄存器X和寄存器Y。数据块传送时,X和Y寄存器都可自动加、减1~16,X寄存器常作为源地址指针,Y寄存器常作为目的地址指针,故X和Y寄存器有时也称做指针寄存器。

当指令具有一个以上16位数值作为其结果时,变址寄存器也可当做累加器使用。由于CPU12的通用数据寄存器较少,因此,乘法运算时需要X参与,除法运算时需要X、Y同时参与。仅有的两条特殊的8位与16位相加指令为B与X或Y相加,结果分别放在X、Y中,实际上它们已经演变成有效地址加载指令。此外,X、Y不再参与其他的算术运算。例如,不存在X、Y与存储器字之间的加、减法运算,也没有X、Y与A或D之间的加、减法运算。复位时X、Y均为$0000。

3.堆栈指针(Stack Pointer,SP)

堆栈是在内存中专门开辟出来的、按照“先进后出,后进先出”原则进行存取的区域。堆栈指针SP是指向下一个栈地址的16位寄存器。堆栈指针作为8位或者16位的偏移量寻址中,SP充当变址寄存器功能,CPU利用SP的内容来确定操作数的地址。

4.程序计数器(Program Counter,PC)

16位程序计数器的内容决定了程序的执行顺序,用户可以读取,但不能直接写入。因为要自动寻址复位矢量,复位后PC自动回到默认状态。

CPU12工作时,PC始终指向指令序列中下一条要执行的指令,分支、调用或转移指令均能改变PC值。PC是特殊寄存器,决定CPU的取指地址,因此不能挪作他用,但可以像SP一样,在大多数变址寻址方式下作为变址寄存器,只是不能用于自动增减地址的变址寻址操作。

PC主要为CPU服务,不能参与任何运算,但可辅助进行变址寻址操作。

5.条件码寄存器(Condition Code Register,CCR)

以下主要介绍CCR寄存器中的低8位。低8位包括两部分,一是5个算术特征位即标志位(Arithmetic Flag Bit)H、N、Z、V、C,反映上一条指令执行结果的特征(状态);二是3个MCU控制位,即中断屏蔽位X和I以及STOP指令控制位,通常由软件设定,以控制CPU行为。复位后,X、I均为1,即屏蔽系统中断。

除C、H位,其他各位不参与运算,各位含义简要说明如下。

C:进位/借位标志(Carry/Borrow Flag)。当加法运算产生进位或减法运算产生借位时,则C=1,否则,C=0。乘法、除法、移位操作或C语言相关指令都会改变C的值。

V:溢出标志(Overflow Flag)。算术运算后,若出现2补码(Two's-Complement)溢出时,则V=1;若无溢出,V=0。

Z:零标志(Zero Flag)。当运算结果为0时,则Z=1;结果不为0时,Z=0。算术或逻辑运算后,或者比较、加载、存入操作后,若操作结果为0,则Z=1。

N:符号位(负标志)(Negative Flag)。当运算结果为负时,则N=1。N位表示运算结果最高位,算术或逻辑运算后,或者比较、加载、存入操作后,将N置为最高位。N位主要用在二进制补码运算中,负数的最高位是1,正数的最高位是0。当运算结果最高位是1时,则N=1。N标志也可用作标志位,例如,如果用寄存器或存储器存储单元最高位作为一个状态,用户可通过加载累加器测试N位,以决定程序分支。

H:辅助进位(半进位)标志(Half-carry Flag)。加法过程中,若累加器A中的第3位向第4位产生进位,则H=1;否则,H=0。H位仅仅由累加器A和B的加法指令ABA、不带进位加法指令ADD和带进位加法指令等改变。H标志位主要用于BCD码运算,十进制调整指令DAA利用H标志位将累加器A中的结果调整为BCD码。

I:可屏蔽中断位(Maskable Interrupt Bit)。I位是全局中断屏蔽控制位(global interrupt mask),用于禁止或允许所有可屏蔽中断源,这些中断源包括外部中断和片内中断请求。当I=1时,禁止可屏蔽中断请求;当I=0时,允许可屏蔽中断请求。复位时I=1,进入中断服务程序时,该位自动置位。为了允许可屏蔽中断请求,该位必须软件清零。当I=1时,产生的可屏蔽中断请求被挂起并记忆,直到该位被清除。当I=0时,若产生可屏蔽中断请求,则CPU将I位状态压入堆栈,然后自动置位I,以阻止中断服务期间的其他可屏蔽中断请求。中断服务程序中的中断返回指令RTI将会自动恢复压入堆栈前的I位状态,重新允许可屏蔽中断请求。中断服务程序中I位也可清零,实现中断嵌套功能。

X:非屏蔽中断位(Non-maskable Interrupt Bit)。X位用于屏蔽来自引脚的外部中断请求。当X=1时,禁止外部中断请求;当X=0时,允许外部中断请求。非屏蔽中断的典型应用是处理系统故障,如掉电等意外情况。但系统在上电和初始化前,若允许非屏蔽中断,则可能会产生虚假中断。复位时X=1。为了允许引脚的外部中断服务请求,该位必须软件清零。X位一旦被清零,则不能通过软件重新置位X,除非复位才能再次置位X。

S:STOP指令屏蔽位(STOP Mask Bit)。S位用于禁止CPU执行STOP指令。当S=1时,禁止执行STOP指令;当S=0时,允许执行STOP指令。STOP指令将关闭MCU时钟信号,振荡器停止工作,MCU处于低功耗工作模式。若该位置1,若遇到STOP指令,则作为NOP指令处理。复位时S=1。