Freescale公司于2005年推出HCS12X系列单片机,该系列是HCS12系列的增强型产品,基于S12 CPU内核,可以达到25 MHz的HCS12的2~5倍的性能。S12X系列增加了172条指令,可以执行32位运算,总线频率最高可达40 MHz,并且改进了中断处理能力。

S12X系列单片机采用复杂指令集计算机(CISC)架构,集成了中断控制器,具有丰富的寻址方式。中断有7个优先级,并且内核支持优先级的调度,最多可以有117个中断源。

S12X系列单片机的最大特点是增加了一个并行处理的外围协处理器XGATE模块,它是一个独立于主处理器(S12XD)的可编程RISC内核。XGATE可作为一个高效的DMA控制器使用,能够自主地实现外设与RAM之间的高速数据传输,并在数据传送过程中灵活进行数据处理;XGATE也可作为一个单独的算法单元完成运算功能,如通信协议的实现;XGATE还可作为虚拟外设使用,如使用通用I/O口模拟串行通信口功能,或对简单的外设通过软件包装实现功能强大的个性化外设功能等。集成XGATE的目的就是在日益复杂的嵌入式系统中,减轻S12XD主处理器的负担,以增强系统的数据吞吐能力和应用功能设计的灵活性。

S12X系列单片机与S12系列单片机的主要区别如表2-2所示。

表2-2 S12X系列单片机与S12系列单片机的主要区别

XGATE模块大大提高了MCU处理应用程序的能力。通过承担中断源处理功能,从而降低了主处理器的负担,使得中断服务程序能够在XGATE中处理的同时,主处理器可以并行的处理其他应用程序。通过表2-2的比较,可以近似地认为S12X核的性能是S12的5倍。

在S12X系列中,中断控制器硬件产生的中断可以选择由XGATE或者S12XD主处理器来处理。XGATE对于任何中断的处理都会减轻主处理器的中断负荷,并且XGATE完全有能力响应整个中断。

从图2.1中可以看到,一个开关中断信号可以指向XGATE或者主处理器,如果指向XGATE,它就会执行所响应的中断服务程序;当程序执行完成后,等待下一个中断请求。另外有的寄存器可以使XGATE指向特殊的中断信号,并且中断优先级的等级可以设置为7个级别之一。如果有两个中断请求同时产生,则处理器就会根据中断级别的优先级高低来判断,优先级高的中断首先执行。这些中断等级在S12XD主处理器和XGATE中相同。

XGATE和主处理器完全一样,是一个支持C编译器的可编程内核。当中断源产生时,它开始运行;在完成中断任务以后,它会中止时钟工作等待下次事件发生,以降低功耗。

XGATE与主处理器之间可相互中断以进行同步。XGATE有一个特殊指令SIF,用于向主处理器提交中断。通常SIF为XGATE线程的最后一条指令,用以触发主处理器中断。在默认情况下,此时XGATE的中断矢量就对应于此前XGATE所处理的中断,故由SIF所触发的主处理器的中断服务程序通常不必查询中断源。

XGATE是一个协处理器,它可以直接使用,几乎可以直接进入所有的存储空间。XGATE的创新特点就在于它以独特的方式访问MCU内部RAM单元,通过交换总线功能,MCU的内部总线允许交叉进入RAM区。当主处理器全速执行时,它访问RAM只需半个时钟总线周期,XGATE可以在另外半个时钟总线周期访问RAM。若主处理器不进入访问RAM的周期内,则XGATE访问RAM的速度就会是主处理器访问RAM最高速度的两倍。

另外,XGATE有8个软件中断源。主处理器通过置位或清除XGATE的软件触发寄存器(XGSWT)中相应的位来触发或清除这8个中断源。需要注意的是,由于XGSWT属于片上外设寄存器,所以XGATE也可以通过XGSWT的位设置向自己发出中断信号。

图2.1 使用主处理器或者XGATE的中断响应过程

XGATE协处理器结构如图2.2所示,它具有以下基本特征。

图2.2 XGATE协处理器结构

XGATE是一个16位的精简指令集内核。内核拥有8个16位通用寄存器R0~R7,1个程序计数器PC,1个4位的条件码寄存器CCR。其中R0恒为0,可用于对变量的快速清零或置位。R1和R7有额外用途:XGATE响应中断时,硬件将中断向量表中对应通道的1个16位字装载到R1(通常用做数据指针),将栈指针装载到R7,如图2.3所示。

图2.3 XGATE编程模式

XGATE共有72条独立的指令,指令时钟最高可达100 MHz。XGATE的时钟速度总是主处理器总线速度的2倍。XGATE的大部分指令是对通用寄存器的操作,为单周期指令。访问存储器的指令为双周期指令。跳转指令视条件而定可能为1或2个周期指令。XGATE有一些特殊的比特提取及插入的单周期指令,特别适用于串行通信协议使用。

S12X的全局存储空间共有8 MB,XGATE可以访问其中片内的64 KB空间。这64 KB空间包括2 KB的片上外设寄存器,30 KB的片上闪存和最大32 KB的片内RAM。注意XGATE不能访问EEPROM空间或片外资源。XGATE的访问空间完全限制在主处理器内部访问空间范围内。地址仲裁的规则是主处理器的优先级总高于XGATE,如图2.4所示。

图2.4 XGATE全局地址映射图

XGATE的代码执行是由事件驱动的,这里的事件就是指中断。所谓事件驱动就是指由中断来触发XGATE运行。没有中断时,XGATE不执行任何指令,从而也没有功耗。可见XGATE的代码就是一组中断服务程序,没有主程序或空闲时的循环程序。XGATE的中断服务程序也称做线程。

主处理器与XGATE之间常用的通信方式是共享资源。由于这两个内核可以独立异步的访问内存及片上外设,就会产生数据完整性问题。为了保证共享数据的完整性,XGATE集成了8个硬件互斥信号量(Semaphore)。用户可以通过硬件信号量来同步两个内核对共享数据的访问。信号量有3种状态:释放、主处理器锁定和XGATE锁定。每个内核在访问共享资源前,应当首先锁定相应的信号量;在访问结束后应当释放相应的信号量。

相比于S12系列单片机而言,S12X系列单片机的型号目前还是较少的,S12X系列单片机目前有以下几个子系列:MC9S12XA系列、MC9S12XB系列、MC9S12XD系列、MC9S12XE系列、MC9S12XF系列、MC9S12XH系列和MC9S12XS系列。下面简要介绍几个子系列单片机的各自特点。

这三个系列的单片机是以低成本和低功耗为目的设计的,具有良好的电磁兼容性和高效的代码执行效率。MC9S12XA系列主要包括MC9S12XA256和MC9S12XA512两种型号的单片机,其中MC9S12XA512包含外部总线接口EBI,模块映像控制MMC功能,中断控制器INT,用于监控HCS12X CPU和XGATE总线活动的调试模块DBG和背景调试模式BDM功能,具有两个A/D模块,每个为12通道10位分辨率,具有4个独立暂停期限的定时器PIT,暂停期限可以在1~224总线时钟周期之间选择,同时还有CRG模块,具有低噪声/低功耗皮尔斯(Pierce)振荡器、PLL、COP监视器、实时中断、时钟监控器等功能。

MC9S12XB系列目前主要包括MC9S12XB128和MC9S12XB256两种型号的单片机。它们的总线频率均为33 MHz,该系列单片机与MC9S12XD系列单片机完全兼容,相比于S12XD系列而言,S12XB系列单片机精简了一些功能,并通过降低总线速率来减少成本。

MC9S12XE系列单片机与MC9S12XD系列单片机完全兼容,同时提高了系统的集成功能。MC9S12XE系列单片机工作频率为50 MHz,工作电压为3.3~5.5 V,包括一个存储器保护单元(MPU),用于防止软件执行过程中的系统错误。此外XGATE也得到了加强,频率可以达到100 MHz,同时与其他单片机上的XGATE模块也是兼容的。

MC9S12XF系列单片机除了包括其他一些S12X的共有功能外,还具有1个符合FlexRay协议V2.1的FlexRay控制器,FlexRay技术的引入使其网络性能得到大幅提升,FlexRay网络可用于车身、底盘和安全等领域应用。该系列目前主要包括MC9S12XFE128和MC9S12XFR128两种型号的单片机,工作频率可以达到38 MHz。

MC9S12XS系列单片机是高性能MC9S12XE系列单片机的经济性、高效性产品的补充,带有一套为汽车车身和乘客舒适度应用而优化设计的改进型片上外围设备、存储器等模块,可应用于汽车坐椅控制模块、空调控制模块、各种车身控制模块等的设计应用。

MC9S12XS128只是S12X家族中的一个成员。该器件包括大量的片上存储器和外部I/O。MC9S12XS128是一个16位器件,由16位中央处理单元(CPU12X)、128 KB程序Flash(P-Flash)、8 KB RAM、8 KB数据Flash(D-Flash)组成片内存储器。同时还包括2个异步串行通信接口(SCI)、1个串行外设接口(SPI)、1个8通道输入捕捉/输出比较(IC/OC)定时器模块(TIM)、16通道12位A/D转换器(ADC)和一个8通道脉冲宽度调制模块(PWM)。

MC9S12XS128具有91个独立的数字I/O口,其中某些数字I/O口具有中断和唤醒功能。另外还具有1个CAN 2.0A/B标准兼容模块(MSCAN)。

MC9S12XS128有3种封装,分别是64引脚封装、80引脚封装和112引脚封装。图2.5为MC9S12XS128的内部结构框图,其中功能模块是按照112引脚封装给出的;图2.6为MC9S12XS128的112引脚封装图;图2.7为MC9S12XS128的80引脚封装图。

MC9S12XS128主要特性包括:

● 16位CPU 12X。

● INT(中断模块)。

✧ 嵌套的7级中断;

✧ 每个中断源可以灵活配置中断级别;

✧ 外部非屏蔽高优先级中断(XIRQ)。

● 系统完整性特性。

✧ 上电复位(POR);

✧ 非法地址检测复位;

✧ 低电压检测中断或复位;

✧ COP看门狗;

✧ 时钟监视功能。

● 内部存储器。

✧ 128 KB程序Flash;

✧ 8 KB RAM;

✧ 8 KB数据Flash。

● 内部PLL模块。

✧ 不需要外部元件;

✧ 可配置的选项,以降低EMC辐射(频率调制)。

● 时钟和复位发生器(CRG)。

✧ COP看门狗

图2.5 MC9S12XS128内部结构框图

图2.6 MC9S12XS128的112引脚封装图

图2.7 MC9S12XS128的80引脚封装图

✧ 实时中断;

✧ 时钟监控;

✧ 停止模式下的快速唤醒;

✧ 产生系统复位。

● 模/数转换器(ATD)。

✧ 8位/10位/12位分辨率可选;

✧ 3μs的10位单通道转换时间;

✧ 左对齐/右对齐数据转换;

✧ 外部和内部转换触发功能;

✧ 停止模式下为转换提供内部时钟;

✧ 连续转换模式;

✧ 16个模拟输入通道;

✧ 多通道扫描;

✧ 引脚能够用于数字I/O口。

● 定时器模块(TIM)。

✧ 8通道16位输入捕捉和输出比较功能;

✧ 16位计数器,8位精度预分频器;

✧ 1个16位脉冲累加器。

● 周期中断定时器(PIT)。

✧ 4通道24位模数递减计数器;

✧ 可产生超时中断;

✧ 可用超时触发外设;

✧ 定时器起始通道调整。

● 脉冲宽度调制器(PWM)。

✧ 最多提供8通道8位或者4通道16位的脉冲宽度调制器;

✧ 每个通道可以单独编程设置周期和占空比;

✧ 可设置输出信号中央对齐或者左对齐;

✧ 可编程时钟选择,宽范围时钟频率。

● MSCAN模块。

✧ 可达1 Mbps通信速率,兼容CAN2.0 A和CAN2.0 B;

✧ 5个可配置FIFO接收缓冲区;

✧ 3个内部优先级发送缓冲区;

✧ 可编程选择2×32位、4×16位或8×8位的标识符接收滤波器;

✧ 低通滤波器唤醒;

✧ 环路自检功能;

✧ 侦听模式监测CAN总线状态;

✧ 软件激活或自动唤醒总线关闭功能;

✧ 16位发送/接收报文的时间标签。

● 串行外设接口模块(SPI)。

✧ 可配置8位或16位数据长度;

✧ 全双工或单线双向模式;

✧ 双缓冲的发送和接收功能;

✧ 主机模式或从机模式;

✧ 先移位MSB或LSB功能;

✧ 串行时钟相位和极性可选。

● 串行通信接口(SCI)。

✧ 2个全双工或单线工作方式;

✧ 标准不归零(NRZ)传号/空号数据格式;

✧ 可编程脉冲宽度的IrDA 1.4归零反转(RZI)格式;

✧ 13位波特率选择;

✧ 可编程的字符长度;

✧ 可编程的发送器和接收器极性;

✧ 边沿有效接收唤醒;

✧ 支持LIN的间隔检测和发送冲突检测。

● 输入/输出端口特性。

✧ 最多91个通用I/O口引脚和2个专用输入口引脚;

✧ 可配置输入引脚上拉或下拉电阻;

✧ 可配置输出引脚驱动能力。

● 外围设备。

✧ 2个增强型串行通信接口模块(SCI);

✧ 2个串行外设接口模块(SPI);

✧ 2个MSCAN模块;

✧ I 2 C总线接口模块;

✧ 2个8通道10位AD;

✧ 8通道16位增强型捕捉定时器(ECT);

✧ 8通道8位或4通道16位PWM。

MC9S12XS系列具有非常丰富的输入/输出端口资源,同时集成了多种功能模块,端口包括PORTA、PORTB、PORTE、PORTK、PORTT、PORTS、PORTM、PORTP、PORTH、PORTJ和PORTAD共11个端口。端口引脚大多为复用引脚,往往具有多重功能,所有端口都具有通用I/O口功能。其中PORTA、PORTB和PORTK作为通用I/O口;PORTE中的

和

和

引脚可作为外部中断输入口;PORTT集成了TIM模块功能;PORTS集成了SCI模块和SPI模块功能;PORTM集成了CAN总线模块;PORTP集成了PWM模块功能;PORTH和PORTJ可作为外部中断输入口;PORTAD集成了ATD模块功能。

引脚可作为外部中断输入口;PORTT集成了TIM模块功能;PORTS集成了SCI模块和SPI模块功能;PORTM集成了CAN总线模块;PORTP集成了PWM模块功能;PORTH和PORTJ可作为外部中断输入口;PORTAD集成了ATD模块功能。

以112引脚MC9S12XS128为例,其引脚功能说明参见表2-3,其中所有电源引脚功能在后文中详细介绍,详细功能说明请参考MC9S12XS128数据手册。

表2-3 MC9S12XS128引脚功能说明

(续表)

(续表)

(续表)

(续表)

注意: 表2-3中有些特殊功能可定义为多个引脚,如SCI1的TXD1可定义PS3引脚,或PM1引脚,或PP2引脚;SCI1的RXD1可定义PS2引脚,或PM0引脚,或PP0引脚。对于这些具有相同功能的引脚定义,由PIM模块中的端口T路径寄存器PTTRR和模块路径寄存器MODRR确定。

端口T路径寄存器(Port T Routing Register,PTTRR)确定PWM和TIM相应通道的引脚定义,如图2.8所示。

图2.8 端口T路径寄存器

PTTRR7:PTTRR7位确定通道PWM7的引脚定义。

● 0表示PWM7对应引脚为PP7;

● 1表示PWM7对应引脚为PT7。

PTTRR6:PTTRR6位确定通道PWM6的引脚定义。

● 0表示PWM6对应引脚为PP6;

● 1表示PWM6对应引脚为PT6。

PTTRR5:PTTRR5位确定通道PWM5的引脚定义。

● 0表示PWM5对应引脚为PP5;

● 1表示PWM5对应引脚为PT5。

PTTRR4:PTTRR4位确定通道PWM4的引脚定义。

● 0表示PWM4对应引脚为PP4;

● 1表示PWM4对应引脚为PT4。

PTTRR2:PTTRR2位确定TIM通道2的引脚定义。

● 0表示IOC2对应引脚为PT2;

● 1表示IOC2对应引脚为PP2。

PTTRR1:PTTRR1位确定TIM通道1的引脚定义。

● 0表示IOC1对应引脚为PT1;

● 1表示IOC1对应引脚为PP1。

PTTRR0:PTTRR0位确定TIM通道0的引脚定义。

● 0表示IOC0对应引脚为PT0;

● 1表示IOC0对应引脚为PP0。

由PTTRR寄存器复位值可知,MC9S12XS128上电复位后,若不配置该寄存器,则PWM7~PWM4默认为引脚PP7~PP4,IOC2~IOC0默认为引脚PT2~PT0。

模块路径寄存器(Module Routing Register,MODRR)确定SCI1和SPI0相应引脚定义,如图2.9所示。

图2.9 模块路径寄存器

MODRR寄存器中的MODRR7和MODRR6两位确定SCI1模块引脚定义,MODRR4确定SPI0模块引脚定义。具体引脚定义说明参见表2-4和表2-5。

表2-4 SCI1模块引脚定义

表2-5 SPI0模块引脚定义

由MODRR寄存器复位值知道,MC9S12XS128上电复位后,若不配置该寄存器,则SCI1模块默认使用引脚PS3和PS2,SPI0模块默认使用引脚PS4~PS7。

PIM模块功能及其他寄存器的介绍详见本书第5章。

本节以112引脚MC9S12XS128为例介绍部分引脚功能及参考电路设计。

1.XTAL和EXTAL(47、46)——振荡器引脚

XTAL和EXTAL分别是晶体驱动输出和外部时钟输入引脚。EXTAL引脚既可以接晶振,也可以接外部COMS兼容的时钟信号,驱动内部时钟发生电路,器件中所有的时钟信号都来自该引脚输入的时钟。XTAL引脚为晶体驱动输出,当EXTAL引脚外接时钟信号时,XTAL引脚悬空。时钟电路的几种接法如图2.10、图2.11和图2.12所示。

输入引脚控制时钟由晶体和Pierce振荡器电路提供还是外部时钟电路提供。

输入引脚控制时钟由晶体和Pierce振荡器电路提供还是外部时钟电路提供。

图2.10 内部闭环控制Pierce振荡器连接(

=1)

=1)

图2.11 全摆幅Pierce振荡器连接(

=0)

=0)

图2.12 外部时钟连接(

=0)

=0)

2.

(42)——外部复位引脚

(42)——外部复位引脚

引脚是一个低电平有效的双向控制信号。该引脚做输入时,将其拉低,可将MCU初始化成一个已知的起始状态。当任何MCU内部复位源触发时,该引脚输出低电平对外指示这种状态。

引脚是一个低电平有效的双向控制信号。该引脚做输入时,将其拉低,可将MCU初始化成一个已知的起始状态。当任何MCU内部复位源触发时,该引脚输出低电平对外指示这种状态。

引脚内部上拉。

引脚内部上拉。

3.BKGD/MODC(23)——背景调试和模式引脚

对于背景调试通信而言,该引脚是一个伪漏极开路引脚。在复位期间,该引脚用于选择MCU操作模式。

的上升沿,将该引脚的状态锁存保持在MODC位。该引脚内部上拉。BKGD采用自定义协议接收串行的背景调试命令,发送命令执行结果,实现实时在线调试功能。Freescale定义的标准BDM调试插头如图2.13所示。

的上升沿,将该引脚的状态锁存保持在MODC位。该引脚内部上拉。BKGD采用自定义协议接收串行的背景调试命令,发送命令执行结果,实现实时在线调试功能。Freescale定义的标准BDM调试插头如图2.13所示。

图2.13 标准BDM调试插头

4.PE7/ECLKX2/

(36)——端口E输入/输出引脚7

(36)——端口E输入/输出引脚7

PE7定义为通用输入/输出引脚。ECLKX2定义为时钟输出引脚,输出频率是内部总线频率的2倍。

定义为输入信号,它用于控制使用晶振与内部闭环控制Pierce振荡器电路,还是晶振与全摆幅Pierce振荡器电路,还是外部时钟电路。

定义为输入信号,它用于控制使用晶振与内部闭环控制Pierce振荡器电路,还是晶振与全摆幅Pierce振荡器电路,还是外部时钟电路。

具体应用设置详见图2.10、图2.11和图2.12。在复位期间,该引脚内部上拉。

具体应用设置详见图2.10、图2.11和图2.12。在复位期间,该引脚内部上拉。

5.

(55)——可屏蔽中断请求

(55)——可屏蔽中断请求

PE1可定义为通用输入引脚或可屏蔽外部中断输入

引脚。

引脚。

信号可从停止(STOP)或等待(WAIT)模式下唤醒MCU。该引脚通过软件设置是否和中断逻辑连接,

信号可从停止(STOP)或等待(WAIT)模式下唤醒MCU。该引脚通过软件设置是否和中断逻辑连接,

可选择下降沿或低电平触发。复位后,

可选择下降沿或低电平触发。复位后,

默认为低电平触发中断方式,当CCR寄存器中的I位为1时,

默认为低电平触发中断方式,当CCR寄存器中的I位为1时,

中断被屏蔽。通过软件清除或者置位CCR寄存器中的I位使能或禁止所有可屏蔽中断。

中断被屏蔽。通过软件清除或者置位CCR寄存器中的I位使能或禁止所有可屏蔽中断。

6.

(56)——非屏蔽中断请求

(56)——非屏蔽中断请求

PE0可定义为通用输入引脚或非屏蔽外部中断输入

引脚。

引脚。

信号可在停止(STOP)或等待(WAIT)模式下唤醒MCU。

信号可在停止(STOP)或等待(WAIT)模式下唤醒MCU。

是低电平触发中断方式。当

是低电平触发中断方式。当

引脚低电平时,MCU无法进入停止(STOP)模式。在复位期间,当CCR寄存器中的X位为1时,非屏蔽中断被屏蔽。系统初始化程序后,可通过软件清除CCR寄存器中的X位,使能非屏蔽中断。

引脚低电平时,MCU无法进入停止(STOP)模式。在复位期间,当CCR寄存器中的X位为1时,非屏蔽中断被屏蔽。系统初始化程序后,可通过软件清除CCR寄存器中的X位,使能非屏蔽中断。

注意: X位一旦被清零,就不能再通过软件的方式置1。非屏蔽中断经常用于处理系统掉电或者硬件故障等特殊应用要求。

关于中断及复位的论述,后文相关章节会有详细的论述。

7.电源相关引脚

MC9S12XS128的电源引脚汇总参见表2-6。

表2-6 MC9S12XS128的电源引脚汇总

为I/O口驱动提供外部电源和地。所有VDDX引脚内部连接,所有VSSX引脚内部连接。

VDDR和VSSR两个电源引脚之间需要外接一个旁路电容(100~220 nF),并为内部电压调节器供电。

内核电源额定1.8 V供电电压由内部电压调节器提供,允许没有静态外部负载。

NVM电源额定2.8 V供电电压由内部电压调节器提供,允许没有静态外部负载。

这些引脚为A/D转换器提供工作电源,同时为内部电压调节器提供参考电源。

VRH和VRL是A/D转换器的参考电压输入和地引脚。

这些引脚为振荡器和锁相环提供工作电压和地。PLL工作电源额定1.8 V供电电压由内部电压调节器提供,允许没有静态外部负载。

CPU12是一款高速16位中央处理单元(Central Processing Unit,CPU),与68HC11中央处理单元CPU11具有相同的编程模型。CPU12指令集是对68HC11指令集的扩展,68HC11程序无须修改可在CPU12运行。CPU12X指令集是对CPU12指令集的扩展,CPU12程序无须修改可在CPU12X执行,但CPU12X不支持CPU12的模糊指令集。

CPU12(X)内核主要有以下特性:

● 16位数据宽度支持高效算术运算和高速数学计算;

● 支持多字节指令,包括大量单字节指令,能更有效利用ROM空间;

● CPU12X指令运行效率更高。CPU12X能够在指令队列缓冲区中,立即存取至少3个字节的机器码;

● 强大的变址寻址能力,包括:

✧ 堆栈指针作为变址寄存器寻址;

✧ 程序计数器作为变址寄存器寻址;

✧ A、B或D累加器偏移量寻址;

✧ 自动先递增或先递减、后递增或后递减变址寻址。

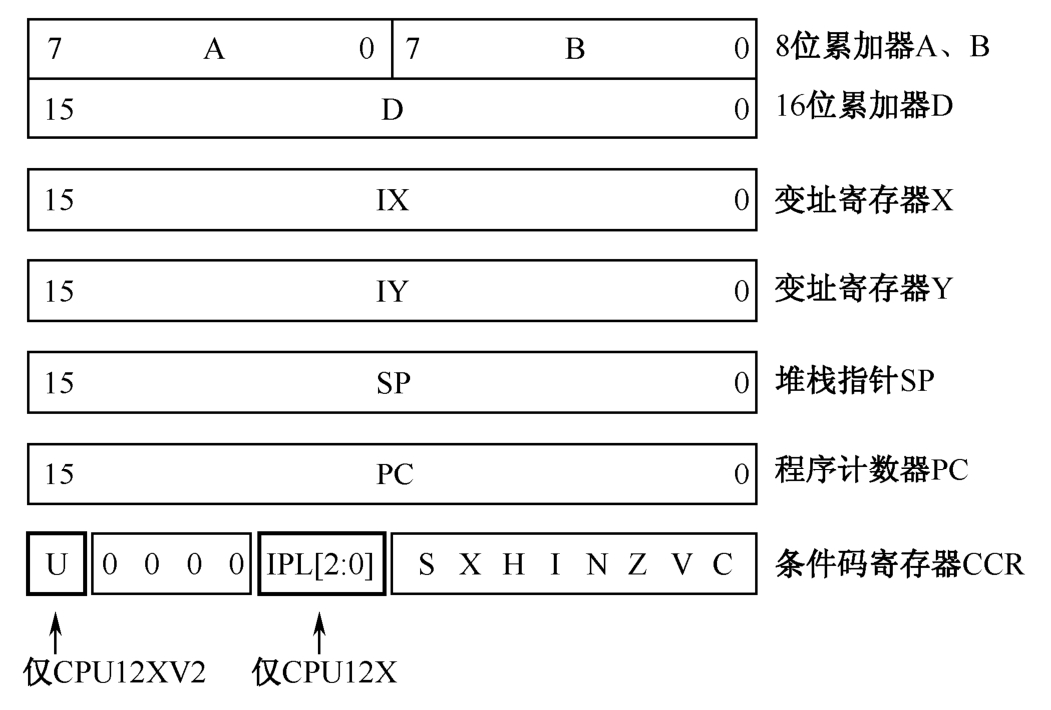

CPU12编程模型如图2.14所示。

图2.14 CPU12编程模型

CPU12编程模型包括:

● 2个8位通用累加器(A和B);对某些指令,这两个8位累加器可组合为一个16位累加器D;

● 2个变址寄存器X和Y;

● 16位堆栈指针SP;

● 16位程序计数器PC;

● 8位条件码寄存器CCR。

CPU12X编程模型在CPU12模型的CCR寄存器中增加了一个高8位条件码寄存器CCRH。CPU12X编程模型的CCR寄存器中增加的内容为:

● CPU12X为16位条件码寄存器CCRW(CCRH:CCRL);

● CPU12XV2在CCRH寄存器中增加了用户位。

1.累加器(Accumulator)A、B

累加器A、B是8位通用寄存器,用于存放操作数和运算结果。读取数据时,累加器A、B用于存放从存储器读出的数据;写入数据时,累加器A、B用于存放准备写入存储器的数据。执行算术、逻辑操作时,累加器首先存放一个操作数;执行完毕时,累加器存放操作结果。累加器A、B是指令系统中最灵活的寄存器,各种寻址方式均可对其寻址。复位时,累加器中的内容不受影响。有些指令将累加器A、B组合为一个16位累加器D使用。绝大多数指令都可使用累加器A或B,但也有一些特殊指令A和B不能交换使用(如ABA、SBA、CBA和DAA等),必须使用指定的累加器。

2.变址寄存器(Index Register)X、Y

CPU12内部有两个16位地址寄存器X和Y,称为间接寻址寄存器,简称间址寄存器或变址寄存器。一般情况下作为指针寄存器,用于多种寻址方式下的地址计算,也可用于临时存放数据或参与一些运算,只能按照16位方式访问。CPU12中,这两个变址寄存器可交替使用,而不会降低执行速度或增加程序长度。

汇编语言中,这两个寄存器进一步简称为寄存器X和寄存器Y。数据块传送时,X和Y寄存器都可自动加、减1~16,X寄存器常作为源地址指针,Y寄存器常作为目的地址指针,故X和Y寄存器有时也称做指针寄存器。

当指令具有一个以上16位数值作为其结果时,变址寄存器也可当做累加器使用。由于CPU12的通用数据寄存器较少,因此,乘法运算时需要X参与,除法运算时需要X、Y同时参与。仅有的两条特殊的8位与16位相加指令为B与X或Y相加,结果分别放在X、Y中,实际上它们已经演变成有效地址加载指令。此外,X、Y不再参与其他的算术运算。例如,不存在X、Y与存储器字之间的加、减法运算,也没有X、Y与A或D之间的加、减法运算。复位时X、Y均为$0000。

3.堆栈指针(Stack Pointer,SP)

堆栈是在内存中专门开辟出来的、按照“先进后出,后进先出”原则进行存取的区域。堆栈指针SP是指向下一个栈地址的16位寄存器。堆栈指针作为8位或者16位的偏移量寻址中,SP充当变址寄存器功能,CPU利用SP的内容来确定操作数的地址。

4.程序计数器(Program Counter,PC)

16位程序计数器的内容决定了程序的执行顺序,用户可以读取,但不能直接写入。因为要自动寻址复位矢量,复位后PC自动回到默认状态。

CPU12工作时,PC始终指向指令序列中下一条要执行的指令,分支、调用或转移指令均能改变PC值。PC是特殊寄存器,决定CPU的取指地址,因此不能挪作他用,但可以像SP一样,在大多数变址寻址方式下作为变址寄存器,只是不能用于自动增减地址的变址寻址操作。

PC主要为CPU服务,不能参与任何运算,但可辅助进行变址寻址操作。

5.条件码寄存器(Condition Code Register,CCR)

以下主要介绍CCR寄存器中的低8位。低8位包括两部分,一是5个算术特征位即标志位(Arithmetic Flag Bit)H、N、Z、V、C,反映上一条指令执行结果的特征(状态);二是3个MCU控制位,即中断屏蔽位X和I以及STOP指令控制位,通常由软件设定,以控制CPU行为。复位后,X、I均为1,即屏蔽系统中断。

除C、H位,其他各位不参与运算,各位含义简要说明如下。

C:进位/借位标志(Carry/Borrow Flag)。当加法运算产生进位或减法运算产生借位时,则C=1,否则,C=0。乘法、除法、移位操作或C语言相关指令都会改变C的值。

V:溢出标志(Overflow Flag)。算术运算后,若出现2补码(Two's-Complement)溢出时,则V=1;若无溢出,V=0。

Z:零标志(Zero Flag)。当运算结果为0时,则Z=1;结果不为0时,Z=0。算术或逻辑运算后,或者比较、加载、存入操作后,若操作结果为0,则Z=1。

N:符号位(负标志)(Negative Flag)。当运算结果为负时,则N=1。N位表示运算结果最高位,算术或逻辑运算后,或者比较、加载、存入操作后,将N置为最高位。N位主要用在二进制补码运算中,负数的最高位是1,正数的最高位是0。当运算结果最高位是1时,则N=1。N标志也可用作标志位,例如,如果用寄存器或存储器存储单元最高位作为一个状态,用户可通过加载累加器测试N位,以决定程序分支。

H:辅助进位(半进位)标志(Half-carry Flag)。加法过程中,若累加器A中的第3位向第4位产生进位,则H=1;否则,H=0。H位仅仅由累加器A和B的加法指令ABA、不带进位加法指令ADD和带进位加法指令等改变。H标志位主要用于BCD码运算,十进制调整指令DAA利用H标志位将累加器A中的结果调整为BCD码。

I:可屏蔽中断位(Maskable Interrupt Bit)。I位是全局中断屏蔽控制位(global interrupt mask),用于禁止或允许所有可屏蔽中断源,这些中断源包括外部中断和片内中断请求。当I=1时,禁止可屏蔽中断请求;当I=0时,允许可屏蔽中断请求。复位时I=1,进入中断服务程序时,该位自动置位。为了允许可屏蔽中断请求,该位必须软件清零。当I=1时,产生的可屏蔽中断请求被挂起并记忆,直到该位被清除。当I=0时,若产生可屏蔽中断请求,则CPU将I位状态压入堆栈,然后自动置位I,以阻止中断服务期间的其他可屏蔽中断请求。中断服务程序中的中断返回指令RTI将会自动恢复压入堆栈前的I位状态,重新允许可屏蔽中断请求。中断服务程序中I位也可清零,实现中断嵌套功能。

X:非屏蔽中断位(Non-maskable Interrupt Bit)。X位用于屏蔽来自引脚的外部中断请求。当X=1时,禁止外部中断请求;当X=0时,允许外部中断请求。非屏蔽中断的典型应用是处理系统故障,如掉电等意外情况。但系统在上电和初始化前,若允许非屏蔽中断,则可能会产生虚假中断。复位时X=1。为了允许引脚的外部中断服务请求,该位必须软件清零。X位一旦被清零,则不能通过软件重新置位X,除非复位才能再次置位X。

S:STOP指令屏蔽位(STOP Mask Bit)。S位用于禁止CPU执行STOP指令。当S=1时,禁止执行STOP指令;当S=0时,允许执行STOP指令。STOP指令将关闭MCU时钟信号,振荡器停止工作,MCU处于低功耗工作模式。若该位置1,若遇到STOP指令,则作为NOP指令处理。复位时S=1。