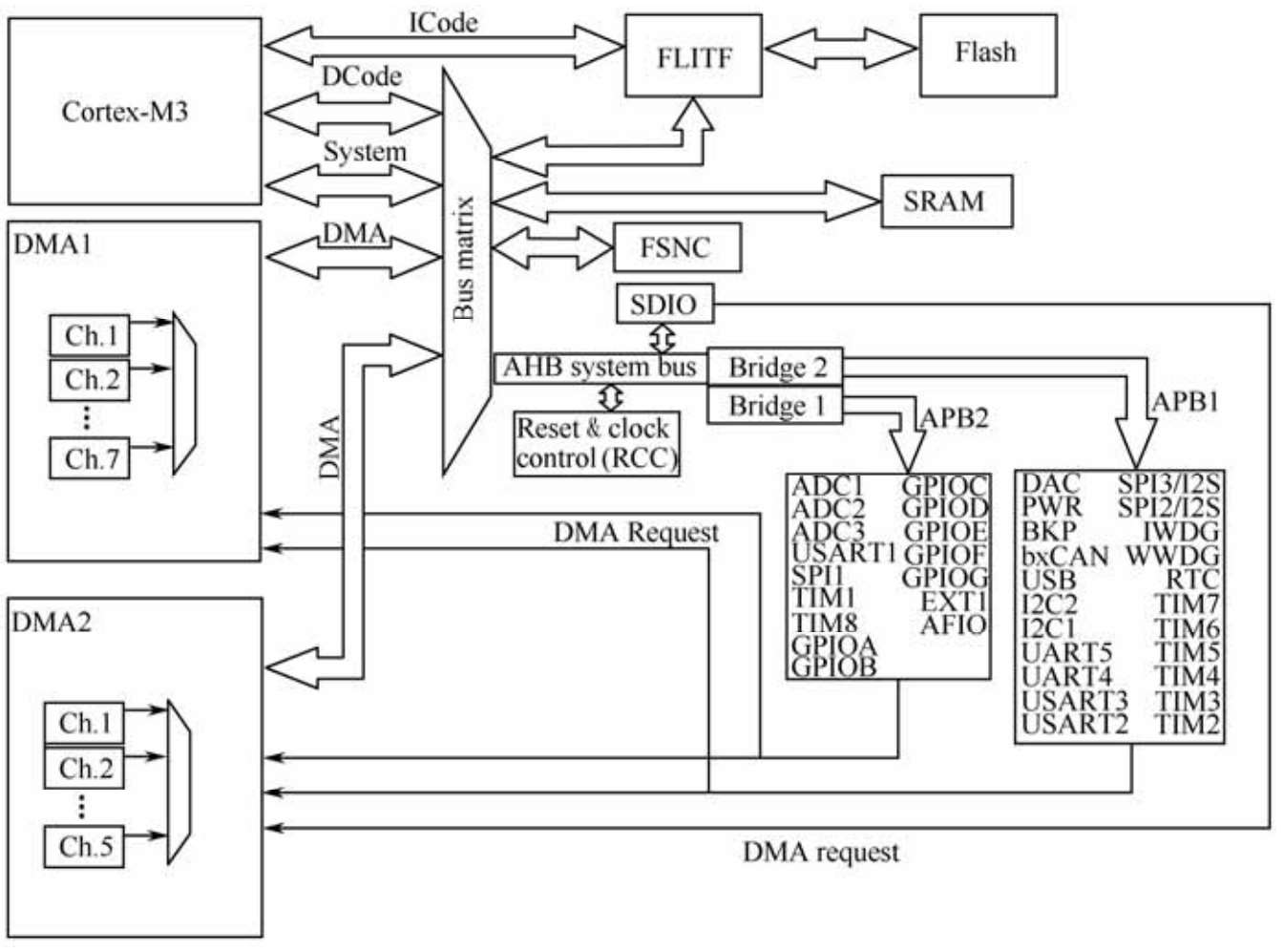

STM32系统结构框图如图3.7所示。系统框图的中心位置是总线矩阵,利用轮换算法,协调内核系统总线和DMA主控总线之间的访问仲裁。总线矩阵由4个驱动单元和4个被动单元构成。驱动单元包括Cortex™-M3内核DCode总线(D-bus)、系统总线(S-bus)、通用DMA1和通用DMA2。被动单元包括内部SRAM、内部闪存存储器、FSMC和AHB到APB的桥(AHB2APBx)。AHB2APBx用于连接所有的APB设备。AHB外设通过总线矩阵与系统总线相连,允许DMA访问。

图3.7 STM32系统结构框图

◆ ICode总线:将Cortex™-M3内核的指令总线与闪存指令接口相连接。指令预取在此总线上完成。

◆ DCode总线:将Cortex™-M3内核的DCode总线与闪存存储器的数据接口相连接(常量加载和调试访问)。

◆ 系统总线:连接Cortex™-M3内核的系统总线(外设总线)到总线矩阵,总线矩阵协调内核和DMA间的访问。

◆ DMA总线:将DMA的AHB主控接口与总线矩阵相连,总线矩阵协调CPU的DCode和DMA到SRAM、闪存和外设的访问。

◆ AHB/APB桥(APB):2个AHB/APB桥在AHB和2个APB总线间提供同步连接。APB1操作速度限于36MHz,APB2操作于全速(最高72MHz)。在每一次复位以后,所有除SRAM和FLITF以外的外设都被关闭,在使用一个外设之前,必须设置寄存器RCC_AHBENR来打开该外设的时钟。

当对APB寄存器进行8位或16位访问时,该访问会被自动转换成32位的访问——桥会自动将8位或32位的数据扩展,以配合32位的向量。

程序存储器、数据存储器、寄存器和输入/输出端口被组织在同一个4GB的线性地址空间内。数据字节以小端格式存放在存储器中。一个字里的最低地址字节被认为是该字的最低有效字节,而最高地址字节是最高有效字节。

可访问的存储器空间被分成8个主要块,每个块为512MB。

其他所有没有分配给片上存储器和外设的存储器空间都是保留的地址空间,请参考相应器件数据手册中的存储器映像图。外设寄存器的映像请参考相关章节。

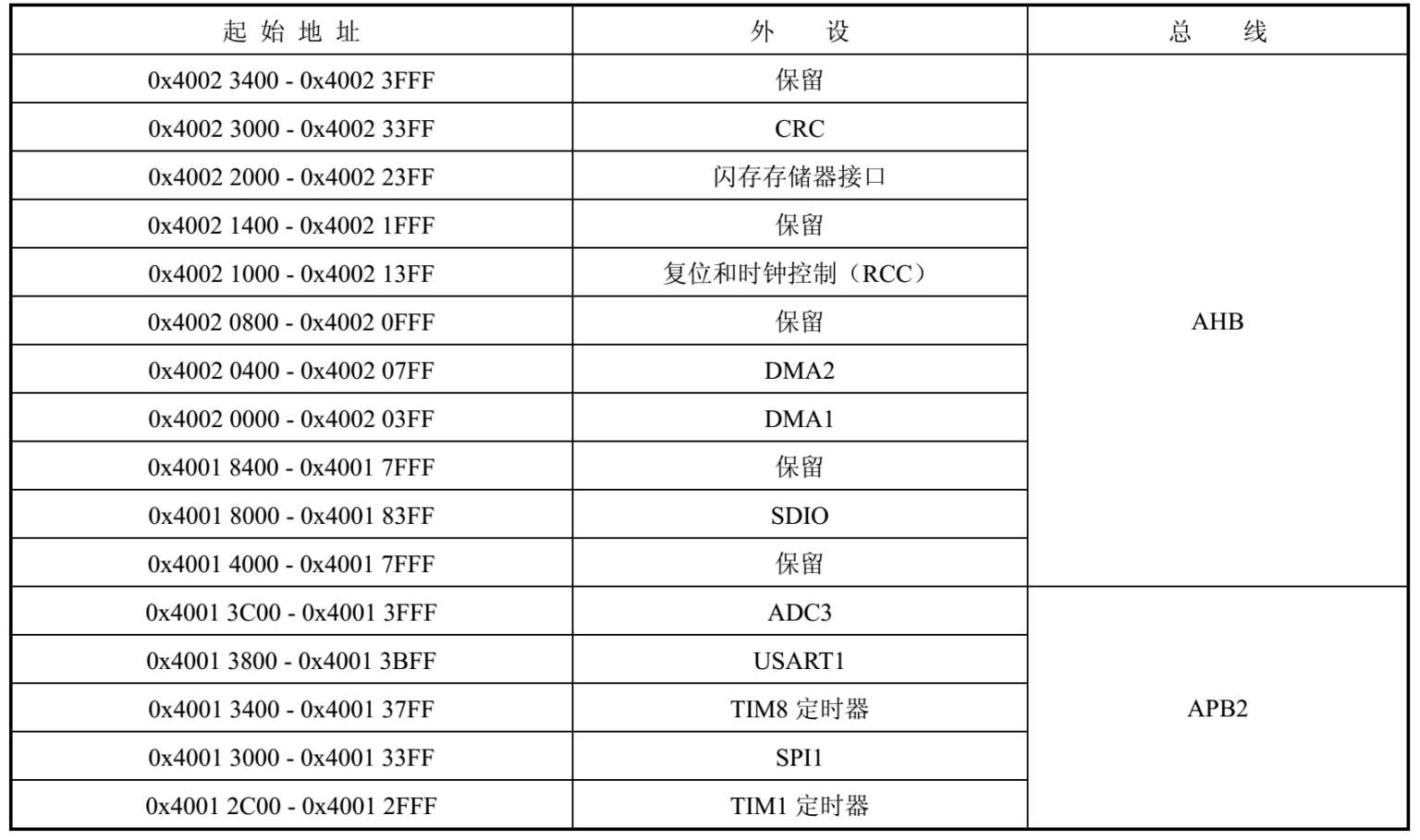

表3.1所示为寄存器组起始地址。

表3.1 寄存器组起始地址

续表

STM32F10xx内置64KB的静态SRAM。它可以以字节、半字(16位)或全字(32位)访问。SRAM的起始地址是0x2000 0000。

Cortex-M3存储器映像包括两个位段(bit-band)区。这两个位段区将别名存储器区中的每个字映射到位段存储器区的一个位,在别名存储区写入一个字,具有对位段区的目标位执行读-改-写操作的相同效果。在STM32F10xx里,外设寄存器和SRAM都被映射到一个位段区里,这允许执行单一的位段的写和读操作。

下面的映射公式给出了别名区中的每个字是如何对应位带区的相应位的:

bit_word_addr=bit_band_base+(byte_offset x 32)+(bit_number×4)

其中:bit_word_addr是别名存储器区中字的地址,它映射到某个目标位;bit_band_base是别名区的起始地址;byte_offset是包含目标位的字节在位段里的序号;bit_number是目标位所在位置(0~31)。

下面的例子说明如何映射别名区中SRAM地址为0x20000300的字节中的位2:

0x22006008=0x22000000+(0x300×32)+(2×4)

对0x22006008地址的写操作与对SRAM中地址0x20000300字节的位2执行读—改—写操作有着相同的效果。

读0x22006008地址返回SRAM中地址0x20000300字节的位2的值(0x01或0x00)。

高性能的闪存模块包括主存储块、信息块和闪存存储器接口寄存器,有以下主要特性。

高达512KB闪存存储器结构:闪存存储器由主存储块和信息块组成。

◆ 主存储块容量:

① 小容量产品主存储块为4KB×64位,每个主存储块划分为32个1KB的页(见表3.2)。

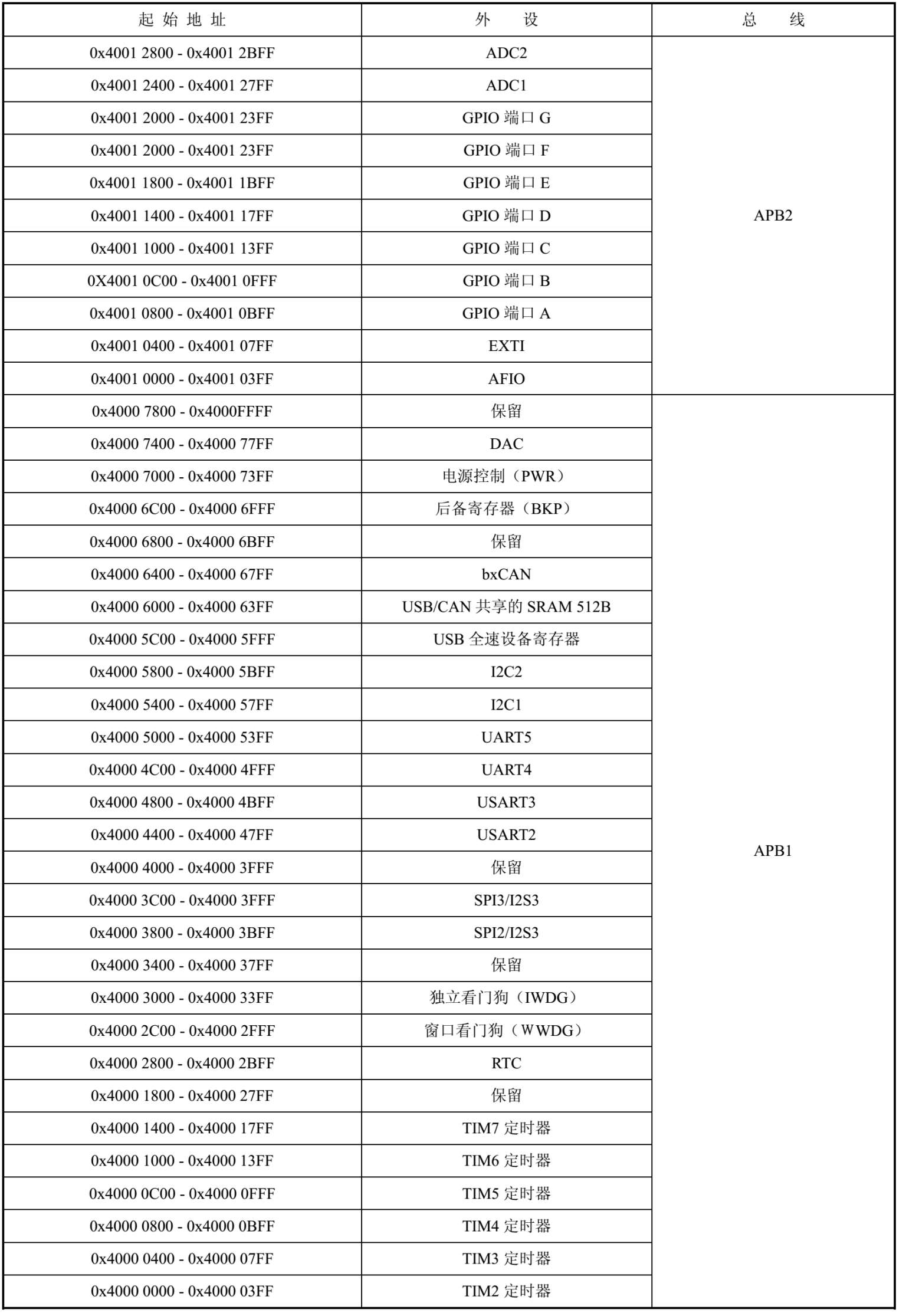

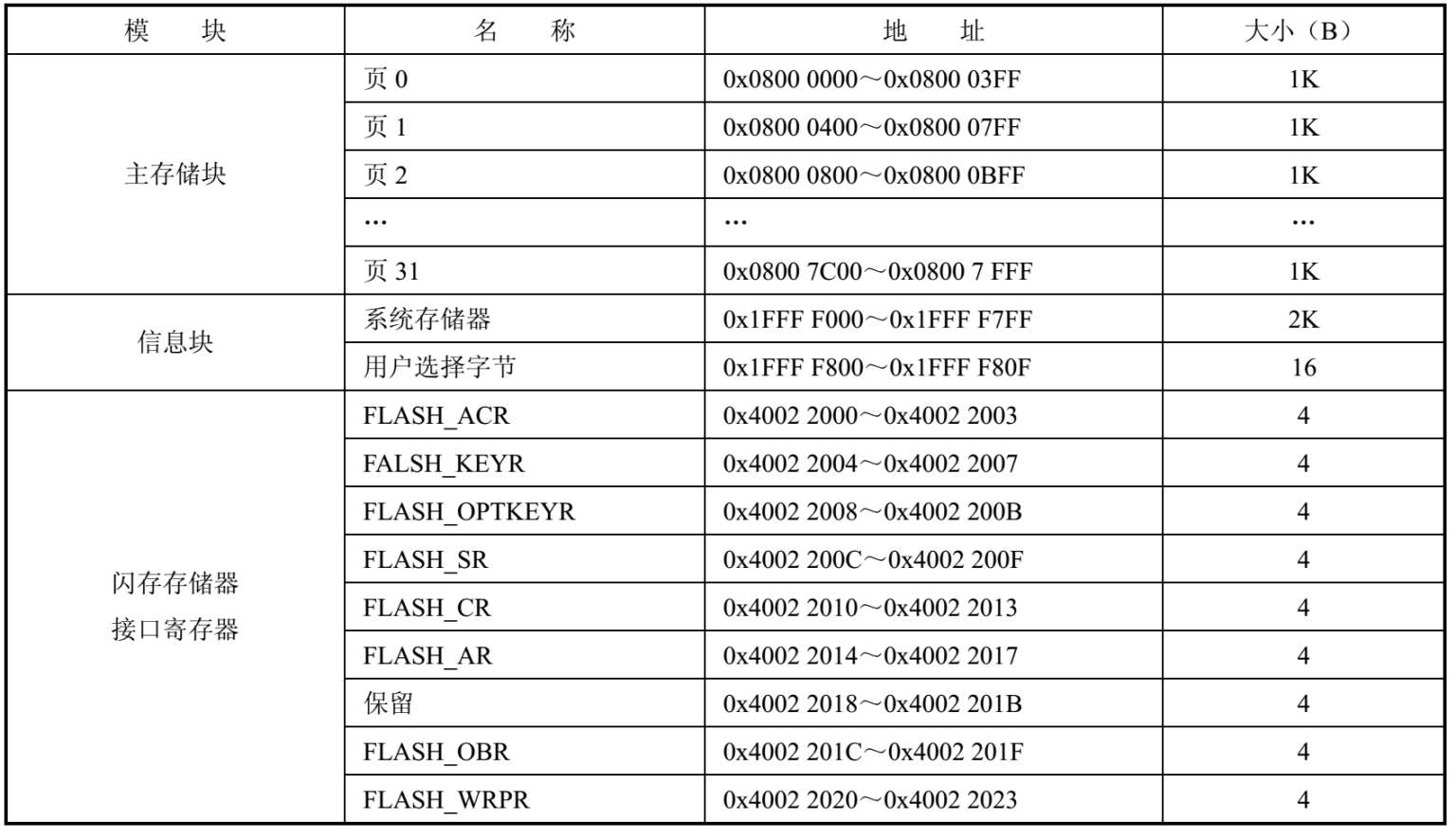

表3.2 小容量产品闪存模块的组织

② 中容量产品主存储块为16KB×64位,每个主存储块划分为128个1KB的页(见表3.3)。

表3.3 中容量产品闪存模块的组织

③ 大容量产品主存储块为64KB×64位,每个主存储块划分为256个2KB的页(见表3.4)。

表3.4 大容量产品闪存模块的组织

◆ 信息块为258×64位,每个信息块划分为一个2KB的页和一个16B的页。

◆ 闪存存储器接口寄存器:

① 带预取缓冲器的读接口(每字为2×64位)。

② 选择字节加载器。

③ 闪存编程/擦除操作。

④ 访问/写保护。

● 闪存读取

闪存的指令和数据访问是通过AHB总线完成的。预取模块是通过ICode总线读取指令的。仲裁作用在闪存接口,并且DCode总线上的数据访问优先。

读访问可以有以下配置选项。

◆ 等待时间:可以随时更改的用于读取操作的等待状态的数量。

◆ 预取缓冲区(2个64位):在每一次复位以后被自动打开,由于每个缓冲区的大小(64位)与闪存的带宽相同,因此只需一次读闪存的操作即可更新整个缓冲区的内容。由于预取缓冲区的存在,CPU可以工作在更高的主频。CPU每次取指最多为32位的字,取一条指令时,下一条指令已经在缓冲区中等待。

◆ 半周期:用于功耗优化。

值得注意的是,这些选项应与闪存存储器的访问时间一起使用。

◆ 等待周期体现了系统时钟(SYSCLK)频率与闪存访问时间的关系:

0等待周期,当0<SYSCLK<24MHz;

1等待周期,当24MHz<SYSCLK≤48MHz;

2等待周期,当48MHz<SYSCLK≤72MHz。

◆ 半周期配置不能与使用了预分频器的AHB一起使用,时钟系统应该等于HCLK时钟。该特性只能用在时钟频率为8MHz或低于8MHz时,可以直接使用的内部RC振荡器(HSI),或主振荡器(HSE),但不能用PLL。

◆ 当AHB预分频系数不为1时,必须置预取缓冲区处于开启状态。

◆ 预取缓冲器的打开和关闭操作只有在系统时钟(SYSCLK)小于24MHz时才能执行。一般而言,预取缓冲器的打开和关闭操作在初始化过程中执行,这时微控制器的时钟由8MHz的内部RC振荡器(HSI)提供。

◆ 使用DMA:DMA在DCode总线上访问闪存存储器,它的优先级比ICode上的取指高。DMA在每次传送完成后具有一个空余的周期。有些指令可以和DMA传输一起执行。

● 编程和擦除闪存

闪存编程一次可以写入16位(半字)。闪存擦除操作可以按页面擦除或完全擦除(全擦除)。全擦除不影响信息块。为了确保不发生过度编程,闪存编程和擦除控制器块是由一个固定的时钟控制的。写操作(编程或擦除)结束时可以触发中断。仅当闪存控制器接口时钟开启时,此中断可以用来从WFI模式退出。

在STM32F10xx里,可以通过BOOT[1:0]引脚选择三种不同启动模式,如表3.5所示。

表3.5 启动模式

在系统复位后,SYSCLK的第4个上升沿、BOOT引脚的值将被锁存。用户可以通过设置BOOT1和BOOT0引脚的状态,来选择在复位后的启动模式。

在从待机模式退出时,BOOT引脚的值将被重新锁存。因此,在待机模式下BOOT引脚应保持为需要的启动配置。在启动延迟之后,CPU从地址0x0000 0000获取堆栈顶的地址,并从启动存储器的0x0000 0004指示的地址开始执行代码。

因为固定的存储器映像,代码区始终从地址0x0000 0000开始(通过ICode和DCode总线访问),而数据区(SRAM)始终从地址0x2000 0000开始(通过系统总线访问)。Cortex-M3的CPU始终从ICode总线获取复位向量,即启动仅适合于从代码区开始(典型的从Flash启动)。STM32F10xx微控制器实现了一个特殊的机制,系统不仅可以从Flash存储器或系统存储器启动,还可以从内置SRAM启动。

根据选定的启动模式,主闪存存储器、系统存储器或SRAM可以按照以下方式访问。

◆ 从主闪存存储器启动:主闪存存储器被映射到启动空间(0x0000 0000),但仍然能够在它原有的地址(0x0800 0000)访问它,即闪存存储器的内容可以在两个地址区域访问——0x0000 0000或0x0800 0000。

◆ 从系统存储器启动:系统存储器被映射到启动空间(0x0000 0000),但仍然能够在它原有的地址(0x1FFF F000)访问它。

◆ 从内置SRAM启动:只能在0x2000 0000开始的地址区访问SRAM。

当从内置SRAM启动时,在应用程序的初始化代码中,必须使用NVIC的异常表和偏移寄存器,重新映射到向量表SRAM中。

内嵌的自举程序用于通过USART1串行接口对闪存存储器进行重新编程。这个程序位于系统存储器中,由ST在生产线上写入。