Cortex-M3处理器和嵌套向量中断控制器(NVIC)对所有异常按优先级进行排序并处理。所有异常都在处理模式中操作。出现异常时,自动将处理器状态保存到堆栈中,并在中断服务程序(ISR)结束时自动从堆栈中恢复。在状态保存的同时取出向量快速地进入中断。

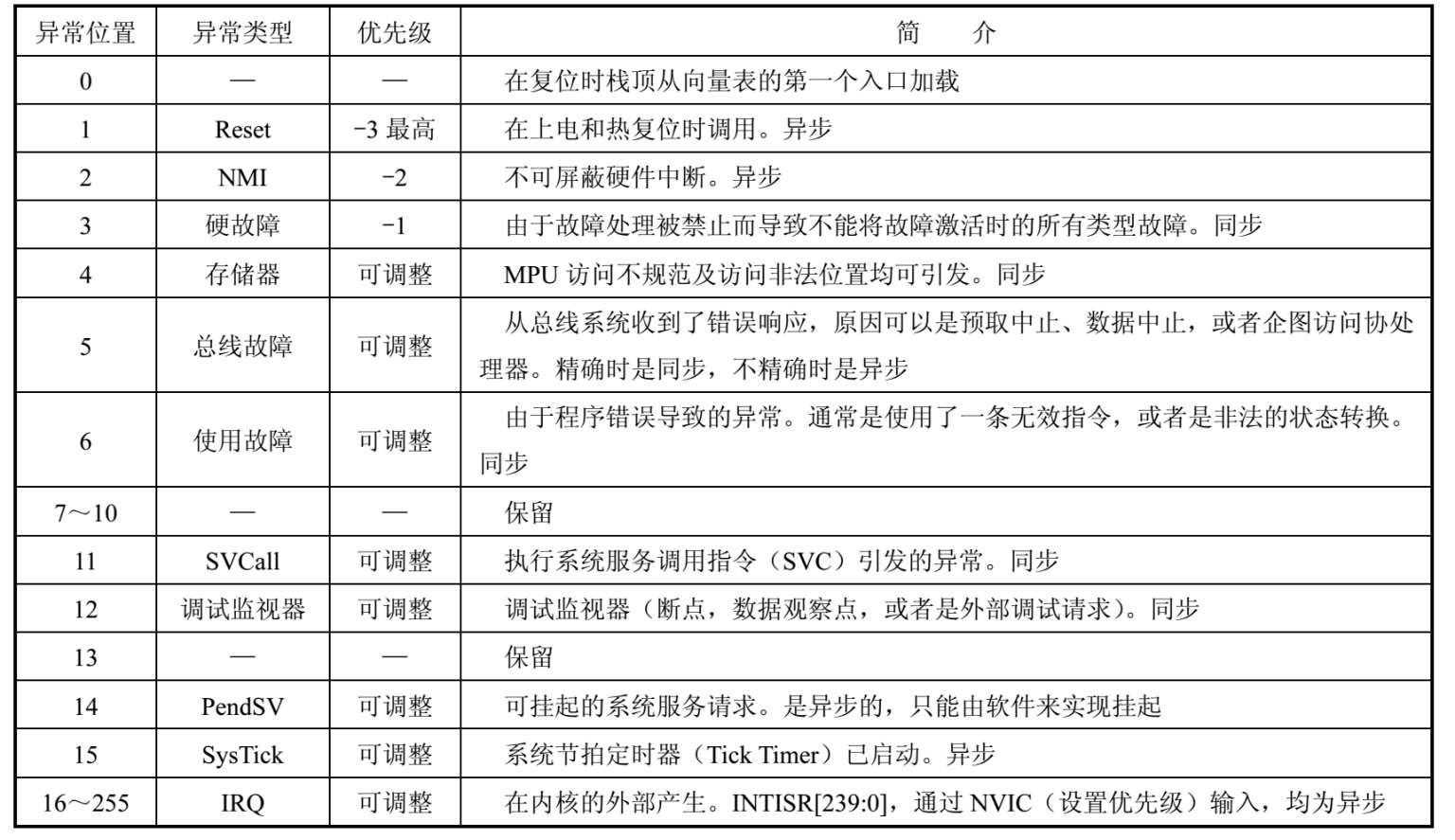

Cortex-M3支持大量异常,包括固定数量的系统异常和最多240个外部中断——通常称为IRQ。具体使用了这240个中断源中的多少个,由芯片制造商决定。除了Sys Tick之外,由外设产生的中断信号,全连接到NVIC的中断输入信号线。表2.4列出了Cortex-M3可以支持的所有异常。

表2.4 Cortex-M3支持的异常

作为中断功能的强化,NVIC还有一条NMI输入信号线。NMI究竟被拿去做什么,还要视处理器的设计而定。在多数情况下,NMI被连接到一个看门狗定时器,有时也会是电压监视功能块,以便在电压掉至危险级别后警告处理器。NMI可以在任何时间被激活,甚至是在处理器刚刚复位之后。同时有一定数量的系统异常是用于故障处理的,它们可以由多种错误条件引发。NVIC还提供了一些故障状态寄存器,以便于故障服务例程找出导致异常的具体原因。

根据表2.4,Cortex-M3支持3个固定高优先级和最多256个可编程优先级。3个固定异常是复位、NMI和硬故障,它们有固定的优先级,并且其优先级号是负数,从而高于所有其他异常。所有其他异常的优先级都是正数可编程的。为了处理不同优先级的异常,定义了占先、末尾连锁、返回和迟来等多种处理方式。

● 占先

新的异常比当前的异常或线程的优先级更高并打断当前的流程,这是对挂起中断(pendedinterrupt)的响应。如果挂起中断的优先级比当前的ISR或线程的优先级更高,则进入挂起中断的ISR。如果一个ISR抢占了另一个ISR,则产生中断嵌套。在进入异常时,处理器自动保存其状态,将状态压栈。与此同时,取出相应的中断向量。当处理器状态被保存并且ISR的第一条指令进入处理器流水线的执行阶段时,开始执行ISR的第一条指令。状态保存在系统总线上执行。取向量操作根据向量表所在位置可以在系统总线或D-Code总线上执行,见向量表偏移寄存器。

● 末尾连锁

末尾连锁(Tail-chain)是处理器用来加速中断响应的一种机制。在结束ISR时,如果存在一个挂起中断,其优先级高于正在返回的ISR或线程,那么就会跳过出栈操作,转而将控制权让给新的ISR。

● 返回

在没有挂起(pending)异常或没有比被压栈的ISR优先级更高的挂起异常时,处理器执行出栈操作,并返回到被压栈的ISR或线程模式。

在响应ISR之后,处理器通过出栈操作自动将处理器状态恢复为进入ISR之前的状态。如果在状态恢复过程中出现一个新的中断,并且该中断的优先级比正在返回的ISR或线程更高,则处理器放弃状态恢复操作并将新的中断作为Tail-chain来处理。

● 迟来

迟来是处理器用来加速占先的一种机制。如果在保存前一个占先的状态时出现一个优先级更高的中断,则处理器转去处理优先级更高的中断,开始该中断的取向量操作。状态保存不会受到迟来的影响。因为被保存的状态对于两个中断都是一样的,状态保存继续执行不会被打断。处理器对迟来中断进行管理,直到ISR的第一条指令进入处理器流水线的执行阶段。返回时,采用常规的Tail-chain技术。