下面所有操作都是在启动软件,打开demo_complete.sip完成的,使用完可选择关闭当前的文件,但不要存盘,然后重新打开。亦可Command>中直接输入reopen。

1.放大、缩小和自动滑屏的命令

最常用的方法利用鼠标滚轮,向上滚轮是放大,向下滚轮是缩小。按住鼠标中键移动可滑屏。当用户用鼠标中键单击第一点,向下方移动是缩小,向上方移动是放大。以下是相关命令:

●Zoom by Point表示两坐标之间的区域放大。

●Zoom Fit表示显示整块基板。

●Zoom In表示放大。

●Zoom Out表示缩小。

●Zoom World表示显示整个工作区域。

●Zoom Center画面移至正中央。

●Zoom Previous表示回到上一个画面。

在实际操作中,用户可把其中的任何命令设置成快捷键的方式来进行。

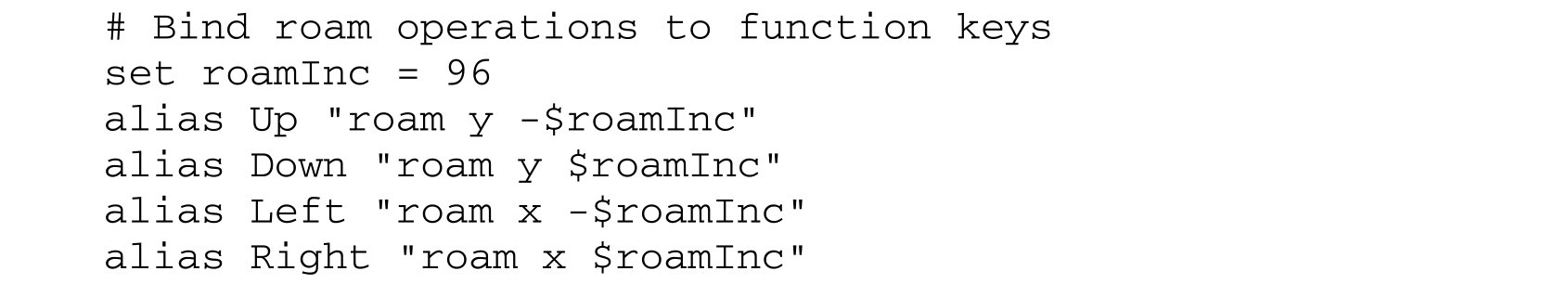

上下左右键,可用来滑屏。滑屏的长度是由env文件中的下列语句决定的:

操作命令如下:

●选择Start→Programs→Cadence→Release SPB16.3→SiP,启动SiP软件,打开demo_complete.sip文件。

●选择View→Zoom by Point,将两坐标之间的区域放大。

●把鼠标放置到工作界面,单击鼠标左键,移动鼠标出现一个动态的窗口,再次单击鼠标左键完成区域放大。

●在工作界面单击鼠标中键,向上移动鼠标出现一个动态的窗口,再次单击鼠标中键完成放大。向下移动鼠标中键,移动鼠标出现一个动态的窗口,再次单击鼠标中键完成区域缩小。可利用鼠标滚轮,向上滚轮是放大,向下滚轮是缩小。

●在工作界面中,按住鼠标中键,上下左右移动,可完成滑屏。

●选择View→Zoom World,显示整个工作区域。

●选择View→Zoom Fit,显示整块基板。

●选择View→Zoom In表示放大,在命令行中输入alias F2 zoom in并按回车键。然后按【F2】键可完成放大功能。这个方法只对当前的项目有效。当用户重新启动SiP命令自动改成默认的方式。如果用户需要改成永久有效,可在env文件中进行直接修改。

●选择View→Zoom Out表示缩小。

2.改变网络颜色的命令

这个命令在新版软件中改变较大,原来用户通过Highlight来点亮网络,在新的软件中可对网络设置固定的颜色。

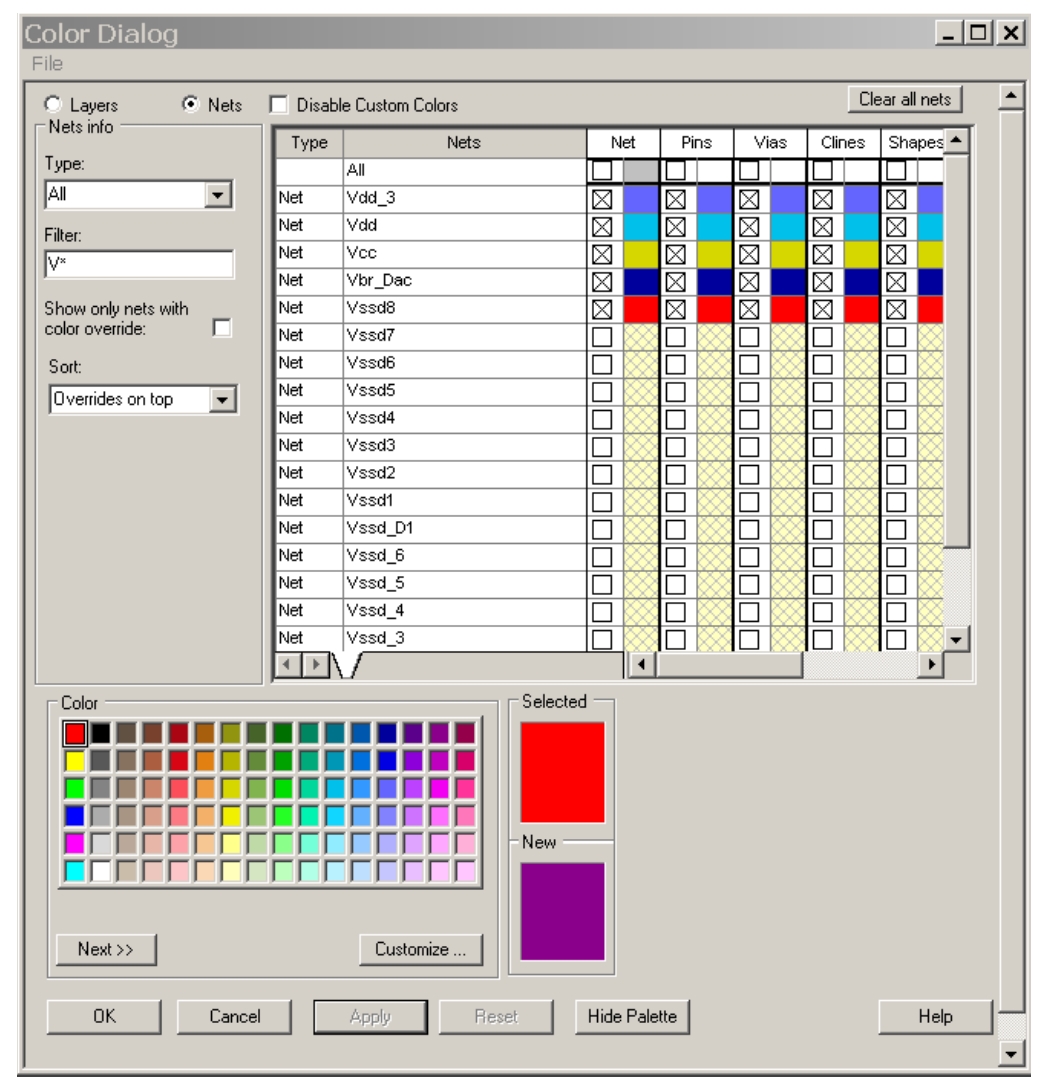

(1)选择Display→Color/Visibility命令,弹出Color Dialog对话框。在左上角选择Nets单选按钮,如图2-9所示。

图2-9 网络颜色设置

(2)在Tpye下拉列表框中选择All。在Filer文本框中输入V*,按【Tab】键。单击图中左下角的Color区,选择红色。然后选择Net Vssd8,Net列,表示Vssd_8的网络颜色变成红色。如果不需要整个网络变成红色,可选择单独选择Pins、Vias、Clines、Shape、Rats改变颜色。

(3)单击Apply按钮,表示网络Vssd_8颜色已经改成红色。

(4)如果用户需要找到所有已经设置颜色的网络,可在Sort下拉列表框中选择Override on top或者Overrides on bottom,可把已经设置好颜色的网络调到前面或后面。

(5)勾选Show only nets with color override表示在右边界面中只显示所有设置了颜色的网络。

(6)选择Vbr_Dac网络的Net行,单击鼠标右键,在弹出的快捷菜单中选择Clear custom color,表示清除网络Vbr_Dac的颜色设置。

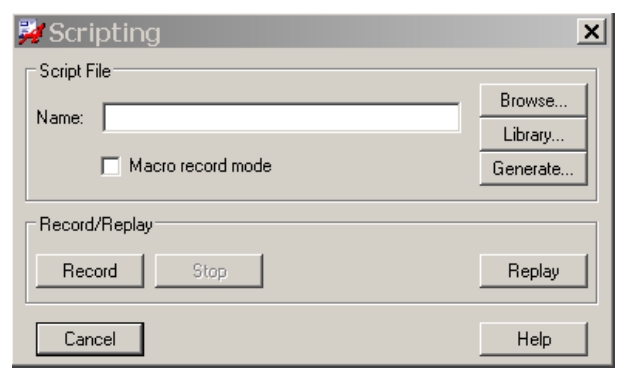

3.File→Script命令

Sip可将用户正在进行的所有动作记录成一个文本文件,其默认的文件后缀名是.scr。以后可重新播放这个文件,重复选择之前的所有命令。

(1)选择File→Open命令,打开文件demo_complete.sip文件。

(2)选择File→Script命令,弹出Scripting对话框,如图2-10所示。在Name文本框中输入demo,如图2-10所示。

图2-10 Scripting界面

(3)弹出Padstack for Component对话框,选择smd550cir_1,单击OK按钮。

(4)选择View→Zoom In命令,将画面放大,并能见到BGA的引脚。

(5)选择Display→Show Element命令,或单击

图标。把鼠标放在控制面板中的Find上,单击All off按钮,并勾选Pins复选框。选择任一Pin,弹出Show Element对话框。

图标。把鼠标放在控制面板中的Find上,单击All off按钮,并勾选Pins复选框。选择任一Pin,弹出Show Element对话框。

(6)选择File→Script命令,弹出Scripting对话框,单击Stop状态栏中Rec demo消失,表示已经停止录制。

(7)下面来测试一下这个命令。选择View→Zoom Fit命令,回到全局状态。

(8)选择File→Script命令,单击Browse按钮,选择demo,单击Replay按钮,弹出Show Element对话框。

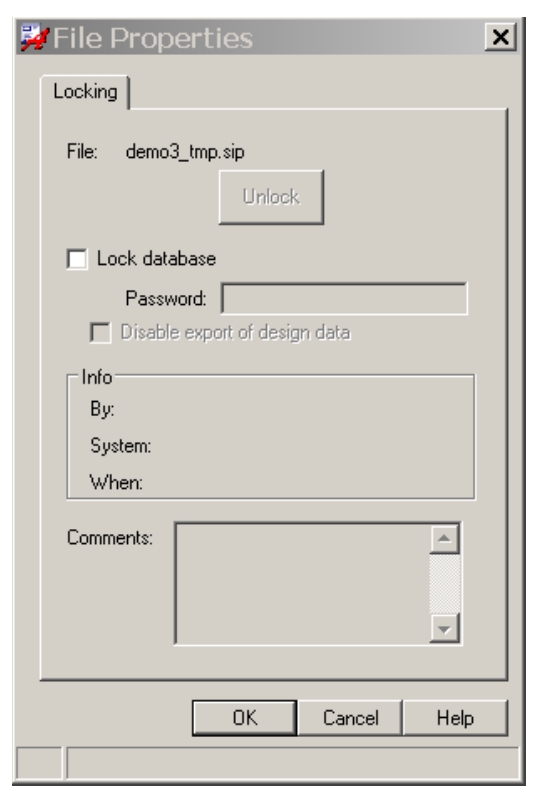

4.File→Properities命令

这个命令主要用来锁住文件,确保用户的设计文件是可读的文件,防止别的用户修改该文件。

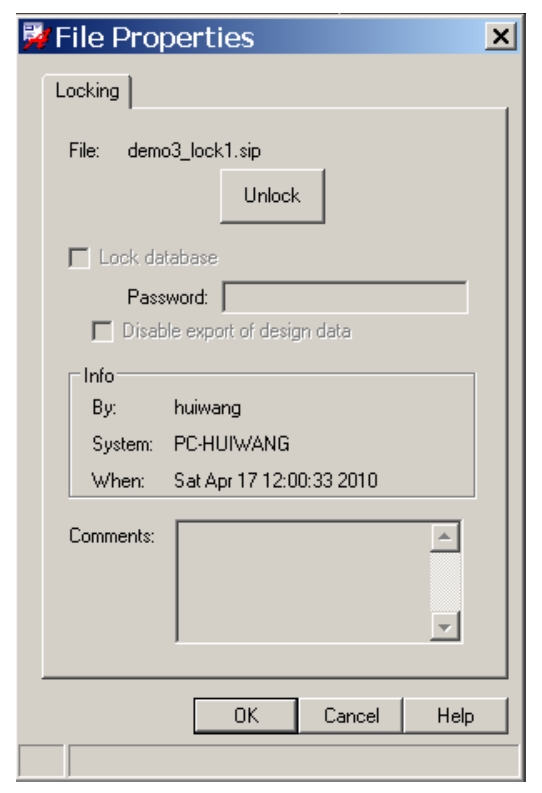

(1)选择File→Properties命令,弹出File Properties对话框,如图2-11所示。

(2)勾选Lock database复选框,在Password文本框中输入123,单击OK按钮,弹出Cadence SiP Layout XL对话框。

(3)在Please confirm password文本框中再次输入123,单击OK按钮。

(4)弹出File Properties对话框,在File name文本框中输入demo_lock,单击Save按钮,表示此文件是只读文件。

(5)解锁文件,需要选择File→Properties命令,弹出如图2-12所示的对话框。

图2-11 File Properties对话框

图2-12 解锁文件

(6)单击Unlock按钮,弹出Cadence SiP Layout XL对话框,在Passwork to unlock文本框中输入123,单击OK按钮。再次单击File Properties对话框中的OK按钮,表示完成解锁。

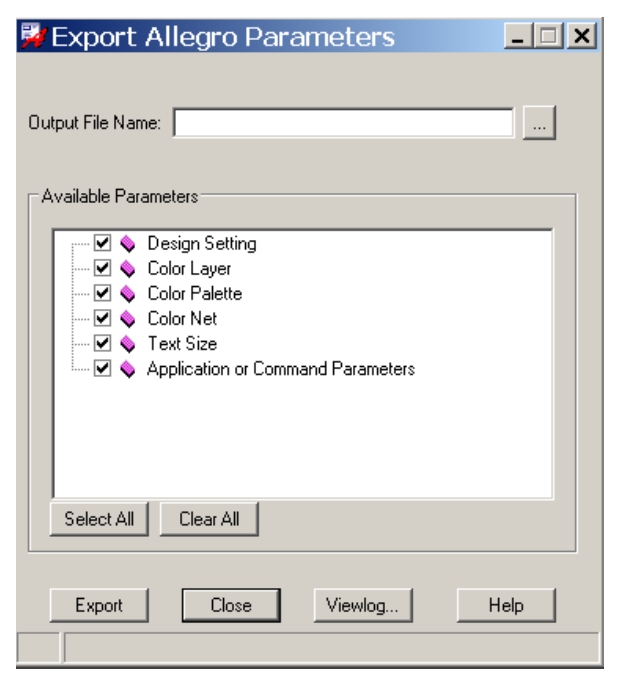

5.File→Export Parameters和File→Import Parameters命令

这个功能是SPB16.01新添加的功能。可把Design Setting、Color layer、Color Palette、Color Net、Text Size和Appication or Command Parameters方便地输出成文件。在新的设计中通过File→Import Parameters命令调入。

(1)选择File→Export Parameters命令,弹出Export Allegro Parameters对话框,如图2-13所示。

图2-13 Allegro参数输出

(2)在Output File Name文本框中输入demo,单击Select All按钮,再单击Export按钮。

●Design Setting主要包含的内容是全局变量(主要是指Setup→Design Parameter中的参数)、栅格的设置和光绘文件的定义。

●Color Layer为每层颜色的设置。

●Color Palette为颜色调色板的设置。

●Color Net为网络颜色的设置。这个参数同net有关,新的设计中必须有相应的net才行,没有相应的net,自动清除。

●Text Size为文字大小的设置。

●Application or Command Parameters为所有其他支持的命令,包括auto name、auto rename、auto assignment、auto silkscreen、global dynamic fill、autovoid、export logic、drafting、gloss line fattening、gloss dielectric generation、Option对话框的设置、test prep、automatic placment、atuo swap、thieving、backdrill和Signoise analysis。这些命令的设置都可存在此文件中。

(4)选择Tools→Utilities→File Mangager命令,弹出Windows资源管理器,可在右边窗口中找到刚产生的demo.prm文件。

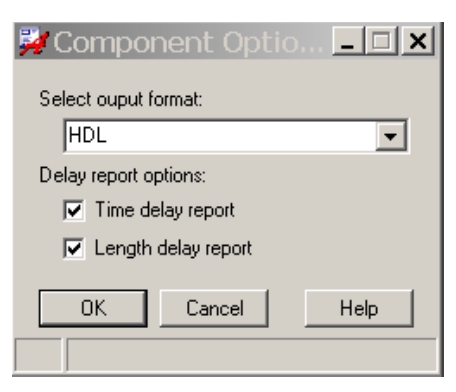

6.File→Export Brodlevel Symbol命令

此命令产生PCB设计所需要的各种文件。

(1)选择File→Export Broadlevel Symbol命令,弹出Component Option对话框,如图2-14所示。

图2-14 Component Opticn对话框

(2)在Select output format下拉列表中选择HDL,并勾选Time delay report和Length delay report复选框,单击OK按钮。

(3)弹出Padstack for Component对话框,选择Bga_Pad,单击OK按钮。

(4)选择Tools→Utilities→File Manager命令,在当前目录下产生一个Component的目录。双击Component,进入Component目录,有以下文件:

●Bga.dra

●Bga.psm:PCB的库文件

●Bga.tsg

●Bga_pad.pad:焊盘库

●Chips.prt

●Package_pin_delay:以时间为单位输出的引脚延时

●Package_pin_delay_lenght:以长度为单位输出的引脚延时

●symbol

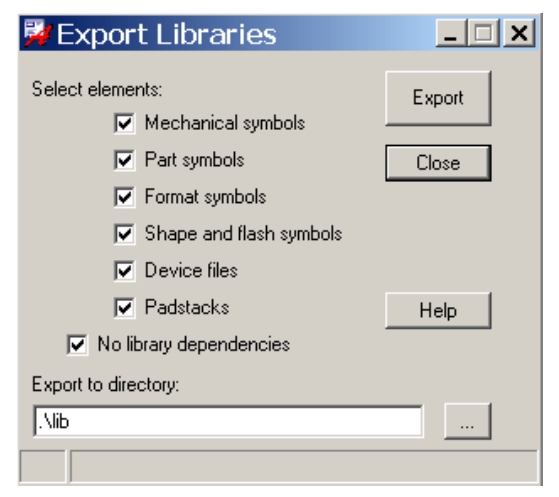

7.File→Export Library命令

从基板上输出当前基板设计中所用的库文件。

(1)选择File→Export Libraries,弹出Export Libraries对话框,如图2-15所示。

图2-15 输出库文件

(2)勾选Mechanical symbols、Part symbols、Format symbols、Shape and flash symbols、Device files、Padstacks和No library dependencies。

(3)在Export to directory文本框中输入.\lib,表示把所有的库输出到当前路径的lib目录下。

(4)单击Export按钮。

(5)选择Tools→Utilities→File manager命令打开资源管理器,双击lib,可看到输出的所有库文件。

8.File→Export Symbol Spreadsheet命令

输出元器件的信息的电子表格。

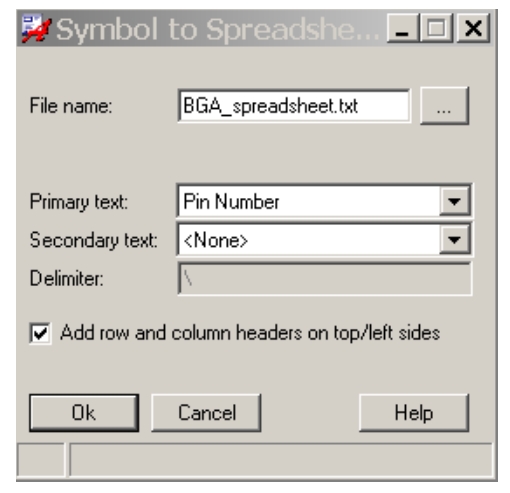

(1)选择File→Export Symbol Spredsheet命令,单击BGA Symbol,弹出Symbol to Spreadsheet对话框,如图2-16所示。

图2-16 输出电子表格文件

(2)在File name文本框中输入BGA_spreadsheet.txt。

(3)在Primary text下拉列表框中选择Pin Number。

(4)在Secondary text下拉列表框中选择Net Name。

(5)在Delimiter中输入“\”。表示用“\”来分割Primary text和Secondary text。

(6)勾选Add row and column headers on top/left sides复选框。

(7)单击OK按钮。

(8)选择Tools→Utilitities→File Manager命令,在资源管理器中选择BGA_spreadsheet.txt,单击鼠标右键,在弹出的快捷菜单中选择Open with,在弹出的对话框中选择Windows Excel打开该文件。

9.移动物体命令

这个命令的使用方法比较多,下面分别介绍。

(1)第一种方法:在General Edit模式下,直接拖曳。

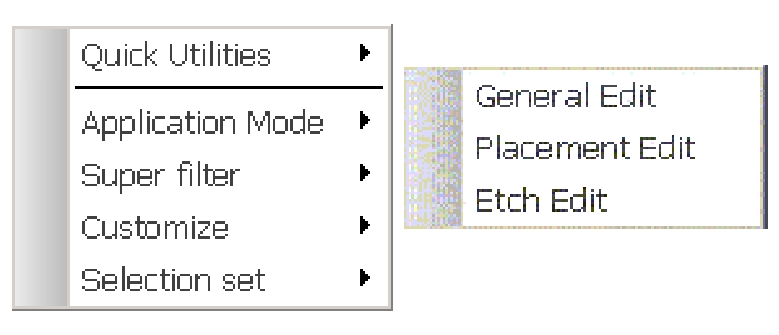

①在工作区域的空白处,单击鼠标右键,弹出图2-17所示的快捷菜单。

图2-17 鼠标右键快捷菜单

②选择Application Mode→General Edit命令,此时在右下角出现GEN文字,表示现在在General Edit工作模式下。

③单击鼠标右键,从弹出的快捷菜单中选择Super filiter→Symbol。

④把鼠标移动到用户所要移动的物体上,按下鼠标左键进行拖曳。

(2)第二种方法:在Etch Edit/Placement模式下,单击移动。

①选择Etch Edit模式,或者单击图标

。在右下角出现EE文字,表示在Etch Edit工作模式下。右下角出现PLC文字,表示在Placement工作模式下。

。在右下角出现EE文字,表示在Etch Edit工作模式下。右下角出现PLC文字,表示在Placement工作模式下。

②单击鼠标右键,从弹出的快捷菜单中选择Supper filiter→Symbol。

③单击BGA Symbol,移动鼠标,就可移动物体了。

(3)第三种方法:在Find面板中操作。

①选择Edit→Move,命令把鼠标移动到控制面板的Find上。在Find中单击All Off按钮,勾选Symbol。

②单击BGA Symbol,移动鼠标,可移动Symbol。这个方法是16.0版本之前常用的方法。建议用户好好地熟悉前两种新的方法。

(4)第四种方法:设置快捷键的方法。

①在命令行中输入funckey m move并按回车键。

②在命令行中输入m。把鼠标移动到控制面板的Find上。在Find中单击All Off按钮,然后勾选Symbol。

③单击BGA Symbol,移动鼠标,可移动Symbol。

10.Edit→Copy命令

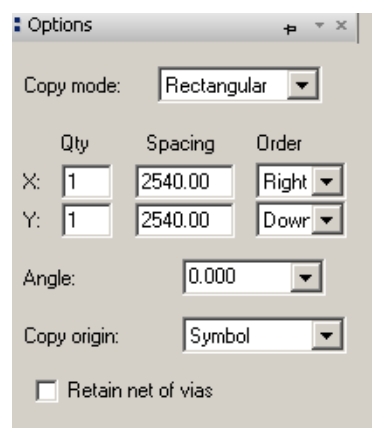

(1)选择Edit→Copy命令,把鼠标移动到控制面板的Find上,在Find中单击All off按钮,勾选Vias。

(2)把鼠标移动到控制面板的Options上,设置参数,如图2-18所示。

(3)在工作区域单击Via,在命令行输入x 7000 8150。

11.Edit→Cline Change Width命令

(1)选择Edit→Cline Change Width命令,把鼠标移动到控制面板的Options上,如图2-19所示。

(2)选择Single trace mode(two-pick)单选按钮,表示选择单线的模式。Multi trace mode表示多线的模式,即一次可选择多条线来进行。可通过鼠标左键进行对话框选择。

图2-18 复制选择对话框

图2-19 Cline Change Width选项

(3)在New width文本框中输入175.00UM,表示新的线宽是175μm。

(4)不需要勾选Filte by cline width复选框,如果需要对某一线宽的线进行改变,可勾选,并在Min width和Max width中输入值。

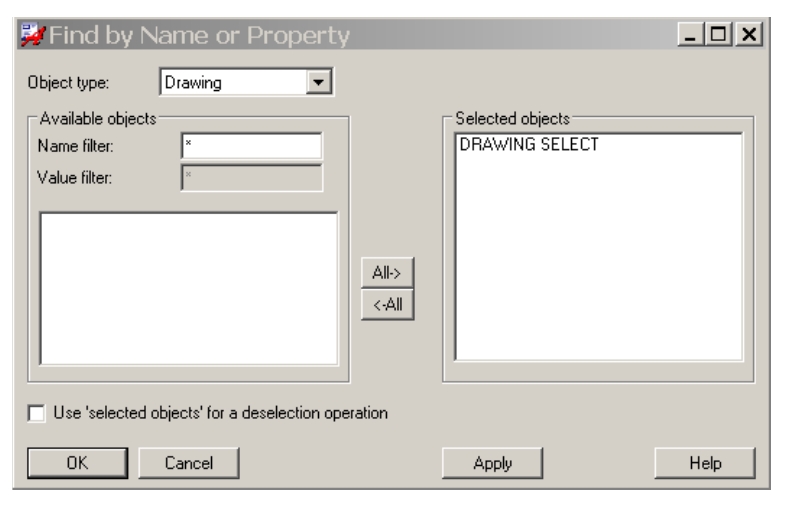

12.Edit→Properities

(1)选择Edit→Properities命令。

(2)把鼠标移动到在控制面板中的Find上。在Find By Name中选择Drawing。单击More按钮,弹出Find by Name or Property对话框,如图2-20所示。

图2-20 Find by Name or Property对话框

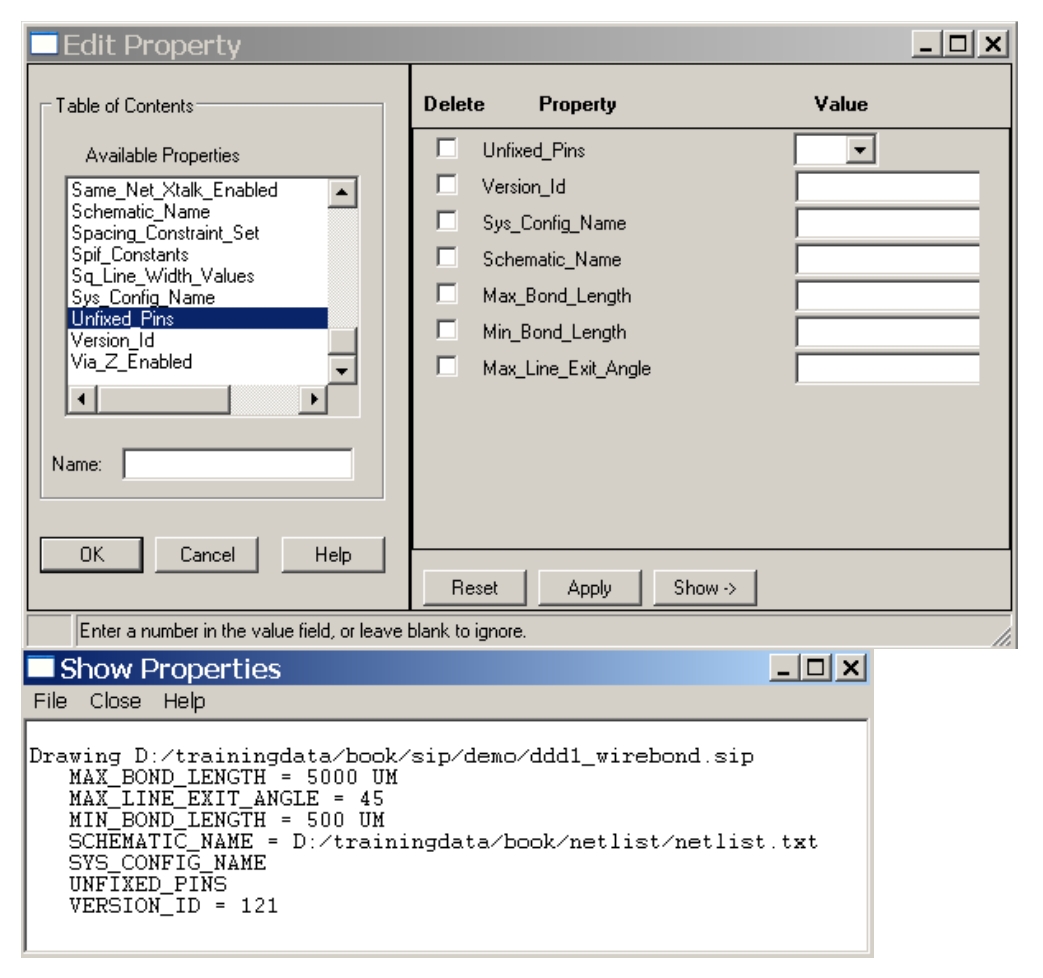

(3)单击DRAWING SELECT,单击Apply按钮,弹出Edit Property对话框,如图2-21所示。

图2-21 编辑属性

(4)在Table of Contents栏中选择Unf ixed_Pins,并单击Apply按钮。在Show Properties对话框中应当出现UNFIXED_PINS,两次单击OK按钮。

(5)选择Edit→Move命令,把鼠标移到控制面板的Find上,单击All Off按钮,然后勾选Pins复选框。

(6)把鼠标移动到BGA的Pin上,单击,可移动BGA的引脚了。

13.Edit→BGA和Edit→Die命令

这两个命令主要用来修改BGA Symbol和Die Symbol。因为这两命令里面有很多种用法,这里只介绍常见的用法。用户可自己试一下其他的方法。

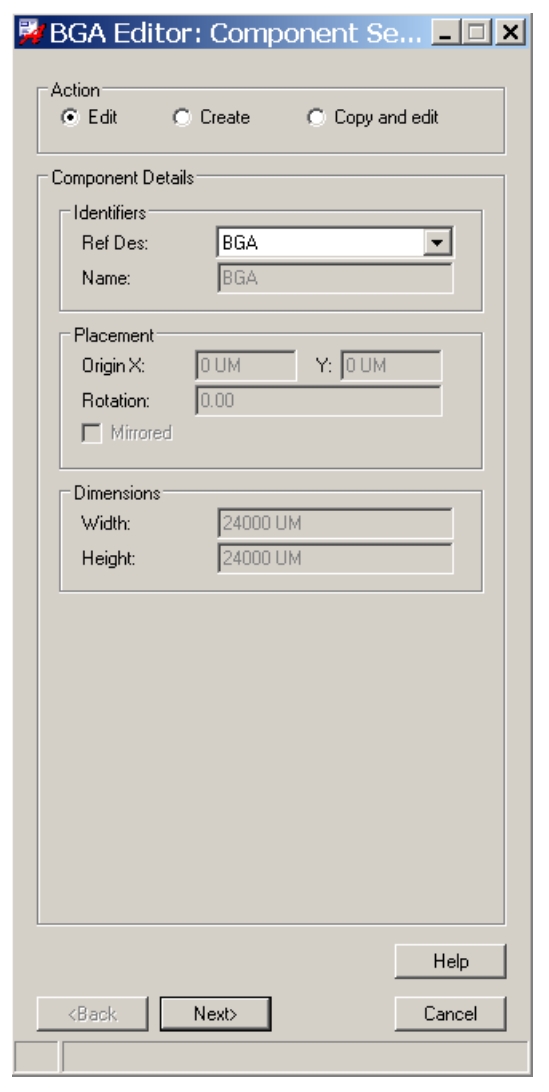

(1)选择Edit→BGA命令,弹出BGA Editor对话框,如图2-22所示。

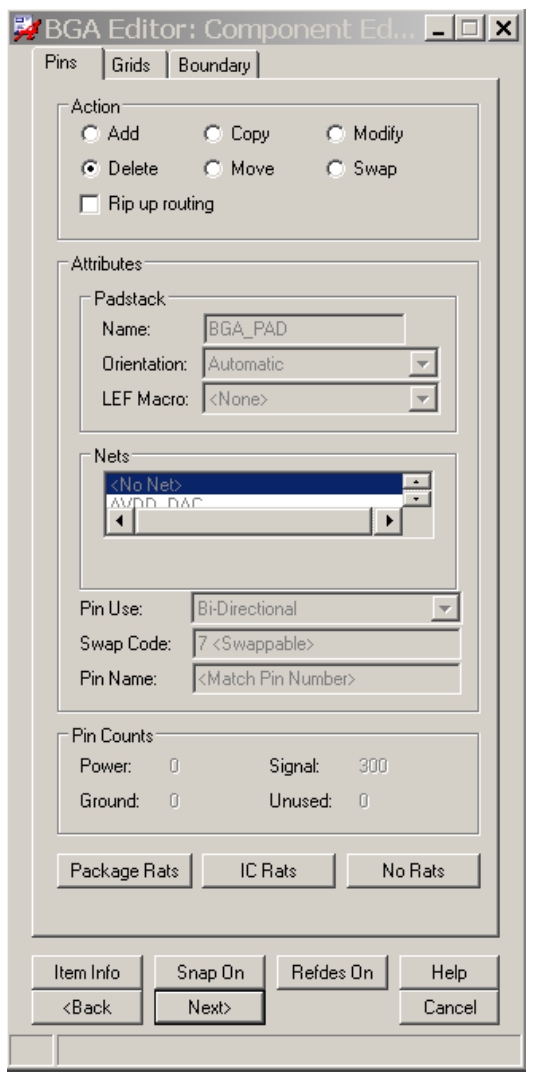

(2)在Action栏中,选择Edit单选按钮表示选择编辑状态,单击Next按钮,弹出BGA Editor对话框,如图2-23所示。

●Add表示加入Pin,选择这个选项,在Attributes栏中,可在Name文本框中输入焊盘。在Orienteation下拉列表框中选择焊盘旋转方向。

●在Nets列表框中,选择要加引脚的网络名。

●在Pin Use下拉列表框中选择信号的输入状态。

●在Swap Code文本框中输入可引脚互换的组。

图2-22 编辑BGA 1

图2-23 编辑BGA 2

(3)在Action栏中,选择Delete单选按钮,移动鼠标选择BGA的引脚,单击BGA的引脚,可删除不需要的BGA引脚。

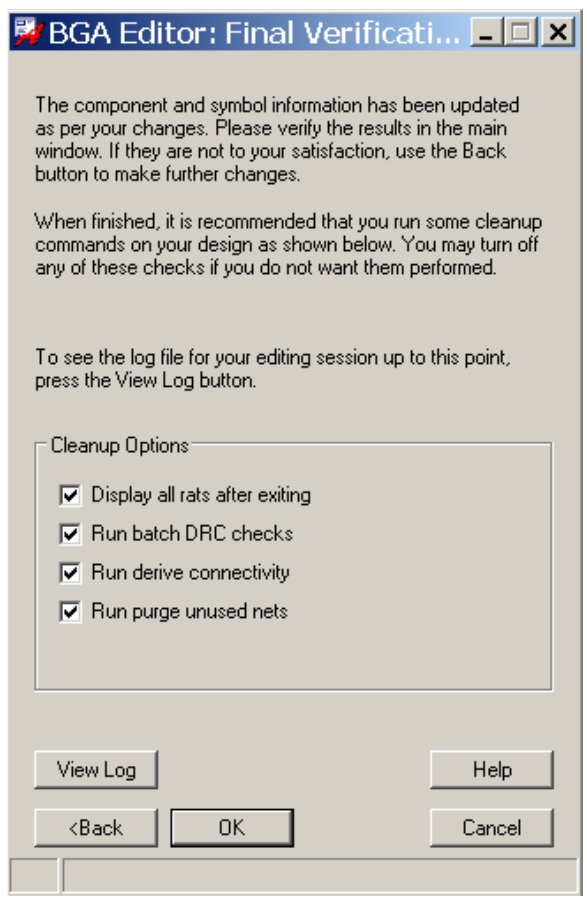

(4)单击Next按钮,弹出BGA Editor对话框,如图2-24所示。

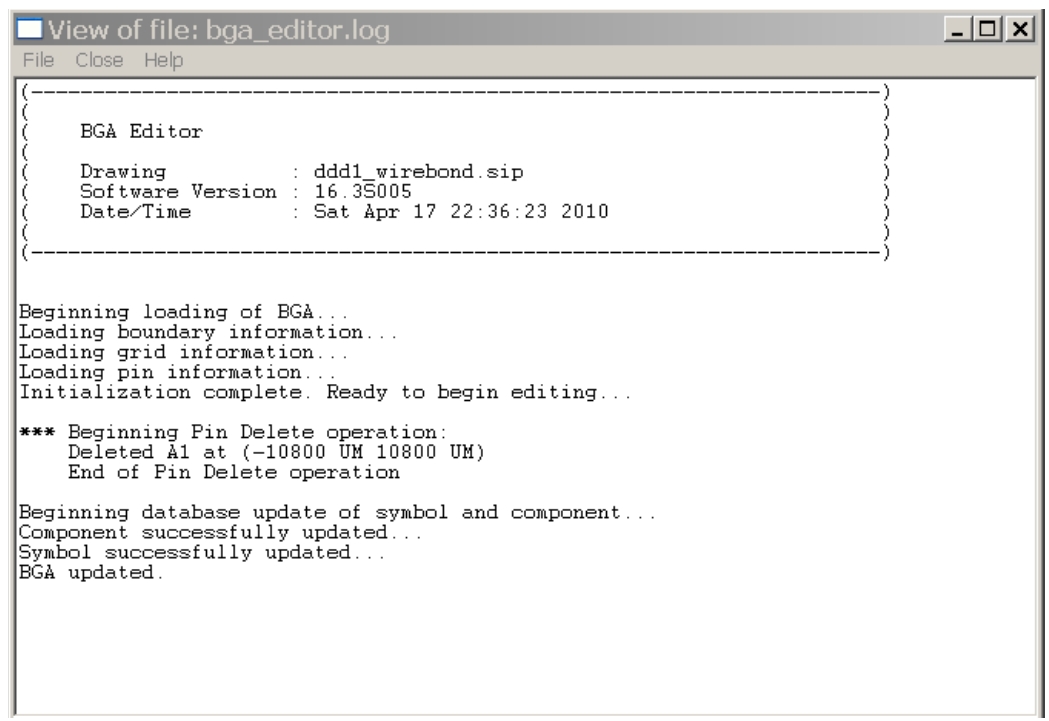

(5)单击View Log按钮在新弹出的对话框中可看到说明文件,如图2-25所示。

图2-24 编辑BGA 3

图2-25 编辑BGA的文件

(6)选择File→Close命令单击OK按钮完成。单击“Back”按钮,可返回上一步。单击Cancel按钮可取消所有的操作。

14.View→Color view Save命令

这个功能主要是选择显示的物体。

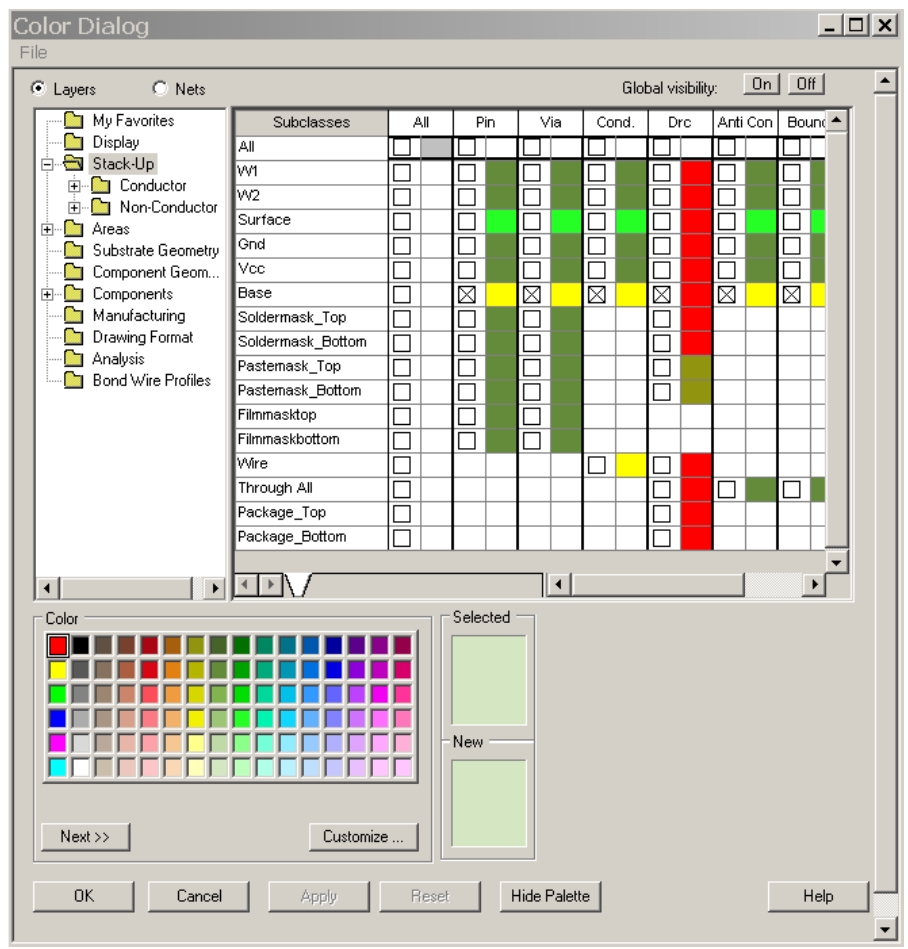

(1)选择Display→Color/Visibity,命令弹出Color Dialog对话框,如图2-26所示。

图2-26 设置颜色

(2)单击Global visibitity后的off按钮,表示关掉所有的显示。

(3)单击Stack-Up,在右边的窗口中,选择Base行,选择All列的方框。

(4)单击Subbstrate Geometry,在右边窗口勾选Outline。单击OK按钮。

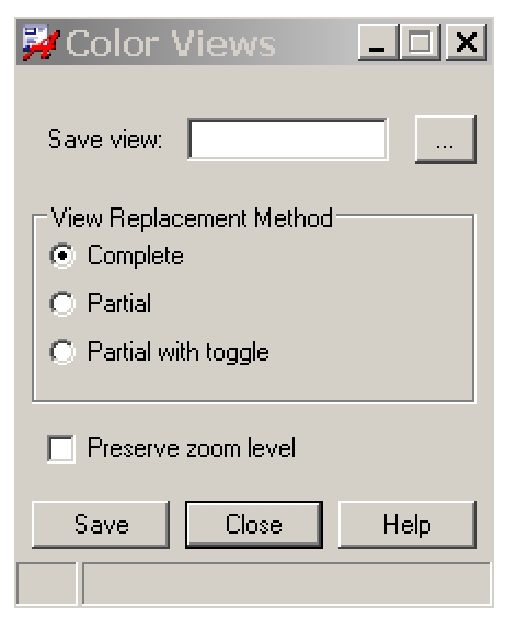

(5)选择View→Color View Save命令,弹出Color Views对话框,如图2-27所示。

图2-27 Color Views对话框

(6)在Save view文本框中输入Bottom,选择Complete单选按钮。

(7)单击Save按钮。

(8)下面来验证一下,选择Display→Color/Visibility命令,弹出Color Dialog对话框。单击Globbal visibility栏中,单击On按钮。在弹出对话框中单击Yes确认。单击OK按钮。

(9)移动鼠标到控制面板的Vsibility上,在Views中选择Bottom,在工作界面中可以看到Bottom层。

15.View Flip Design

这个命令是SPB16.3中新的功能,就是直接把SiP 设计进行Y 轴镜向。主要在完成Bottom层布线时提供更加直接的视图。

16.View→Reset UI to Cadence Default命令

从SPB16.0开始,控制面板中的三个页面就改成了可折叠式的形式。可选择每个页面右上角的三个键来调整。要想迅速复位,可选择这个功能键。

17.Disply→Pin Highlight命令

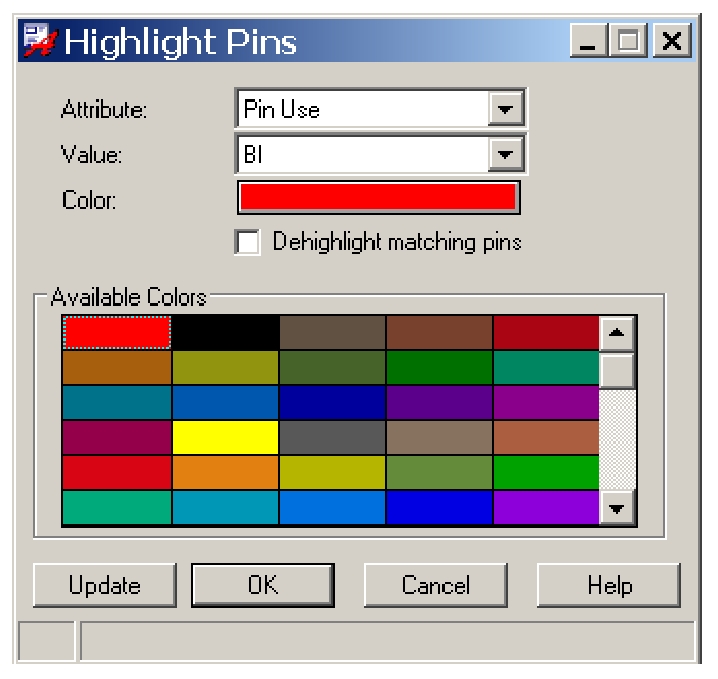

(1)选择Display→Pin Highlight命令,弹出Highlight Pins对话框,如图2-28所示。

图2-28 Highlight Pins对话框

(2)在Attribute下拉列表框中选择Pin Use,在Value下拉列表框中选择BI,在Color列表框中选择红色,不要勾选Dehighlight matching pins复选框。

(3)单击“Update”按钮,这时BGA的Pin会出现红色。

18.Disply→Finger Highlight

(1)选择Display→Finger Heighlight命令,弹出Highlight Fingers对话框,如图2-29所示,这个功能也是SPB16.3最新的功能。

图2-29 Highlight Fingers对话框

(2)在Attribut下拉列表框中选择Finger Alignment。在Value下拉列表框中选择Aligned with Wire。在Color列表框中设置为红色。

(3)不要勾选Dehighlight matching fingers复选框,如勾选,不点亮。

(4)不要勾选Temporary highlight复选框,如勾选,表示临时点亮。

(5)单击Update按钮。工作界面中的Bonding Finger会变成红色。

19.Display→Show Rat line\diplay→Blank Rat line\Disply→Rats by layer命令

这个命令主要用来显示飞线和不显示飞线。飞线主要是指在基板上没有完成连接的信号线。在SiP的布局(Placement)和布线(Routing)阶段都会用到这个功能。下面用操作命令来演示一下使用的过程。

(1)选择Display→Color Visibility命令,弹出Color Dialog对话框,如图2-26所示。

(2)选择左边的Display。

●Rats top-top表示可设置在TOP层飞线的颜色。

●Rats top-Bottom表示可设置TOP层到BOTTOM层飞线的颜色。

●Rats bottom表示可设置BOTTOM层飞线的颜色。

(3)选择Display→Show Rat line→All命令,表示显示所有飞线。

(4)选择Display→Blank Rat line→All命令,表示不显示所有飞线。

(5)选择Display→Show Rat line→Net命令,把鼠标移动到在控制面板中的Find上,在Find By Name中选择Net,单击More按钮,弹出Find by Name or Property对话框。

(6)在Available objects栏的Name filter中输入vout*,按【Tab】键。在对话框中出现vout_Adc和Vout_Ss两个网络。

(7)单击Vout_Adc网络。网络移到右边对话框中。

(8)单击“Apply”按钮。在工作区域出现Vout_Adc网络的飞线。

20.Setup→datatip customization命令

显示信息提示的功能。当移动鼠标到菜单上时,停留一下,就可看到信息提示框,但主要针对设计的信息提示。先看一下这个命令相关的配置文件。

(1)选择Setup→User Preference命令,选择Display,选择Datatips。

●Datatips_delay缺省的值是250毫秒。表示当鼠标放到对象上250毫秒以上,就出现信息提示框。可在100到2000毫秒之间自定义这个值。

●Datatips_fixedpos缺省表示信息提示框出现在鼠标附近。设定此值,表示信息提示框可固定在命令行的上方。

●Disable_datatips,如果勾选,则不显示信息提示框。

●Disable_hover_over,如果勾选,则不允许动态地点亮和出现信息提示框。

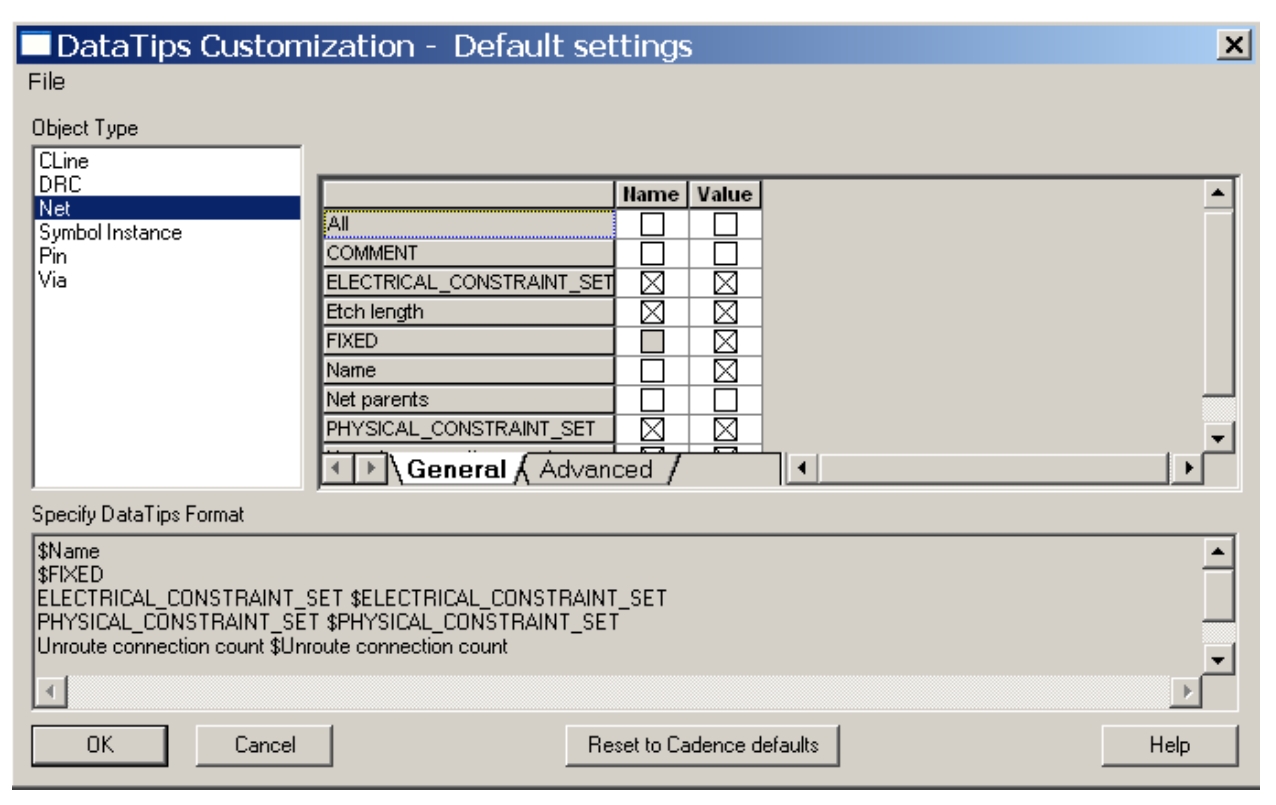

(2)选择Setup→Datatip customization命令,弹出DataTips Customization对话框,如图2-30所示。

图2-30 DataTips Customization

(3)在Object Type中,选择Net。在右边勾选Etch Length,单击OK按钮。

(4)移动鼠标到在控制面板的Find上,单击All Off按钮,勾选Net。

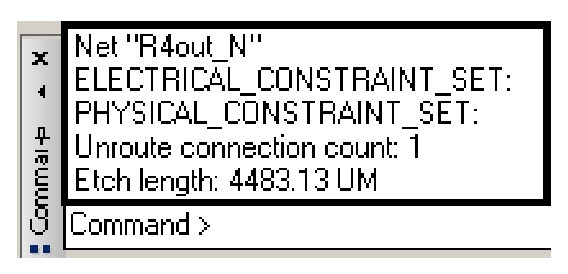

(5)移动鼠标到工作区域的网络上,在命令行上方出现信息提示框,如图2-31所示。

图2-31 信息提示框

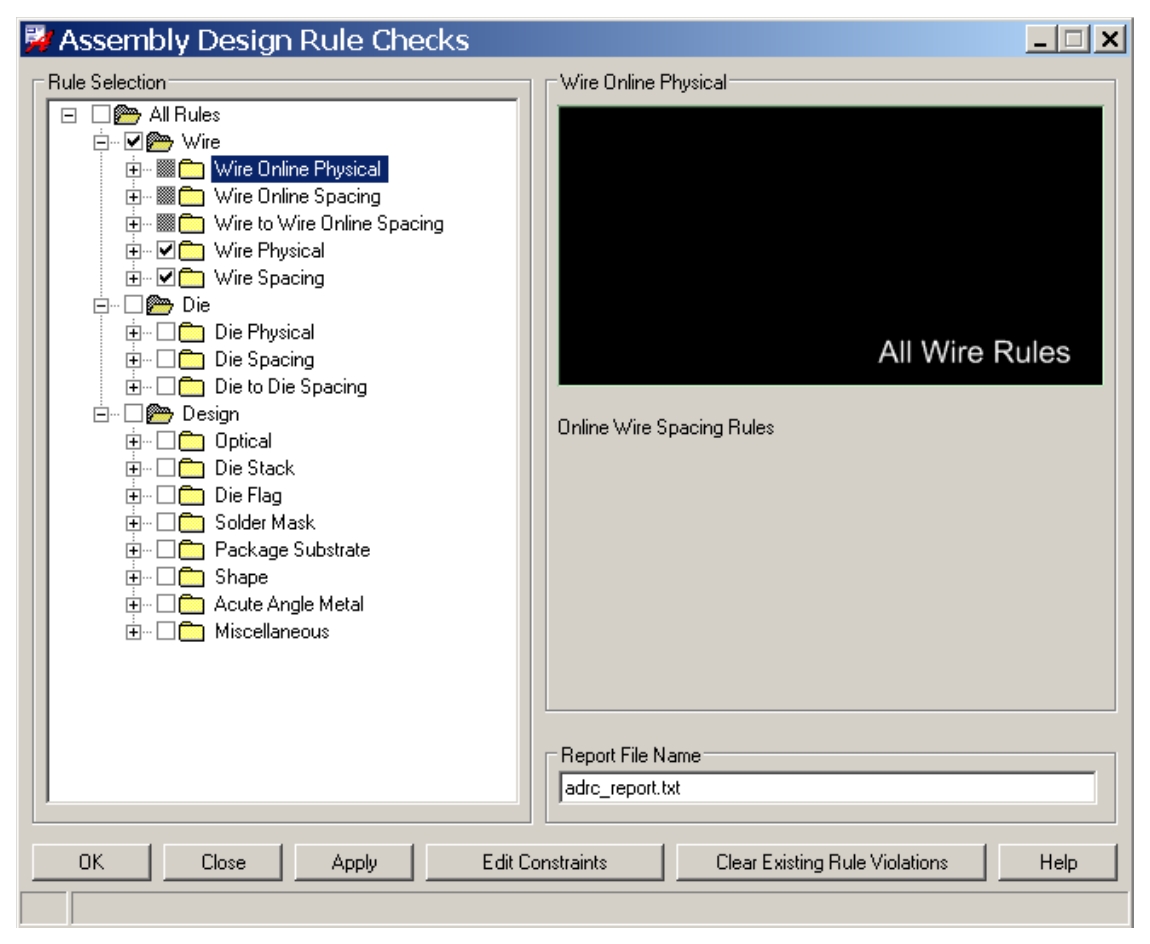

21.Manufacture→Assembly Rules Check命令

这个是SiP产品独有的装配检查,可方便地测试用户完成的设计能不能满足生产的需求。

选择Manufacture→Assembley Rules Check命令,弹出Assembly Design Rule Checks对话框,如图2-32所示。

图2-32 装配规则检查

主要有三大类规则,分别针对Wire、Die和Design。

(1)Wire的设计规则:

●Wire Online Physcial规则

Wire Length:表示要校验键合线的长度。通常根据键合线的直径不同,可连接的长度是不同的。这个规则可定义键合线最长的长度。

Wire Length:表示要校验键合线的长度。通常根据键合线的直径不同,可连接的长度是不同的。这个规则可定义键合线最长的长度。

Wire Maximum Angle to Die Edge:键合线到Die的最大允许角度。

Wire Maximum Angle to Die Edge:键合线到Die的最大允许角度。

●Wire Online Spacing规则

Finger To Component Edge Bonding:Finger到元件之间的距离。

Finger To Component Edge Bonding:Finger到元件之间的距离。

Wire to Die Pin Spacing:表示键合线到Die引脚之间的间距。

Wire to Die Pin Spacing:表示键合线到Die引脚之间的间距。

Wire to Finger Spacing:表示键合线到Bonding Finger之间的距离。

Wire to Finger Spacing:表示键合线到Bonding Finger之间的距离。

●Wire to Wire Online Spacing规则

Wire End to Wire End Spacing:检查键合线终端到终端的距离。

Wire End to Wire End Spacing:检查键合线终端到终端的距离。

Wire to Wire Spacing:检查键合线到键合线之间的距离,是二维的距离。

Wire to Wire Spacing:检查键合线到键合线之间的距离,是二维的距离。

●Wire Physical规则

Wire Length over Lower Die Stack Member:检查键合线重叠到下面的Die,或Spacer或Interposer的长度。这个值是比例值或具体的值。

Wire Length over Lower Die Stack Member:检查键合线重叠到下面的Die,或Spacer或Interposer的长度。这个值是比例值或具体的值。

Wire Length over Parent Die:检查键合线和本身Die的重叠长度。

Wire Length over Parent Die:检查键合线和本身Die的重叠长度。

Wire Maximum Angle to Finger:检查键合线同Bonding Finger之间的角度。

Wire Maximum Angle to Finger:检查键合线同Bonding Finger之间的角度。

●Wire Spacing规则

Wire Substrate End Distance Inside Solder Mask:检查键合线的终点是否在阻焊之内。

Wire Substrate End Distance Inside Solder Mask:检查键合线的终点是否在阻焊之内。

Wire to Component Spacing:键合线到元件的距离。

Wire to Component Spacing:键合线到元件的距离。

(2)Die的设计规则

●Die Physcial规则

Die Overhang:检查两个相邻Die、Spacer或Interposer外框之间的距离。

Die Overhang:检查两个相邻Die、Spacer或Interposer外框之间的距离。

Die Pad Pitch:检查Die引脚之间的间距。

Die Pad Pitch:检查Die引脚之间的间距。

Die Pad to Lower Die Overhang:检查Die引脚到下层Die外框之间的距离。

Die Pad to Lower Die Overhang:检查Die引脚到下层Die外框之间的距离。

Die Pad to Upper Die Spacing:下层的Die引脚到上层Die之间的距离。

Die Pad to Upper Die Spacing:下层的Die引脚到上层Die之间的距离。

●Die Spacing规则

Die to Connected Finger Spacing:检查Die到Bonding Finger之间的距离。

Die to Connected Finger Spacing:检查Die到Bonding Finger之间的距离。

Die to Finger Spacing:检查Die到Bonding Finger之间的距离。

Die to Finger Spacing:检查Die到Bonding Finger之间的距离。

Die to Package Edge Spacing:检查Die到基板边的距离。

Die to Package Edge Spacing:检查Die到基板边的距离。

●Die to Die Spacing规则

Die to Die Spacing,Connected Dies:检查有连接关系两个Die之间的距离。

Die to Die Spacing,Connected Dies:检查有连接关系两个Die之间的距离。

Die to Die Spacing,Unconnected Dies:检查没有连接关系两个Die之间的距离。

Die to Die Spacing,Unconnected Dies:检查没有连接关系两个Die之间的距离。

(3)Design的设计规则

●Optical规则

Wire to Die Pad Optional Shot:检查键合线跨过Die引脚的最小和最长的距离。

Wire to Die Pad Optional Shot:检查键合线跨过Die引脚的最小和最长的距离。

Wire to Finger Optional Short:检查键合线跨过Finger的最小和最长的距离。

Wire to Finger Optional Short:检查键合线跨过Finger的最小和最长的距离。

Wire to Wire Optional Short,Die to Die:检查键合线跨过键合线的最小和最长的距离。

Wire to Wire Optional Short,Die to Die:检查键合线跨过键合线的最小和最长的距离。

Wire to Wire Optical Short,Die to Substrate:检查键合线跨过键合线最小和最长的距离。

Wire to Wire Optical Short,Die to Substrate:检查键合线跨过键合线最小和最长的距离。

●Die Stack规则

Center to Center Delta,Extents Based:检查堆叠的Die、Spacer、Interposer中心距(Die、Spacer、Interposer外框的中心)在Top或者在Bottom之间的距离。

Center to Center Delta,Extents Based:检查堆叠的Die、Spacer、Interposer中心距(Die、Spacer、Interposer外框的中心)在Top或者在Bottom之间的距离。

Center to Center Delta,Pins Based:检查堆叠的Die、Spacer、Interposer中心距(Die、Spacer、Interposer引脚的中心)在Top或者在Bottom之间的距离。

Center to Center Delta,Pins Based:检查堆叠的Die、Spacer、Interposer中心距(Die、Spacer、Interposer引脚的中心)在Top或者在Bottom之间的距离。

Die Stack Height:检查堆叠Die的总高度。

Die Stack Height:检查堆叠Die的总高度。

Die Stack to Die Stack Spacing:检查两个堆叠的Die之间的距离。

Die Stack to Die Stack Spacing:检查两个堆叠的Die之间的距离。

●Die Flag规则

Die Flag to Die Flag Spacing:检查两个Die外框之间的距离。

Die Flag to Die Flag Spacing:检查两个Die外框之间的距离。

Die Flag to Discrete Component Pad Spacing:检查Die外框到分离器件之间的距离。

Die Flag to Discrete Component Pad Spacing:检查Die外框到分离器件之间的距离。

Die Flag to Finger Spacing:检查Die外框到Bonding Finger之间的距离(二维)。

Die Flag to Finger Spacing:检查Die外框到Bonding Finger之间的距离(二维)。

Die Flag to Package Edge Spacing:检查Die外框到基板外框之间的距离(二维)。

Die Flag to Package Edge Spacing:检查Die外框到基板外框之间的距离(二维)。

●Sloder Mask规则

Continuous Solder Mask Coverage Check:检查在Top和Bottom层的网络布线是否有阻焊。表示除去在Bonding Fingers、Pin起点,其他在Top和Bottom层的导体必须有阻焊。这个规则不检查电源和地网络,也不检查带有NO_SM_COVERAGE属性的网络。

Continuous Solder Mask Coverage Check:检查在Top和Bottom层的网络布线是否有阻焊。表示除去在Bonding Fingers、Pin起点,其他在Top和Bottom层的导体必须有阻焊。这个规则不检查电源和地网络,也不检查带有NO_SM_COVERAGE属性的网络。

Minimum Solder Mask Shape:检查阻焊层的Voids的最小宽度。

Minimum Solder Mask Shape:检查阻焊层的Voids的最小宽度。

Minimum Solder Mask Void:检查阻焊曾的Shape的最小宽度。

Minimum Solder Mask Void:检查阻焊曾的Shape的最小宽度。

Solder Mask to Die Edge Spacing:检查阻焊到Die外框的距离。

Solder Mask to Die Edge Spacing:检查阻焊到Die外框的距离。

Solder Mask to Package Substrate Edge Spacing:检查阻焊到基板边的距离。

Solder Mask to Package Substrate Edge Spacing:检查阻焊到基板边的距离。

Solder Mask to Solder Mask Spacing:检查阻焊到阻焊之间的距离。

Solder Mask to Solder Mask Spacing:检查阻焊到阻焊之间的距离。

●Package Substrate

Any Metal to Any Metal Spacing:检查任意金属到金属之间的间距。

Any Metal to Any Metal Spacing:检查任意金属到金属之间的间距。

Cline to Via Overlap:检查线到过孔之间的距离。主要指线和盲、埋孔之间的距离,仅考虑二维的距离,即当距离小于设定值就报DRC。并不考虑孔通线之间在Z轴上的距离。

Cline to Via Overlap:检查线到过孔之间的距离。主要指线和盲、埋孔之间的距离,仅考虑二维的距离,即当距离小于设定值就报DRC。并不考虑孔通线之间在Z轴上的距离。

Conductor to Package Substrate Edge Spacing:检查物理层到基板板边的距离。

Conductor to Package Substrate Edge Spacing:检查物理层到基板板边的距离。

Discrete Component Pad To Finger Spacing:检查分离器件的引脚到Bonding Finger之间的距离。

Discrete Component Pad To Finger Spacing:检查分离器件的引脚到Bonding Finger之间的距离。

Discrete Component to Package Edge Spacing:检查分离器件到基板边的间距。

Discrete Component to Package Edge Spacing:检查分离器件到基板边的间距。

Exposed Metal To Exposed Metal Spacing:没有阻焊的金属到没有阻焊的金属之间的距离。

Exposed Metal To Exposed Metal Spacing:没有阻焊的金属到没有阻焊的金属之间的距离。

Finger to Package Substrate Edge Spacing:检查Bonding Finger到基板边的距离。

Finger to Package Substrate Edge Spacing:检查Bonding Finger到基板边的距离。

Minimum Cline Segmeng:检查最小线段的长度。

Minimum Cline Segmeng:检查最小线段的长度。

Trace Extension From Finger:检查线从Bonding Finger的延伸段的长度。

Trace Extension From Finger:检查线从Bonding Finger的延伸段的长度。

Via To Package Substrate Edge Spacing:检查过孔到基板边的距离。

Via To Package Substrate Edge Spacing:检查过孔到基板边的距离。

●Shape

Actue Angle Shape Boundary:检查Shape的边沿是否有锐角。

Actue Angle Shape Boundary:检查Shape的边沿是否有锐角。

Minimum Shape Check:检查最小的Shape的宽度。

Minimum Shape Check:检查最小的Shape的宽度。

Minimum Void Check:检查在Shape上Voids的宽度。

Minimum Void Check:检查在Shape上Voids的宽度。

●Acute Angle Metal

Acute Angle Routing:检查线的锐角。

Acute Angle Routing:检查线的锐角。

Merged Metal Minimum Angle:检查两个需要合并的Shape之间的角度(不小于一个0~90度之间的值)。

Merged Metal Minimum Angle:检查两个需要合并的Shape之间的角度(不小于一个0~90度之间的值)。

Trace Minimum Angle To Pad:检查线和引脚(Via、Bonding Finger、Pin)之间的最小角度

Trace Minimum Angle To Pad:检查线和引脚(Via、Bonding Finger、Pin)之间的最小角度

Trace Minimum Angle To Shape:检查线和Shape之间的最小角度。

Trace Minimum Angle To Shape:检查线和Shape之间的最小角度。

Trace Minimum Angle To Trace:检查线和线之间的角度。

Trace Minimum Angle To Trace:检查线和线之间的角度。

●Miscellaneous

Conductor Shape Void Overlap:检查所有Shape的Voids在相邻的层重叠的部分。这个规则检查两个Voids的重叠,忽略层间的距离。

Conductor Shape Void Overlap:检查所有Shape的Voids在相邻的层重叠的部分。这个规则检查两个Voids的重叠,忽略层间的距离。

Degassing Void Overlap:检查因为Degass所产生的Voids重叠的部分。

Degassing Void Overlap:检查因为Degass所产生的Voids重叠的部分。

Tombstone Check:立碑检查,这个规则检查所有的两个引脚分离器件。规则要求两个引脚上的连线总宽度之比在一定的范围,避免立碑现象的产生。

Tombstone Check:立碑检查,这个规则检查所有的两个引脚分离器件。规则要求两个引脚上的连线总宽度之比在一定的范围,避免立碑现象的产生。

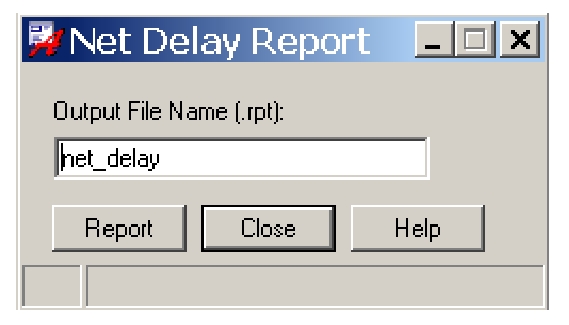

22.Report→Net delay report命令

这个命令主要是要报告非电源网络(没有定义电压值)的网络的延时的值。

(1)选择Report→Net Delay Report命令,弹出Net Delay Report对话框,如图2-33所示。

图2-33 网络延时报告

(2)选择Tools→Utilities→File Manager命令,在打开的对话框中选择net_delay.txt,双击打开该文件。

23.Reports→Conductor Length Report命令

这个命令主要是报告导体的长度。主要报告项目:Net Name Finger Wire SURFACE Conductor BASE Conductor Total Conductor Via Total Conductor+Wire+Via SURFACE Plating Total Plating Overall Total

(1)选择Reports→Conductor Length Report命令,弹出Save As对话框。

(2)单击Save按钮。

(3)选择Tools→Utilities→File Manager命令,双击conductor_length.txt文件。

24.Report→Wire Bond Report命令

这个命令主要报告键合线的情况,可产生二维和三维的键合线的长度报告。

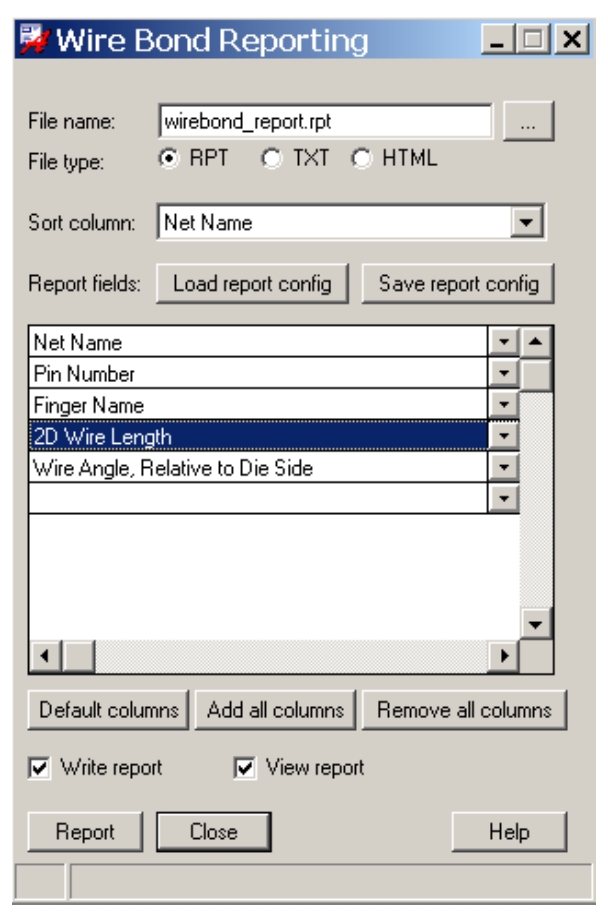

(1)选择Report→Wire Bond Report,弹出Wire Bond Reporting对话框,如图2-34所示。

图2-34 Wire Bond Reporting对话框

(2)在File name文本框中自动输入wirebond_report.rpt,用户也可输入新的名字。

(3)在File type中可选择RPT、TXT和HTML文件格式。

(4)在Report fields中,用户可选择需要报告的内容。

●Index

●Net name

●Pin number

●Pin Location

●Pin wire count

●End Pin Numberl

●End Pin Location

●Finger name

●Finger padstack

●Finger Location

●Finger wire count

●BGA ball Number

●BGA ball Location

●3D Wire Length

●2D Wire Length

●Wire Diameter

●Wire Type

●Wire Profile

●Wire Start Location

●Wire End Location

●Wire Material

●Wire Start Height,Relevative to Substrate

●Wire End Height,Relevative to Substrate

●Finger Angle,Relative to Die Side

●Finger Angle,Relative to Wire Angle

(5)用户选好后,单击Save report config。表示下次用户再需要输出相似的报告时,通过单击Report按钮,在弹出的Wirebond Report对话框中设置。

25.Report→Metal Usage Report命令

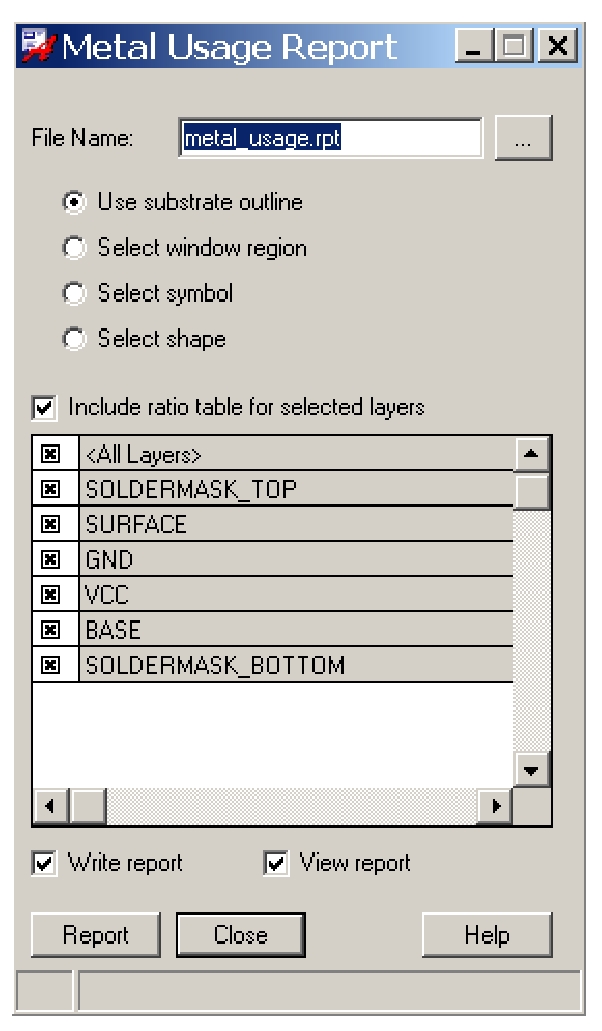

这个命令主要输出每个层或选择的区域金属占总面积的比例。

(1)选择Report→Metal Usage Report命令,弹出Metal Usage Report对话框,如图2-35所示。

图2-35 Metal Usage报告

(2)在File Name文本框中输入新的文件名或使用默认的文件名metal_usage.rpt。

(3)选择Use substrate outline表示用基板框来计算金属的使用率。

●Select window region表示选择对话框。

●Select symbol表示选择元件封装。

●Select shape表示选择Shape。

(4)Include ratio table for selected layers表示选择的层金属化的输出比率。

(5)单击Report按钮,弹出Metal Usage Report对话框。

26.Tools→Database Daily命令

记录基板设计的日记。

27.Tools→Derive Connectivity命令

可把Gerber文件转化成物理层的连线。

●Convert Lines to Connect Lines转化lines到Clines

●Convert Figure Stackups to Vias转化Figure到Via。

28.Tools→Utilities License used命令

(1)选择Tools→Utilities→License Used命令,弹出Cadence SiP Layout XL:License In Use对话框,如图2-36所示。

图2-36 License In Use 对话框

(2)表示当前使用的License是SiP_Layout_XL。