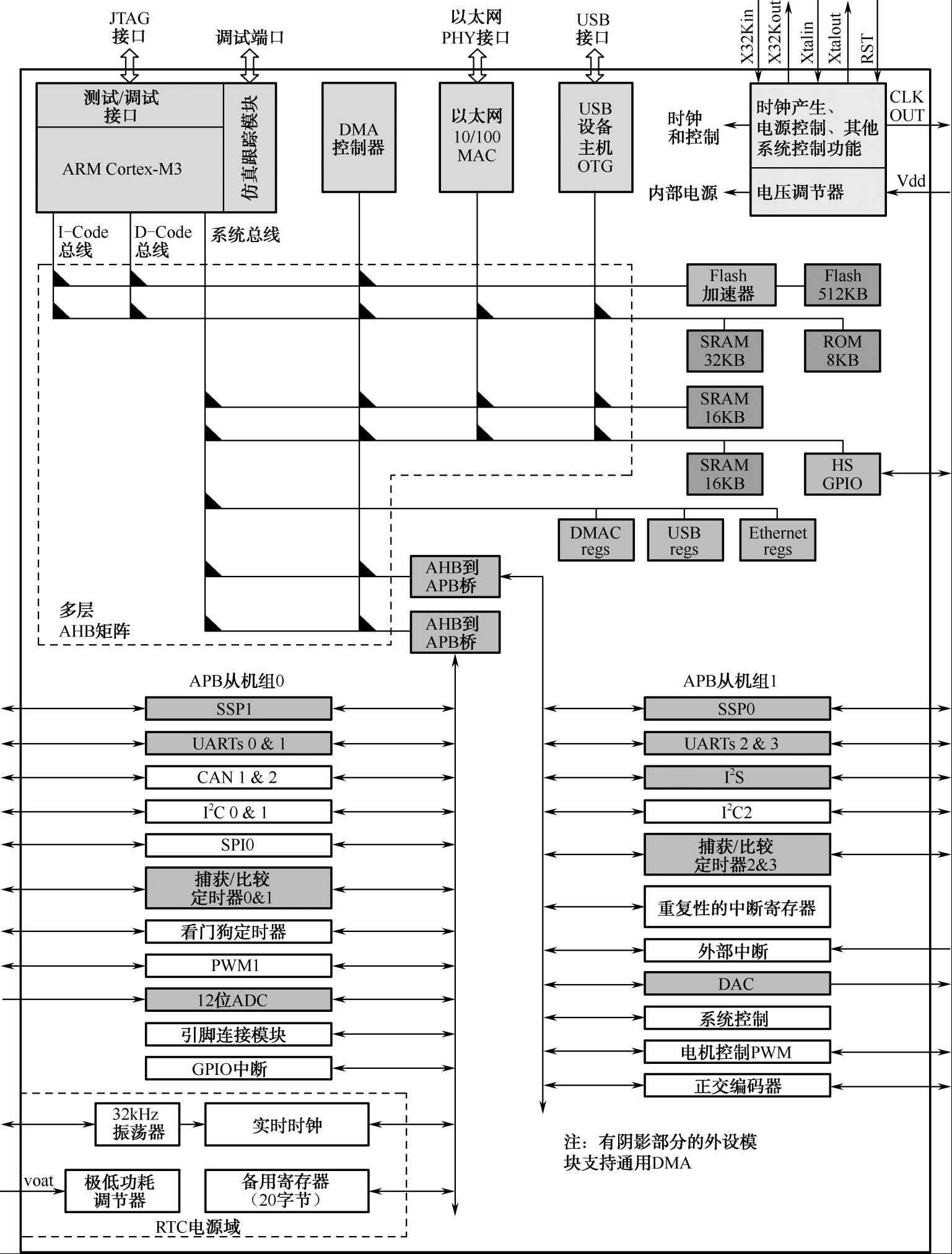

LPC17XX的结构图如图 2-1 所示。该结构图包含Cortex-M3 内核、多层AHB矩阵,以及各LPC17XX外设。

ARM Cortex-M3 包含三条AHB-Lite总线:一条系统总线,以及I-Code和D-Code总线。后两者的速率较快,且与测试/调试接口的用法类似:一条总线专用于指令取指(I Code);另一条总线用于数据访问(D-Code)。这两条内核总线允许同时执行操作,即同时对不同的设备目标进行操作。

图 2-1 LPC17XX的结构图

LPC1700 系列Cortex-M3 微控制器使用多层AHB矩阵来连接Cortex-M3 总线,并以灵活的方式将其他总线主机连接到外设,允许多层AHB矩阵上的各外设(使用了不同的从端口)同时被不同的总线主机访问,从而获得最优化的性能。

APB外设使用多层AHB矩阵的独立从机端口通过两条APB总线连接到CPU上,这就减少了CPU和DMA控制器之间的争用,可实现更好的性能。APB总线桥配置为写缓冲区操作,使得CPU或DMA控制器无须等待APB写操作结束。

LPC17XX的Cortex-M3 微控制器使用Cortex-M3 CPU的r2p0 版本,包含如下系统方面与调试方面的特征。

1.系统方面的特征

(1)嵌套的向量中断控制器(NVIC):NVIC包括系统定时器。

(2)唤醒中断控制器(WIC):WIC可更有效地将CPU从低功耗模式中唤醒。

(3)存储器保护单元(MPU)。

(4)ROM表:ROM表提供了调试部件到外部调试系统的地址。

2.调试方面的特征

(1)JTAG调试接口。

(2)串行线调试:串行线调试允许仅使用两条线进行调试操作,简单的跟踪功能可增加第三条线。

(3)嵌入式跟踪宏单元(ETM):ETM提供指令跟踪功能。

(4)数据观察点和跟踪(DWT)单元:DWT允许数据地址或数据值匹配为跟踪信息或触发其他事件。DWT包含 4 个比较器和计数器以用于特定的内部事件。

(5)指令跟踪宏单元(ITM):软件可写ITM以发送信息到跟踪端口。

(6)跟踪端口接口单元(TPIU):TPIU编码并向外面提供跟踪信息,这可以在串行线浏览器引脚(Serial Wire Viewer pin)或 4 并行跟踪端口上实现。

(7)Flash修补和断点(FPB):FPB可产生硬件断点并且在代码空间中重新映射特定的地址到SRAM作为更改非易失性代码的暂时方法。FPB包括 2 个文字比较器(literal comparator)和 6 个指令比较器。

LPC1700 系列Cortex-M3 微控制器含有 512KB的片上Flash存储器。一个新的 2-端口Flash存储器加速器通过两条快速AHB-Lite总线将其使用性能扩至极限。该存储器可用于存放代码和数据。对Flash存储器的编写可通过若干种方式来实现。LPC1700 系列Cortex-M3微控制器可通过串口进行在系统编程。应用程序也可以在运行时对Flash进行擦除和/或编程,从而给数据存储域的固件升级等操作带来极大的灵活性。

LPC1700 系列Cortex-M3 微控制器包含共计为 64KB的片上静态RAM存储器,包括主32KB SRAM(CPU和高速总线上的 3 个DMA控制器均可对其进行访问),以及另外两个各为 16KB的、位于AHB多层矩阵独立从机端口的SRAM模块。这种结构允许各自执行CPU和DMA访问操作,从而使得对总线主机的延迟变少或无延迟。