1.3 时钟资源和时钟管理模块 |

|

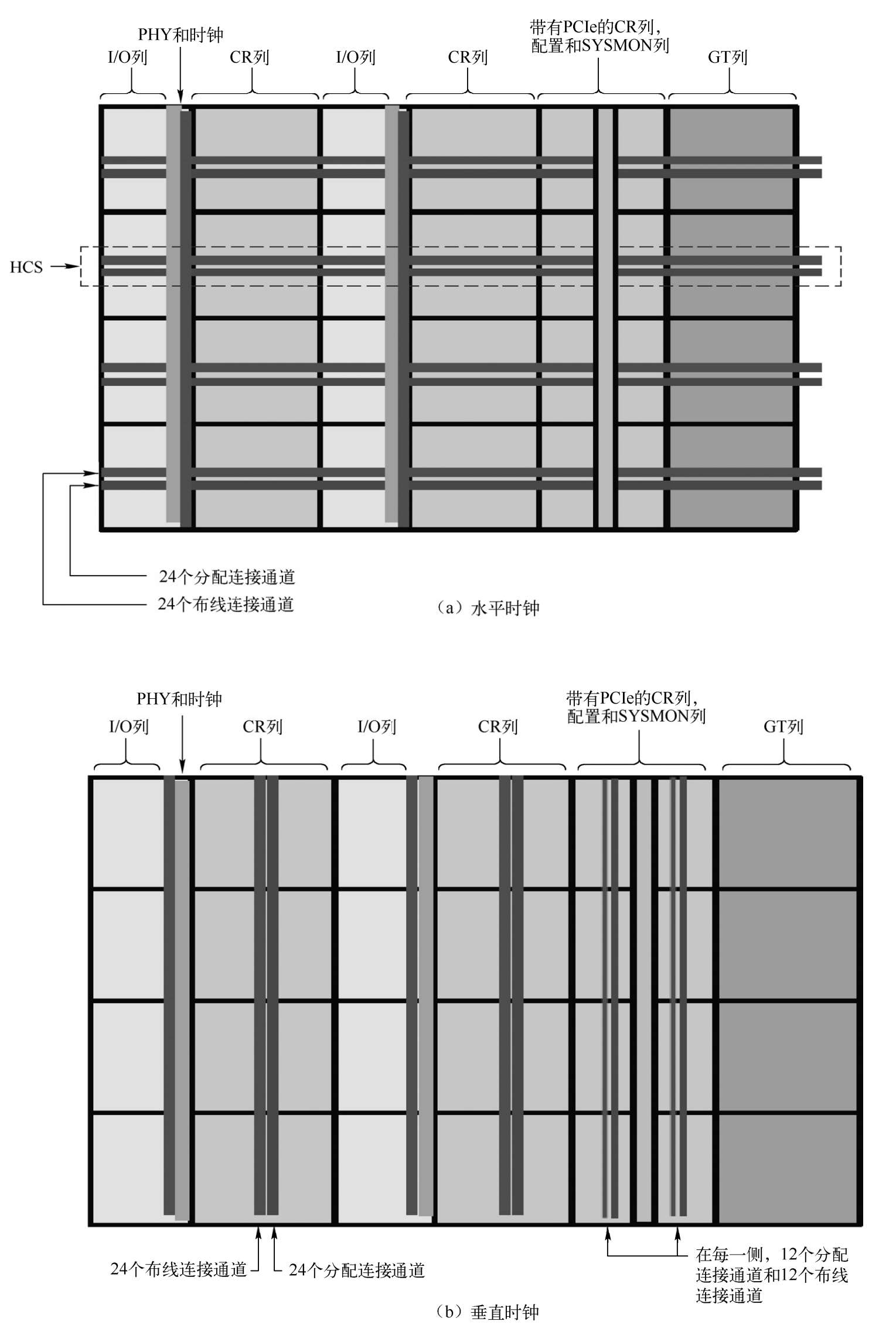

图1.10给出了Ultrascale结构的时钟结构图。从图中可以看出,基本的结构是由表示分段时钟行和列的CR块构成,CR以一个单元的方式排列,从而就可以构造出行和列。每个CR包含切片、DSP、36Kb BRAM。在每个CR中,所包含这些资源的数目在行方向上可能不同,但是在垂直方向是一样的。每个CR的高度是60个CLB、24个DSP和12个BRAM,从而为元器件构建了这些资源的列。从图中可以看出:

(1)在CR的中间插入I/O和GT列。

(2)与I/O列相邻的是PHY块,包含时钟管理单元(CMT)、全局时钟缓冲区、全局时钟复用结构和I/O逻辑管理功能。

(3)时钟结构存在一个单个的列,其包含配置逻辑、系统监控器和PCIe。

(4)一个水平时钟脊梁(Horizontal Clock Spine,HCS)穿过每行CR、I/O和GT的中间。HCS含有水平布线和分布引线,以及叶子时钟缓冲区,还有在水平/垂直布线和分配之间的时钟网络互连。

(5)垂直的布线连接通道和分配连接一列内所有的CR,而垂直布线跨越一个完整的I/O列。时钟结构包含24个水平布线连接通道和24个分布引线连接通道,以及24个垂直布线连接通道和24个分配引线连接通道。

(6)I/O由来自PHY的时钟直接驱动,或者通过布线引线由相邻的PHY驱动。

UltraScale结构的时钟资源包括:全局时钟输入、字节时钟输入、时钟缓冲和布线。

图1.10 Ultrascale结构的时钟结构

在每一个I/O组(Bank)上有四个全局时钟(Global Clock,GC)引脚,可以直接访问全局时钟缓冲区、MMCM和PLL。GC输入提供了高速访问全局和区域时钟资源的专用通道。

每个I/O组位于一个单个时钟域内,包含52 个I/O引脚。

字节通道时钟(DBC和QBC)输入引脚对是专用的时钟输入,直接驱动源同步的时钟到I/O块的比特切片。在存储器应用中,这些称为DQS。

PHY全局时钟包含BUFGCTRL、BUFGCE和BUFGCE_DIV。它们中的每一个,都可以被来自相邻Bank、MMCM、同一PHY的PLL和互连直接驱动。时钟缓冲区用于驱动整个芯片内的布线和分配资源。每个PHY包含24个BUFGCE、8个BUFGCTRL和4个BUFGCE_DIV。但是,在同一时刻,只有使用其中的24个缓冲区。

此外,还包含BUFCE_LEAF时钟缓冲区、BUFG时钟缓冲区和BUFG_GT时钟缓冲区。其中:

该时钟缓冲区提供对时钟1~8的分频,该分频时钟用于收发器时钟。

在叶子级别上,该时钟缓冲区提供了时钟的门控能力。

UltraScale结构的每个I/O组包含一个时钟管理单元(Clock Management Tile,CMT),每个CMT包含下面的功能单元:

(1)一个混合模式的时钟管理器(Mixed-mode ClockManager,MMCM)。

(2)两个相位锁相环(Phase Lock Loop,PLL),其目的主要用于为I/O生成时钟。但是,它也包含了用于内部结构的MMCM的一些功能集。

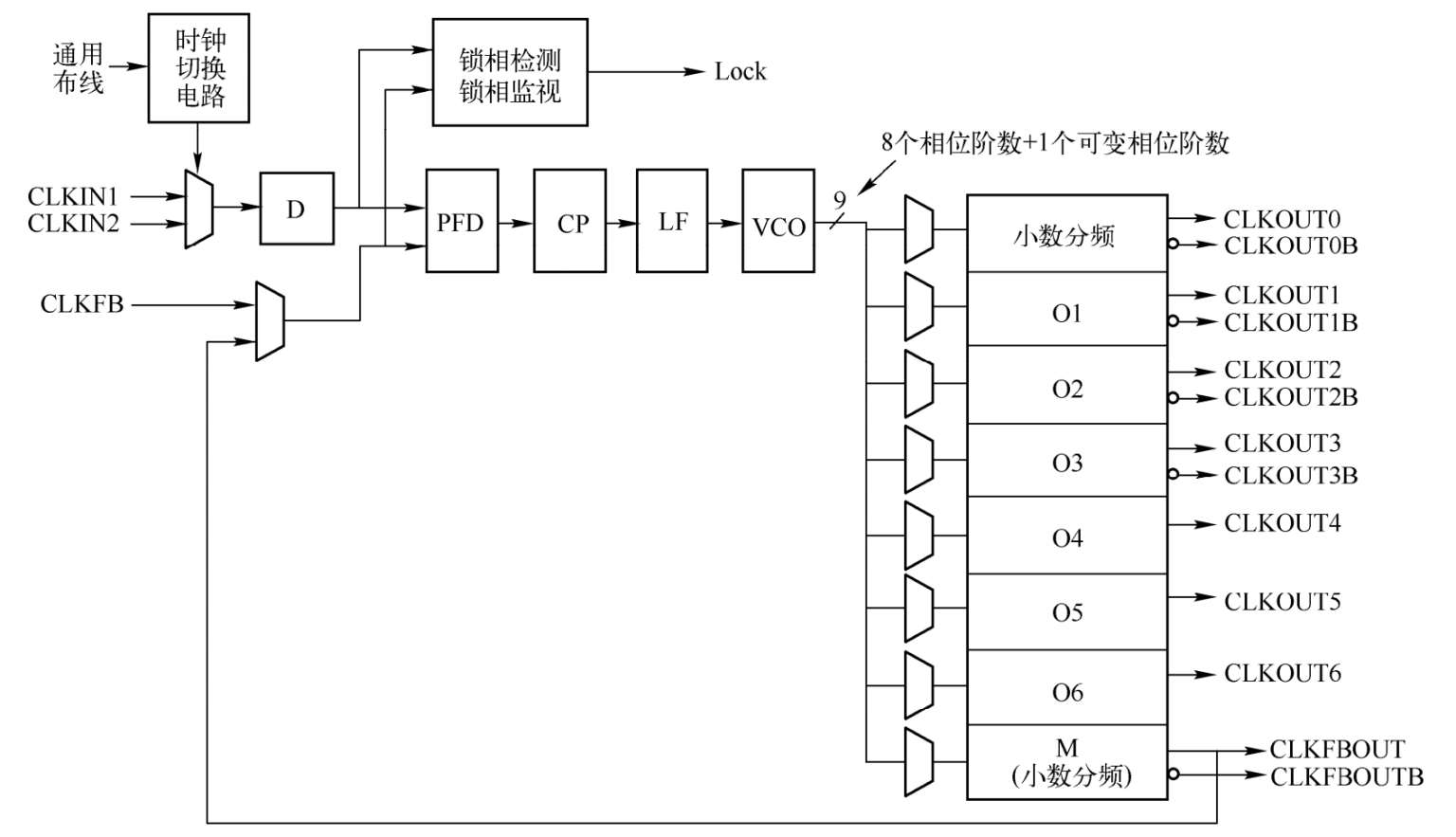

图1.11给出了MMCM的内部结构。MMCM用于宽范围频率的合成、内部或者外部时钟的抖动过滤器。MMCM的核心是一个压控振荡器(Voltage Controlled Oscillator,VCO),根据来自相位频率检测器(Phase Frequency Detector,PFD)的电压,VCO增加或者降低频率。

MMCM中有三个可编程的分频因子D、M和O。通过动态配置端口,就可以在配置和正常的操作期间,对其进行编程。预触发器D,用于降低输入时钟的频率,然后将其送入相位/频率比较器;反馈分频器M,由于在将它送给相位比较器之前,其将VCO的输出频率进行分频,所以其充当乘法器的角色。必须选择合适的D和M,以便VCO处于其指定的频率范围内。VCO有8个等间隔的输出相位(0°、45°、90°、135°、180°、225°、270°和315°)。可以选择其中的一个相位,来驱动一个输出分频器。可以在配置时,对每个分频器进行编程,分频因子为从1~128的任意整数。

图1.11 MMCM的内部结构

MMCM有3个输入抖动过滤器选项:低带宽、高带宽或者优化的模式。其中:

(1)低带宽模式有最好的抖动衰减。

(2)高带宽模式有最好的相位偏置。

(3)优化模式允许Vivado工具找到最好的设置。

MMCM也有一个小数计数器,它位于反馈路径(充当乘法器)或者输出路径。小数计数器允许非整数的1/8增量。因此,增加频率合成能力8倍。根据VCO的频率,MMCM也能够提供小幅度增量的固定相移或者动态的相移。在1600MHz时,相位移动时间增量是11.2ps。

PLL比MMCM的特性要少得多,在一个时钟管理单元内的两个PLL,其基本上是为专用的存储器接口电路提供必要的时钟。在PLL中心的电路类似于MMCM,带有PFD和VCO,以及可编程的M、D和O计数器。每个PLL有两个至FPGA结构的分频输出,以及到存储器接口电路的一个时钟加上一个使能信号。