3.4 设计综合和分析 |

|

本节将对设计进行综合。综合就是将RTL级的设计描述转换成门级的描述,在该过程中,将进行逻辑优化,并且映射到Xilinx器件原语(也称为技术映射)。

Vivado集成环境综合是基于时间驱动的,专门为存储器的利用率和性能进行了优化。综合工具支持SystemVerilog,以及VHDL和Verilog混合语言。该综合工具支持Xilinx设计约束XDC(该约束是基于工业标准的Synopsys设计约束SDC格式)。

在综合的过程中,需要知道下面的一些概念:

(1)在综合的过程中,综合工具使用XDC约束驱动综合优化,因此必须存在XDC文件。

(2)时序约束考虑。

① 首先必须综合设计,但没有用于约束编辑器的时序约束。

② 当综合后,可以使用约束向导初步定义时序约束。

(3)综合设置提供了对额外选项的访问。

(4)当打开被综合的设计后,注意设计流程管理器的变化。通过设置调试点,这样允许将调试特性集成在Vivado环境中。

本节将介绍设置综合选项参数的含义,便于后面在修改综合选项参数时,理解这些参数的含义。在“Flow Navigator”流程浏览器窗口界面下,找到并展开“Synthesis”选项。在展开项中,单击“Systhesis Settings”选项,弹出如图3.15所示的综合属性设置对话框。

图3.15 综合属性设置对话框

(1)在“Default constraint set”右侧通过下拉框,可以选择用于综合的多个不同的设计约束集合。一个约束集合是多个文件的集合,它包含XDC文件中用于该设计的设计约束条件。有两种类型的设计约束,如下所示。

① 物理约束:定义了引脚的位置和内部单元的绝对或者相对位置。内部单元包括块RAM、LUT、触发器和器件配置设置。

② 时序约束:定义了设计要求的频率。如果没有时序约束,Vivado集成设计环境仅对布线长度和布局阻塞进行优化。

通过选择不同的约束,得到不同的综合结果。再后面章节中,则会详细说明不同约束对设计性能的影响。

(2)在“Options”区域下的“Strategy”(策略)右侧的下拉框,选择用于运行综合的预定义综合策略。设计者可以定义自己的策略,后面将会介绍如何创建一个新的策略。表3.1给出了运行策略选项,默认设置和其他选项。

表3.1 运行策略选项,默认设置和其他选项

① tcl.pre和tcl.post:该选项是用于Tcl文件的挂钩,分别在综合前和综合后立即运行。

注意

注意

tcl.pre和tcl.post脚本中的路径是相对于当前工程的路径:

注

注

可以使用当前工程或者当前运行的DIRECTORY属性定义脚本中的相对路径:

② -flatten_hierarchy:设计者可从下面的选项设置。

● none:告诉综合工具不要将层次设计平面化(展开)。综合的输出和最初的RTL有相同的层次。

● full:告诉综合工具将层次化设计,充分展开,只留下顶层。

● rebuilt:当设置的时候,rebuilt允许综合工具展开层次,执行综合,然后基于最初的RTL,重新建立层次。这个值允许跨越边界进行优化。最终的层次类似于RTL,这是为了分析方便。

③ -gate_clcok_conversion:该选项是打开或者关闭综合工具对带有使能时钟逻辑转换的能力,门控时钟转换的使用也要求使用RTL属性。

④ -bufg:该选项控制综合工具推断设计中需要BUFG的个数。在网表内,设计中使用的其他BUFG对综合过程是不可见的时候,使用这个选项。

由“-bufg”后面的数字决定工具所能推断出的BUFG的个数。例如,如果“-bufg”选项设置为最多12个,在RTL内例化了3个BUFG,则工具还能推断出9个BUFG。

⑤ -fanout_limit:该选项指定在开始复制逻辑前,信号必须驱动的负载的个数。这个目标限制,通常是引导性质的。当工具确定必须复制逻辑时,就忽略该选项。

注

注

该选项不影响控制信号。例如,置位、复位和时钟使能。如果需要则使用MAX_FANOUT复制这些信号。

⑥ –directive:代替“effort_level”选项。当指定时,这个选项用不同的优化策略运行Vivado综合过程。它的值是“Default”和“RuntimeOptimized”时,更快地运行综合,以及进行较少的优化。

⑦ -fsm_extraction:该选项控制如何提取和映射有限自动状态机。当该选项为“off”时,将状态机综合为逻辑。或者设计者可以从“one-hot”、“sequential”、“johnson”、“jzaij”或者“auto”选项中指定状态机的编码类型,即one_hot、sequential、johnson、gray或者auto。

⑧ -keep_equivalent_registers:该选项阻止将带有相同逻辑输入的寄存器进行合并。

⑨ -resource_sharing:该选项用于在不同的信号间共享算术操作符。可选的值有“auto”、“on”和“off”。

注

注

选择“auto”时,根据设计要求的时序,决定是否采用资源共享;“on”表示总是进行资源共享;“off”表示总是关闭资源共享。

⑩ -control_set_opt_threshold:该选项设置时钟使能优化的门限,用于降低控制设制的个数,默认为1。给定的值是扇出的个数,Vivado工具将把这些控制设置移动到一个D触发器的逻辑中。如果扇出比这个值多,则工具尝试让信号驱动寄存器上的“control_set_pin”。

⑪ -no_lc:当选中该选项时,关闭LUT的组合,即不允许将两个LUT组合在一起构成一个双输出LUT。

⑫ -shreg_min_size:该选项推断SRL的门限,用于推断将寄存器链接起来映射到SRL的个数。

⑬ -max_bram:默认为-1,表示让工具尽可能选择BRAM,它由器件内BRAM的个数所限制。

⑭ -max_dsp:类似于“-max_bram”选项的含义,只是该选项用于DSP。

注

注

如果读者想更进一步了解每个选项的说明,则单击并高亮显示每个选项的名字。在选项下方的窗口内将给出每个选项的具体含义。

本节将详细介绍Vivado支持的属性,这些属性用在设计代码或者约束文件中,用于控制综合的结果。

注

注

不支持在RTL内嵌入时序约束。

该选项用于通知Vivado,D输入引脚能够接收相对于时钟源的异步数据,或者说寄存器是一个同步链上正在同步的寄存器。这个属性可以放置在任何寄存器上,其值为“FALSE”或者“TRUE”。

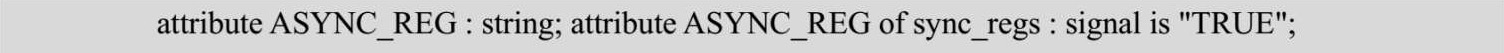

(1)ASYNC_REG Verilog例子

(2)ASYNC_REG VHDL例子

该属性是一个非常有用的调试属性,它用于关闭层次上的某一级,使能综合可以为该模块或者实体创建黑盒。该属性可以放置在一个模块、实体或者元器件上。由于该属性影响综合编译器,所有它只能在RTL级上设置。

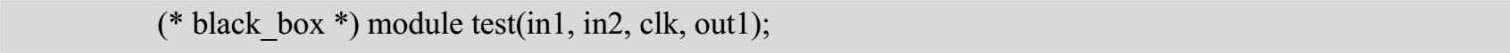

(1)BLACK_BOX Verilog 例子

注

注

不需要值。

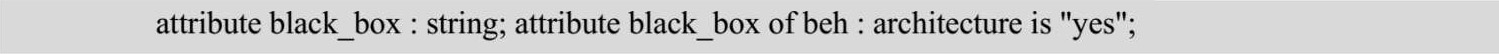

(2)BLACK_BOX VHDL 例子

该属性用于输入,确定所使用缓冲区的类型。对于时钟来说,Vivado综合工具默认使用IBUF/BUFG;而对于输入使用IBUF。其值可以是“ibuf”、“ibufg”和“none”。它放置在顶层端口,只能在RTL级描述中使用。

(1)BUFFER_TYPE Verilog例子

(2)VHDL 例子

使用该属性,用于替换“KEEP”或者“KEEP_HIERARCHY”属性,其原理和这两个属性一样。然而,不像这两个属性,“DONT_TOUCH”属性是向前注解到布局和布线,以阻止逻辑优化。其取值为“TRUE/FALSE”或者“yes/no”。该属性可以放置在信号、模块、实体或者元器件上。

(1)DONT_TOUCH Verilog例子

① wire例子

② module例子

③ instance例子

(2)DONT_TOUCH VHDL例子

① signal 例子

② entity例子

该属性用于控制状态机的编码。典型的,基于启发式的方法,Vivado工具为状态机选择一个编码协议。在指定的某些编码类型下,这些设计类型可以工作得更好。该属性放置于状态寄存器上,有效值为“one_hot”、“sequential”、“Johnson”、“gray”和“auto”。可以在RTL级或者XDC中设置该属性。

(1)FSM_ENCODINGVerilog 例子

(2)FSM_ENCODINGVHDL 例子

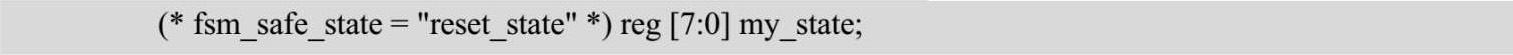

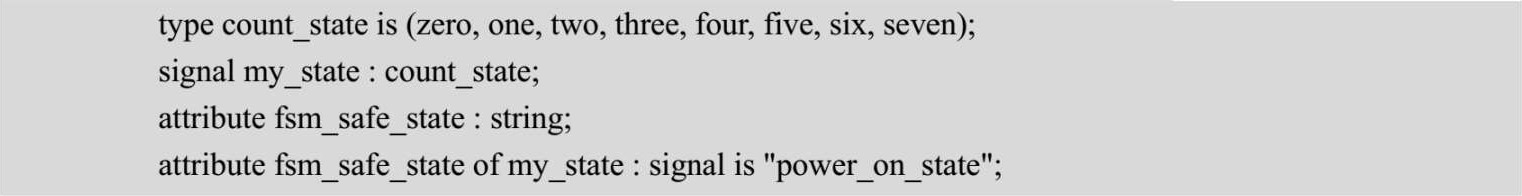

当检测到状态机中有非法状态时,该属性告诉综合工具,插入逻辑到状态机中。当下一个时钟周期到来时,将其置为一个已知状态。例如,如果one hot编码,而进入“0101”状态(对于onehot编码,这是非法的),则状态机应该能够恢复。该属性放在状态寄存器上,其有效值为“reset_state”或者“power_on_state”,该属性只能用于RTL级。

(1)FSM_SAFE_STATEVerilog例子

(2)FSM_SAFE_STATEVHDL 例子

该属性表示在case、casex或者casez描述中,给出了所有可能情况的取值。如果指定了case的值,Vivado综合工具则不能创建额外的逻辑用于case值。该属性放置在case描述中,由于该属性影响编译器,可以改变设计的逻辑行为。因此,它只能在RTL中设置。

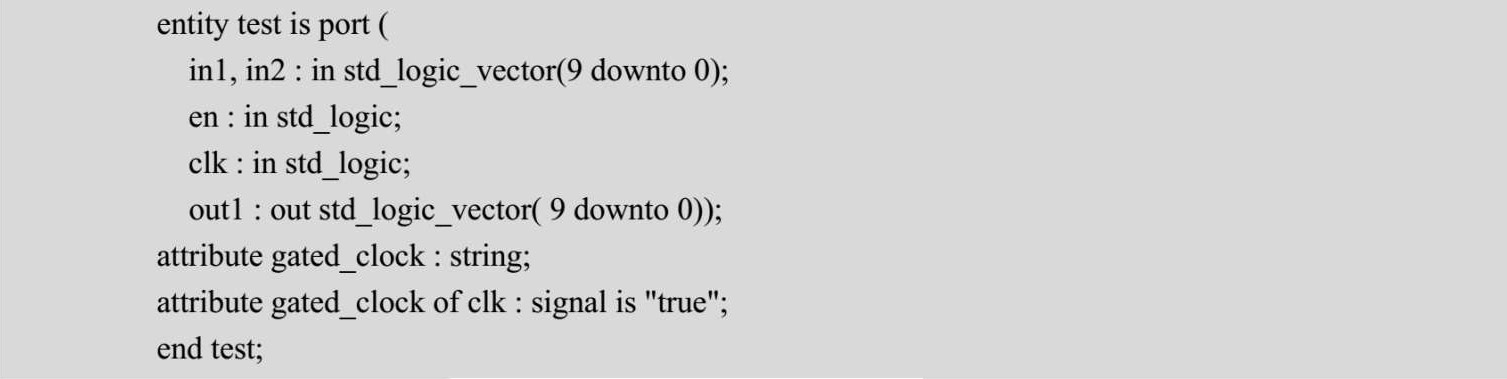

Vivado允许门控时钟的转换。有两项用于执行这个转换:

(1)Vivado GUI的开关,用于指导工具尝试转换。在Vivado主界面左侧“Flow Navigator”窗口下,找到“Synthesis Settings”选项。在选项设置中,将“-gated_clock_conversion”选项设置为“off”、“on”和“auto”。当选择“auto”时,如果发生下面事件,则进行转换:

① gated_clock属性设置为true。

② Vivado综合工具检测到门,并且设置了有效的时钟约束。

该选项是让工具做出决定。

(2)RTL属性指导工具确认在门控逻辑中,指示哪个信号是时钟。该属性放置在时钟信号或者端口上。

① GATED_CLOCK Verilog例子

② GATED_CLOCK VHDL 例子

IOB不是综合属性,它被下游的实现工具使用。这个属性指示是否将寄存器放入I/O缓冲区。其值为“true”或者“false”,将这个属性放置在需要寄存器的I/O上。可以在RTL级或者XDC中设置该属性。

(1)IOB Verilog例子

(2)IOB VHDL 例子

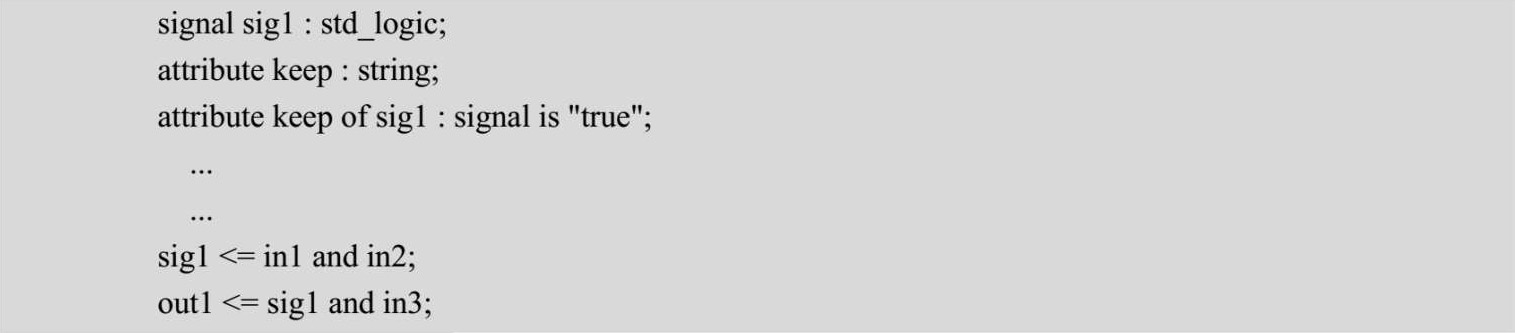

该属性用于阻止优化,即信号被优化或者被吸收进逻辑块中。该属性告诉Vivado综合工具保持放置信号,则该信号将出现在网表中。其取值为“true”或者“false”。该属性可以放置在信号、寄存器或者线网络上。Xilinx推荐在RTL中设置该属性。

注意

注意

该属性不强迫布局和布线工具保持该信号。在这种情况下,使用“DONT_TOUCH”属性。

(1)KEEP Verilog 例子

(2)KEEP VHDL 例子

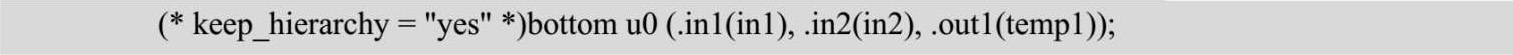

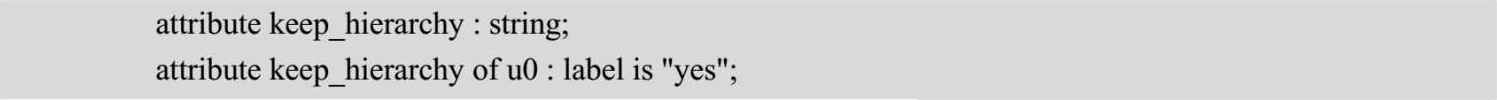

该属性用于阻止在层次边界的优化。Vivado综合工具尝试保持在RTL级所定义的层次,但是由于QoR的原因,它会展开它们。如果在实例上放置了该属性,综合工具将保持静态级的逻辑层次。它不能用于那些描述控制三态输出和I/O缓冲区的模块。该属性可以放置在实例的模块或者结构级上,只能在RTL级使用该属性。

(1)KEEP_HIERARCHY Verilog例子

① On module

② On instance

(2)KEEP_HIERARCHY VHDL例子

① On module

② On instance

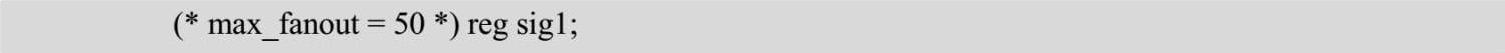

该属性告诉综合工具,对寄存器和信号的扇出进行限制。可以在RTL中指定,将其作为工程的一部分。其值为整数,该属性只能用于寄存器和组合信号。可以在RTL或者XDC中设置该属性。该属性可以覆盖在综合属性设置中对“-fanout_limit”的设置的值。

(1)MAX_FANOUT Verilog 例子

(2)MAX_FANOUT VHDL 例子

该属性用来指示以并行结构构建case描述。该属性只能用于RTL描述中。

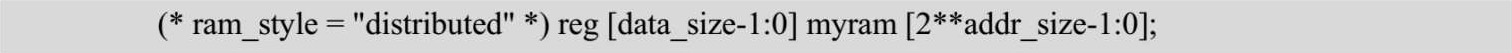

该属性用于帮助Vivado综合工具推断存储器的实现方式。可用的值为“block”或者“distributed”。可以在RTL或者XDC中设置该属性。

(1)RAM_STYLE Verilog 例子

(2)RAM_STYLE VHDL 例子

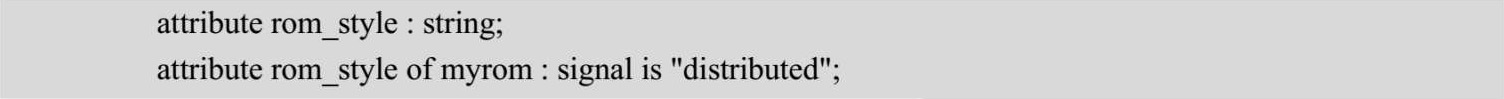

该属性用于帮助Vivado综合工具推断ROM存储器的实现方式。可用的值为“block”或者“distributed”。可以在RTL或者XDC中设置该属性。

(1)ROM_STYLE Verilog 例子

(2)ROM_STYLE VHDL例子

该属性用于帮助Vivado工具确认是否推断SRL结构,可接受的值是“yes”或者“no”。该属性放在用于SRL的信号上或者带有SR的模块或者实体上。可以在RTL或者XDC中设置该属性。

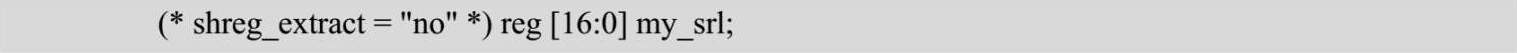

(1)SHREG_EXTRACTVerilog例子

(2)SHREG_EXTRACTVHDL例子

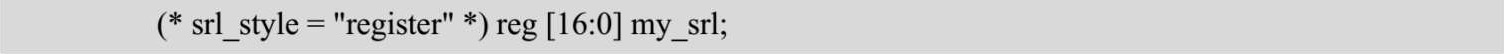

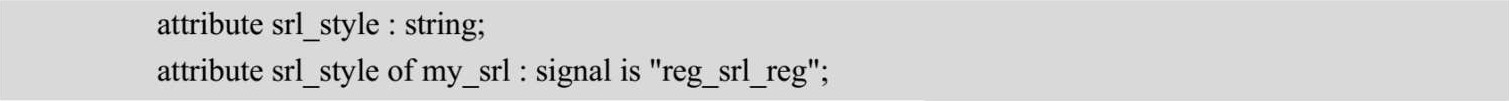

该属性告诉综合工具,如何推断在设计中发现的SR。可用的值为“register”、“srl”、“srl_reg”、“reg_srl”和“reg_srl_reg”。将该属性放置在声明为SRL的信号上。只能在RTL中设置该属性。此外,该属性只能用于静态SRL。

(1)SRL_STYLE Verilog 例子

(2)SRL_STYLE VHDL例子

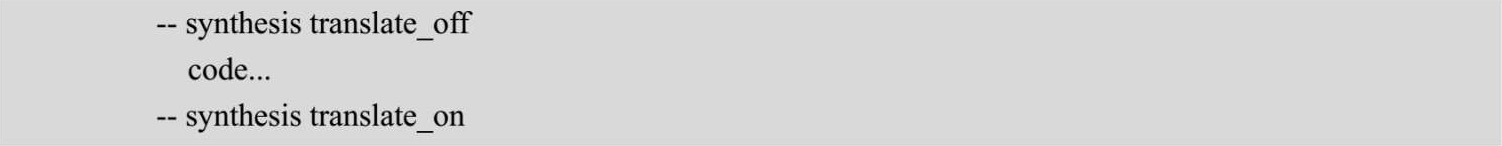

该属性告诉Vivado综合工具忽略代码块,在RTL中的注释中给出该属性。注释通过使用“synthesis”、“synopsys”和“pragma”关键字开始。该属性只能在RTL中设置。

(1)TRANSLATE_OFF/TRANSLATE_ON Verilog例子

(2)TRANSLATE_OFF/TRANSLATE_ON VHDL例子

该属性告诉Vivado综合工具如何处理综合算术指令。默认的,乘法、乘法-加法、乘法-减法、乘法-累加使用DSP48块。加法器、减法器和累加器可以使用这些块,但是默认使用分布逻辑实现。该属性强迫使用DSP48块,可用的值是“yes”和“no”。该属性可以放置在RTL内的信号、结构和元件、实体和模块上。可以在RTL和XDC中设置该属性。

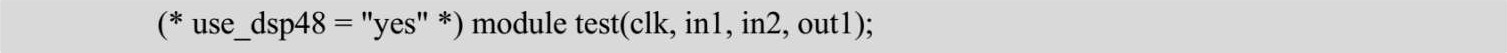

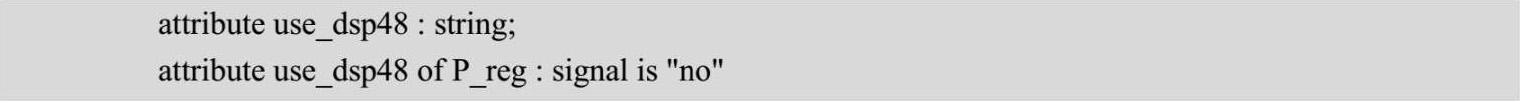

(1)USE_DSP48 Verilog例子

(2)USE_DSP48 VHDL例子

本节将对设计进行综合。实现对设计进行综合的步骤如下所示。

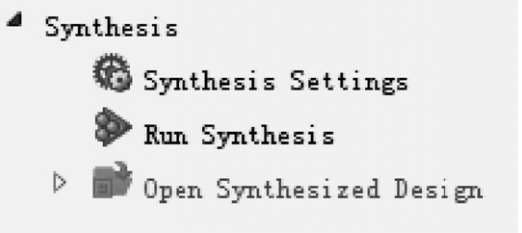

第一步 :如图3.16所示,在流程处理窗口下找到“Synthesis”选项,并展开。或者在Tcl命令行中,输入“launch_runs synth_1”脚本命令,运行综合。

图3.16查看RTL级网表

注

注

如果前面已经运行过综合,在重新运行综合前,必须执行“reset_run synth_1”脚本命令,然后再执行“launch_runs synth_1”脚本命令。

第二步 :在展开项中,选择“Run Synthesis”选项,并单击鼠标左键,开始对设计进行综合。

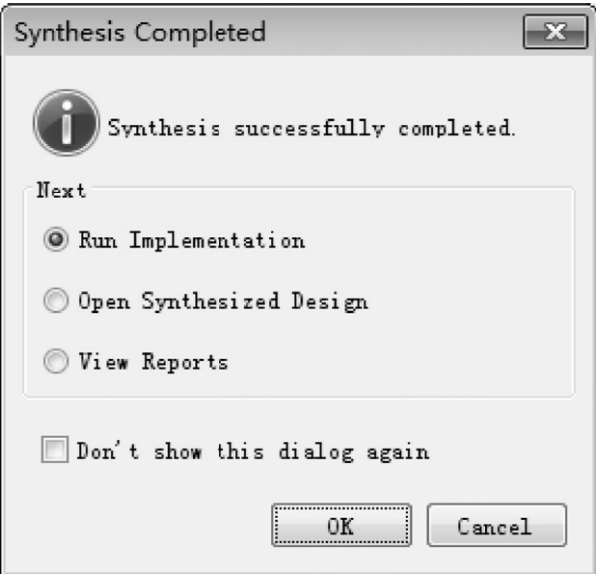

第三步 :当对设计综合完成后,弹出如图3.17所示的“Synthesis Completed”(综合完成)对话框,该对话框提供了3个选项:

图3.17 “Synthesis Completed”(综合完成)对话框

(1)Run Implementation(运行实现过程)。

(2)Open Synthesized Design(打开综合后的设计)。

(3)View Reports(查看报告)。

先选择“Open Synthesized Design”选项。

第四步 :单击图3.17中的【OK】按钮。

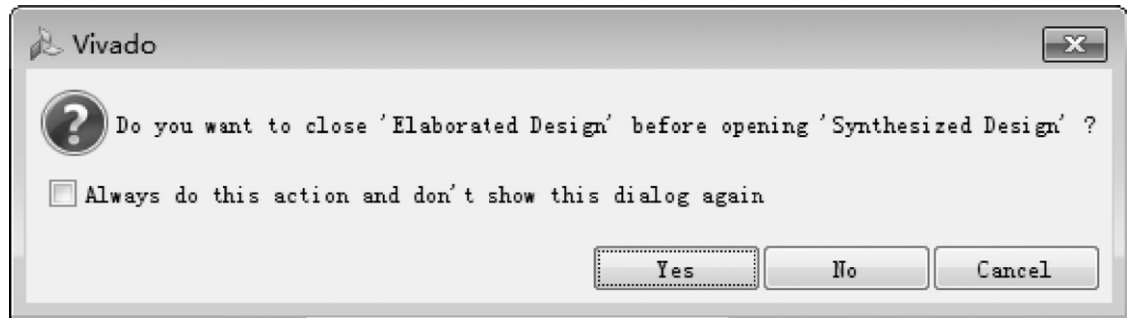

第五步 :如图3.18所示,弹出“Vivado”对话框,提示关闭前面执行“Elaborated Design”所打开的原理图界面,单击【Yes】按钮,Vivado开始执行打开综合后设计的过程。

图3.18“Vivado”对话框

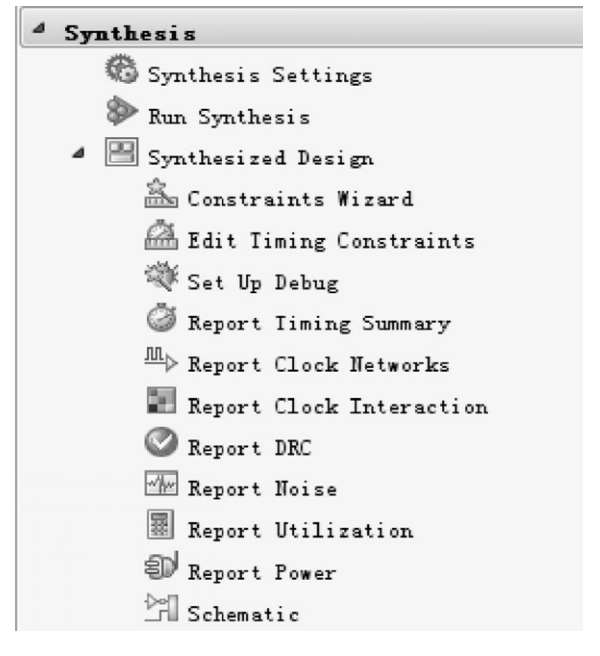

第六步 :当执行完该过程后,如图3.19所示,可以展开“Synthesized Design”选项。在“Synthesized Designed”选项中提供了下面的选项:

图3.19 Synthesis Design选项列表

(1)Constraints Wizard(约束向导)。

(2)EditTiming Constraints(编辑时序约束)。该选项用于启动时序约束标签。

(3)Set Up Debug(设置调试)。该选项用于启动标记网络视图界面,那些标记过的网络视图将用于调试目的。

(4)Report Timing Summary(报告时序总结)。该选项生成一个默认的时序报告。

(5)Report Clock Networks(报告时钟网络)。该选项生成该设计的时钟树。

(6)Report Clock Interaction(报告时钟相互作用)。该选项用于在时钟域之间,验证路径上的约束收敛。

(7)Report DRC(报告DRC)。该选项用于对整个设计执行设计规则检查。

(8)Report Noise(报告噪声)。该选项用于对设计中的输出和双向引脚执行一个SSO分析。

(9)Report Utilization(报告利用率)。该选项用于生成一个图形化的利用率报告。

(10)Report Power(报告功耗)。该选项用于生成一个详细的功耗分析报告。

(11)Schematic(原理图)。该选项用于打开原理图视图界面。

第七步 :在图3.19所示的界面内,单击“Schematic”选项。如图3.20所示,显示了对该设计综合后的网表结构。

图3.20 该设计的完整网表结构

思考题3.1: 为什么是这种结构?(提示:FPGA是基于查找表结构)

提示

提示

当综合后,设计表示为层次和基本元素的互连网表。对应于:

(1)模块(Verilog HDL中的module)/实体(VHDL中的Entity)的实例。

(2)基本的元素,包括:

① 查找表LUT、触发器、进位链元素、宽的多路复用器MUX。

② 块RAM、DSP单元。

③ 时钟元素(BUFG、BUFR、MMCM)。

④ I/O元素(IBUF、OBUF、I/O触发器)。

(3)在尽可能的情况下,对象的名字与详细描述网表中的名字相同。

思考题3.2: 看看输入缓冲区、输出缓冲区的结构,分析一下该设计的逻辑通路。

第八步 :查看每个LUT的内部映射关系。在图3.20内分别用鼠标选择相应的LUT,总共6个LUT。先选择最上面的一个LUT。如图3.21所示,在Vivado源窗口下方的“CellProperties”,选择“Truth Table”标签,可以看到逻辑表达式0=I0&I1,下面给真值表映射。

图3.21 LUT的内部映射关系

思考题3.3: LUT内部实现的逻辑关系?(提示:在每个查找表内实现了该设计的每种逻辑运算关系)

思考题3.4: 在前面的设计中,可以看到Verilog的描述方法,类似于C语言。C语言通过按位逻辑运算符实现逻辑运算。用FPGA实现和C语言在CPU上实现有什么本质的区别?

注

注

C语言在CPU上实现,靠程序计数器,串行执行;而FPGA上数字逻辑的实现是并行实现的,由逻辑流推动。其处理数据的能力在同样的频率下,要比CPU快6倍。所以这也是FPGA在进行海量数据处理的巨大优势,请读者务必认真体会。

本节将查看综合后的报告。从图3.19中可以看出,Vivado可以提供最重要的报告,而Vivado当前工程窗口底部的“Reports”标签窗口下,包含了其他有用的报告。如图3.22所示,在“Reports”标签窗口下的“Synth Design”选项下,提供了下面的报告选项:

(1)HDL文件的综合、综合的过程、读取时序约束、来自RTL设计中的RTL原语。

(2)时序优化目标、技术映射、去除引脚/端口、最终单元的使用(技术映射)。

以表格的形式给出技术映射单元的使用情况。图3.23给出了利用率报告,内容包括切片逻辑、存储器、DSP切片、IO、时钟,以及设计中所用到的其他资源。

图3.22 “Reports”标签窗口内容

图3.23资源使用情况报告

思考题3.5: 读者阅读该报告,查看该设计占用资源的情况。