这部分内容主要包括计算机体系结构与组成结构、CPU特性、指令系统、流水线技术,以及并行技术等方面的知识。在历年的考试中,涉及本部分的知识点的考题占整个“计算机硬件基础”知识的约一半。本部分的考题主要以知识性记忆为主,特别值得重视的知识点包括对各种分类的灵活判断、围绕CPU特性的计算与流水线执行指令的时间计算。另外,本节列出的针对7个考点出题的频度相差不大,每年都会轮换,没有很明显的侧重点。

难度系数:☆☆ 考查频度:☆☆ 考查权重:☆☆

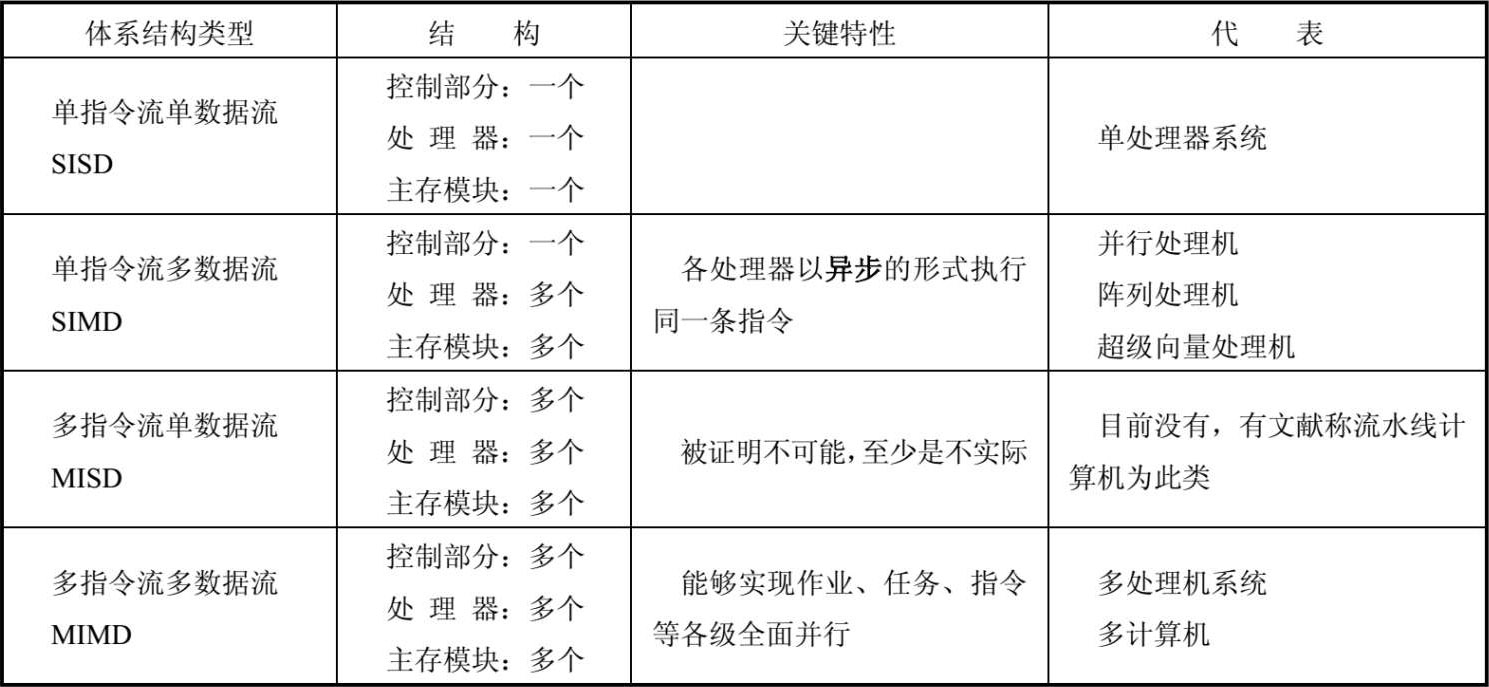

本知识点的考查关键在于每种Flynn分类的结构特点、代表性系统及其关键特性,主要是记忆型题目。

计算机体系结构是计算机系统的概念性结构和功能特性。而常见的分类法包括Flynn、冯氏分类两种。

(1)Flynn分类法:它是根据指令流、数据流和多倍性三方面进行分类的,如表3-1所示。

表3-1 Flynn分类法

(2)冯氏分类法:以计算机系统在单位时间内所能够处理的最大二进制位数分类。它将系统分为字串位串(字宽=1,位宽=1)、字并位串(字宽>1,位宽=1)、字串位并(字宽=1,位宽>1)、字并位并(字宽>1,位宽>1)4种。

难度系数:☆ 考查频度:☆ 考查权重:☆

对于本知识点,重点在于记忆5个部件的名称,以及它们的子组成部分的名称,能够正确地做出选择。

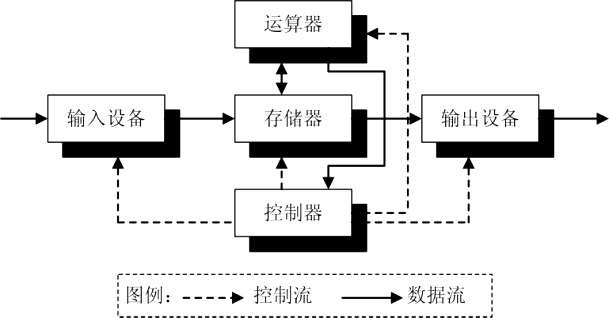

直到今天为止,计算机硬件系统还是依照冯·诺依曼所设计的体系结构,即由运算器、控制器、存储器、输入设备和输出设备5大部件组成,如图3-2所示。

图3-2 计算机硬件组成结构示意图

其中, 运算器和控制器 组成中央处理器(CPU)。运算器负责完成算术、逻辑运算功能,通常由 ALU (算术/逻辑单元)、 寄存器 、多路转换器、 数据总线 组成;控制器则负责依次访问程序指令,进行指令译码,并协调其他设备,通常由 程序计数器 (PC)、指令 寄存器 、 指令译码器 、状态/条件寄存器、时序发生器、 微操作信号发生器 组成。

其中总线是一种内部结构,它是CPU、内存、输入、输出设备传递信息的公用通道,主机的各个部件通过总线相连接,外部设备通过相应的接口电路与总线相连接,从而形成了计算机硬件系统。

系统总线包含有三种不同功能的总线,即数据总线(DataBus,DB)、地址总线(Address Bus,AB)和控制总线(Control Bus,CB)。

· “数据总线(DB)”用于传送数据信息。

· “地址总线(AB)”是专门用来传送地址的。

· “控制总线(CB)”用来传送控制信号和时序信号。

难度系数:☆☆ 考查频度:☆ 考查权重:☆

本知识点的重点在于理解指令周期、总线周期、时间周期等概念,能够根据它们来计算执行时间、传输速度等。

对于CPU而言,有许多与工作速度相关的特性,这也是计算机硬件基础知识中很重要的一个知识点。

· 指令周期:是指取出并执行一条指令所需的时间,也称为机器周期。

· 总线周期:是指CPU从存储器或I/O端口存取一个字节所需的时间,也称为主振周期。

· 时钟周期:指的是CPU处理动作的最小单位,通常我们说的赛扬1.8GHz,2.0GHz就是指每秒有1.8G、2.0G个时钟周期。

它们之间的关系是: 一个指令周期可以划分为一个或多个总线周期 ,根据指令的不同,需要的总线周期也不同;而 一个总线周期又可以分为几个时钟周期 ,通常是4个时钟周期,但也有些计算机可能不同。该知识点的考查点通常包括以下内容。

(1)计算总线数据传输速率。

比较简单,只要结合公式进行计算:

总线数据传输率=时钟频率/每个总线包含的时钟周期数×每个总线周期传送的字节数

例如:某系统总线的一个总线周期包含3个时钟周期,每个总线周期中可以传送32位数据。若总线的时钟频率为33MHz,则总线的带宽(即传输速度)应该是多少呢?根据上述公式得出:33MHz/3×32b=11MHz×4B=44MB/s。要注意的是各种进制的单位转换,这是历来考生容易错的知识点。

(2)计算系统速度(通常是指令/秒、事务项/秒)。

计算每秒执行的指令数的关键,在于找出平均每条指令需要多少个总线周期,然后将总线周期数(时钟频率/每个总线包含的时钟周期数)除以这个平均周期数,就可以计算出来。但通常不同的指令需要的总线周期数是不同的,这就需要有各种指令需要的总线周期数,以及指令的频度,通过计算得出。

每秒指令数=时钟频率/每个总线包含的时钟周期数/指令平均占用总线周期数

事务项通常是由指令构成的,只要计算整个事务项的指令需要花费多少时间即可。

难度系数:☆☆ 考查频度:☆ 考查权重:☆☆☆

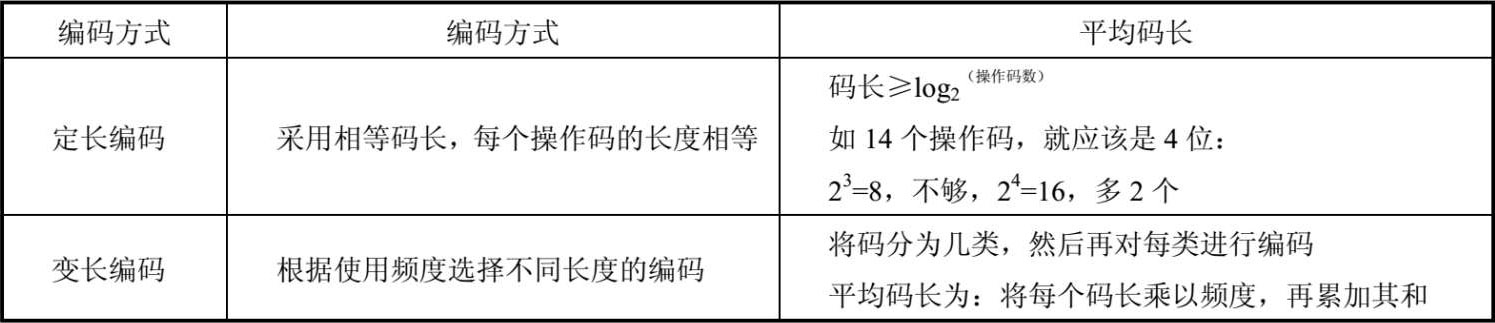

本知识点的重点在于掌握定长编码和变长编码的含义和码长的计算,以及指令的几种常见的寻址方式的特点。

在计算机中,CPU会定义出自己特定的指令系统,不过都遵循着统一的标准格式。指令的基本格式是由操作码和地址码两个部分组成的。操作码指出该指令要完成什么操作,地址码则提供原始的数据。指令系统中定义操作码的方式可以分为规整型(定长编码)和非规整型(变长编码)两种,如表3-2所示。

表3-2 指令系统定义操作码

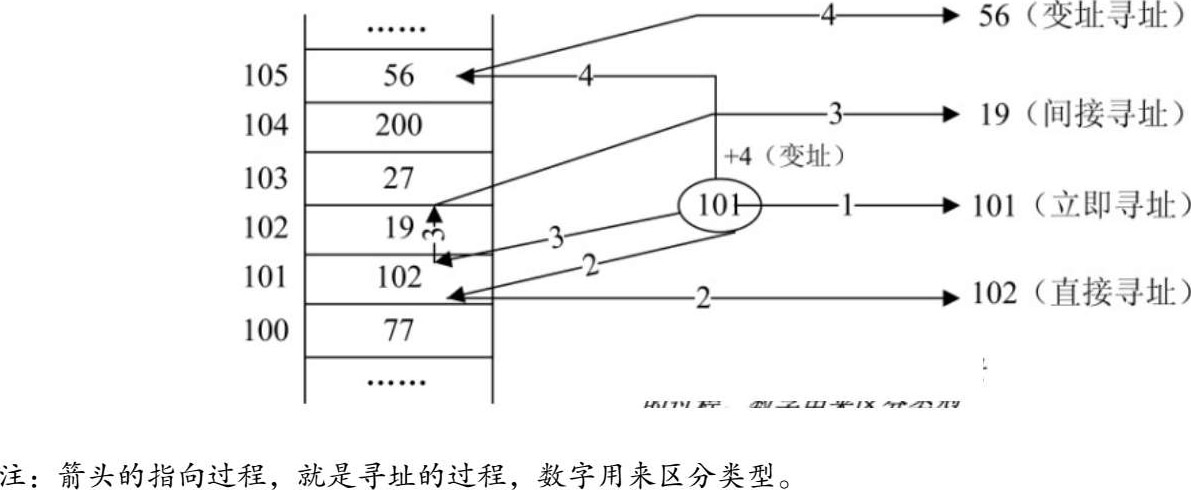

在指令系统中用来确定如何提供操作数或提供操作数地址的方式称为寻址方式和编址方式。操作数可以存放在CPU中的寄存器(用寄存器名操作)、主存储器(指出存储单元地址)、堆栈(先进后出的存储机制,用栈顶指针SP来标出其当前位置)、外存储器或外围设备中。不过在运算时,数据均在主存储器中,操作数可以采用以下几种寻址方式。

· 立即寻址:直接给出操作数而非地址。

· 直接寻址:直接给出操作数地址或所在寄存器号(寄存器寻址)。

· 间接寻址:给出的是指向操作数地址的地址。

· 变址寻址:给出的地址需与特定的地址值累加从而得出操作数地址。

图3-3直观地说明了这几种寻址方式的特点。

图3-3 寻址示意图

难度系数:☆ 考查频度:☆ 考查权重:☆

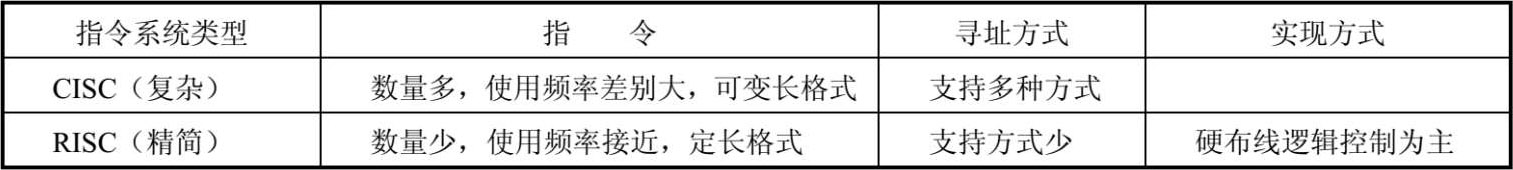

本知识点的重点在于了解RISC和CISC这两种不同的指令设计的主要优缺点与区别。

为了提高操作系统的效率,人们最初选择了向指令系统中添加更多、更复杂的指令这种方式来实现,而且随着不断地升级和向后兼容的需要,指令集也越来越大。这种类型的计算机,我们称为复杂指令计算机(CISC)。后来研究发现,计算机指令系统如果使用少量结构简单的指令,就会提高计算机性能,这就是精简指令集计算机(RISC)。计算机执行程序所需的时间P由三方面因素决定,编译后产生的机器指令数I、执行每条指令所需的平均周期数CPI,以及每个机器周期的时间T。它们的关系是P=I×CPI×T。而RISC正是通过简化指令的途径使计算机结构更合理,减少指令执行周期数,提高运算速度的。虽然RISC编译后产生的 机器指令数(I)增多 了,但 指令所需的周期数(CPI ) 和 每个周期的时间(T ) 都可以 减少 。它与CISC可谓各有特色(如表3-3所示)。

表3-3 RISC与CISC的区别

典型的RISC处理器包括:DEC的Alpha 21164,IBM的Power PC620,HP的PA-8000,SGI MIPS分部的TS,以及Sun的Ultra SPARC。目前RISC处理器技术的发展方向是采用并行处理技术(包括超级流水线、超级标量、超长指令字)大幅度地提高运算速度。

难度系数:☆☆ 考查频度:☆☆ 考查权重:☆☆

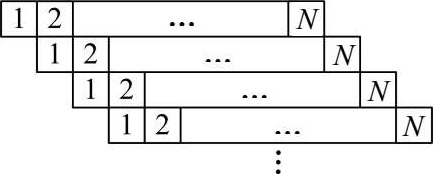

本知识点的重点在于理解流水线的工作原理(与实际工作中的流水作业其实是相似的,考生可以结合这个日常生活中的场景进行理解),并且能够知道如何计算流水线的指令执行所需的时间,以及哪些因素会破坏流水线的执行。

流水线技术是通过并行硬件来提高系统性能的常用方法,它其实是一种任务分解技术,把一件任务分解为若干顺序执行的子任务,不同的子任务由不同的执行机构来负责执行,而这些执行机构可以同时并行工作。其工作原理如图3-4所示。

图3-4 流水线工作原理示意图

(1)计算执行时间。

假定有某种类型的任务,可分成 N 个子任务,每个子任务需要时间 t ,则完成该任务所需的时间为 Nt 。若以传统的方式,则完成 k 个任务所需的时间是 kNt 。而使用流水线技术执行,花费的时间是 Nt +( k -1) t 。也就是说,除了第一个任务需要完整的时间外,其他都通过并行技术节省下了大量的时间,只需一个子任务的单位时间就够了。

另外要注意的是,如果每个子任务所需的时间不同,则其速度取决于其执行顺序中最慢的那一个( 也就是流水线周期值等于最慢的那个指令的周期 ),要根据实际的情况进行调整。

例如,若指令流水线把一条指令分为取指令、分析和执行3部分,且3部分的时间分别是取指令2ns,分析2ns,执行1ns。那么,最长的是2ns,因此100条指令全部执行完毕所需要的时间就是(2ns+2ns+1ns)+(100-1)×2ns=203ns。

另外,还应该掌握几个关键的术语:流水线的吞吐率(任务数/完成时间),加速比(不采用流水线的执行时间/采用流水线的执行时间)。

(2)影响流水线的主要因素。

如图3-4所示,流水线的关键在于“重叠执行”,因此如果这个条件不能够满足,流水线就会被破坏。这种破坏主要来自如下几种情况。

· 转移指令:因为前面的转移指令还没有完成,流水线无法确定下一条指令的地址,因此也就无法向流水线中添加这条指令。从这里的分析可以看出,无条件跳转指令是不会影响流水线的。

· 共享资源访问的冲突:也就是后一条指令需要使用的数据,与前一条指令发生的冲突,或者相邻的指令使用了相同的寄存器,这也会使得流水线失败。

· 响应中断:当有中断请求时,流水线也会停止。对于这种情况有两种响应方式:一种是立即停止——精确断点法,这种方法能够立即响应中断;另一种是流水线中的指令继续执行,不再新增指令到流水线——不精确断点法。

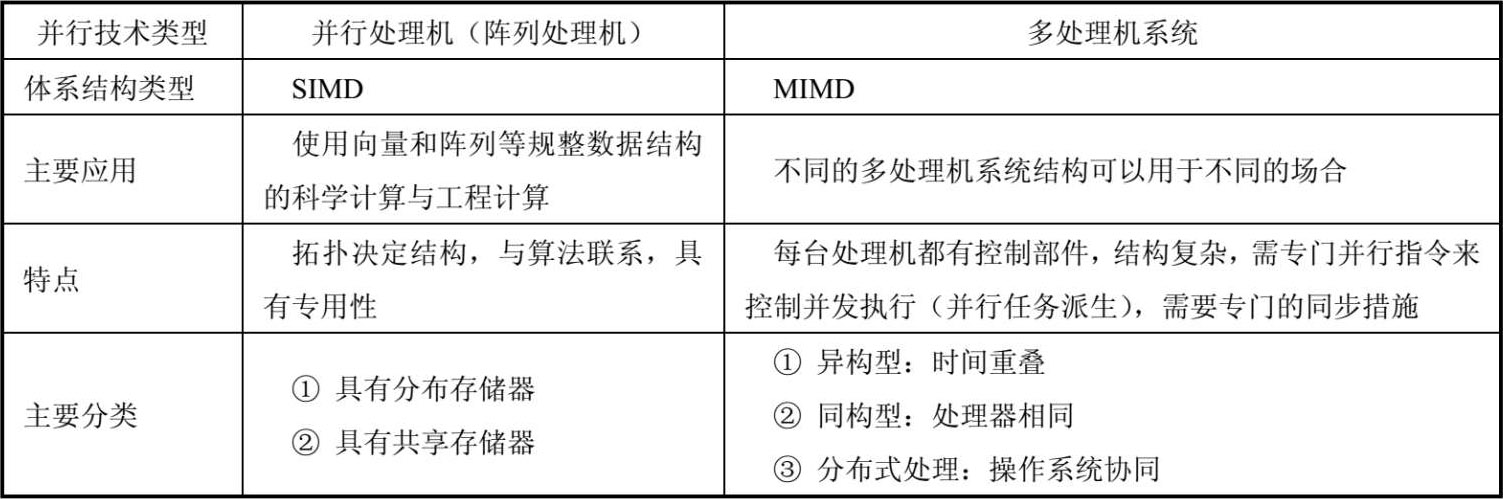

难度系数:☆☆ 考查频度:☆ 考查权重:☆

本知识点的重点在于理解时间重叠、资源重复、资源共享3种并行措施,能够了解并行性发展的方向,以及并行处理机、多处理机的相关知识,要注意与体系结构划分相结合的知识点。

并行性是指在同一时刻或同一时间间隔内完成两种或两种以上性质相同或不同的工作,只要在时间上互相重叠,都存在并行性。

(1)并行措施分类。

· 时间重叠:多个处理过程在时间上相互错开,轮流重叠使用同一套硬件设备,主要代表是流水线部件、流水线处理机。

· 资源重复:空间重复,即引入多套硬件设备共同完成,主要代表是多处理机系统、阵列式处理机等。

· 资源共享:也是在时间上并行,通过软件实现。主要表现在多道程序和分时系统中,可以说分布式处理系统和计算机网络是更高层次的资源共享。

(2)主要并行技术(如表3-4所示)。

表3-4 主要并行技术

(3)并行性的发展。

· 单处理机。主要是在功能部分上改进,按3种并行措施(主要是时间重叠)来实现。

资源共享:多道程序、分时系统、虚存器→多终端、远程终端→分布式处理系统。

资源共享:多道程序、分时系统、虚存器→多终端、远程终端→分布式处理系统。

资源重复:多存储块、多操作部件→相联处理机、并行处理机→同构型多处理机。

资源重复:多存储块、多操作部件→相联处理机、并行处理机→同构型多处理机。

时间重叠:先行控制、高速缓存→指令、操作、宏流水线→异构型多处理机。

时间重叠:先行控制、高速缓存→指令、操作、宏流水线→异构型多处理机。

· 多机系统。属于多指令流多数据流计算机系统,主要包括以下几种发展方式。

网络化:通信处理机、计算机网络→计算机局域网→分布式处理系统。

网络化:通信处理机、计算机网络→计算机局域网→分布式处理系统。

多机互联:紧耦合系统→可重构、容错多处理机→同构型多处理机。

多机互联:紧耦合系统→可重构、容错多处理机→同构型多处理机。

功能专用化:松耦合系统→高级语言、数据库处理机→异构型多处理机。

功能专用化:松耦合系统→高级语言、数据库处理机→异构型多处理机。