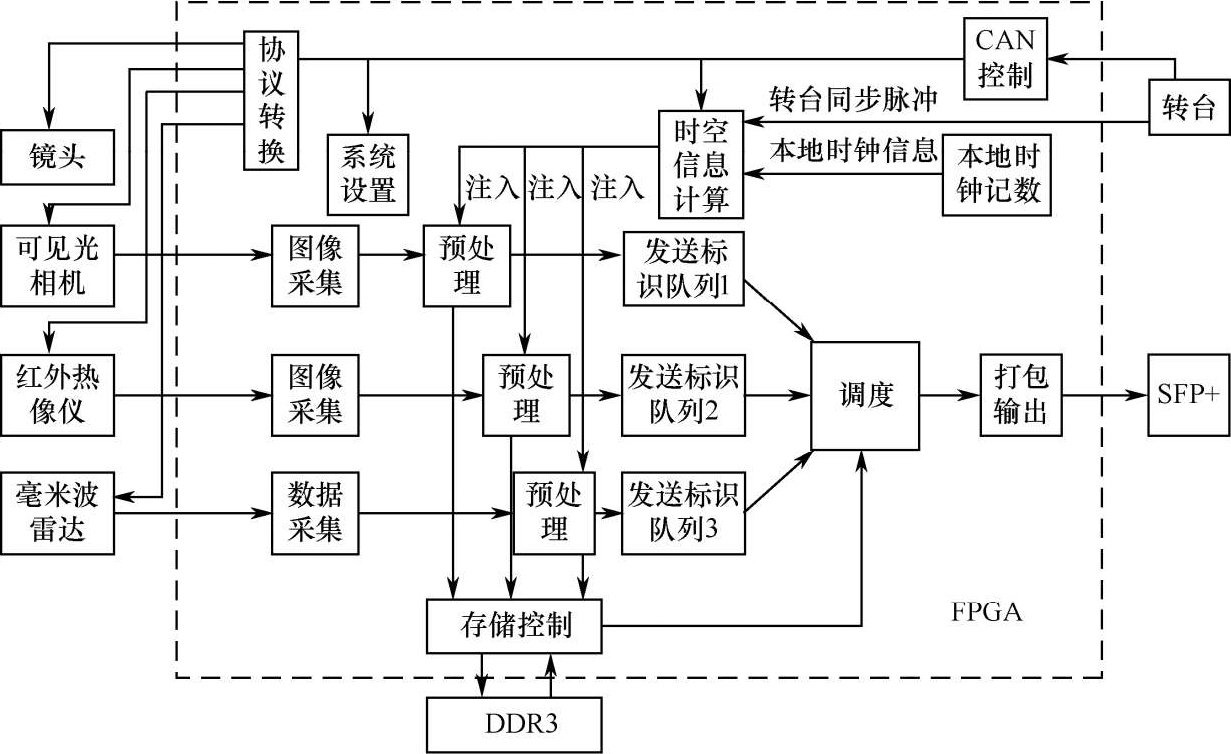

多源异类传感器采集控制系统采用SOPC的实现方案,大部分功能在FPGA内部完成。FPGA内部功能框图如图2所示。FPGA内部软件主要由以下几个模块构成:CAN总线控制模块,图像采集模块,图像预处理模块,存储控制模块,时空同步信息计算模块,调度模块,编码输出模块。以下对控制系统中一些关键功能模块进行介绍。

图2 FPGA 内部功能模块组成

系统的正常工作需要对各种探测器进行参数配置更新,需要对系统自身工作参数进行设置,对工作模式进行选择等,所有控制信息指令通过CAN总线节点传输到FPGA。在FPGA内部对接收到的数据帧进行分析解读,根据不同帧对应的内容将控制数据发给不同的模块,对周边外设以及系统自身工作模式进行控制。被控制对象中的红外热像仪、毫米波雷达、可见光相机以及镜头的控制指令均符合异步串口通信协议,差别仅在控制帧格式定义与波特率的不同,在FPGA内部需要解析接收帧做CAN总线数据到控制数据的协议转换,以及将接收的数据按照串口定义格式进行并串转换,依照不同的波特率将数据发送出去。系统参数与时空同步校正信息被系统内部所使用,解析完帧ID号后将所获取的数据更新FPGA内部开辟的寄存器,系统将按照更新后的参数进行工作。

多源异类传感器返回的探测信息数据格式不一致,需要在FPGA内部做归一化处理。在典型工作模式下转台转速为180°/s,可见光相机以不低于70帧/s速度输出1280×1024分辨率的8bit位宽数据将可覆盖全视场,可见光相机每帧图像曝光后输出数据按行到来,根据帧频的不同单个像素时钟下到来多个像素,图像采集模块首先对数据进行了数据位宽的归一化处理转换,为了降低系统内部处理时钟频率并且数据位宽与高速缓存的DDR3控制接口相适配,设置内部总线位宽为128bit,即将到来的多位宽数据统一转换为128bit位宽数据进行处理。可见光相机选用CMOS相机,经过相机内部自带列向噪声消除后依旧存在一些FPN噪声,控制系统将在预处理模块对到来的数据流进行简单的FPN噪声消除的图像预处理操作。预处理模块同时通过对到来帧首行数据进行信息叠加,将相机曝光时刻锁存的时空同步信息注入当前可见光图像帧首行。红外热像仪输出数据格式为以固定周期输出288个8bit深度像素数据列。在采集模块主要利用FIFO进行了红外数据速率和位宽的转换,在预处理模块则实现了红外热像仪每列数据的时空同步信息注入。雷达数据以符合串口协议的数据帧的形式到达,在采集模块解析出有效数据后将在数据帧尾注入时空同步信息。三个异类传感器返回数据在预处理完毕之后进入相对应的FIFO中等待写入DDR3指定区域,DDR3读写控制器通过查询FIFO中数据量进行对应的数据写入操作,同时将该通道数据写入DDR3区域的起始地址和写入的长度记录到对应的发送标识队列FIFO中,等待系统调度模块查询读出。

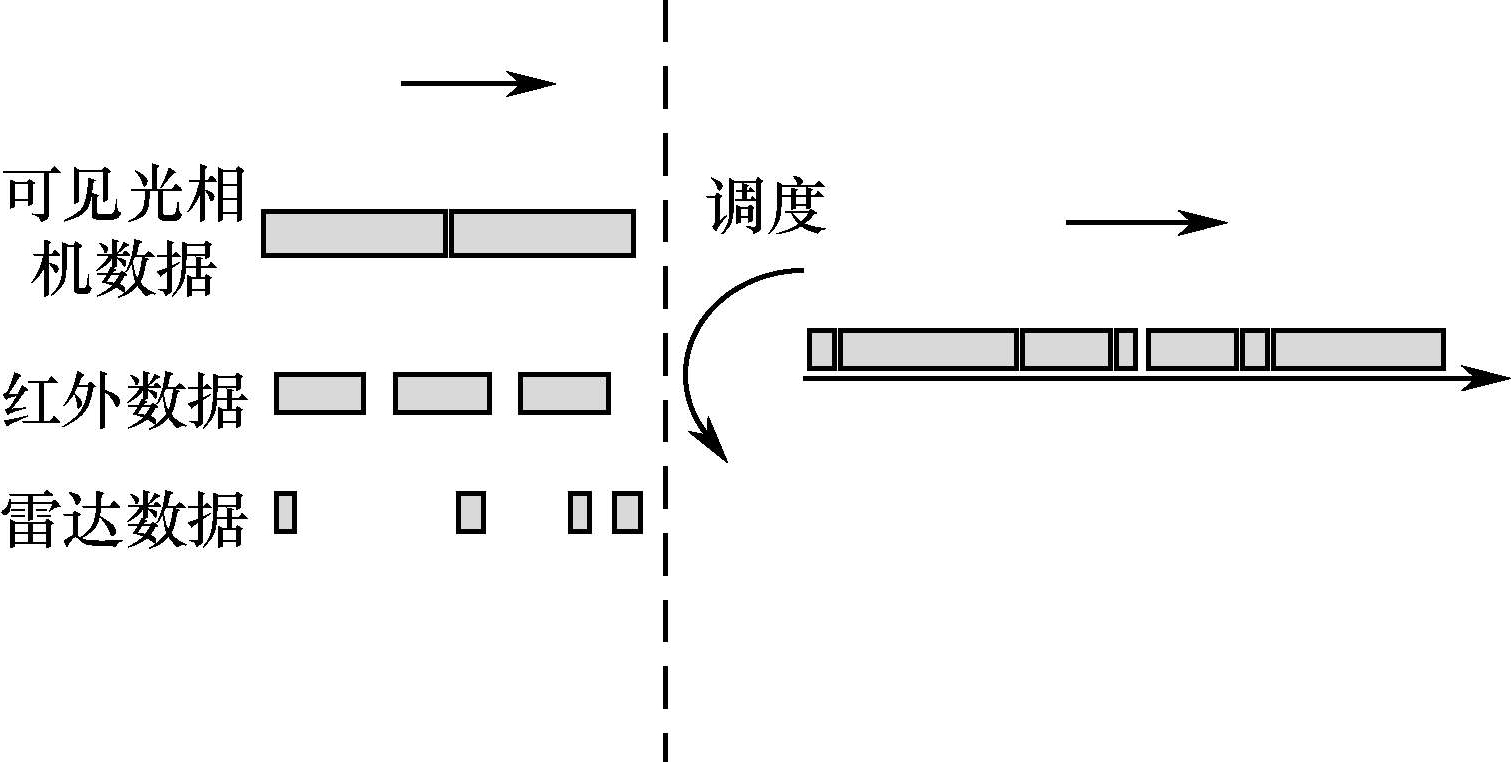

对于缓存区内的异类传感器数据,已经按照传感器类型进行了数据的分区域存储,每一行或者帧数据的存储起始地址和长度被记录在相应的发送标识队列FIFO中。FPGA将采用公平查询的方式对待发送数据进行调度处理。调度模块公平查询的实现方式为查询三个发送标识队列FIFO是否为空,若为空则表明当前查询的传感器未产生足够待发送数据,系统将查询下一个发送标识队列FIFO。若当前查询队列FIFO不为空,则调度模块将从当前发送标识FIFO读出一个数据,根据数据中的地址与数据长度信息从DDR3中相应地址位置读出指定长度的数据信息送入编码输出模块,多源异类数据调度发送示意图如图3所示。

图3多源异类数据调度

编码输出模块将进行数据位宽与速率的转换,对数据流进行自定义格式的组帧,并利用Xilinx自带的aurora核对帧数据流进行8b/10b编码和并串转换,实现系统内多位宽的并行数据到高速串行数据的转换。典型工作模式下可见光相机传输所需带宽主要与帧频有关,以150帧/秒速度计算传输带宽约1.5Gb/s。红外热像仪输出数率较可见光相机低,注入时空同步信息后的数据传输所需要带宽约为300Mb/s。雷达数据直接返回目标位置和速度信息,传输所需带宽约为2Mb/s。系统中的高速串行数据链路传输速率设计为5Gb/s,能够满足多通道高速数据的输出需求并留有较大余量。数据输出至FPGA外部的SFP+光模块进行电/光转换后由光纤输出,在采集计算机有配套使用的专用采集板卡,数据经过PCIE接口被计算机采集。