逻辑器件的选型首先是逻辑电平的选择,在传统的单板设计中,TTL 和 CMOS 逻辑电平被广泛应用,是数字电路设计中最常见的两种逻辑电平,LVTTL和LVCMOS是它们的低电平版本,其他的高速电平大多都衍生自TTL和CMOS。

TTL 指晶体管—晶体管逻辑,由于晶体管是流控器件,且输入电阻较小,因此 TTL 电平的器件速度快,但功耗较大;CMOS 是 MOS 管逻辑,由于 MOS 管是压控器件,且输入电阻极大,因此CMOS电平的器件速度较慢,但功耗较小,同时由于CMOS器件输入阻抗很大,外界微小的干扰就可能引起电平的翻转,因此 CMOS 器件上未使用的输入引脚应做上下拉处理,不能浮空。

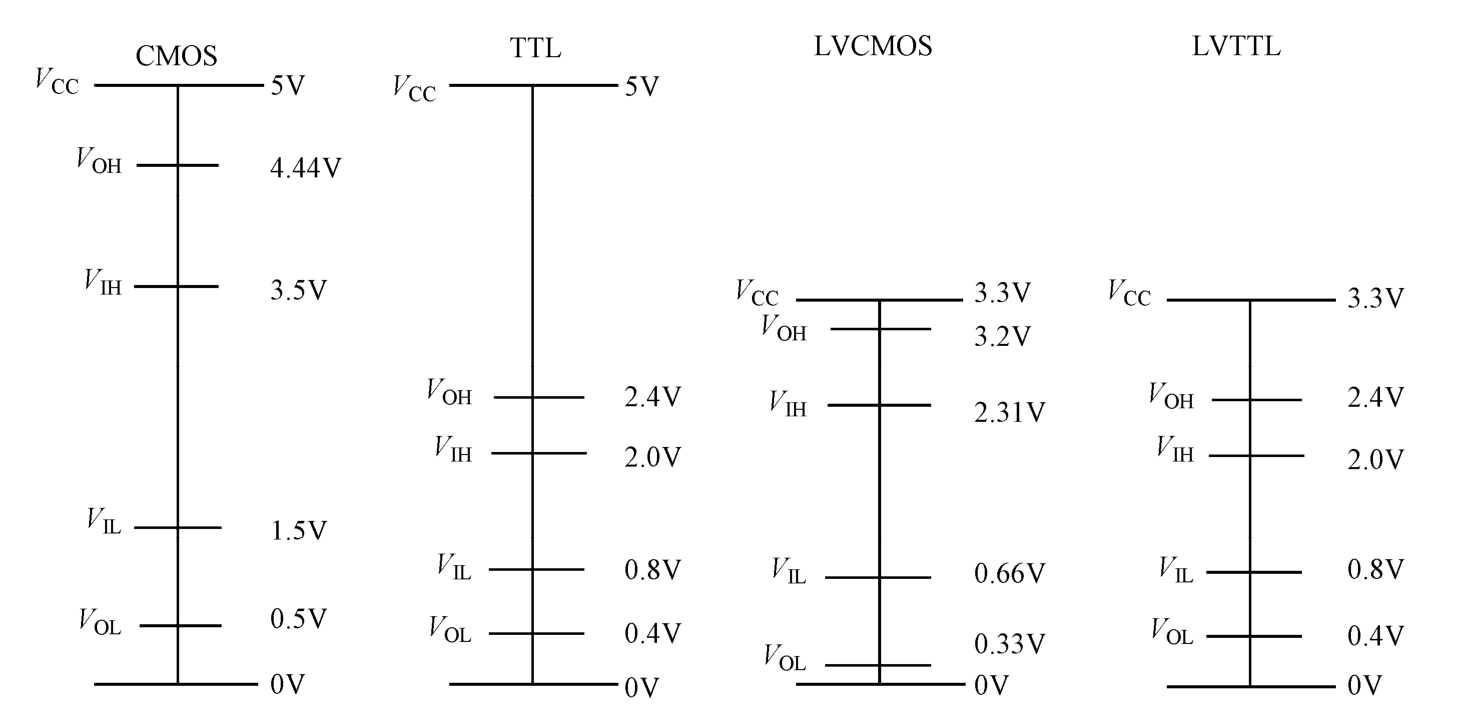

现实中的信号是连续的模拟信号,而数字信号只有“1”和“0”两种逻辑状态,需使用阈值来定义信号的逻辑状态。下面以图3.5以例,说明信号的逻辑电平定义。

图3.5 逻辑电平阈值示例

在图3.5中,对每种逻辑电平都定义了四个阈值,即V OH 、V OL 、V IH 、V IL 。

当逻辑器件输出高电平时,电平的幅值应高于V OH ,即V OH 为输出高电平的最小值;

当逻辑器件输出低电平时,电平的幅值应低于V OL ,即V OL 为输出低电平的最大值;

当逻辑器件输入高电平时,电平的幅值应高于V IH ,即V IH 为输入高电平的最小值。

当逻辑器件输入低电平时,电平的幅值应低于V IL ,即V IL 为输入低电平的最大值。

从图 3.5 可以发现,各逻辑电平的阈值并不相同,因此相互间并非可以直接互连。只有同时满足以下条件时,不同逻辑电平的器件才能直接互连。

条件一 ,发送方V OH 大于接收方V IH ,且提供一定的噪声容限。

条件二 ,发送方V OL 小于接收方V IL ,且提供一定的噪声容限。

例如,当LVTTL电平的器件能承受5V信号的输入时,可以和TTL电平的器件直接互连;CMOS 器件作为发送方,TTL 器件作为接收方,两者可以互连;但 TTL 器件作为发送方,CMOS器件作为接收方时,则不能互连。

相同电平的逻辑器件之间,能自然满足以上两个条件,因此可以直接互连。

需注意,图 3.5 只是一个示意图,对于不同型号的逻辑器件,即使使用同种逻辑电平,阈值也不一定相同,设计中应查阅器件资料以获得各项阈值参数。

对于电平不同,且不能满足直接互连条件的逻辑器件,可采用以下方法实现互连。

方法一 ,使用电平转换芯片。例如,74ACT16245,其输入端为 TTL 电平,输出端为CMOS电平,因此支持TTL到CMOS电平的转换。当存在大量信号需做电平转换时,可采用这种方法。

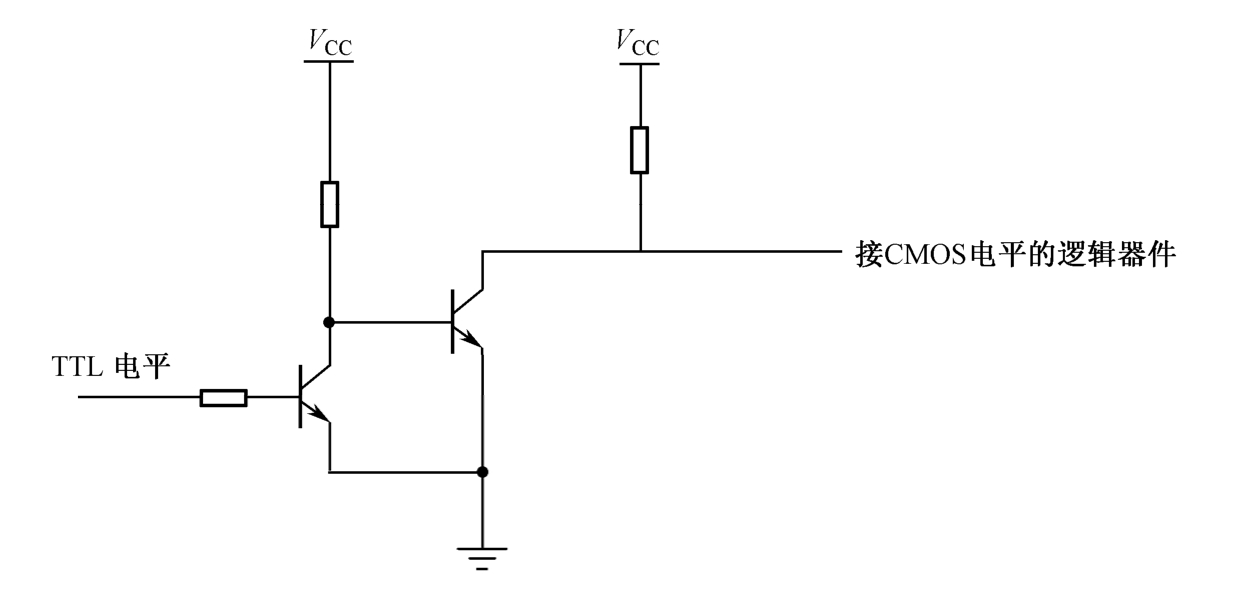

方法二 ,使用 OC(集电极开路)门或 OD(漏极开路)门实现逻辑电平的转换。如图3.6所示,通过OC门电路,TTL器件可与CMOS器件相连。OC或OD门还常被用于低逻辑电平驱动高逻辑电平的场合。

图3.6 利用OC门实现逻辑电平的转换

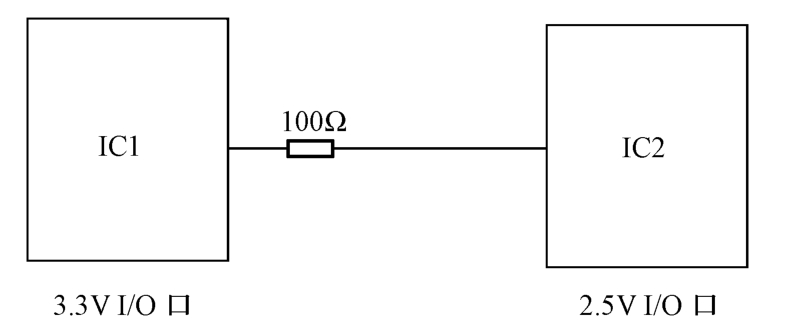

方法三 ,高逻辑电平驱动低逻辑电平时,可串联 50~330Ω电阻实现电平的转换。如图3.7所示,IC1的I/O接口是3.3V电平,IC2的I/O接口是2.5V电平,可通过串联电阻实现两者的互连,串联电阻的阻值需根据I/O口动态电流进行计算。

图3.7 串联电阻实现逻辑电平的转换

电路设计时,通过 JTAG 接口(一种标准的接口,将在第 8 章进行详细介绍),可将单板上的芯片连成一条链路。如果遇到某些芯片的JTAG接口逻辑电平与其他芯片不同,可利用方法二和方法三实现链路的连接。

逻辑器件互连时,除考虑电平转换之外,还应考虑器件的驱动能力、时延特性等,后续章节将有对应内容的讨论。

电路设计中,74族逻辑器件的厂家有TI、NXP、Fairchild等。

根据工艺不同,逻辑器件可分为三类:Bipolar(双极型),CMOS(互补金属氧化物半导体)和BiCMOS(Bipolar CMOS)。

Bipolar 是由双极型晶体管组成的集成电路,如 TTL 电路就属于 Bipolar,特点是速度快,驱动能力强,但功耗较大。

CMOS 是由场效应管构成的集成电路,特点是功耗低,集成度高,但驱动能力和速度比Bipolar差。

随着高速电路的发展,单板密度越来越高,功耗越来越大,器件的工作速度也越来越快,Bipolar和CMOS已逐渐不能满足设计的要求,需要采用新的工艺——BiCMOS。

BiCMOS主要具有以下两种优势:

(1)BiCMOS 以 CMOS 工艺为主,CMOS 电路充当高集成度和低功耗的电路核心部分,用Bipolar电路充当输入/输出接口部分,因此可以充分发挥Bipolar和CMOS的优势,同时具有速度高、驱动能力强和功耗低、集成度高的优点。

(2)随着工作温度和工作电压的变化,CMOS 器件和 Bipolar 器件的许多特性都会发生变化,且对于许多特性参数,CMOS 和 Bipolar 器件的变化方向是相反的。例如,传输延时参数,随着温度的降低,CMOS 器件的传输延时减小,而 Bipolar 器件的传输延时增大;随着温度的升高,CMOS 器件的传输延时增大,Bipolar 器件的传输延时虽然也增大,但增加的幅度小于 CMOS 器件。BiCMOS 工艺将 Bipolar 和 CMOS 这两种具有互补特性的工艺结合在一起,使得器件参数随工作电压和工作温度的变化曲线较平缓,提高了器件的性能。

电路设计中常用的 74 族逻辑器件,根据制造工艺、I/O 接口结构的不同,可分为多种系列 [26] 。

ABT:先进BiCMOS技术(Advanced BiCMOS Technology)

AC/ACT:先进CMOS逻辑(Advanced CMOS Logic)

AHC/AHCT:先进高速CMOS逻辑(Advanced High-Speed CMOS Logic)

ALS:先进低功耗肖特基逻辑(Advanced Low-Power Schottky Logic)

ALVC:先进低电压CMOS技术(Advanced Low-Voltage CMOS Technology)

ALVT:先进低电压BiCMOS技术(Advanced Low-Voltage BiCMOS Technology)

AS:先进肖特基逻辑(Advanced Schottky Logic)

AVC:先进极低电压CMOS逻辑(Advanced Very Low-Voltage CMOS Logic)

CBT:Crossbar技术(Crossbar Technology)

F:快速逻辑(F Logic)

FCT:快速CMOS TTL逻辑(Fast CMOS TTL Logic)

HC/HCT:高速CMOS逻辑(High-speed CMOS Logic)

LS:低功耗肖特基逻辑(Low-Power Schottky Logic)

LV/LVC:低电压CMOS技术(Low-Voltage CMOS Technology)

LVT:低电压BiCMOS技术(Low-Voltage BiCMOS Technology)

S:肖特基逻辑(Schottky Logic)

以上所列出的系列可被分别归入Bipolar、CMOS、BiCMOS三种工艺类别。

Bipolar工艺:F、S、AS、LS、ALS等。

CMOS工艺:LV、LVC、AC、AHC、AVC、ALVC、HC、HCT、CBT、FCT等。

BiCMOS工艺:LVT、ABT、ALVT、GTL等。

例如,高速电路设计中常用的 16245 总线驱动器有多种系列,分别属于以上三种类型。其中,属于 CMOS 工艺的有 74AC16245、74FCT16245、74AVC16245 等,属于BiCMOS工艺的有74ABT16245、74LVT16245等。

基于制造工艺、I/O 接口结构的不同,这些系列的逻辑器件具有不同的特性。例如,LV和 LVC 系列,都属于 CMOS 工艺,但 LV 采用的是 2μm 制造工艺,而 LVC 采用的是0.8μm 制造工艺,因而 LVC 系列逻辑器件在驱动能力、延迟时间、信号变化沿速率等方面都优于LV系列器件。而LVT工艺基于BiCMOS工艺,BiCMOS兼有Bipolar和CMOS的优势,因此与LV、LVC相比,LVT的各方面性能又更高一筹。

在选型时需要注意,Bipolar工艺的逻辑器件,接口电平一般是TTL或LVTTL。CMOS工艺的逻辑器件,接口电平则可能是CMOS、TTL、LVTTL等类型,例如,74LV125A的输入和输出接口电平都是 LVTTL,而 74LV125AT 的输入接口电平是 TTL,输出接口电平是CMOS。BiCMOS 工艺的逻辑器件,为提高接口速率和驱动能力,输入和输出接口电平往往是TTL或LVTTL。

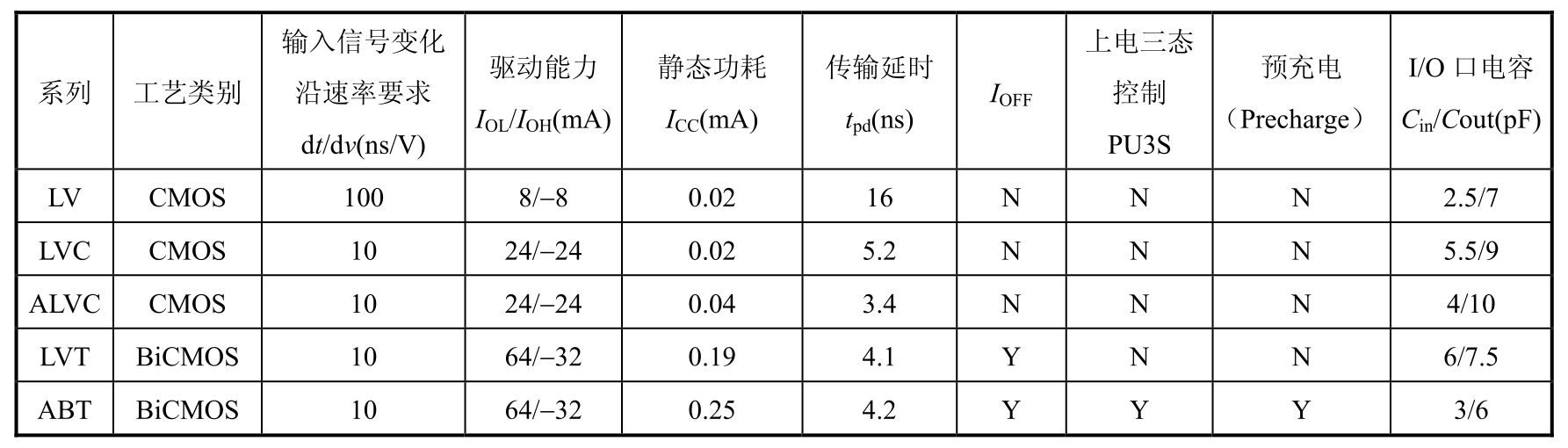

以电路设计中最常用的几种逻辑器件系列为例,性能比较如表3.1所示 [26] 。

表3.1 常见逻辑器件系列性能

表 3.1 以五种有代表性的系列为例,对逻辑器件的关键性能做了比较。其中,LV 是最基础的、低速且低驱动能力的逻辑器件,LVC 是性能中等的 CMOS 器件,ALVC 是传输延时最小的 CMOS 器件,LVT 和 ABT 是 BiCMOS 器件。需注意的是,表中所列的参数均摘自该系列中的某一特定器件,并不适用于系列中的所有逻辑器件,同种系列的器件,如74LVT125与74LVT16245,某些性能参数就存在微小的差别;某些LVC器件支持I OFF (I OFF 将在后面3.2.4小节中介绍),而某些不支持I OFF 。因此在设计中,具体参数还应查询对应的器件资料。

表 3.1 中第三列是该系列器件对输入信号变化沿的速率要求,LV 系列主要应用于低速设计,对变化沿的速率要求仅为 100ns/V,而其他四种系列可用于高速设计,因此对输入信号变化沿的速率要求也比较高;第四列是该系列器件输出电流的能力,值越大则驱动能力越强;第五列是衡量静态功耗的参数,I CC 指器件处于静态(无负载)时,流入器件电源引脚的电流;第六列是衡量器件传输延时的参数,高速电路的器件选型时,应选择延时小的逻辑器件,因此后四种器件更适合于高速应用;第七~九列是与热插拔有关的性能,将在后续章节讨论。

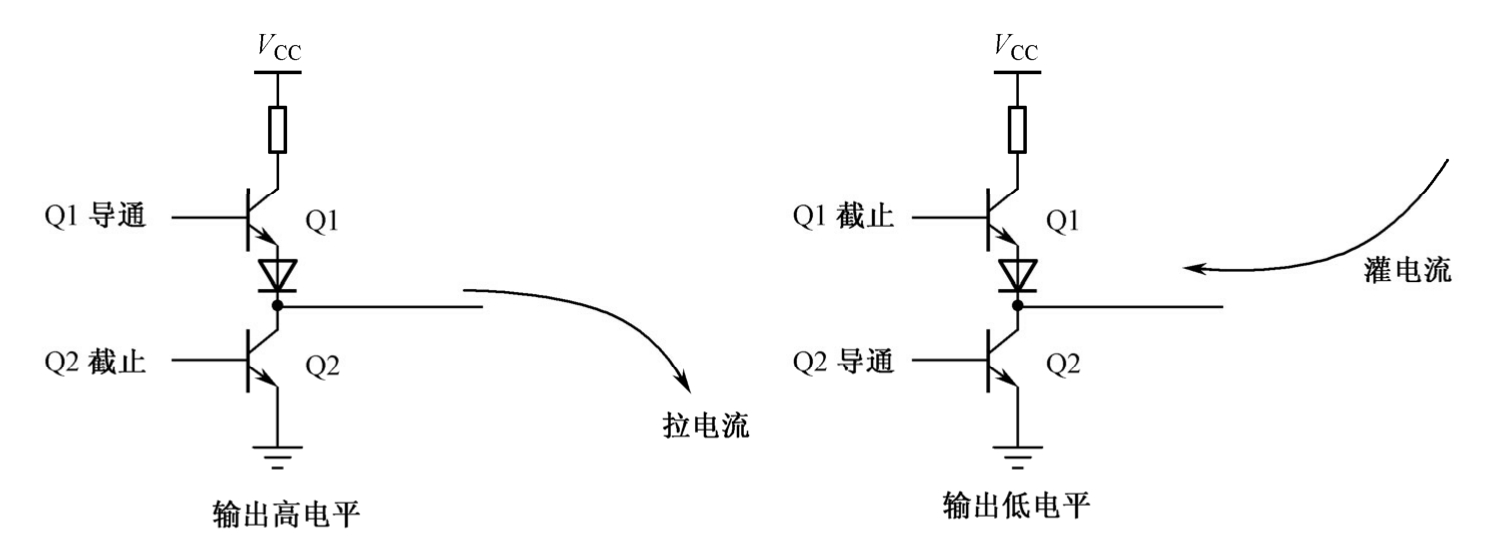

通常定义流入器件的电流为正,流出器件的电流为负,以输出端口为 TTL 电平的逻辑器件为例,输出高电平时电流流出器件,电流方向为负,称为拉电流(负载从逻辑器件拉出电流);输出低电平时电流流入器件,电流方向为正,称为灌电流(负载将电流灌入逻辑器件),参见图3.8。因此“驱动能力”列的I OL 参数用正值表示,而I OH 参数用负值表示。

图3.8 拉电流和灌电流 [1]

某电平为 LVTTL 的总线采用 74LVT16245 作为信号驱动器,测试中发现信号振铃过大,最大过冲达到4.3V,超过负载端器件的最大输入电平要求。

【讨论】

LVT系列的逻辑器件驱动能力很强,其I OL 和I OH 分别达到64mA和-32mA。强驱动能力的逻辑器件,优势在于其输出信号能在 PCB 上传输较远的距离,不易受外界环境的干扰,且能同时驱动多个负载,但劣势在于,由于其驱动能力太强,可能导致信号在接收端产生振铃现象。因此,在应用强驱动能力的逻辑器件时,输出端应增加串联电阻,实现阻抗匹配。在本案例中,在74LVT16245的每个输出端串联一个33Ω的电阻,振铃现象消失。

【拓展】

在总线驱动的场合,每个输出端都增加一个串联电阻,会耗费大量宝贵的 PCB 面积,为节省 PCB 面积,可选用内部带有串联电阻的逻辑器件型号。例如 74LVTR245,器件内部的每个输出端都含有一个内置的串联电阻。

某 PHY 芯片利用复位信号无效时的上升沿采样数据总线的状态,根据总线信号的逻辑状态来完成上电配置。调试时偶尔会发现在 PHY 上电完成后,其状态出错。读取相关配置寄存器后,可定位为上电配置出错。

【讨论】

设计中,复位信号和数据总线都经过 74LVT164245 驱动,不过由于数据信号线较多,复位信号和数据总线分别经过了不同的 74LVT164245,通过多次测量抓取出错时的信号时序,发现出错时,复位信号无效沿采样的数据总线信号状态不正确。查看 74LVT164245 器件资料,该器件的传输延时参数 t pd ,其最小值为 1ns,最大值为 4.1ns。同一型号的器件,传输延时也存在一定的差异,对于时序要求高的应用,应尽量采用同样的驱动路径。

【拓展】

高速电路设计中,随着信号速率的不断提高,信号的时钟周期减小到仅有若干纳秒,此时微小的逻辑器件差异性,将对高速设计造成很大的影响。对电路设计者而言,应意识到器件的这一差异,尽量避免出现由于器件差异而引起的错误。

理解要点:

① Bipolar工艺的器件,特点是速度高,驱动能力强,但功耗较大;CMOS工艺的器件,特点是功耗低,集成度高,但驱动能力和速度比Bipolar差;而BiCMOS兼有Bipolar和CMOS的优势。

② 不同电平的器件之间互连时,在V OH 、V OL 、V IH 、V IL 之间需满足的两个条件。

③ 灌电流和拉电流的电流方向。

只有熟练掌握逻辑器件资料上各项参数所代表的含义,才能正确选型。本小节介绍在逻辑器件选型中,需重点关注的参数。

本小节的介绍,以四通道总线驱动器74LVC125A为例。

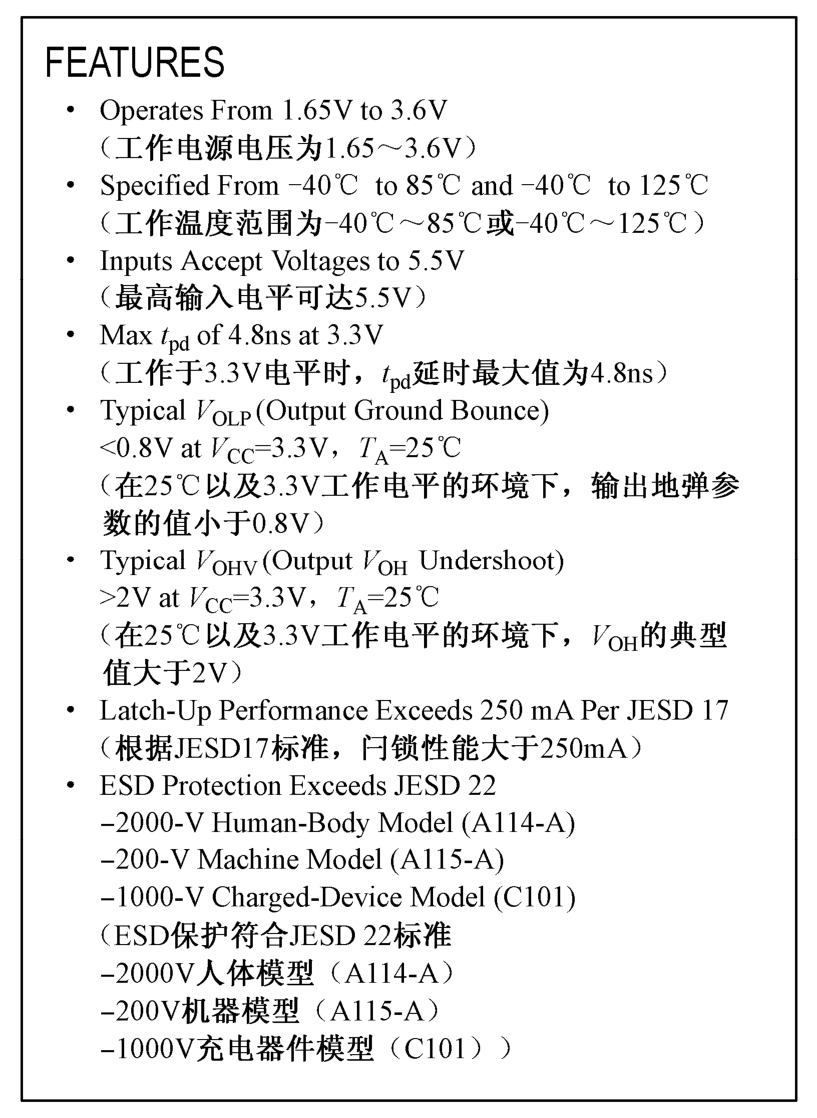

器件资料的首页列出了该器件最关键的几项参数“FEATURES”,参见图3.9。

图3.9 74LVC125A特性参数 [27]

在器件选型时,往往需要查阅并比较大量的器件,然后逐一筛选,而通过“FEATURES”则可以实现第一步的筛选。例如,74LVC125A 的“FEATURES”提供了几项关键信息:推荐电源电压 V CC 的范围是 1.65~3.6V,那么该器件显然不适合工作在 V CC =5V的场合;根据器件工作环境温度参数可知,该器件符合工业级温度标准;根据允许输入电平为5.5V可知,虽然该器件推荐的V CC 不能达到5V,但可以承受5V信号输入,即能与TTL等电平的器件接口。

通过“FEATURES”完成第一步器件筛选后,可以找到若干初步符合设计要求的器件,此时,应结合器件资料详细信息,进一步分析。

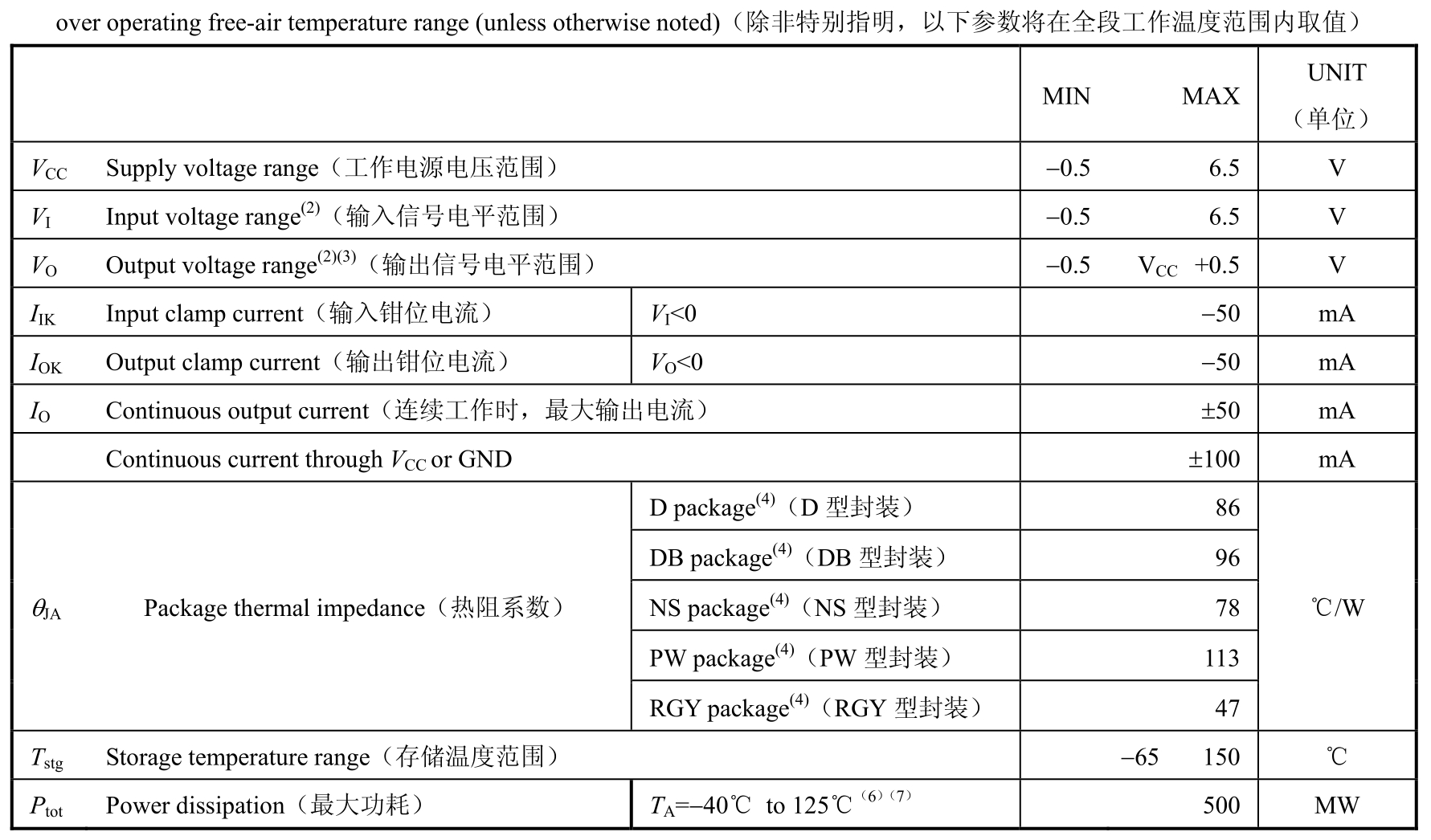

下面以表3.2为例,说明一种器件最大极限参数表的内容。

表3.2 74LVC125A极限参数表 [27]

器件的工作条件如果超出了极限工作表中对应的参数,可能造成器件的永久损坏。

· V CC :电源电压。应注意两点:第一,确保上电和下电时,电源电压的过冲小于极限值;第二,正常工作时,电源电压加上纹波的最大值应小于极限值。

· V I :输入信号电平。输入信号的上升沿和下降沿都会存在过冲,要求上过冲不能超过6.5V,下过冲不能超过-0.5V。

· Vo:输出信号电平。本参数用于分析当该器件作为发送方时,输出信号是否会超出接收端器件的 V I 极限参数要求。表中该栏的 V CC 不是极限参数表中的 V CC 极限值,而是器件工作时的电源电压。

· I IK :输入钳位电流,指器件工作电压超出正常范围之外时,允许流入器件输入端的最大电流。

· I OK :输出钳位电流,指器件工作电压超出正常范围之外时,允许流入器件输出端的最大电流。

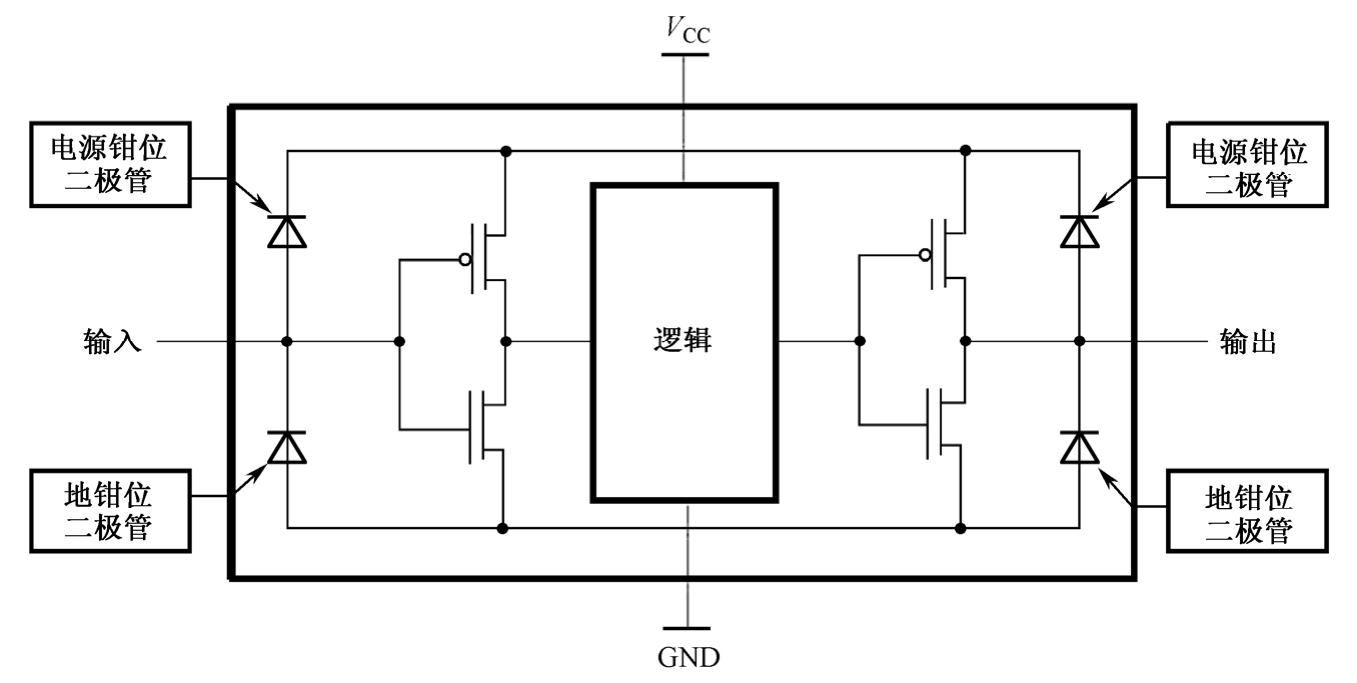

CMOS 器件的输入端电平如超出电源电压或地电平,将引起闩锁。如图 3.10 所示,为保护逻辑器件,在输入/输出端口与电源 V CC 、地(GND)之间,往往内置有钳位二极管,当端口电平超出 V CC 或 GND 时,该二极管能将电平钳位在极限的范围之内,从而避免对器件的损坏。一般情况下,每个逻辑器件的输入/输出端口都内置有地钳位二极管,但不一定内置有电源钳位二极管。由于地钳位二极管的存在,当电平最小值低于 GND 时,地钳位二极管导通,将端口电平钳位在-0.5V(0.5V是内置二极管导通时的压降),因此V I 和V O 的极限最小值为-0.5V。同理,对于输入/输出端口内置有电源钳位二极管的逻辑器件,当电平最大值高于V CC 时,电源钳位二极管导通,将端口电平钳位在V CC +0.5V,因此V I 和V O 的极限最大值为 V CC +0.5V,这类器件有 AC、ACT、AHC、ALVC、AS、F、HC、HCT、S 等系列。而对于 ABT、ALVT、AVC、LV、LVC、LVT 等系列,没有内置电源钳位二极管,当输入电平高于V CC 时,要通过工艺保证器件不被损坏,因此V I 和Vo的极限最大值是一个电平值,如74LVC125A,该值为6.5V,这是器件工艺可以保证的最高电平。

图3.10 逻辑器件输入/输出钳位电路 [26]

当端口电平低于 GND 时,地钳位二极管导通,电流经二极管由 GND 流出端口,该电流有一个最大值,如74LVC125A,该值为-50mA(流出器件),超出该电流,则钳位电路无法正常工作。对于内置有电源钳位二极管的逻辑器件,当端口电平高于V CC 时,电源钳位二极管导通,电流经二极管由端口流入 V CC ,则该电流同样有一个最大值,为正值(流入器件),由于74LVC125A没有内置电源钳位二极管,因此无此项参数要求。

· I O :器件正常工作时,输出端口上允许的最大输出拉电流(负值)或灌电流(正值)。

· θ JA :热阻系数,用于计算器件工作时的温度。

· P tot :器件工作时的最大功耗。

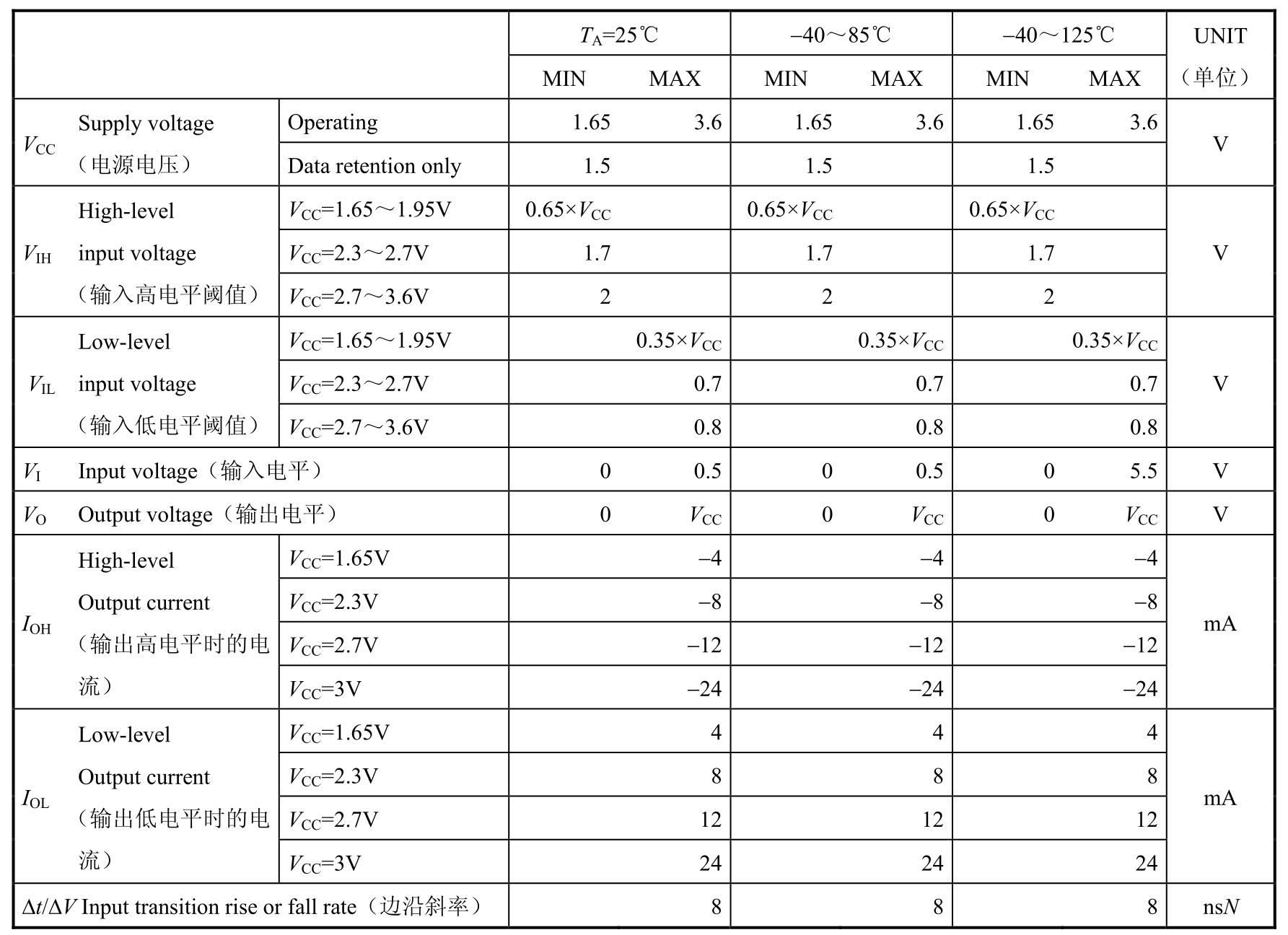

下面以表3.3为例,说明一种器件推荐参数表的内容。

表3.3 74LVC125A推荐参数表 [27]

当满足推荐参数表的要求时,逻辑器件运行于最佳工作状态。根据工作温度的不同,参数值可能有略微差别,例如,在 74LVC125A 的推荐参数表中,参数值按 25℃、-40~85℃、-40~125℃分为三列。

· V CC :电源电压。只有 V CC 处在表中所列范围之内时,才能保证器件正常的工作状态。

· V IH 、V IL :器件资料分别提供了这两个参数的最小值和最大值,仅当输入电平高于V IH 的最小值时,才能被判决为高电平,仅当输入电平低于 V IL 的最大值时,才能被判决为低电平。输入端口为 TTL 电平时,V IH =2V,V IL =0.8V;输入端口为CMOS电平时,参数与V CC 成一定的比例关系(如V IH =0.7×V CC ,V IL =0.3×V CC )。这一点往往可以作为判断输入端电平种类的依据。需注意,输入电平处于 V IH 和V IL 之间时,可能导致以下问题的出现:输出信号逻辑状态不正确、产生较大的静态电流I CC 、输出产生振铃、电源和地之间出现较大的电流通路、损坏器件。

· V I :推荐的输入信号电平范围。在应用中,这一参数可用于判断该器件是否支持高于 V CC 的电平输入,如 74LVC125A,V CC 推荐的最大值为 3.6V,而 V I 能承受最高达5.5V的输入电平,所以74LVC125A能与5V供电的逻辑器件直接互连。并不是每种逻辑器件都支持高于 V CC 的输入信号电平,如 74LV125A,其 V CC 最大值为5.5V,而V I 的最大值也是5.5V。

· V O :输出信号电平范围。

· I OH /I OL :输出高电平/低电平时的电流。电流将随着 V CC 的不同而不同,V CC 越高,电流越大。

· Δt/ΔV:对输入信号变化沿速率的要求。只有输入信号变化沿满足此参数要求时,逻辑器件才能可靠地识别出输入状态的变化,并做出有效的反应。信号变化沿越缓,则处于非稳态区域的时间越长,对器件工作的稳定性越不利。有两种情况可能造成信号边沿过缓,一是驱动方驱动能力不足,一是信号路径上容性太大。根据第 1 章的知识,信号的最高频率往往不是其周期频率,而是其边沿的频率分量,信号边沿越陡,高频分量越多,也越容易出现过冲,所以高速电路设计中往往希望信号边沿缓一些,但边沿太缓,又不能满足器件输入端Δt/ΔV 的要求,因此信号边沿既不能太陡,也不能太缓。

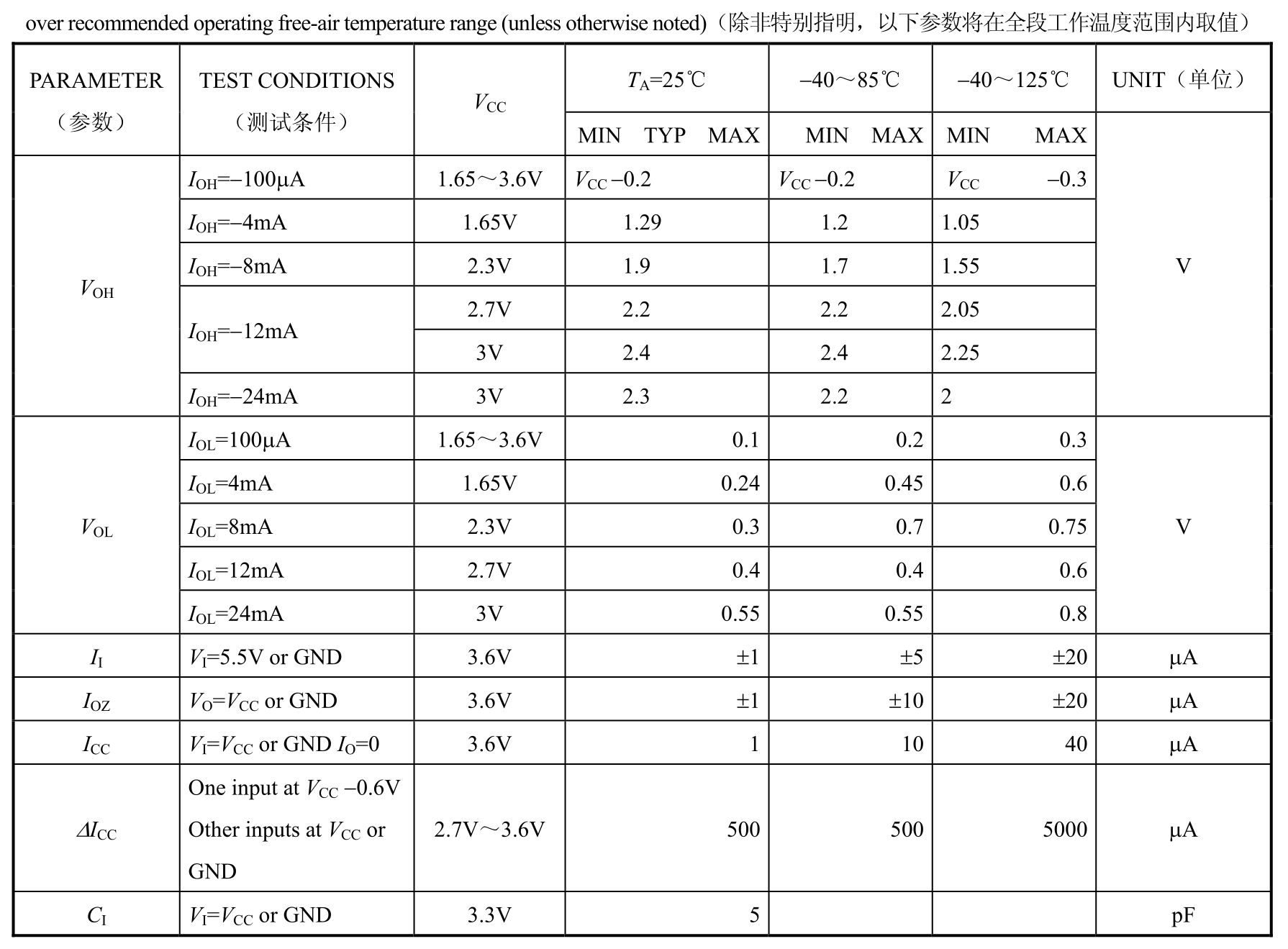

下面以表3.4为例,说明一种器件的电气参数表的内容。

表3.4 74LVC125A电气参数表 [27]

· V OH /V OL :输出高电平的最小值/输出低电平的最大值。

· I I :器件正常工作时流入(输入信号为高电平)或流出(输入信号为低电平)输入端口的电流。CMOS 工艺的逻辑器件属于压控型,输入电流很小,I I 参数仅为几微安;Bipolar工艺的逻辑器件属于流控型,输入电流较大,I I 参数达几毫安。因此,通过I I 参数的值,可判断该器件输入端口的工艺类型,当器件的I I 参数与输入静态电流 I CC 参数的值相近时,该器件的工艺类型为 CMOS。例如,74LVC125A 属于CMOS工艺,I I 参数的最大值仅1μA(25℃),I CC 参数的最大值也是1μA。又如,74LS00属于Bipolar工艺,I I 参数的最大值达1mA。

· I IH /I IL :输入高电平/低电平时流入输入端口电流的最大值。由于CMOS器件的输入阻抗极大,输入端口电流一般就是漏电流,用 I I 定义即可,所以,CMOS 工艺的逻辑器件资料中不提供 I IH 和 I IL 这两个参数(如本处 74LVC125A 的器件资料中无这两个参数)。Bipolar 器件输入高电平和低电平时,输入引脚上的电流差异很大,需用 I IH 和 I IL 分别定义,如 74LS00 的 I IH 最大值为 40μA,而 I IL 可达-1.6mA。设计时应根据I IH 和I IL 的要求选择上、下拉电阻阻值。

· I OZ :输出端口为高阻时的泄漏电流。

· I CC :静态电流,指器件上电后,处于静态(无负载)时,流入电源引脚 V CC 的电流值。

· ΔI CC :CMOS工艺的逻辑器件资料提供该参数,指CMOS器件输入端口由TTL高电平驱动时,在 I CC 基础上额外增加的电流量。根据 3.2.1 节,TTL 电平的 V OH 大于 CMOS 电平的 V IL ,但小于 V IH ,所以当使用 TTL 电平的驱动器驱动 CMOS 电平的接收器件为高电平时,输入信号电平并不能满足 CMOS 器件的输入要求 V IH 和V IL ,处于非稳态,电流将急剧增加,该增加的电流用ΔI CC 定义。对74LVC125A而言,ΔI CC =500μA(25℃),是其I CC 参数的500倍。

· C I :输入电容,是指逻辑器件输入端口的寄生电容。在电路设计时,该参数可被视为衡量驱动器驱动能力的指标,许多专用的驱动器件,如 Cypress 公司的时钟驱动器CY2305器件资料中,定义C L 参数为30pF,即该器件输出引脚的容性负载能力是30pF,而74LVC125A器件的C I 参数值为5pF,则CY2305的一个输出端口最多能同时驱动6个74LVC125A的输入端口。

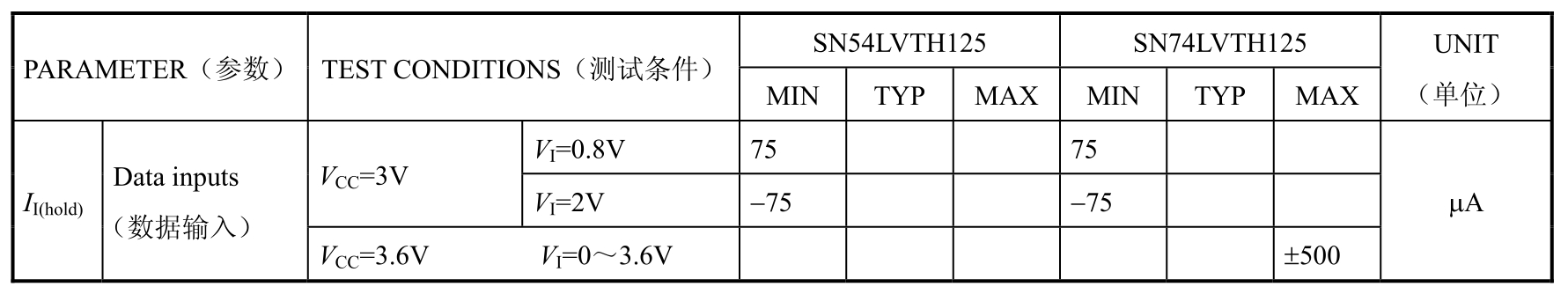

对支持总线保持(Bus Hold)功能的逻辑器件,器件资料上还会提供以下参数:

· I I(hold) :输入保持电流。当驱动器件进入高阻状态后,为使接收器件的输入引脚保持在前一个逻辑状态所需提供的电流。74LVTH125 是支持总线保持功能的逻辑器件,其I I(hold) 参数定义见表3.5。

表3.5 74LVTH125 I I(hold) 参数 [28]

对支持总线保持功能的器件,根据其输入引脚需保持的电平不同,电流需求也不同。一般器件资料上提供的参数是在输入电平保持为V IH 和V IL 时对电流的要求。74LVTH125的输入端口电平为 LVTTL,因此,V IH 和 V IL 参数分别为 2V 和 0.8V,对应的电流要求都是75μA(但流入流出方向不同)。

同时,器件资料上还提供了输入状态翻转(逻辑状态由“0”变“1”或“1”变“0”)时应提供的电流值。应用时需注意,资料上提供的 500μA 是最大值,其含义是,使输入引脚维持在原逻辑状态的最大电流,超过 500μA,则逻辑状态将发生翻转。因此,在要求逻辑状态翻转的应用中,驱动器提供的电流必须大于 500μA,即 500μA 是状态翻转的最小电流要求。参考本章的第一个案例,当驱动电流达不到翻转电流要求时,器件的逻辑状态不会发生变化。

对于定义逻辑状态翻转所需电流的参数,型号较老的系列都是采用 I I(hold) 参数定义,如ABTH、LVTH、LVCH等,而对较新系列的逻辑器件,如74AVCAH164245,器件资料使用I BHH 、I BHL 、I BHHO 、I BHLO 四个参数定义该特性。

· I BHH :支持总线保持功能的器件,其输入引脚保持为V IH 电平时输出的电流值。

· I BHL :支持总线保持功能的器件,其输入引脚保持为V IL 电平时吸收的电流值。

· I BHHO :为使输入引脚的逻辑状态发生从“1”到“0”的翻转,驱动器应吸收电流的最小值。

· I BHLO :为使输入引脚的逻辑状态发生从“0”到“1”的翻转,驱动器应输出驱动电流的最小值。

其中,I BHH 和I BHL 与表3.5中I I(hold) 参数的前两项要求(逻辑状态保持)对应,而I BHHO 和I BHLO 与第三项要求(逻辑状态翻转)对应。

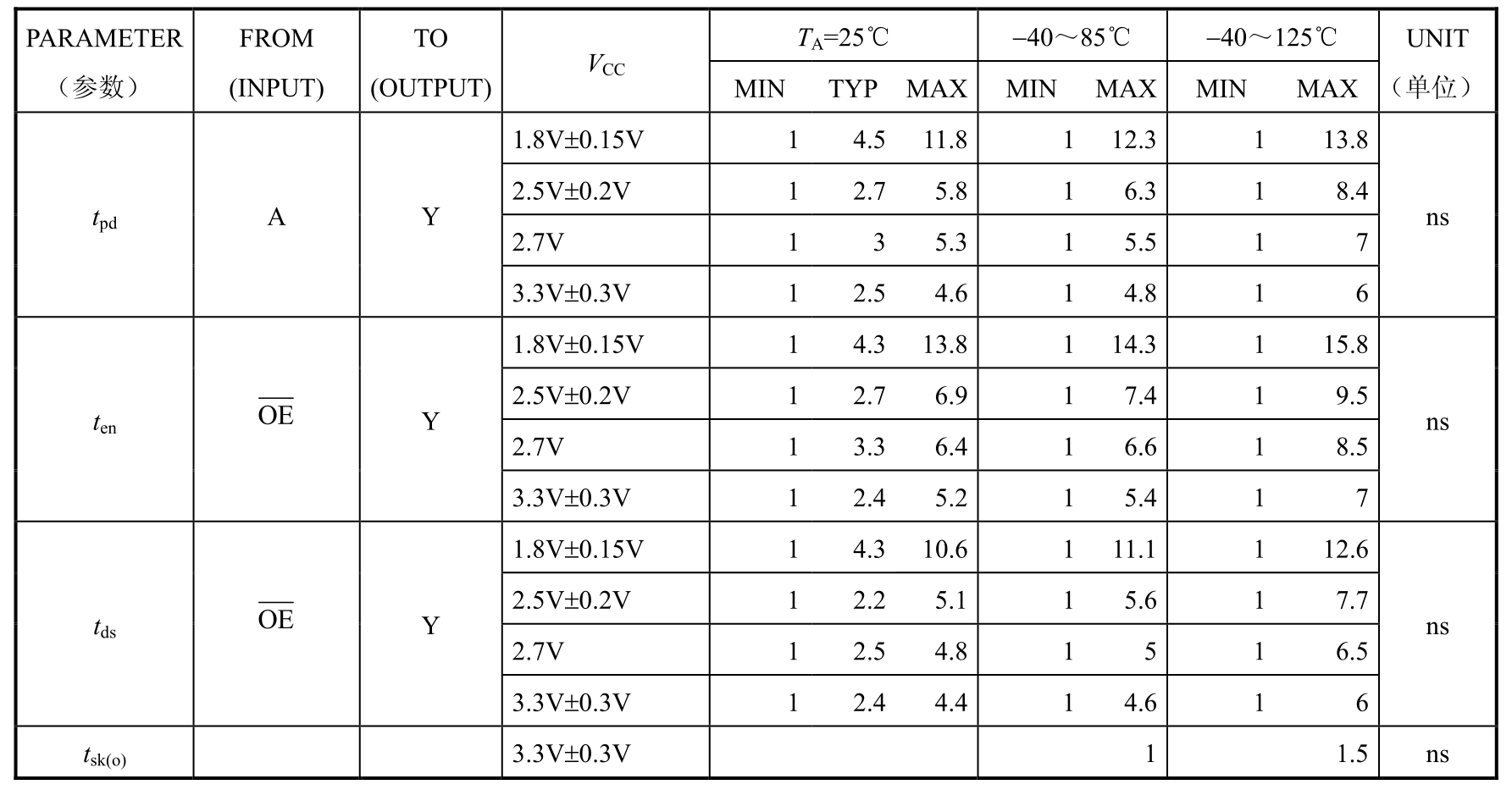

下面以表3.6为例,说明一种器件的传输特性参数表的内容。

表3.6 74LVC125A传输特性参数表 [27]

表3.6中,最重要的参数是:t pd 和t sk(o) 。

· t pd :传输延时,指逻辑状态发生变化时,输入和输出波形上同一电平参考点之间的时间延迟。在某些逻辑器件(如 74LVTH125)资料上,不提供 t pd 参数,而提供了另两个参数:t PLH (逻辑状态由“0”变为“1”,输入和输出波形上同一电平参考点之间的时间延迟)和 t PHL (逻辑状态由“1”变为“0”,输入和输出波形上同一电平参考点之间的时间延迟),实际上是根据状态变化方向的不同,将t pd 参数进行细分,本质上是一样的。如果器件资料上只提供了 t pd 参数,则取值为 t PLH 和 t PHL 的最大值。在时序设计中,应注意同一系列的器件之间,其传输延时参数有一定的差异性。

· t sk(o) :输出偏移失真,指由于制造工艺的限制,器件内部各个输出引脚之间传输延迟的差异。在设计中,如果采用逻辑器件作为总线驱动器,应仔细考虑由于t sk(o) 的存在而对时序造成的影响。

在设计中,与传输特性有关的参数,还有t sk(P) 和t sk(pr) 。

· t sk(P) :脉冲失真,指t PLH 和t PHL 的差值。

· t sk(pr) :封装失真,指同一厂家同一型号的器件,在输出波形上,相互之间存在的差异。

· t pd 、t sk(o) 、t sk(P) 和 t sk(pr) 都是制造工艺造成的器件误差。一般这四个参数的值都非常小,仅为几纳秒,但是在高速电路设计中,当信号速率达到数百兆赫兹时,信号周期也仅有几纳秒,使得这些参数占据了信号周期的较大百分比,对时序裕量造成了很大的威胁,因此必须予以重视。

以上这四个参数虽然都与偏差相关,但对时序分析的意义是不一样的。

t pd 强调的是输入到输出的延时,在逻辑器件作为并行总线的驱动器时,该参数将直接影响总线信号的建立时间和保持时间裕量。根据第5章的内容讲解,当时钟信号和数据信号方向相同时,t pd 的最大值应从数据信号的建立时间裕量中减去,而 t pd 的最小值应加到数据信号的保持时间裕量中。

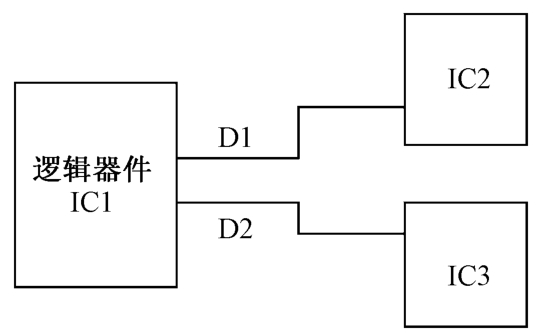

t sk(o) 强调的是不同输出引脚之间的偏移量,如图3.11所示,逻辑器件IC1输出两个状态相同的信号D1和D2,分别送到IC2和IC3,在PCB上D1和D2信号线等长,即希望D1和D2信号到达IC2和IC3时,逻辑状态完全相同,在这种情况下,就必须考虑由于t sk(o) 的存在可能造成的时序问题,假设IC2和IC3将在同一时间对数据信号采样,为保证这两个器件采样正确,并采到同样的数值,要求 D1 和 D2 除满足信号本身所要求的时序裕量外,还应满足由于输出偏移失真造成的时序差异。

t sk(P) 用于衡量占空比失真造成的时序问题。这在 DDR SDRAM等双边沿采样的应用中尤为关键。

t sk(pr) 也是不可避免的器件误差,其对设计者的指导意义在于,应避免将器件理想化。对一系列时序密切相关的信号,如果在链路中通过了不同的逻辑器件,即便逻辑器件型号一致,在接收端仍可能存在时序的偏差,该偏差应在时序裕量计算中得到充分考虑。

图3.11 逻辑器件输出偏移失真

下面以表3.7为例,说明一种器件的操作特性参数表的内容。

表3.7 74LVC125A操作特性参数表 [27]

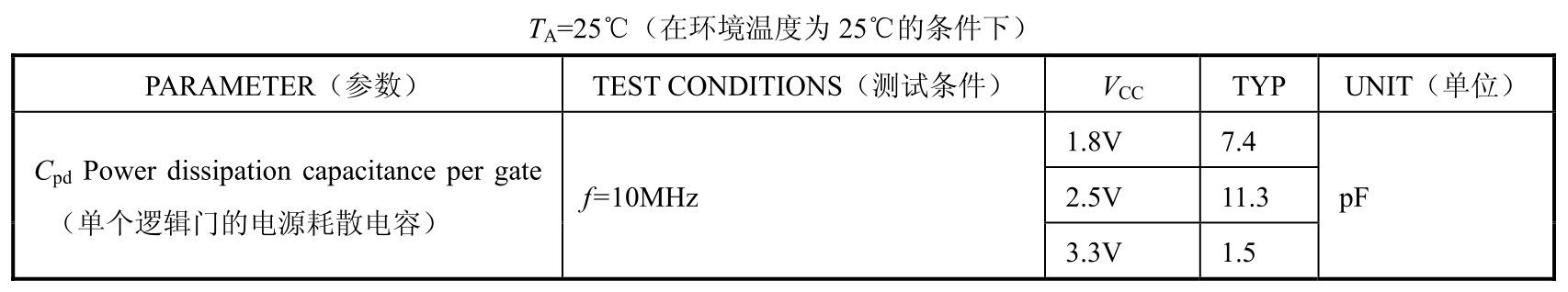

· C pd :电源耗散电容。该参数是在计算 CMOS 工艺的逻辑器件动态功耗时使用的等效电容。

理解要点:

① 在选型时,器件资料的“FEATURES”表是重要的依据。

② 为保证器件的正常工作,电路设计需满足器件资料的“Recommended Operating Conditions”表。

③ 为确定器件工作的时序,需参考器件资料的传输特性参数表。

本小节重点介绍如何计算CMOS工艺逻辑器件的功耗。在3.2.2节对逻辑器件参数的介绍中,提到了许多与功耗相关的参数,如 V CC 、I CC 、C pd 等,那么这些参数将如何影响器件的整体功耗?

逻辑器件资料中,一般都会给出器件工作时的最大功耗 P tot 参数,但这个参数仅能提供最恶劣情况下的功耗估计值,在单板功耗裕量充足时,可使用 P tot 完成粗略的估计,随着单板复杂度的提高,高功耗器件不断增加,单板的功耗分配越来越紧张,要求对器件的功耗估计更贴近实际情况,所以 P tot 并不实用。例如,一个 P tot 参数值为 0.8W 的器件,如果实际应用的信号翻转频率很低,则实际功率将远远小于一个 P tot 参数值为 0.4W。因此,在设计中,有必要将器件的静态功耗和动态功耗区分开,以便根据器件应用场合的不同来评估其实际功耗。

CMOS 器件功耗分为静态功耗和动态功耗 [29] 。当器件所有端口的逻辑状态稳定而不发生变化,则端口无需充/放电,器件内部仅存在泄漏电流 I CC ,此时的功耗就是静态功耗。静态功耗还包括输入端处于非稳态时,由ΔI CC 引起的功耗。当器件端口的逻辑状态发生不断的翻转,器件内部除泄漏电流外,还存在工作电流,且为了驱动容性负载,器件的输出端还需不断充放电,这种由于器件逻辑状态翻转而产生的功耗,称为动态功耗。

静态功耗由两个部分组成。其一,由器件内部泄漏电流产生。CMOS 器件内部,在漏源极与衬底之间,存在寄生的反偏二极管(二极管上承受反向电压),由于二极管内少数载流子的运动,形成反偏电流即漏电流。在逻辑器件资料中,漏电流用 I CC 参数定义(又称为静态电流)。一般漏电流 I CC 很小,随着温度的升高而增大,如 74LVC125A 在 25℃时漏电流仅1μA,而在125℃时漏电流能达到40μA。这一部分功耗的计算公式为

基于制造工艺的不同,逻辑器件的静态功耗差别很大。例如,Bipolar 工艺的 74LS125A,其I CC 参数值为54mA,而CMOS工艺的74LVC125A,I CC 仅为40μA。

因此,Bipolar 器件的静态功耗远大于 CMOS 器件,例如,74LS125A,当 V CC =3.3V时,有P S =3.3V×54mA=178mW;而对于74LVC125A,P S =3.3V×40μA=0.132mW,两者相差1000多倍。

其二,当输入电平不满足器件输入引脚的阈值电平时,器件内部本应完全关断的 MOS管并没有被完全关断,使 V CC 和 GND 之间存在一定的电流通路,由此造成的功耗,也归为静态功耗。在器件资料中,这种电流通路用参数ΔI CC 定义,一般而言,ΔI CC 远大于 I CC ,但漏电流引起的静态功耗是始终存在的,而ΔI CC 引起的静态功耗仅当输入电平不满足输入阈值电平时才会发生。在电路设计中,通过电平转换电路、提高信号的边沿速率,可减小由ΔI CC 引起的静态功耗。

动态功耗分为瞬变功耗P T 和容性负载功耗P L 。

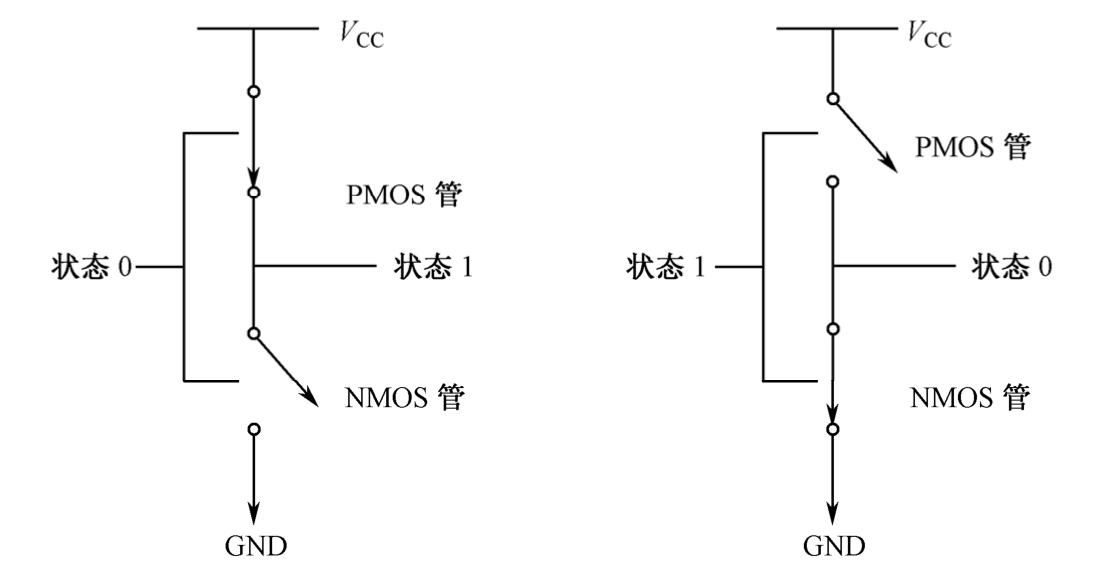

1)瞬变功耗P T

器件逻辑状态改变时,需对内部的容性节点充放电,这个过程存在功率损耗;同时,逻辑状态的改变,伴随着器件内部 MOS 管的开合,如图 3.12 所示,对于 CMOS 工艺的逻辑器件,其输出端口由PMOS管和NMOS管构成,以某CMOS工艺的反相器为例,输入逻辑“0”状态时,输出端口的 PMOS 管闭合而 NMOS 管打开,输入逻辑“1”状态时,PMOS 管打开而 NMOS 管闭合,即理想情况下,任何时候都只有一个 MOS 管闭合导通。在输入状态由“0”变为“1”时,PMOS 管和 NMOS 管的开合状态同时发生改变,受输入信号变化速率和制造工艺的限制,这种开合状态的改变需要一定的时间,因此在某些瞬间,两管同时处于闭合导通的状态,从而形成V CC 到GND的电流通路,造成功耗。

图3.12 CMOS工艺逻辑器件电平翻转 [29]

当输入信号变化速率较快(满足器件Δt/ΔV 参数的要求)时,瞬变功耗 P T 将主要取决于器件内部的节点电容,因此P T 计算公式为

式中 C pd ——电源耗散电容,也是不考虑容性负载时逻辑器件的等效电容,可直接从器件资料上获得;

F I ——输入信号的频率;

N swI ——同时发生状态变化的输入端口数目。

2)容性负载功耗P L

为驱动外部的容性负载,输出端消耗的功率定义为容性负载功耗P L ,其计算公式为

式中 C L ——外部容性负载;

F O ——输出信号的频率;

N swO ——同时发生状态变化的输出端口数目。

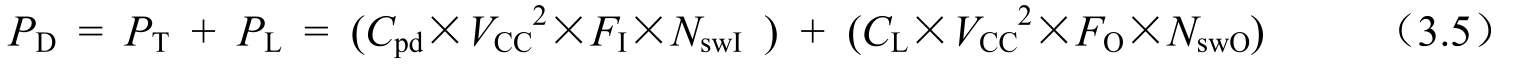

由于动态功耗P D 等于瞬变功耗P T 与容性负载功耗P L 之和,其计算公式为:

总功耗P计算公式为

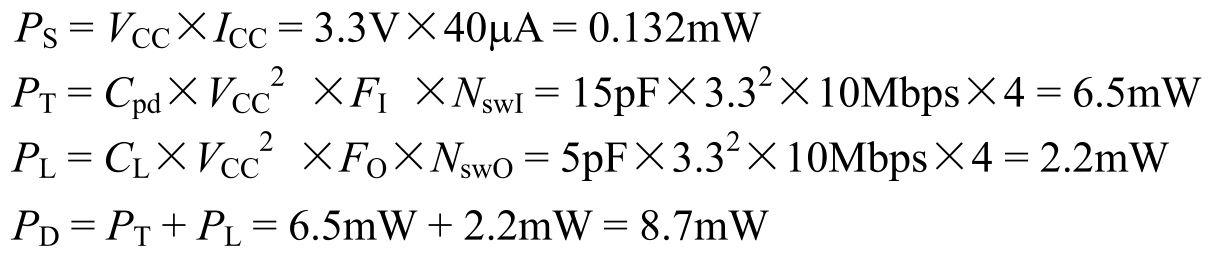

例如,使用 74LVC125A 作为 4 比特数据总线驱动器,数据信号波特率为 10Mbps,供电电源 V CC =3.3V,每个输出引脚的容性负载 C L 为 5pF。从器件资料上可以获得以下参数:I CC (max)=40μA,C pd =15pF,则功率计算为

因此,总功耗P的计算结果为

P=P S +P D =0.132mW+8.7mW=8.832mW

即使考虑20%的裕量,总功耗也仅为11mW,远远小于器件资料上给出的P tot 参数值。

理解要点:

逻辑器件的功耗由静态功耗和动态功耗构成,而动态功耗又分为瞬变功耗和容性负载功耗。

除提供与、或、非、总线驱动等逻辑功能外,逻辑器件还可作为热插拔单板的接口保护器件。

通信设备多由主控板、若干业务板、风扇板、时钟板、电源板等构成,在使用中,经常需要带电插拔某些单板。带电插入时,单板的电源、地以及输入/输出端口几乎同时与背板上的电源、地以及信号线相接触,由于单板电源存在较大的容性,上电缓慢,因此存在输入/输出端口到电源平面或地平面的电流通路,构成倒灌,可能造成对单板接口器件的损坏。同样的情况也出现在带电拔出时。

为了实现单板的热插拔,接口器件应满足一定的要求。根据级别的不同,热插拔可分为以下四个等级 [30] ,这四个等级对接口器件提出了不同的要求。

级别0 ,级别0的器件完全不支持带电插拔,在插拔前必须先关断主电源。绝大多数常用的逻辑器件系列都属于级别 0,如 AC、ACT、AHC、AHCT、ALS、ALVC、AS、F、HC、HCT、HSTL、LS、S、SSTL、TTL等。

级别 1 ,级别 1 的逻辑器件支持局部掉电(Partial-Power-Down)。该特性支持器件掉电时,关断接口到电源的通路,以免接口信号的电流倒灌到电源引脚,损坏器件。但插拔前,主系统必须先暂停接口信号的传输。级别 1 要求接口器件支持 I off 特性。以下逻辑器件系列属于级别1:AVC、LV、LVC、GTL等。

级别2 ,级别2的逻辑器件支持热插拔(Hot Insertion)。除级别1的功能外,还可防止插拔时可能产生的总线冲突。要求接口器件支持I off 、PU3S特性。以下逻辑器件系列属于级别2:ABT、ALVT、LVT等。

级别3 ,级别3的逻辑器件支持在线插拔(Live Insertion)。除级别2的功能外,还能保证单板插拔时接口总线的数据不受影响。要求接口器件支持I off 、PU3S、BIAS V CC 特性。以下逻辑器件系列属于级别3:GTLP等。

以下分别分析I off 、PU3S、BIAS V CC 三种特性。

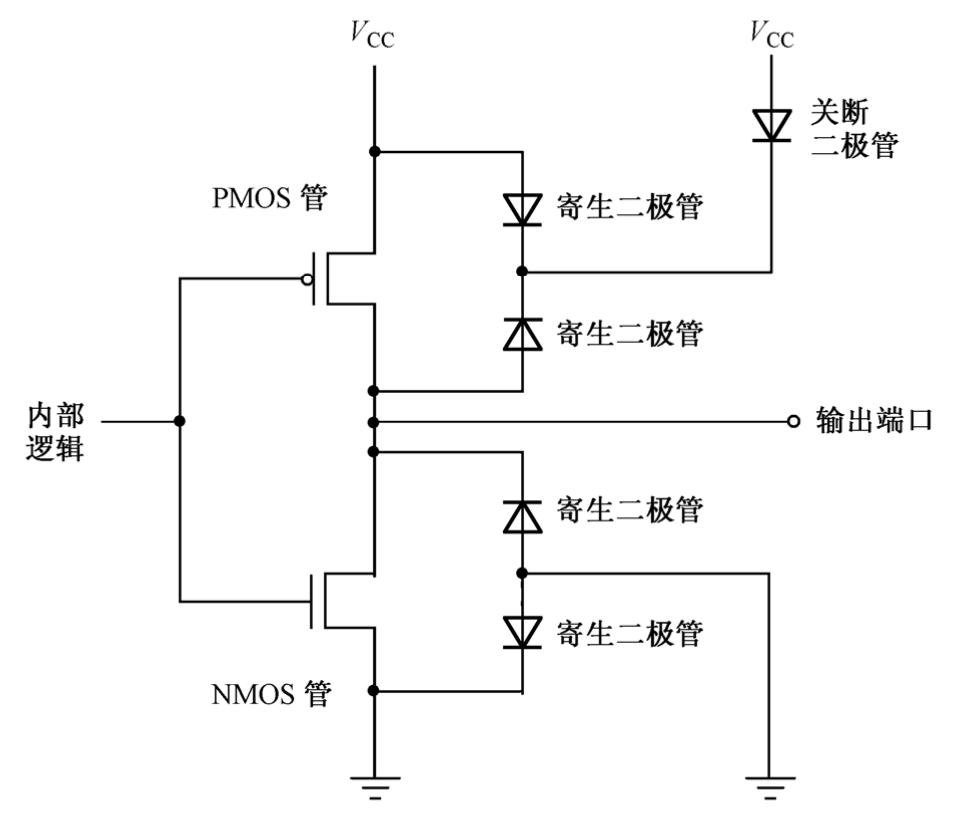

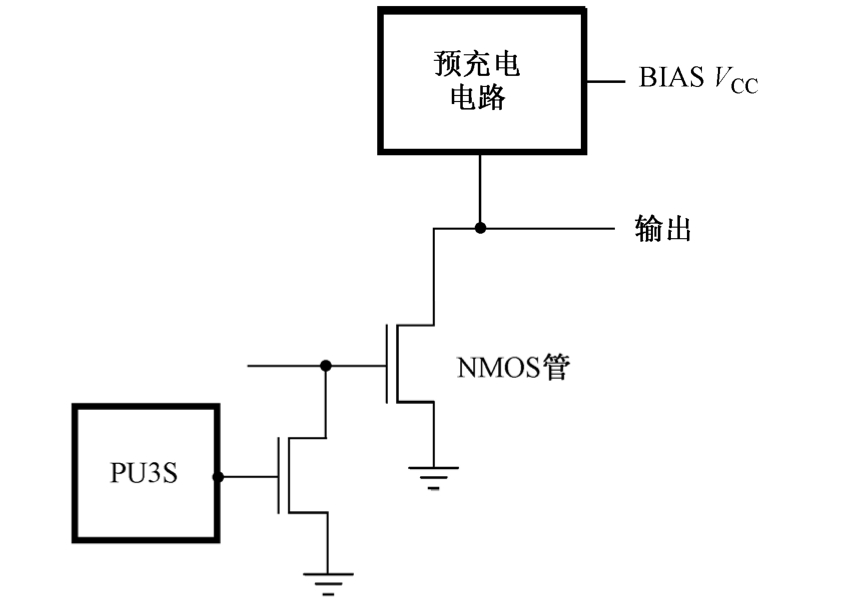

图3.13所示为支持I off 特性的CMOS器件输出端口结构图。与通常的CMOS器件输出端不同的是,I off 特性要求在输出端增加一个关断二极管。

图3.13 I off 结构 [26]

逻辑器件下电时,V CC 电平变为零,但输入/输出端口仍与其他处于工作状态的器件相连,端口上存在一定的电流,如器件端口不包含关断二极管,该端口电流将通过 PMOS 管的寄生二极管流入V CC 引脚。而关断二极管的作用正是阻断该通路。

判断一个逻辑器件是否支持 I off 特性,方法是查看器件资料上是否包含 I off 参数的描述。

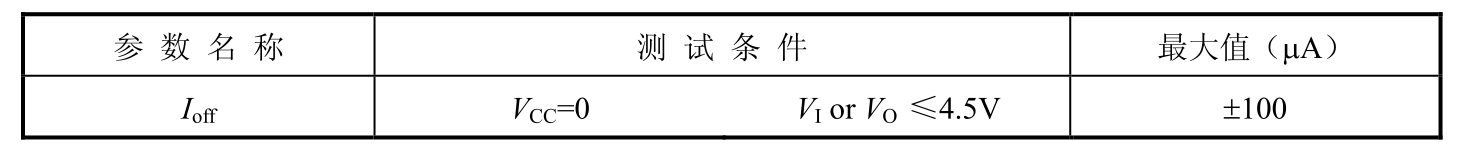

如TI公司的74ABT125器件资料上列有I off 参数,见表3.8。

表3.8 74ABT125 I off 参数

参数 I off 是指,当器件下电即 V CC =0 时,输入或输出端口通过关断二极管的泄漏通道,能流入V CC 引脚的电流最大值为100μA。

I off 结构图中,关断二极管处于PMOS管和V CC 之间,那么在NMOS管和GND之间是否需要同样的二极管?答案是否定的,因为 NMOS 管的寄生二极管已经起到了关断二极管的作用。

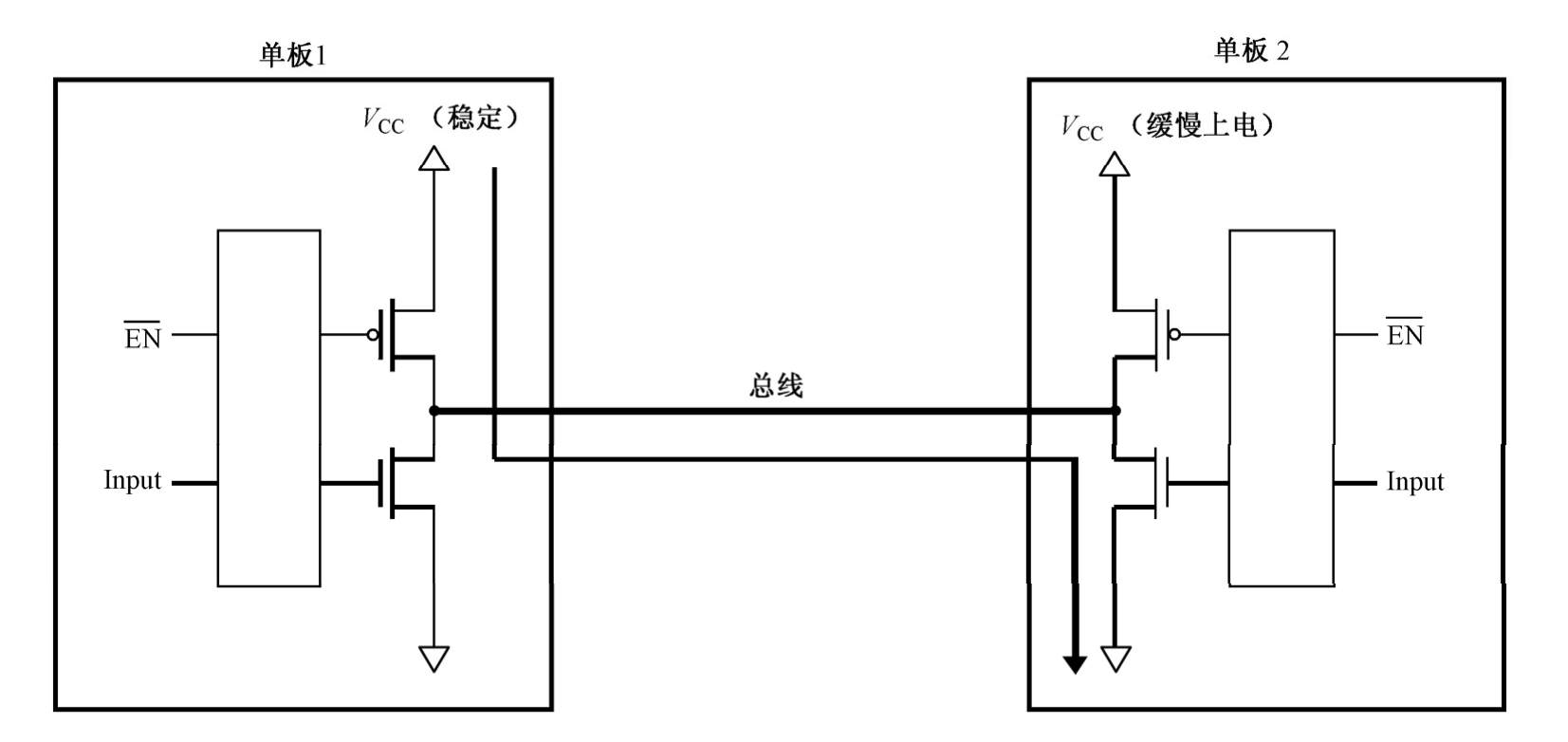

如图 3.14 所示,单板 1 和单板 2 的接口器件是同相驱动器,它们都拥有低电平有效的使能信号 EN#。单板 2 上同相驱动器的 EN#和输入端都通过电阻下拉到地。单板 1 工作时,将接口总线驱动为高电平(CMOS 的上管导通),此时,插入单板 2,由于单板 2 的V CC 上电需要一段时间,而EN#和输入端的状态都为低,因此单板2将驱动输出端口为低电平(CMOS 的下管导通),从而,在单板1 的V CC 和单板2 的 GND 之间出现了一条低阻抗的电流通路,两个接口器件都存在被损坏的可能。

图3.14 上电时的板间总线 [31]

解决方法是使接口器件在V CC 上电完成之前,输出端口保持高阻而不对任何输入信号作出响应,这种解决方法称为上电三态(PU3S)。

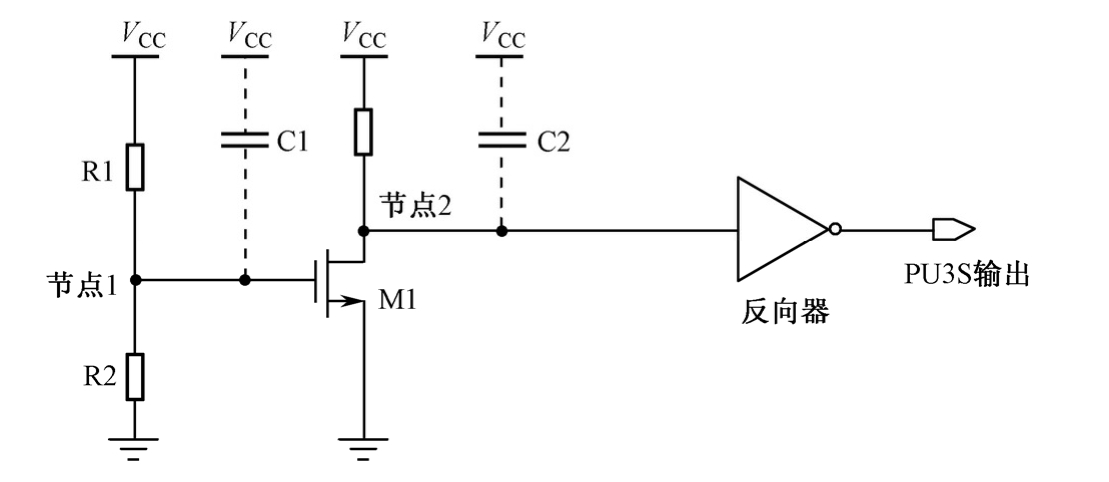

支持 PU3S 的逻辑器件内部包含图 3.15 所示的 PU3S 结构,PU3S 输出低电平时,器件输出端呈现高阻态,只有在 PU3S 输出高电平时,输出端才能对输入端的信号做出正常响应。

PU3S结构中,R1和R2构成分压电路,使M1管只有在V CC 的电平超过阈值后才能导通,因此在 V CC 上电的过程中,节点 2 保持为高电平,驱动 PU3S 输出低电平,V CC 上电完成后,M1导通,节点2变为低电平,驱动PU3S输出高电平,器件输出端开始正常工作。

图3.15 TI公司逻辑器件的PU3S结构 [31]

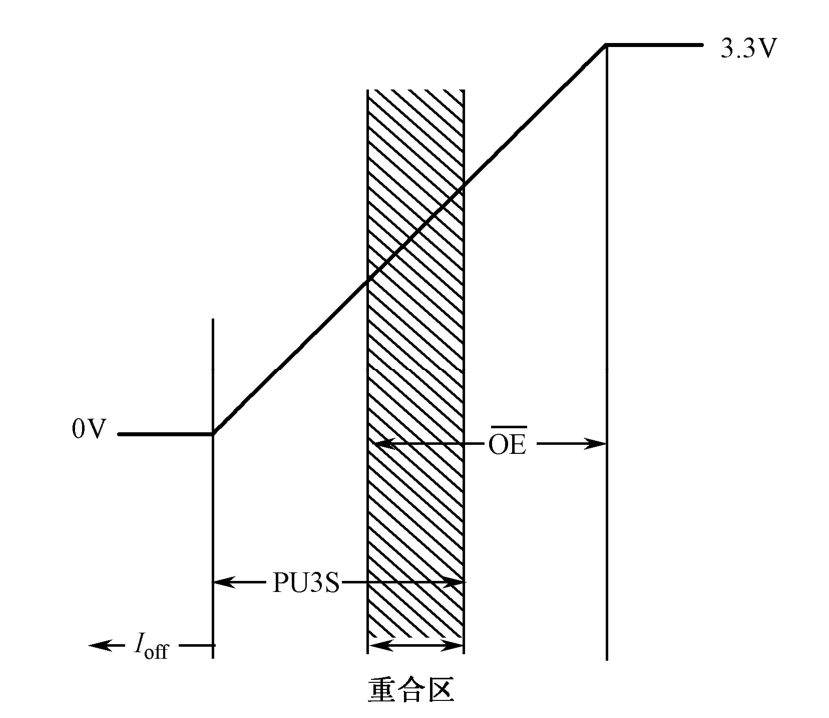

单板热插拔时,对接口器件输出状态的控制是很有必要的。根据V CC 上电的步骤,可将该控制过程分为三个阶段,即I off 阶段,PU3S阶段,OE#控制阶段,如图3.16所示。

图3.16 控制输出端口状态的三阶段 [31]

阶段1 ,V CC =0V时,I off 结构利用关断二极管阻断输出端口与V CC 之间的通道。

阶段2 ,V CC 上电过程中,PU3S结构使输出端口呈现高阻态。

阶段3

,V

CC

上升达到阈值后,PU3S释放对输出端口的控制权,交由

控制。

控制。

阶段 2 和阶段 3 存在一个重合区,其目的是确保接口器件对输出信号的完全控制,在设计中,建议将

信号弱上拉到V

CC

。

信号弱上拉到V

CC

。

在 PU3S 结构中,由于 C1、C2 等电容的存在,当 V CC 上电过快时,PU3S 结构不能正常工作。因此,在支持 PU3S 特性的逻辑器件资料中,提出了对上电速率的要求,由参数Δt/ΔV CC 定义,如 74ABT125,要求Δt/ΔV CC 不小于 200μs/V。在对接口逻辑器件的测试中,应注意对该参数的测量。

在功耗测试中,设计者有时会发现单板上电时电流很大,甚至数倍于单板正常工作时的电流,这往往是由于电源上电过快造成的。因此,对存在上电速率要求的电源,应增加电容或使用缓启动电路。

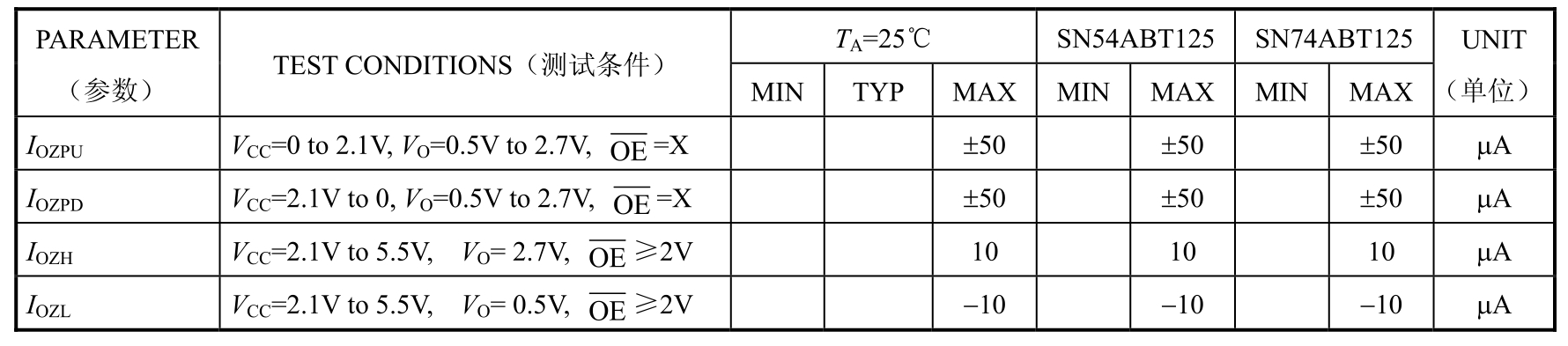

器件资料上与 PU3S 相关的参数有四个,如表 3.9 所示为摘取自 TI 公司 74ABT125 器件资料。

表3.9 与PU3S相关的器件参数表 [32]

I OZPU :指在V CC 上电过程中(达到阈值2.1V前),输出引脚上流入或流出电流的最大值。

I OZPD :指在 V CC 下电过程中(由阈值 2.1V 降为 0V),输出引脚上流入或流出电流的最大值。

I

OZH

、I

OZL

:指当 V

CC

达到阈值电平后,由于输出使能信号

无效,导致输出端口处于高阻态,此时,输出端口上流入或流出电流的最大值。输出高阻态时,输出端口可能处在任何电平位置,如处在高电平,电流用 I

OZH

定义,处在低电平,则用 I

OZL

定义,高阻态时的电流都很小,仅为数微安。由此可以看出,输出高阻态与输出的电平状态无关,此时,输出端的电平可能处于任何位置,但输出电流极小,不具有驱动负载的能力。有些设计者认为,输出高阻时,输出端口的电平为 0,而事实上,输出高阻只是对输出驱动能力的定义,与电平没有任何关系。

无效,导致输出端口处于高阻态,此时,输出端口上流入或流出电流的最大值。输出高阻态时,输出端口可能处在任何电平位置,如处在高电平,电流用 I

OZH

定义,处在低电平,则用 I

OZL

定义,高阻态时的电流都很小,仅为数微安。由此可以看出,输出高阻态与输出的电平状态无关,此时,输出端的电平可能处于任何位置,但输出电流极小,不具有驱动负载的能力。有些设计者认为,输出高阻时,输出端口的电平为 0,而事实上,输出高阻只是对输出驱动能力的定义,与电平没有任何关系。

I off 和 PU3S 实现了对接口器件的硬件保护,但并不能保护接口总线上正在传输的数据。利用BIAS V CC 结构可预充电待插入单板的输入/输出接口,避免对正处于工作状态之中的总线构成干扰。

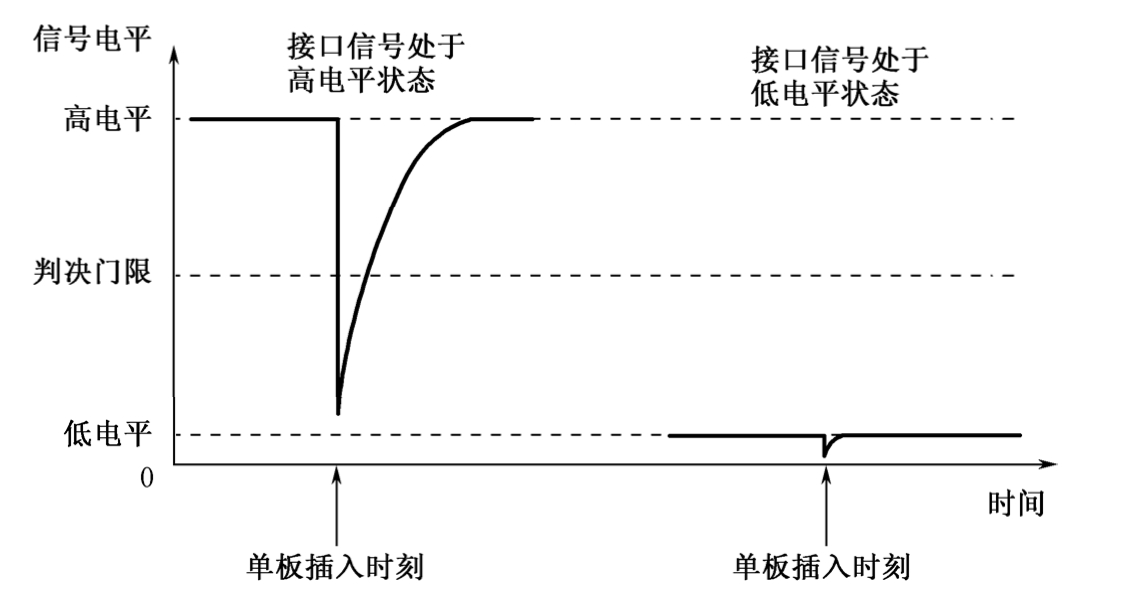

接口器件的引脚都存在一定的容性,而电容的作用是阻碍信号电平的变化,单板插入时,单板上接口器件的引脚电容倾向于将信号电平拉低,待电容充电完毕后,信号电平才能得以恢复。

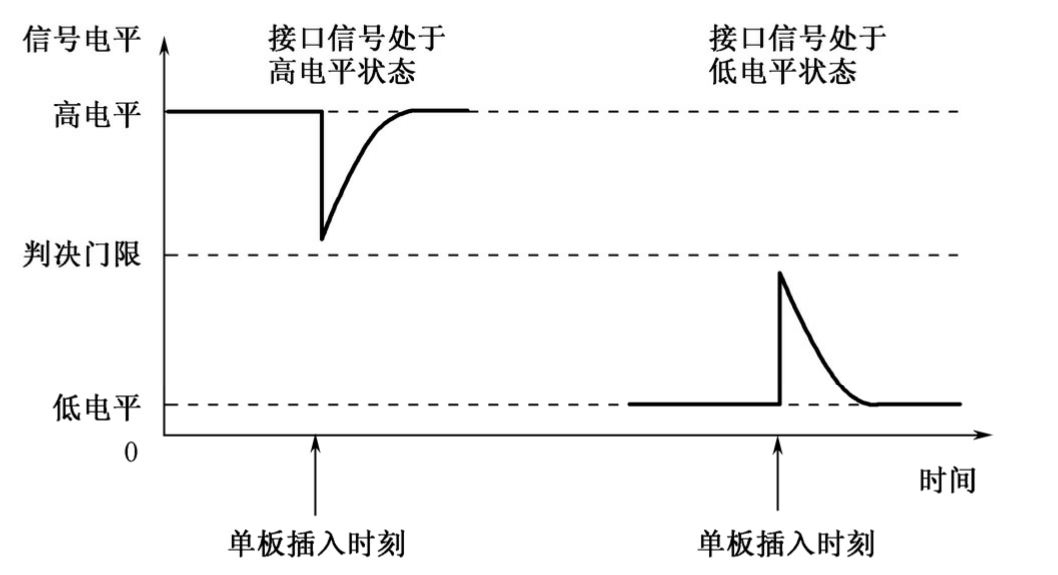

图 3.17 显示了接口信号处于高电平和低电平时,单板插入对信号产生的影响。尤其是接口信号处于高电平时,单板的插入事件可能将信号拉低至判决门限以下,引起逻辑状态出错。

图3.17 单板插入时对接口信号的影响

如图3.18所示,在逻辑器件引脚上增加一个预充电电路,该电路由BIAS V CC 供电(一般而言,BIAS V CC 的电平与V CC 相同,但早于接口器件的V CC 引脚上电),在信号引脚与背板连接器接触之前,使之预充电到某一电平,例如,该电平可以选择为判决门限电平,当信号引脚与背板连接器接触时,由于引脚容性,接口信号仍会被拉向判决门限电平,但不会跨越该门限,因此不会发生判决错误。如图 3.19 所示,可以看到采用预充电电路的单板插入时对接口信号的影响。

图3.18 BIAS V CC 结构

图3.19 采用预充电电路后单板插入时对接口信号的影响

器件资料中,与BIAS V CC 相关的参数有BIAS V CC 、I CC (BIAS V CC )。

· BIAS V CC :指预充电电路的电源,该电源应先于V CC 上电。

· I CC (BIAS V CC ):指预充电电路的电流,该电流一般很小。

例如,支持 BIAS V CC 特性的 74GTLPH1645,其器件资料中对 BIAS V CC 的推荐值为3.15~3.45V,而I CC (BIAS V CC )参数的最大值为5mA。

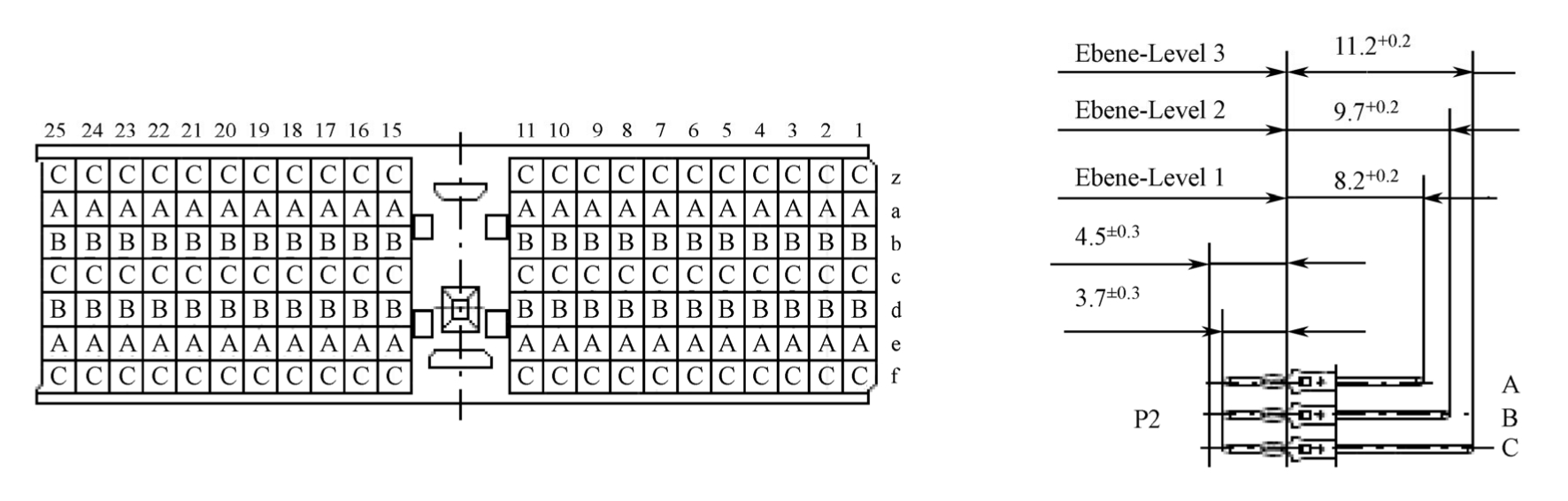

BIAS V CC 结构对信号连接器的选型有一定的要求,要求接口器件的 BIAS V CC 和 GND引脚先与背板连接器相接,以便实现预充电。因此,为实现在线插拔,应选用长短针式信号连接器。

图 3.20 为 ERNI 公司的 2mm 公口连接器,型号是 134802。该连接器的插针长度分三类:A、B、C,其中A类最短,C类最长。连接器分7排25列,最边上的两排(z和f)一般作为屏蔽插针,接单板的信号地GND,可供信号和电源使用的是5排25列。

为实现在线插拔(Live Insertion),GND和BIAS V CC 应选择最长的插针,即C类,而接口信号可选择次长的插针,即B类或A类,V CC 应选择最短的A类。

图3.20 长短针连接器示例

理解要点:

选择支持热插拔功能的逻辑器件时,根据热插拔的等级,需考虑逻辑器件是否支持I off 、PU3S、BIAS V CC 功能。

(1)根据需要选型,不建议盲目地选择性能最好的器件。逻辑器件成本不高,设计者往往会选择同系列中性能最好的型号。例如,总线驱动器有 74LV125A、74LVC125A、74LVT125、74ABT125 等,驱动能力依次从弱到强,设计中盲目地选择驱动能力最强的器件,一方面可能造成辐射增大,产生 EMI(电磁干扰)问题,另一方面也可能导致输出信号过冲太大,超出接收器件输入电平的范围。

(2)时序设计中不能依赖逻辑器件的延时。逻辑器件都具有片内传输延时,但是该参数的器件间差异性较大,不能在设计中被利用。

(3)使用具有总线保持功能的器件时,外部上、下拉不能太弱(即电阻阻值不能太大)。

(4)未用的输入端口电平为CMOS时,需做上、下拉处理。

(5)电源上电速率、输入信号边沿速率应满足器件资料中对应参数的要求。

(6)在热插拔接口器件的应用中,为防止冲击,输出端一般应串联 50Ω电阻,输入端一般应串联 100~200Ω电阻。此时,应确认串联电阻不会对信号电平产生分压影响,以致输入端电平不能满足要求。

(7)当存在热插拔要求时,应根据热插拔的级别,选择对应的器件。