某产品支持业务板的带电插拔,主控板通过业务板的在位信号判断业务板插入或拔出的状态。测试时发现,主控板能检测到业务板的插入,但有时,不能检测到业务板的拔出。

【讨论】

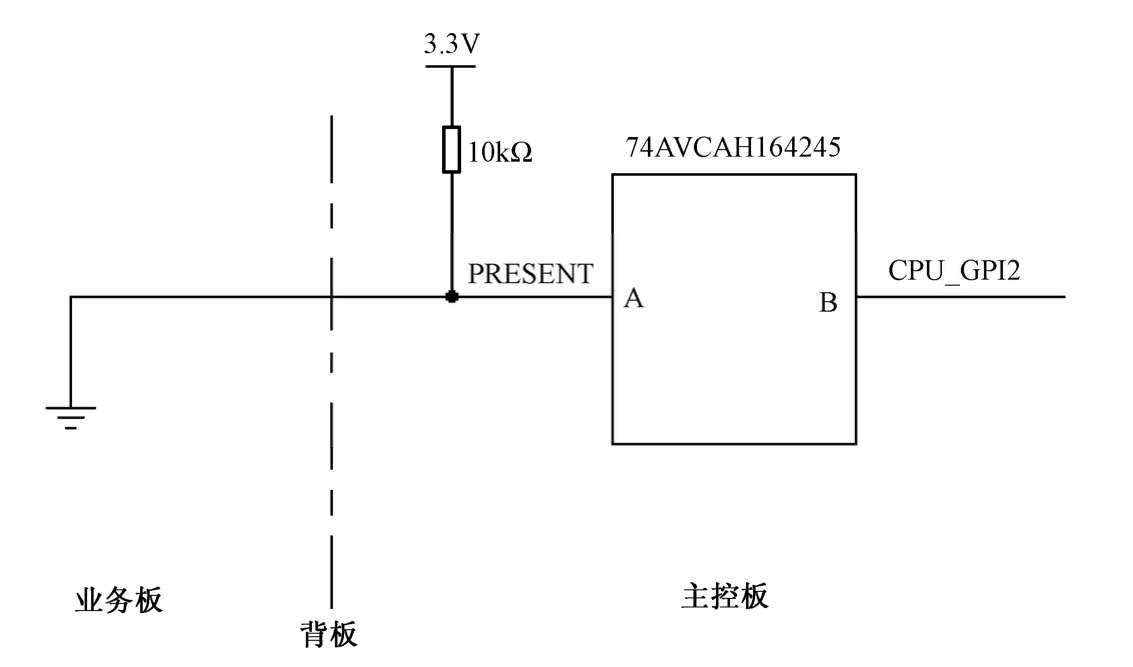

该产品业务板热插拔监控电路如图3.1所示。

图3.1 业务板热插拔监控电路

业务板的在位信号(PRESENT)通过背板连接到主控板逻辑驱动器件74AVCAH164245 的输入端,在业务板上,该信号直接接地,在主控板上,该信号通过10kΩ电阻上拉到 3.3V,PRESENT 信号经驱动后得到 CPU_GPI2 信号,连接到 CPU 的GPIO(通用输入/输出接口)。当业务板插入时,在位信号变为低电平,CPU_GPI2输出低电平,通知 CPU,该槽位的业务板已插入;当业务板拔出时,在位信号变为高电平,CPU_GPI2输出高电平,通知CPU,该槽位的业务板已拔出。

业务板插入时,测量 CPU_GPI2 信号,测得低电平,因此主控板能检测到业务板的插入事件;业务板拔出时,测量 CPU_GPI2 信号多次,发现有时该信号不能变为高电平,导致主控板无法识别业务板的拔出,此时,在主控板上同时测量PRESENT信号,信号状态正确,即拔出业务板后,PRESENT 信号能迅速变为高电平。因此问题定位为,当74AVCAH164245的输入端发生电平由低到高的转换时,输出端不能产生相应的电平变化。

74AVCAH164245 是一种具有总线保持(Bus Hold)功能的驱动器。查阅器件资料,该器件对电平翻转时的电流有一定要求,由参数I BHLO 和I BHHO 定义。

I BHLO 的最小值为525μA,指当电平发生由低到高的翻转时,驱动器应至少吸收电流525μA (接收端电流方向为输入,因此是正电流);I BHHO 的最小值为-525μA,指当电平发生由高到低的翻转时,驱动器应至少输出电流525μA(接收端电流方向为输出,因此是负电流)。

当业务板插入时,逻辑器件74AVCAH164245输入端的电平发生由高到低的翻转,电流从逻辑器件流向地平面,因此逻辑器件能准确识别该电平变化,驱动 CPU_GPI2 为低电平。当业务板拔出时,逻辑器件输入端的电平发生由低到高的翻转,电流由 3.3V 电源平面经 10kΩ电阻流入逻辑器件输入端,提供的电流为 3.3V/10kΩ=330μA,达不到 I BHLO 最小值的要求,因此逻辑器件无法准确识别输入电平的翻转,也就不可能将 CPU_GPI2 信号驱动为高电平。

在改板设计中,将上拉电阻阻值由10kΩ改为1kΩ,热插拔监控功能恢复正常。

【拓展】

本案例中的逻辑器件具有总线保持功能,那么该功能有何实际意义?

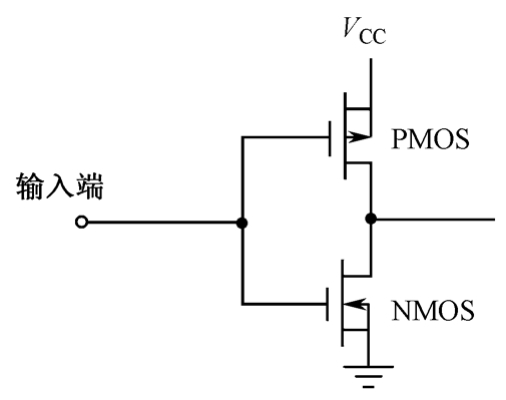

常用的逻辑器件,如 74LV、74AC、74AHC、74HC等系列,都属于 CMOS 器件。CMOS 器件的输入端由栅极连接在一起的一对 PMOS 和 NMOS 构成,如图 3.2 所示。当输入低电平时,PMOS 导通而 NMOS 关闭,输入高电平时,PMOS 关闭而 NMOS 导通,在理想状况下,两个MOS管不会同时导通。

图3.2 CMOS器件输入端

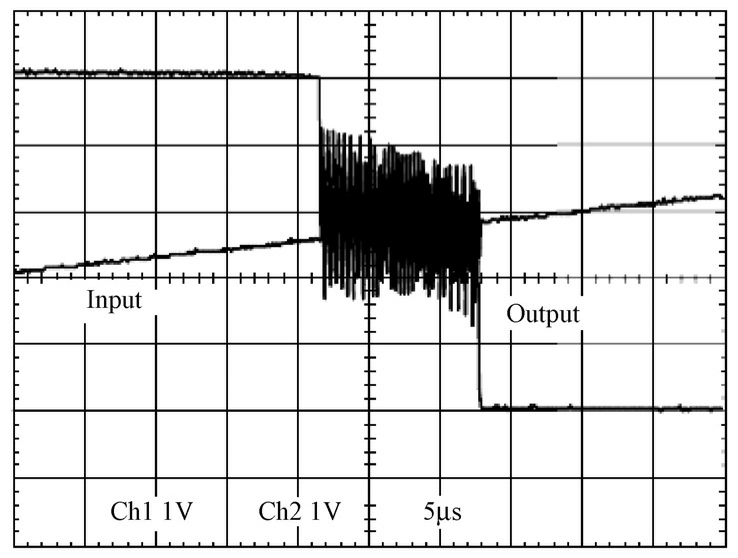

但是,在输入信号的高电平 V IH 和低电平 V IL 之间,存在一段区间,称为非稳态区间。例如,74AVCAH164245 的 V IH(min) 为 2V,V IL(max) 为 0.8V,因此,该器件的非稳态区间为0.8~2V。在这段区间内,PMOS和NMOS都将部分地导通,以致输出产生振荡。

图3.3是CMOS器件输入端处于非稳态时,输出端发生的振荡波形。

图3.3 CMOS器件输入端处于非稳态时,输出端发生振荡 [25]

有三种情况可能导致输入端处于非稳态:

情况一 ,输入信号的边沿斜率不可能是理想的90°,必然会有一段时间处于非稳态,对于这种情况,只能通过提高输入信号边沿爬升速率来解决;

情况二 ,发生总线冲突,导致在同一个信号上,出现了多个驱动源。这可以通过改进设计以避免这种情况的发生;

情况三 ,输入信号没有驱动源,即完全浮空的情况。

第一种情况是必然发生的,第二种情况可以避免,而第三种情况则常用四种解决方法 [25] 。

以下讨论情况三的解决方法:

方法一当输入信号没有驱动源时,使逻辑器件的输出使能引脚 OE#处于无效状态,以关闭与该输入信号对应的输出。

方法二总线上挂有多个器件,且这些器件可以均等地申请总线的控制权。在这种情况下,使最后一个控制总线的器件在工作完成后,仍然保持对总线的驱动,直到下一个器件申请总线的控制权,才释放出总线。这使得在任何时刻,总线上都存在一个器件作为总线驱动者,任何一个接收器件的输入端都不会浮空。PCI总线即采用了这种机制。

方法三上拉电阻。在逻辑器件的输入引脚上增加一个上拉到电源V CC 的电阻,当输入端失去驱动源时,通过该上拉电阻,V CC 可直接作为输入端的驱动源。采用这种方法时,需要注意满足以下两个要求:

要求一 ,信号的上升沿爬升时间t r 应满足逻辑器件的要求。上拉电阻R P 的计算公式为:

式中 C s ——输入引脚的寄生电容;

n——该信号线上并联器件的数目。

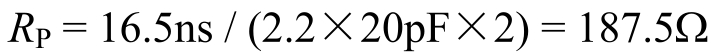

例如,某逻辑器件的上升沿爬升速率要求为 0.2V/ns,电源 V CC 为 3.3V,则 t r 应不大于16.5ns,假设C s =20pF,n=2,则该逻辑器件的输入端上拉电阻R P 计算结果如下:

即只有当上拉电阻阻值小于187.5Ω时,才能满足该器件的上升沿爬升速率要求。

要求二 ,上拉电阻消耗的功率应尽量小。在上例中,上拉电阻上的功耗为3.3 2 /187.5=58mW。

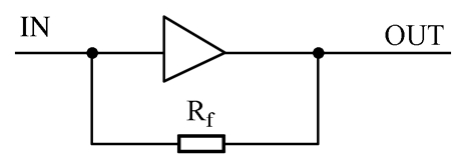

图3.4 总线保持原理框图

为满足要求一,上拉电阻阻值越小越好,而要求二则希望上拉电阻阻值越大越好,在应用中应折中考虑。

方法四总线保持(Bus Hold)。其实现原理是将输出信号通过电阻 R f 反馈回输入端,功能模块图如图 3.4所示。

假设初始状态为,输入端和输出端均为高电平,R f 上没有电流流过。此时如果输入端的驱动源停止驱动,输入端仍可凭借反馈电阻 R f 保持为高电平,R f 上流过电流为漏电流,在器件资料上由参数I OZ 定义,I OZ 很小,一般仅为几微安。

以上针对情况三提出了四种方法。这四种方法都是电路中常见的设计方法。 方法一 需增加 OE#信号,并需要得到外部逻辑电路的配合; 方法二 需得到总线协议的支持; 方法三 需外加上拉电阻,且阻值的选择需根据信号变化沿速率和功耗做出取舍; 方法四 最简单,无需外加元件和辅助电路。

当然在使用具有总线保持功能的器件时,应避免出现本案例所遇到的情况。