直率且诚实的人—如今却需要一个迂回的人。

——《迈向基地》

有句歌词唱得好:“也许你很会说,也许你都不做,没关系,反正也没结果;也许我都不说,可是我都会做,有关系,你就是猜不透。”

请施主们不要望文生义,这里不是《厚黑学》讲座,不会讲如何建立良好的人际关系的事情。这里的“关系”是两个数值比较的意思,也就是“排队队,比个个”的意思。

对了,顺便道个歉。昨天老衲出恭频繁,倒是叫老道顶替了一回,罪过罪过。

一般而言,在数字逻辑系统中,完全不需要判断选择(对应电路里的选择器)的系统不是没有,但是不会太多。说完全没有太绝对了,估计会有人拿出“高阶FIR数字滤波器”等的东西来抬杠。上面的说法里,“不会太多”的论点保险一点。现实世界是充满选择的,因此有了选择苦恼综合征;系统的输出也不是一根筋,因此需要比较和决策。比较是决策的前提,决策是比较的目的,这是辩证法。不懂这个也没有关系,施主们只要知道把系统框图如何变成好的Verilog代码也就够了。举个例子,一个简单的产品筛选系统,首先需要判断产品是不是合格。理论上,合格的才可以出厂。不合格的产品可能又要分成可以返修合格的和无法修理的,这两类的处理可能也不一样。然后可能还要细分和进行不同处理。看到了吧,比较和选择是无时无刻、无处无地不存在的。“学好比较器,才好做代码”。

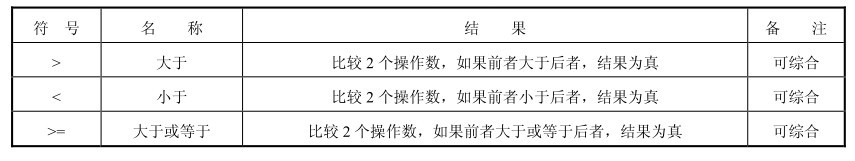

俺们就是“愚公他家——开门见山”,关系操作都是对于两个数值进行的,所谓的“双目操作”。关系操作符包括表3.6中的几个,其中的操作数既可以是无符号数,也允许是有符号数。

表3.6 关系操作符

(续表)

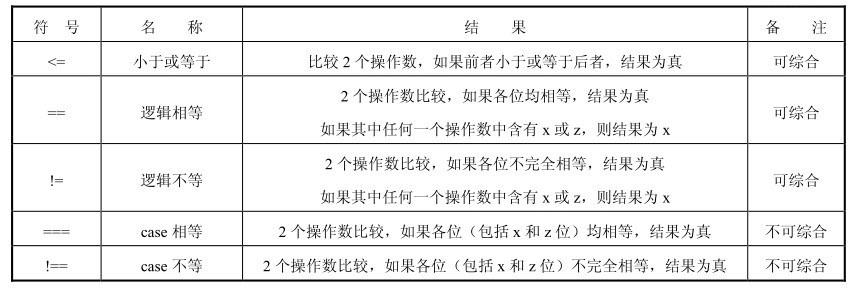

可综合的关系操作的电路元件如图3.7所示。关系操作是有方向性的,一般认为操作是上面的输入相对下方的输入进行的。例如,大于操作,就是a > b,输出result=1;否则,result=0。对于不可综合的“case相等”和“case不等操作”,老衲一如既往不讨论——“敬鬼神而远之”,子曾经曰过。

图3.7 关系操作的电路元件

例3.12给出了一个集合各种关系操作的模块,供大家参考。

【例3.12】各种关系操作

module relational_operators

(

input[3:0]a,b,

output greater,lease

,no_lease,no_great

,equal,no_equal

);

//Definition for Variables in the module

//Load other module(s)

//Logical

assign greater=(a > b);

assign lease=(a < b);

assign no_lease=(a >=b);

assign no_great=(a <=b);

assign equale=(a==b);

assign no_equale=(a !=b);

endmodule

多嘴一句,对于无符号数和有符号数的比较,从代码上看是没有区别的。但是除了相等和不等操作之外,这两类数值的比较在电路上有区别,大家需要注意。

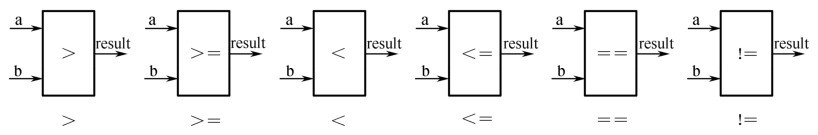

另外,对于相等和不等的操作,可以用逻辑操作来简化,如例3.13所示。

【例3.13】相等与不等的关系操作与逻辑操作实现

在代码中,如果采用关系操作的代码,或许可以不用注释;但是,如果你用了逻辑操作,还不给代码,就会被判决为人品有问题了,后果很严重。

不难发现,“大于操作”与“小于或等于操作”、“大于或等于操作”与“小于操作”互为反操作,如 ~(a > b)和a <=b的值是一样的。

这些都是基本知识,相信施主们自然是了熟于胸的,老僧这里倒是多嘴了。老僧说这个事情的关键在于偷懒,下面只介绍“大于操作”这个东西,也就相当于介绍了四种比较操作的全部了,还不能算是以偏概全。

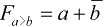

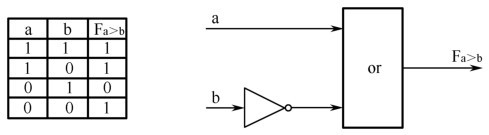

先看最简单的1比特宽度比较操作情况,参考《数字电子技术》教材中的公式

,其真值表与电路如图3.8所示。

,其真值表与电路如图3.8所示。

图3.8 1比特宽度比较操作

这看着还可以接受,少安勿燥,再来看看2比特的情况。

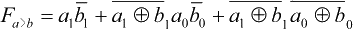

依然参考《数字电子技术》教材中的公式

。有点复杂了吧?这个时候,请允许在下用1比特的比较操作来实现,这样能稍稍简化一些。具体电路如图3.9所示,该图看起来也还好,不算非常复杂。但是提醒一下大家,这里面每个1比特比较操作都是由很多门电路实现的。

。有点复杂了吧?这个时候,请允许在下用1比特的比较操作来实现,这样能稍稍简化一些。具体电路如图3.9所示,该图看起来也还好,不算非常复杂。但是提醒一下大家,这里面每个1比特比较操作都是由很多门电路实现的。

图3.9 2比特宽度比较操作

还有4比特的情况,这里省略了。鄙人已经没有信心做到一点都不出错了。从2比特到4比特的复杂度绝对不止加倍。

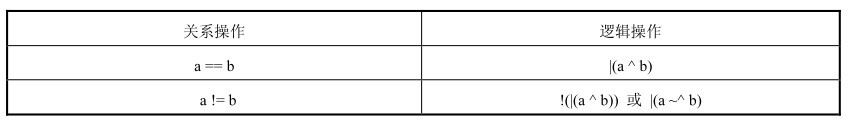

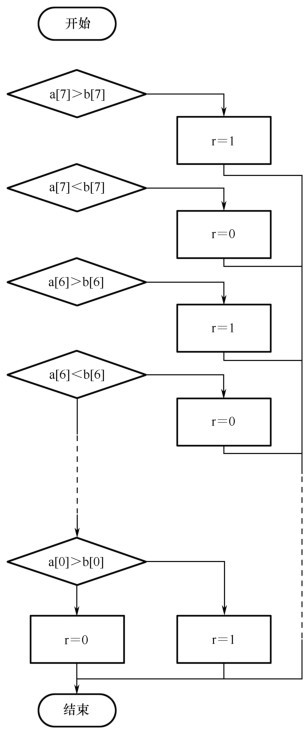

图3.10 8比特宽度“大于”比较器的流程图

高比特宽度的情况,正如前文书的说法,不能用逻辑操作的公式来表示了,原因是太复杂。

说句实话,在这种情况下,对于大多数的应用,直接用Verilog语言里的比较操作也就够了。但是,某家写书,不能就这么一句话结束这一节。因此,继续发扬鄙人特别能“扯犊子”的光荣传统,上演一出莎翁的戏剧:《无事生非》。这里偏偏要用“if”来搞一搞比较操作。另外,下面只讨论无符号数的比较,有符号数嘛?最后咱们再说,也是“照猫画虎”的功夫,大家擅长。

俗话说:“小小孩,老小孩,”今个儿老衲就带大家去小学时候取点经。是的,是小学,您没听错。从现在起,本书后面有很多回到小学的时候,大家要习惯。

“小啊,小儿郎,背着那书包上学堂……”,在小学时,老师是如何教我们比较两个数值的大小的?

“小朋友们,大家坐好!今天我们来学习比较两个数的大小。把两个数放在一起对齐。然后从最高位开始比较:最高位大的数值就大;如果最高位一样,就比较第二位,第二位大的数值就大;……直到比较个位,个位大的数值就大;如果每一位都一样,就是一样大。”

“老师,9比20大,我学会了!”

“什么,老师来看看……我们说对齐,是从个位对齐。谁叫你左边对齐了!”

“啪啪啪……”太暴力,下面省略一万字,南无阿弥陀佛。

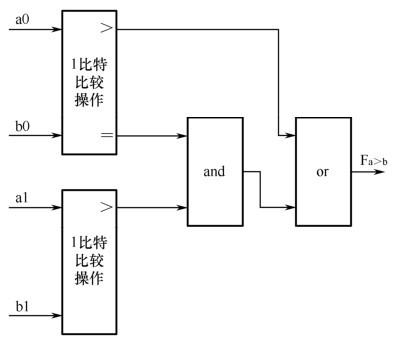

好了好了,牛吹得差不多了。说点正经事情。比较a是否大于b的算法,真的和小学差不多,先扩展位数宽度一致,然后一位位比较,如果相同再向下比;如果不同,假设a在这位是1而b在这一位是0,则输出结果是真的;否则,结果为假。流程图见图3.10(为了简化,假设a和b都是8比特宽度的无符号数)。又有人说了,干嘛不用“for”循环啊?这个估计不用贫僧动手,别人就会把他打成“烂柿子”了,善哉善哉。

其中,有一些逻辑上的等效运算,和大家也掰扯一下。第一,“a[i]^ b[i]”操作相当于公式“a[i]!=b[i]”;其次,“r <=a[1]”等效于运算“(a[i]> b[i])? 1'b1: 1'b0”,或者如果a[i]大于b[i],则r为真“1”,否则,r为假“0”;最后,“(a[0])&& !(b[0]))”对应于a[0]==1'b1 同时 b[0]==1'b0,此时a[0]> b[0]。这些等效,根据采用的综合软件的能力,有时可以简化逻辑。具体推演就算是课外作业了。

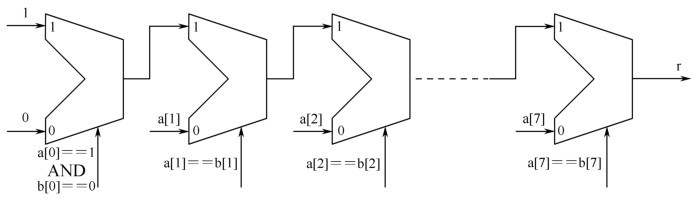

对应的结构图如图3.11所示,可以想到这是一系列串联的选择器。有趣的是,从左边开始画高比特的比较更加简单一些,列位在看的时候要仔细。

图3.11 8比特宽度“大于操作”电路

图3.11里出现了选择器,这个其实是从第五回“穿越过来的”。老衲在这里祈祷:施主们莫提问。施主们数电都得一百分的,在下清楚的。

看到这种“串串”的结构,倒是很容易计算最大的运算时间了:最大运算时间=(单个单元运算时间+单元间传输时延)×级数。大家知道,这个公式里的级数就是输入数字的位宽。因此,在位宽比较大和/或要求建立时间比较短(典型的,就是高速时钟)的情况下,这个“串串香”对数字逻辑设计工程师而言就不好吃了。

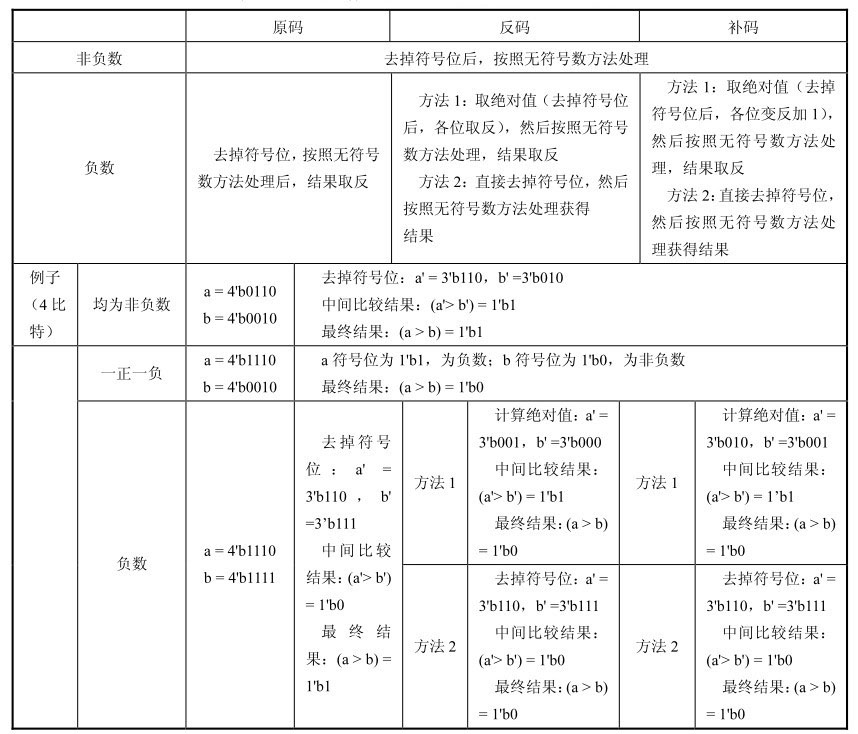

对于有符号数,由于符号位的参与,比较的问题会进一步复杂化。

无论对于何种编码方式,符号位均具有最高的优先权,这个看起来和无符号数有些类似;不同的地方在于该位为“1”反而有可能是小于的象征了。

后面就是比较绝对值部分。对于非负数,去掉符号位就可以和无符号数一样处理了;但是对于负数的处理就和编码方式有关。表3.7给出了大于操作对于不同有符号数编码方式的处理方法。在此基础上,也给出了一些比较的例子。

表3.7 不同编码方式下,有符号数的大于操作

毋庸置疑,对于反码和补码的编码方式,表3.7中的方法2更为简洁。

这正是:

“龙生九子尚有分,输入数字更不等。不怕大小不均衡,关系操作先奇能。比特少时公式生,高位到来链捣腾。如遇高速这个坑,加快还需看后文。”