考TOEFL和IELTS的时候,记住了了一个英文词“Dilemma”。汉语翻译呢,文艺青年叫:“进退维谷”,一般青年是:“窘境”。2B青年会说:“两难。”孟老夫子在几千年前曰“鱼和熊掌不可兼得”,徐克大虾就在《满汉全席》里面解决了这个千年难题:“踏雪寻熊”(附菜谱:用北极白熊的掌,……再加入一碗鲟龙鱼汤……愉悦就无法不从心底里产生了。)。

1.面积与速度的概念

可惜,我们做工程的不能这么不计成本。所以,又有一个装B的词组来了“Trade Off”(记住了,以后忽悠用)。具体到我们的FPGA/ASIC设计,这个“鱼”就是面积,而“熊掌”就是时钟频率(速度)。能不能很好地协调面积与速度的关系,是衡量一个数字逻辑设计工程师能力的一个重要标准。在本书的第2章里面,会说明各种单元模块的不同面积和速度的基本解构;在第6章中,则会通过例子,介绍如何在系统中很好地综合考虑两者的关系,选择比较合适的实现解构(上面那一堆话,就是所谓trade off了)。

先给大家讲一个故事,是我在某著名山寨手机芯片设计厂家的事情。有一次面试一位南洋某著名大学毕业的 Interviewee(被面试者,‘-ee’词根,表示被……者;对应主动的词根是‘-er’,所以我是Interviewer,面试者。Sorry,串台了,今天不是英文课。)。当时,此人主要申请的就是数字逻辑设计工程师。所以,我提问:“请给我设计一个计数器……”。我话声未落,这位老兄就开始写了。于是乎,判语:此人顶多就在学校学过,绝对没有搞过工程。为吗呢?理由1:我没给计数器位数;理由2:我没给时钟频率。在这两个条件缺失的前提下,大罗金仙也不知道该如何设计。天地良心,我真不是故意的,是这位仁兄太心急了。后来呢?后来,此人没有应聘上。再后来,老板不叫我做面试了。因为我面得太严,招不到人。这是我不识时务的结果,大家共勉啊。

这里的“速度”指的是芯片的最高时钟频率,这是个尽人皆知的概念。书说从简,这里不详细论述。

“面积”这个概念来源于 ASIC。我们知道 ASIC 是后期专门生产的,每个 ASIC所占用的资源不尽相同。这个“面积”就是 ASIC 芯片占用单晶硅(Mono-crystalline Silicon)上的面积,是衡量生产数量的一个重要指标。通过面积也可以考察 ASIC 系统的复杂度。

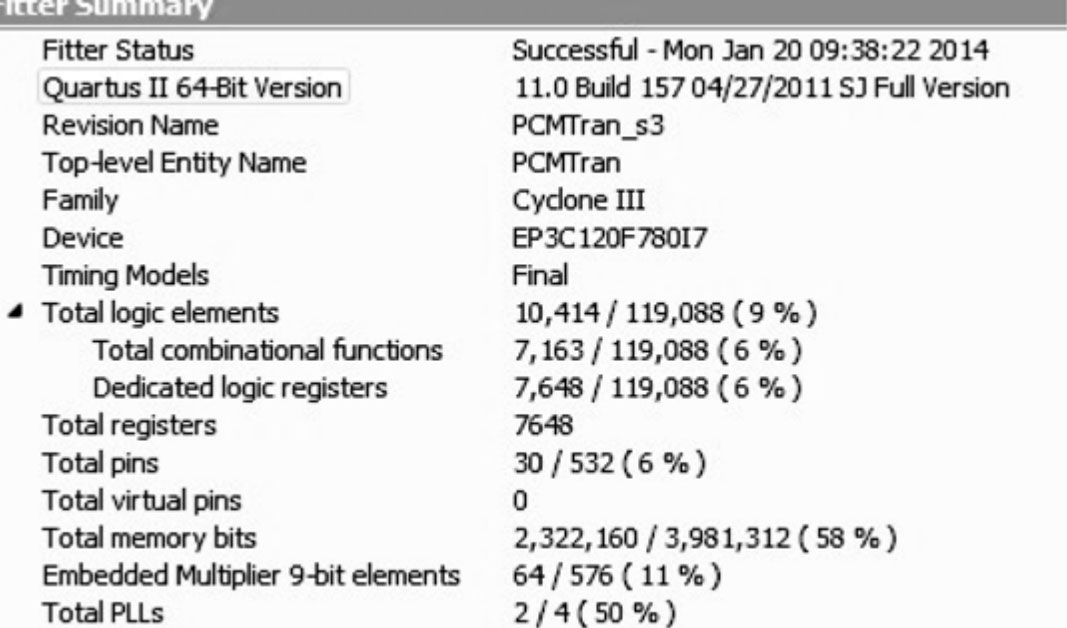

这个名词引申到FPGA领域,当然不是说FPGA芯片内部的大小了。面积指的是FPGA的芯片资源,包括逻辑资源和I/O资源。一般,这个指标通过FPGA的逻辑占用率、布线占用率和管脚占用率表达。这些指标,在布局布线完成后,通过FPGA厂家提供的工具可以统计。每家FPGA的内部架构有所不同,计算的方法也各有差异,因此当你在看FPGA方面的书籍资料的时候经常会看到LUT(Look Up Table,查找表)、LE(Logical Element,逻辑单元)、DFF(D Flip-Flop)、Register(寄存器)等单词。

如果在座的谁有 Xilinx或者 Altera或者其他公司的集成环境,可以准备好。试验一下下,感觉更好。子曾经曰过:“学而时习之,不亦说乎?”图1.22是某公司的统计输出。

图1.22 某设计公司的FPGA占用资源统计

统一地表达,面积就是衡量系统复杂度,或者说成本的一个重要指标。

作为老板的心态,和菜市场上的大妈们是一样的:巴不得不花钱还要买到好菜。具体到芯片的系统架构设计上来,就是要求既要面积小又要速度高。贫僧原来的评价是:这个要求之愚蠢,不亚于“床底下放风筝——异想天开”。后面,贫僧有幸观赏了很多很是“奇葩”和“败家”的设计,才了解到老板们对于人性的丑陋的认识是远远高于某家的。可以说,很多设计都是体现“不能一次把事情做好”这一政治学原理的极好教材,值得老板们来压水分。话说到这里,才发现自己的幼稚。这是闲话,后面不讨论这个问题,都假设我们的设计者是有职业道德的,不会故意瞎设计。

2.速度与面积互换的原则

速度和面积在理想设计上是不可兼得的,但是它们是可以相互转化的。贫僧我“不停地找,不停地问”,虽然不算“上穷碧落下黄泉,两处茫茫皆不见”,也只能找到类似如下的描述。

速度要求的降低可以换取面积的节约。面积越小,就意味着可以用更低的成本来实现产品的功能。速度换面积的原则在一些较复杂的算法设计中常常会用到。对系统架构的设计技术进行改造,将被重复使用的算法模块提炼出最小的复用单元,利用这个最小组合逻辑,通过不同时间调用的方法叫做时分复用。当然,在改造的过程中必然会增加一些其他的资源来实现这个代替的过程。但是只要速度足够慢并且被重用的组合逻辑足够复杂,那么增加的这部分逻辑依然能够实现降低面积提高速度的目的。可以看到,速度换面积的关键是高速基本单元的时分复用。

在这种方法中面积的复制可以换取速度的提高。支持的速度越高,就意味着可以实现更高的产品性能。一些注重产品性能的应用领域可以采用并行处理技术,实现面积换速度。流水线就是一种典型的提高系统速度的方法。在这些算法设计中,流水线设计常常是必须用到的技术。在流水线的设计中,这些被重复使用但是使用次数不同的模块将会占用大量的系统资源。

这些描述是对的,但是对于没有多年功力的初学者而言,就好似佛祖的“拈花一笑”叫人茫然。这样的说法,笔者很不喜欢,所谓“曲高和寡”。孤喜欢热闹,所以要来就来万人齐和的下里巴人。上面的说法足够抽象,不是老夫的风格,下面就用一个计数器例子来说明。

3.面积换速度的例子:计数器七十二变

子曰:“温故而知新,可以为师矣。”鄙人在前面讲过一个在上面的面试典故,不知道现在能记住的还有几人啊(不准翻书!)。里面我叫别人设计一个计数器,被鄙视(太简单了,没花头),然后幸好我反鄙视回去了(不是做工程的,条件不全就开始编码)。

介绍硬件描述语言/FPGA的讲座里面,都会讲到计数器。而且,都在最前面的几节里面,作为一个最简单的时序逻辑的例子。预告一下,这一讲不是不能免俗地重复别人的内容,这里想告诉大家的是一种设计的思想,做不到“人无我有”,也保证做到“人有我新”。这叫“戏法人人会变,各有巧妙不同”。某家试图通过这个看来简单的例子,说一点方法论的玄虚。事先声明,我从来是居心不良的,改不了,所谓“江山易改,本性难移”。只能这么说了:大家遇到我,是你们的不幸。

设问句:在进行一个计数器单元设计之前,我们需要什么前提条件呢?首先,需要功能描述(一个计数器嘛,不就是在不是复位“RST”的状态,每来一个时钟内部/输出加一吗?还描述什么啊?磨洋工吧?——“非也,非也”,这个还是要描述一下。至少我们需要知道一下计数器的内部位数吧?也就是,计数器加到多大才回到0。)另外,就像我们在前面“菜谱”那一讲里面说过的,需要了解系统需要的时钟频率。

这些需求是哪里来的呢?系统工程师?算法工程师?(包不同又要来了。)到了单元设计一类的工作,人家才不会操心呢,就靠数字逻辑设计工程师您自己了。这叫:“自力更生,丰衣足食。”

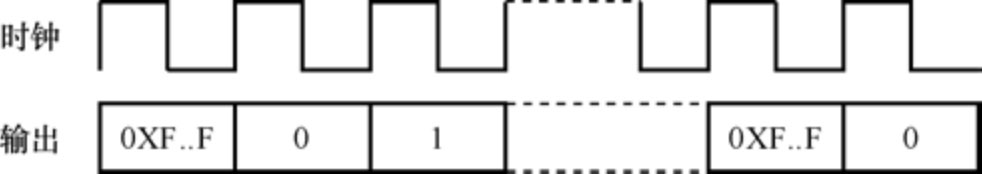

忽略了复位信号 RST 的影响,一个 N 比特计数器,时钟上升沿有效,其时序图如图1.23所示。就是上面所说的“不就是在不是RST状态,每来一个时钟内部/输出加一”。这个是我们所说的行为模型。

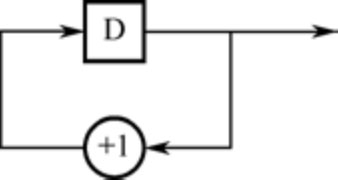

对应的行为级别的电路原理图如图1.24所示。时序逻辑是一个D触发器,组合逻辑是一个N位的“加一”的模块。行为级别的设计的确没有什么花头,而且与时钟频率真的没关系。你就是仿真1000 MHz的时钟,也能得到正确的结果。

图1.23 计数器的时序图

图1.24 计数器的行为级模型

貌似天下太平,可以刀枪入库,马放南山了;然后是“飞鸟尽,良弓藏;狡兔死,走狗烹……”。慢着,本书不是《楚汉演义》,寡人也不是刘邦。你听到1000 MHz不觉得玄乎吗?要有对于危险的直觉的猎人,才是好厨子啊。

首先,贫僧来讲一讲如何提高速度的方法。

所以啊,真的不要因为前仿真通过就沾沾自喜,这仅仅是万里长征的第一步。我们下面要研究建立时间、skew和加一运算的内部位数的关系。

先说点务虚的。一般工程里面不详细区别建立时间与skew这些精细的概念。而是,在这两个时间的基础上加上一个10%左右的裕量,作为信号的稳定时间;稳定时间的倒数呢,就是设计允许最高的时钟频率。

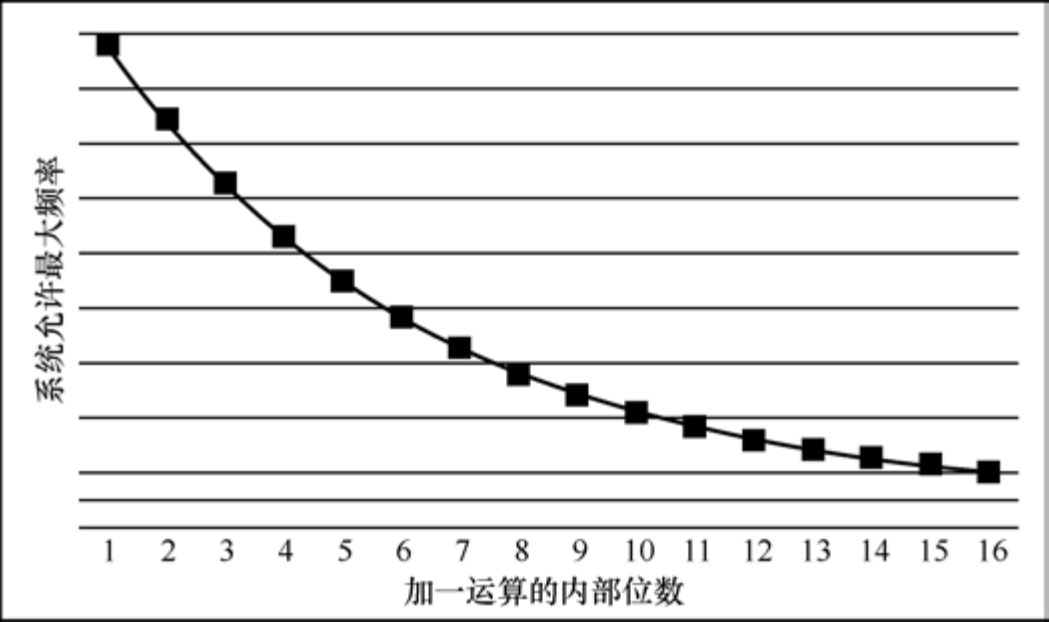

图1.25是一个加一运算的内部位数(也就是计数器输出为主)与设计允许的最高频率之间的大致关系。我自己随便画的,不是仿真的,因为没有相应软件,我又胆小不敢盗版,也不想收到别人的律师涵。(据说某个天线的大拿就因为写讲座收到了仿真软件厂家的律师涵,吓得我……。听说啊,不准转发。我就奇怪了,如果我是那个软件厂家,巴不得给点小钱,叫大侠接着写。多好的广告啊,比养活市场人员便宜多了。总结:这个厂家想不开,该请我去做市场总监。年薪嘛,来个五条黄鱼(金条)好了。)顺便说点正经的,可以看出,随着加一运算内部位数的增加,系统允许的最大频率是急剧降低的。如果同学们有软件,可以帮忙做做仿真给大家共享一个数据,在下不胜感激涕零,在此叩谢了。

图1.25 加一运算踔厉时延与位宽的关系

问题来了:如果系统需要的工作频率和内部加一运算的位数产生矛盾,如之奈何呢?放心,山人自有妙计,这里有锦囊两枚。汝遇到这个场景只须打开一只,问题便可迎刃而解,咳咳咳……(呵呵,假装诸葛孔明,被痰堵住了,对不起观众。)

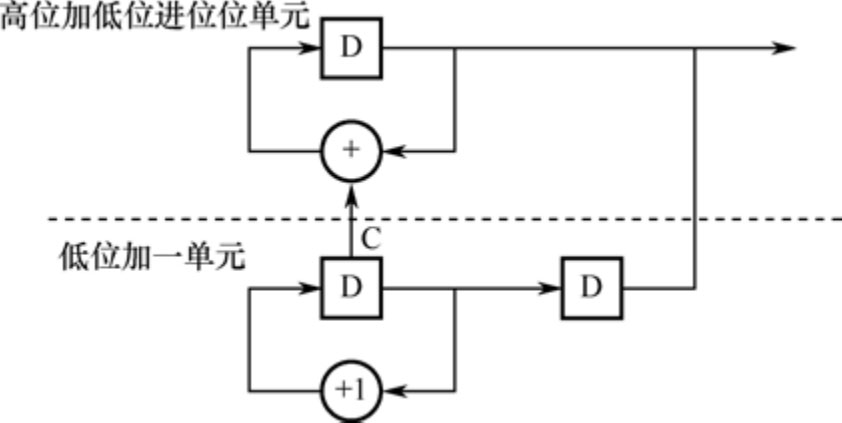

锦囊一 (悟空你又顽皮了,没到时侯呢,就打开啊。):拆分加一单元法(这也叫一刀两断之法。)图1.26是这种方法的结构图,把一个2 N 比特的加一运算分成一个低位加一运算和一个高位加低位进位位的单元。这两个单元分别是几位呢?(“几位”,还“客人楼上雅座请”呢)一般这两部分的运算复杂度差不多,所以也就“二一添作五”地分账了(谁有意见?您竟可以“四六开”、“倒四六”的,我不反对)。低位后面的那个 D触发器是为了同步输出的时序。里面的“C”信号是咩(有观众反映我只用北京方言,这次来个广东话好不。“咩”=“什么”)?正解是低位运算的进位位。最后输出的高低位要拼在一起。

诸位看官,这个系统的工作频率大致等于 N 比特计数器的工作频率了。这个频率指标有了明显的提高;同时呢,系统的功能是没有变化的。这叫万变不离其宗。前面我们说过,IP核设计里面,变化是永恒的。

那么,2 N +1(也就是奇数位数)的计数器怎么办呢?懒得你,学习《小龙人》:“就不告诉你,就不告诉你……”。

锦囊二 :我们重新包装、隆重推出的改进的行波计数器。(行波计数器,第三讲里面不是说不能用吗?为什么又出来了?——好同学啊,竟然还记得那么久之前的事情,子曾经曰过:“孺子可教也”——但是,做工程要细心,某家不是加上了“改进”二字吗?)

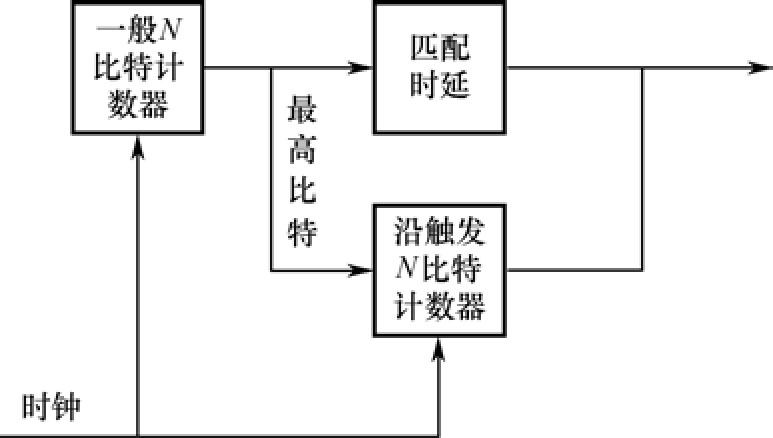

图1.27是针对2 N 比特的计数器的第二种结构。我们按照自顶向下原则,进行一次图纸的设计。

图1.26 计数器的高地位分裂实现

图1.27 计数器的“行波”实现

系统分为两个部分:第一部分是一个一般的计数器;第二部分是若干个沿触发的计数器(图里面只画了一个,多个的自己扩展好了)。匹配时延单元,需要和沿触发的计数器里面的沿检测电路匹配。为了体现系统还是同步的电路,我们专门画上了时钟信号。可以看到,这两个部分的时钟是一致的,系统也就是同步的。

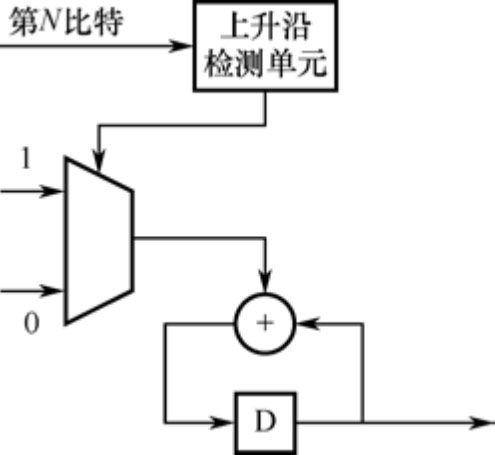

图1.28是沿触发的计数器原理图。这里,利用沿检测电路完成了对于上一级计数器的最高位的采集。使得本单元在输入上升沿时刻完成一次加一操作,而在其他时间不进行操作(也就是加0了)。

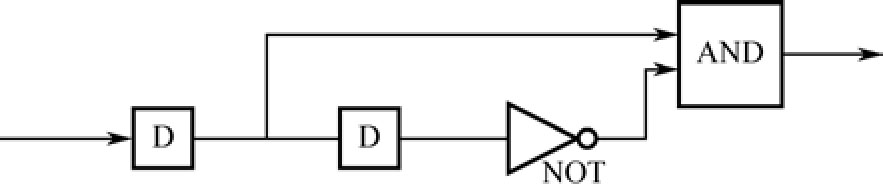

一种沿检测电路如图1.29所示,原理自己分析吧。

图1.28 沿触发计数器

图1.29 沿检测电路

咱们是炒咸菜不放酱油——有言(盐)在先啊,以后像沿检测之类的电路,鄙人就不再提供了。大家都是有学问的人,贫僧说多了就像唐僧了。

就我个人而言,倾向于第一种方案,简单明了。那么,为什么我还介绍了两种方法呢?主要是为了开阔大家的思路。IP核设计这样事情,从来不是只有一条路的(正所谓孟老夫子说的:“条条大路通罗马”)。在设计的时候多想想,说不定还能有点专利什么的,赚点小钱(我的很多专利都是这么来的。钱没赚着,那些流氓公司太抠加上离职就不给钱。)。

比较并行结构和拆分结构,拆分结构的建立时间会增加,面积也会增加,但是允许的时钟频率有所提高。

4.速度换面积的例子:累加器袖中乾坤

花开两朵,各表一支。下面,再聊聊节约面积的方法。

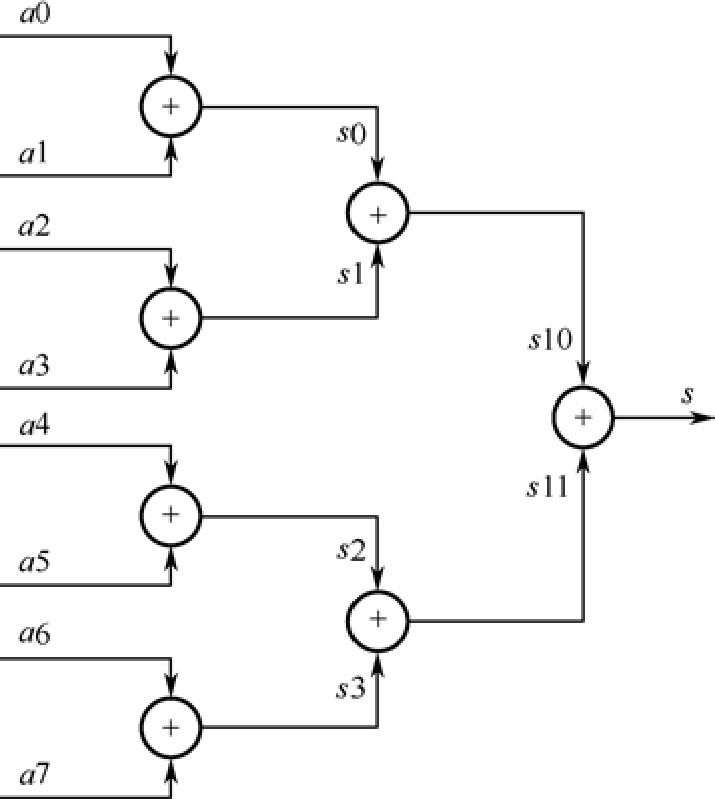

贫僧搞一个不是非工程的简单例子,来说明一下。系统要求计算8个8比特位宽的数字 a 0, a 1,…, a 7和 s : s = a 0+ a 1+…+ a 7。最简单的结构是1个8入1出的加法器,但是这个很不实用。

一般,是用1个2输入的加法器做的:

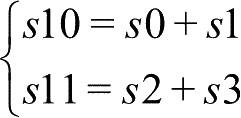

第一级:先算

;

;

第二级:计算

;

;

最后,得到结果: s = s 10+ s 11。对应的结构图如图 1.30 所示,里面用到 7 个加法器。这个数字7说多不多,说少不少的。但是,如果假设不是8个数字,而是64个、128个呢?这个规模就成了“无法承受之多”了。

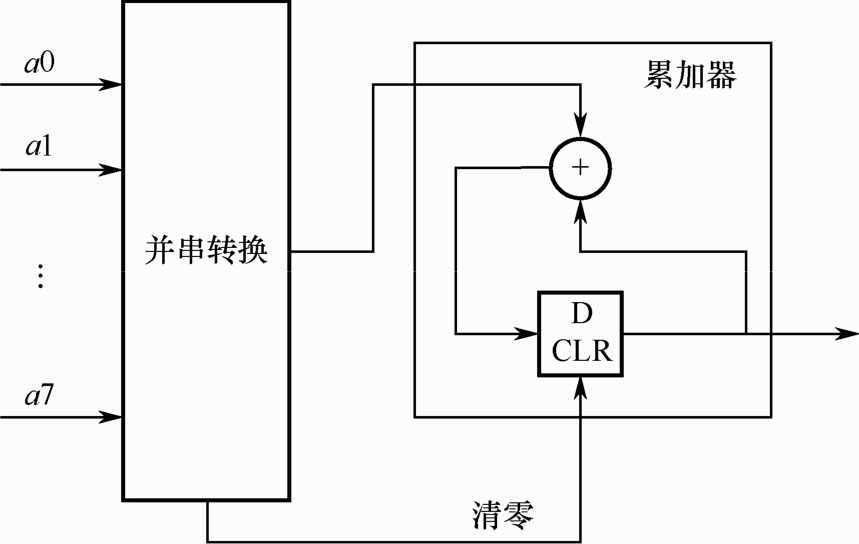

图1.30 个数相加的并行结构

不妨假设并不需要在一个时钟节拍里面完成上面的全部运算,那么可以通过时分复用的方法来减少结构的面积。这个复用的极致就是累加器,结构如图 1.31所示。其中,并串转换单元控制数据按照时钟节拍进入累加器,累加器完成运算。这样,仅仅采用了上面并行结构中的一个加法器,就完成了系统需要的功能。

比较并行结构和时分复用,时分复用的建立时间会增加,但是面积却急剧减少。“有得必有失”的天理循环,谁也跑不掉。

对于更多的加数,只要处理时间满足要求,这个结构还是可以采用的。至于时间不足的情况,可以用拆开系统的方法完成设计。例如 64个加数,用两组累加器计算,每个累加器计算 32个数字。最后再把两组累加器的结果相加,就得到了最终的结果。这个相对复杂,不详细论述。

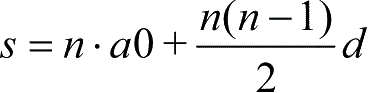

最后,利用已知的信息,可以极大地节约面积。这个话题大部分属于算法简化的范畴,这里稍稍提一句,还是拿上面的累加的例子说事吧。假如,有先验信息这些数据是等差数列,那么大伙儿就不必像图 1.30和图 1.31里面那样麻烦了。直接用等差数列的求和公式:

。对于我们的问题,

n

=8,

s

=8·

a

0+28·

d

,再利用移位简化:

s

=(

a

0 ≪ 3)+(

d

≪ 5)-(

d

≪ 2),如图 1.32所示。

。对于我们的问题,

n

=8,

s

=8·

a

0+28·

d

,再利用移位简化:

s

=(

a

0 ≪ 3)+(

d

≪ 5)-(

d

≪ 2),如图 1.32所示。

图1.31 个数相加的累加器实现

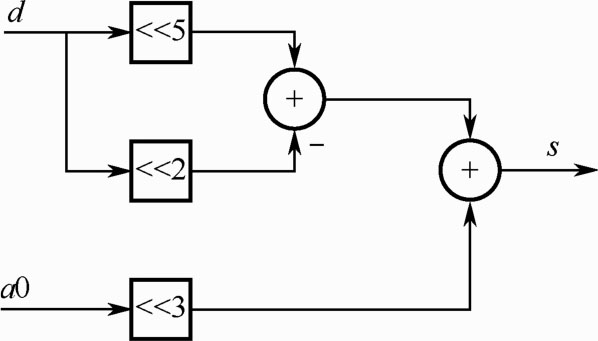

图1.32 等差数列求和结构

比较本部分的算法和前面的结构,在具有等比数列的假设的前提下,用两个加法就可以在一个时钟周期里面获得结果了。显然,存在先验假设的前提下,如果可以加以利用,获得效果是极好的。

再啰嗦几句,这些先验信息谁最清楚呢?对了,是算法工程师,所以平时没事和算法的朋友们搞好关系是很重要的。还有就是,见了文件别先急着设计。多看看,多想想,追着算法工程师多问问,这可能是事半功倍的。这是贫僧的生存秘籍,这里免费奉送了,低调低调。

总而言之(这个英文叫 All in all),我们的设计是三个方面在拔河。这三个方面是:系统需求、面积和速度。三个力量最终的中心点,就是一个最好的设计了。可惜啊,这种“中庸”的结果是很难得到的。

下面的听众朋友们别再打鼾了,读完这首总结的打油诗,本讲这就结束了。估计大家都在等我的打油诗,看完好去洗澡睡觉。

这正是:“孟轲长叹做菜难,徐导妙手寻熊宴;面积速度相较量,中庸之道保平安。代价频率互相转,流水复用模式搬;若有先验信息在,两者得全亦可然。”