在大规模可编程逻辑器件出现前,数字系统设计的最后一个步骤通常是将器件焊接在PCB上。如果设计存在问题并得到解决后,设计者需要重新设计PCB,设计周期被无谓地延长了,设计效率也很低。CPLD/FPGA的出现改变了这一状态。现在,人们在进行逻辑设计时,可以一次又一次随心所欲地改变整个电路的硬件逻辑关系,而不必改变PCB的结构。这一切都是因为CPLD/FPGA具有在系统下载或重新配置的功能。

目前,常见的大规模可编程逻辑器件的编程和配置工艺如下所述。

基于EEPROM或Flash技术的电可擦编程工艺。这种工艺的优点是掉电后编程信息不会丢失,但编程次数有限,编程速度不快。

基于SRAM查找表的编程工艺。在这种编程工艺中,编程信息是保持在SRAM中的,SRAM在掉电后编程信息会立即丢失,在下次上电后,需要重新载入编程信息。通常将编程数据下载到可编程逻辑芯片的过程,对于CPLD来讲称之为编程,而对于FPGA来讲称之为配置(Configure)。

相比之下,电可擦除编程工艺的优点是编程后信息不会因掉电而丢失,但编程次数有限,编程的速度不快。对于SRAM型FPGA而言,理论上其配置次数是无限的,在加电时可随时更改逻辑,但掉电后芯片中的信息即丢失,每次上电时必须重新载入信息,下载信息的保密性也不如前者。

目前可用的下载接口分为专用接口和通用接口两种,其中专用接口包括Lattice早期的ISP接口(ispLSI1000系列)、Altera的PS接口等;通用接口有JTAG接口。

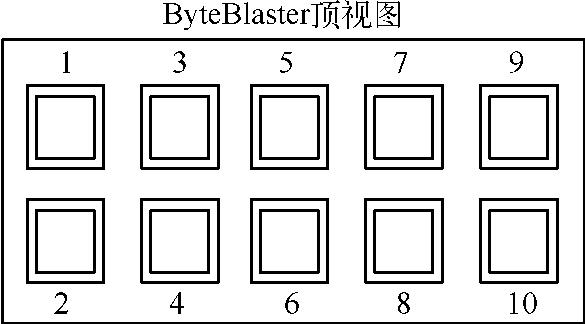

Altera的ByteBlaster接口是一个10芯的混合接口,有PS和JTAG两种模式,都属于串行接口,其引脚排列图如图1-18所示,名称表见表1-2。

图1-18 ByteBlaster信号接口引脚排列图

表1-2 ByteBlaster接口信号名称表

PLD芯片,尤其是FPGA芯片,其下载模式有多种,分别对应于不同格式的数据文件。不同的配置模式又要有不同的接口,如Xilinx公司的FPGA器件有8种配置模式,Altera的FPGA器件有6种配置模式。配置模式的选择是通过FPGA器件上模式选择引脚来实现的,Xilinx公司的FPGA器件有M0、M1、M2三个配置引脚,Altera和FPGA器件有MSEL0、MSEL1两个配置引脚。但各系列也有差别,设计时需参考相应的数据手册。

对于基于SRAM查找表LUT结构的FPGA器件,由于是易失性器件,没有ISP的概念,代之以ICR(In-Circuit Reconfigurability),即在线可重配置方式。FPGA的特殊结构使之在上电后必须进行一次配置。电路可重配置是指在器件已经配置好的情况下进行重新配置,以改变电路逻辑结构和功能。在利用FPGA进行设计时,可以利用FPGA的ICR特性,通过连接PC的下载电缆,快速地下载设计文件至FPGA进行硬件验证。

Altera的SRAM LUT结构的器件中,FPGA可使用6种配置模式,这些模式通过FPGA上的两个模式选择引脚MSEL1和MSEL0上设定的电平来决定。

配置器件,如用EPC器件进行配置。

PS(Passive Serial,被动串行)模式: MSEL1= 0、MSEL0=0。

PPS(Passive Parallel Synchronous,被动并行同步)模式: MSEL1= 1、MSEL0= 0。

PPA(Passive Parallel Asynchronous,被动并行异步)模式: MSEL1=1、MSEL0=1。

PSA(Passive Serial Asynchronous,被动串行异步)模式: MSEL1= 1、MSEL0= 0。

JTAG模式: MSEL1= 0、MSEL0=0。

JTAG实际上是一种国际标准测试协议(IEEE1149.1兼容),主要用于芯片内部测试,以及对系统进行仿真、调试。现在,多数的高级器件都支持JTAG协议。

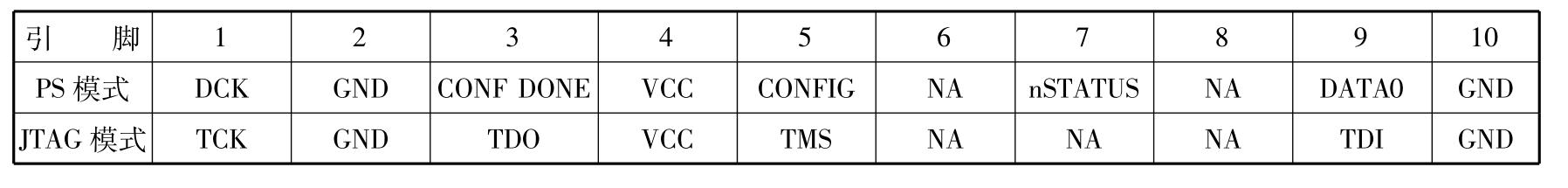

进行电路调试时,可以使用PS配置模式或JTAG模式进行。PS模式是利用PC通过ByteBlaster下载电缆对Altera器件应用ICR。JTAG模式是通过PC的打印机接口使用ByteBlasterⅡ,或者使用PC的USB接口使用ByteBlaster进行FPGA配置,如图1-19所示。使用JTAG配置时,需注意MSEL上电平的选择,要都设置为0,才能用JTAG进行配置。

图1-19 单片FPGA芯片的JTAG配置电路

当设计的数字系统比较大,需要不止一个FPGA器件时,若为每个FPGA器件都设置一个下载口显然是不经济的。Altrera器件的PS模式支持多个器件进行配置。对于PC而言,只是在软件上加以设置支持多器件外,再通过一条ByteBlaster下载电缆即可对多个FPGA器件进行配置。图1-20所示的是PC用ByteBlaster下载电缆对多个FPGA器件进行JTAG配置的原理图。

利用PC对FPGA进行ICR在系统重配置,虽然在调试时非常方便,但当数字系统设计完毕需要正式投入使用时,在应用现场(如车间)不可能在FPGA每次加电后,用一台PC手动地去进行配置。上电后,自动加载配置对于FPGA应用来说是必须的,FPGA上电自动配置有许多种解决方法,如EPROM配置、用专用配置器件配置、单片机控制配置或FlashROM配置等。这里首先介绍专用配置器件配置。

图1-20 对多个FPGA器件进行JTAG配置的原理图

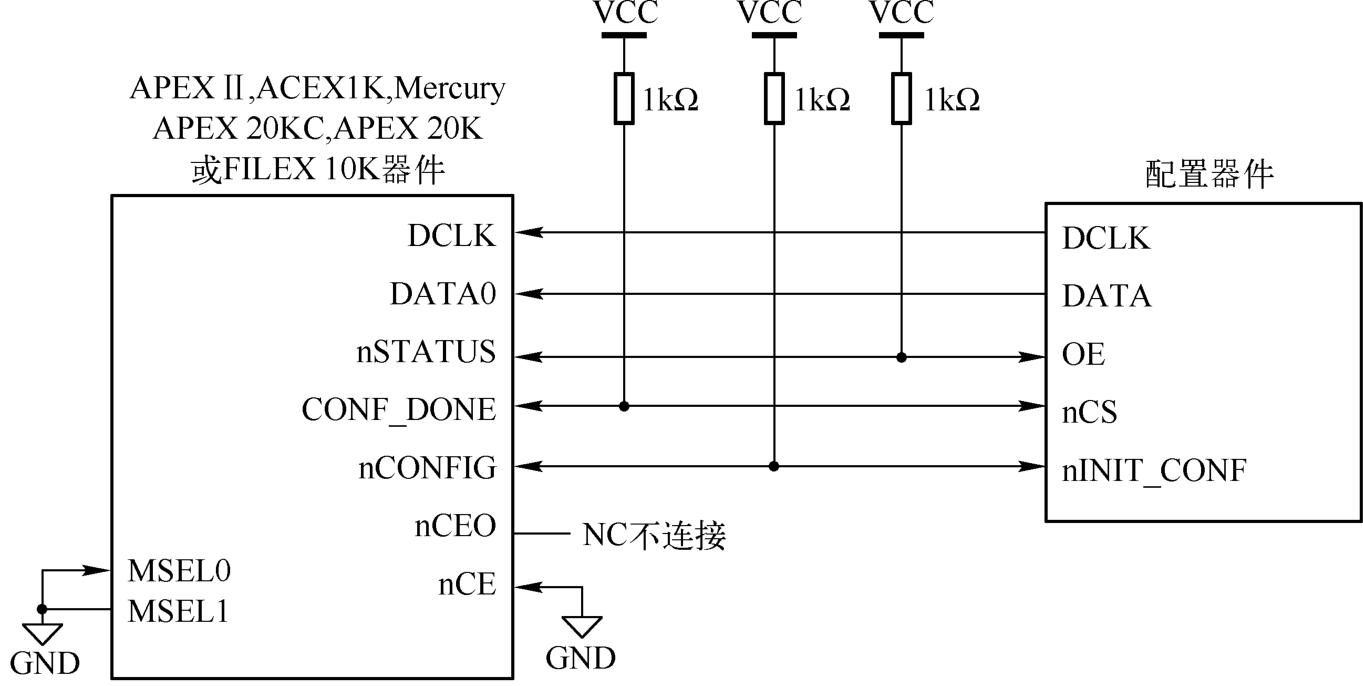

专用配置器件通常是串行的PROM器件。大容量的PROM器件也提供并行接口,按可编程次数分为两类,一类是OTP(一次可编程)器件;另一类是多次可编程的。例如,Alter FPGA常用配置器件EPC1441和EPC1是OTP型串行PROM; EPC2是EEPROM型多次可编程串行PROM。图1-21所示的是采用单个EPC2配置器件配置单个FPGA的配置电路原理图。

图1-21 采用EPC2配置器件配置单个FPGA的配置电路原理图

对于配置器件,Altera的FPGA允许多个配置器件配置单个FPGA器件,也允许多个配置器件配置多个FPGA器件,甚至同时配置不同系列的FPGA。

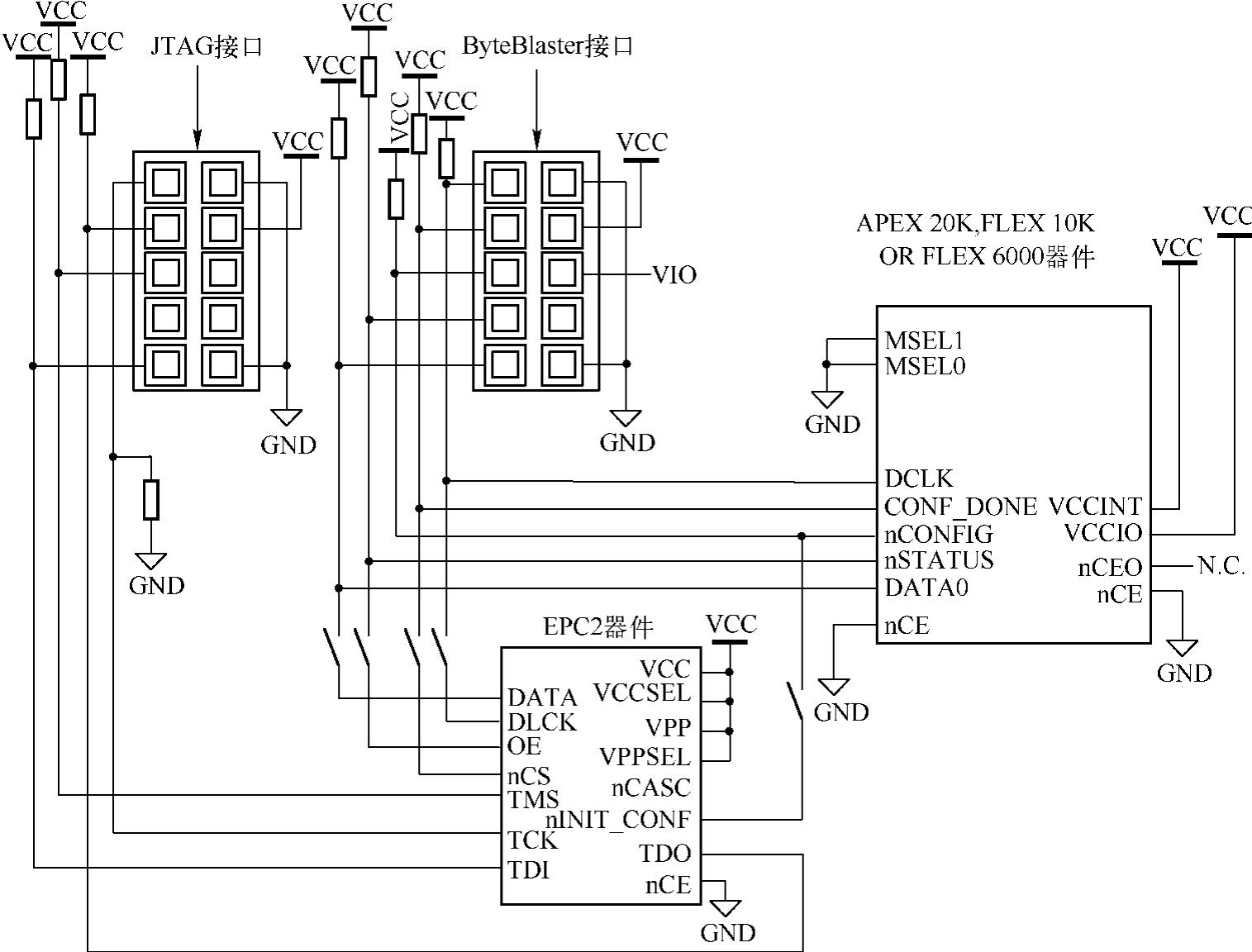

在实际应用中,常常希望能随时更新其中的内容,但又不希望把配置器件从PCB上取下来编程。Altera的可重复编程配置器件(如EPSC4、EPC2)就提供了在系统编程的能力。图1-22所示的是EPC2的编程和配置电路。图中,EPC2本身的编程由JTAG接口来完成,FPGA的配置既可由ByteBlaster(MV)进行,也可由EPC2进行,这时ByteBlaster端口的任务是对EPC2进行ISP方式下载。

EPC2器件允许通过额外的nINIT_CONF引脚对APEX器件配置进行初始化。此引脚可以和要配置器件的nCONFIG引脚相连。JTAG指令使EPC2器件将nINIT_CONF置低电平,接着将nCONFIG置低电平,然后EPC2将nINIT_CONF置高电平并开始配置。当JTAG状态机退出这个状态时,nINIT_CONF释放nCONFIG引脚的控制,配置过程开始初始化。

图1-22 EPC2的编程配置FPGA电路原理图

APEX20、FLEX10K器件可以由EPC2、EPC1和EPC1441配置。FLEX 6000器件可以由EPC1或EPC1441配置。EPC2、EPC1和EPC1441器件将配置数据存放于EPROM中,并按照内部晶振产生的时钟频率将数据输出,OE、nCS和DCLK引脚提供了地址计数器和三态缓存的控制信号。配置器件将配置数据按串行的比特流由DATA引脚输出。一个EPC1441器件可以配置EPF10K10或EPF10K20器件。

当配置数据大于单个EPC2或EPC1器件的容量时,可以级联使用多个此类器件(EPC1441不支持级联)。在这种情况下,由nCASC和nCS引脚提供各个器件之间的握手信号。

当使用级联的EPC2和EPC1器件来配置APEX和FLEX器件时,级联链中配置器件的位置决定了它的操作。当配置器件链中的第一个器件或主器件加电或复位时,nCS置低电平,主器件控制配置过程。在配置期间,主器件为所有的APEX和FLEX器件,以及后序的配置器件提供时钟脉冲。在多器件配置过程中,主配置器件也提供了第一个数据流。在主配置器件配置完毕后,它将nCASC置低电平,同时将第一个从配置器件的nCS引脚置低电平。这样就选中了该器件,并开始向其发送配置数据。多个配置器件同样可以为多个器件进行配置。

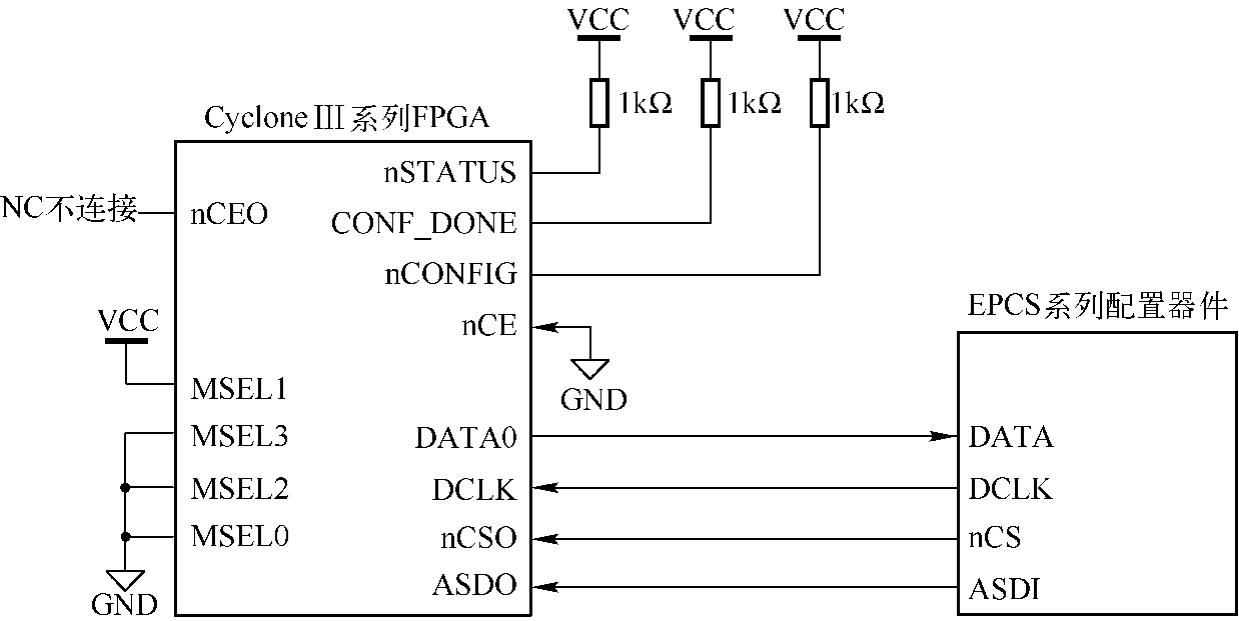

对于CycloneⅡ/Ⅲ/Ⅳ/系列FPGA,也可以使用FPCS系列配置器件进行配置。EPCS系列配置器件需要使用AS模式或JTAG间接编程模式来配置。图1-23所示的是EPCS系列器件与Cyclone FPGA构成的配置电路原理图。

图1-23 EPCS器件配置FPGA的电路原理图

在FPGA实际应用中,设计的保密和可升级是十分重要的。用单片机来配置FPGA可以较好地解决这两个问题。

对于单片机配置FPGA器件,Altera的基于SRAM LUT的FPGA提供了多种配置模式,除以上多次提及的PS模式可以用单片机配置外,PPS模式、PSA模式、PPA模式和JTAG模式都能适用于单片机配置。

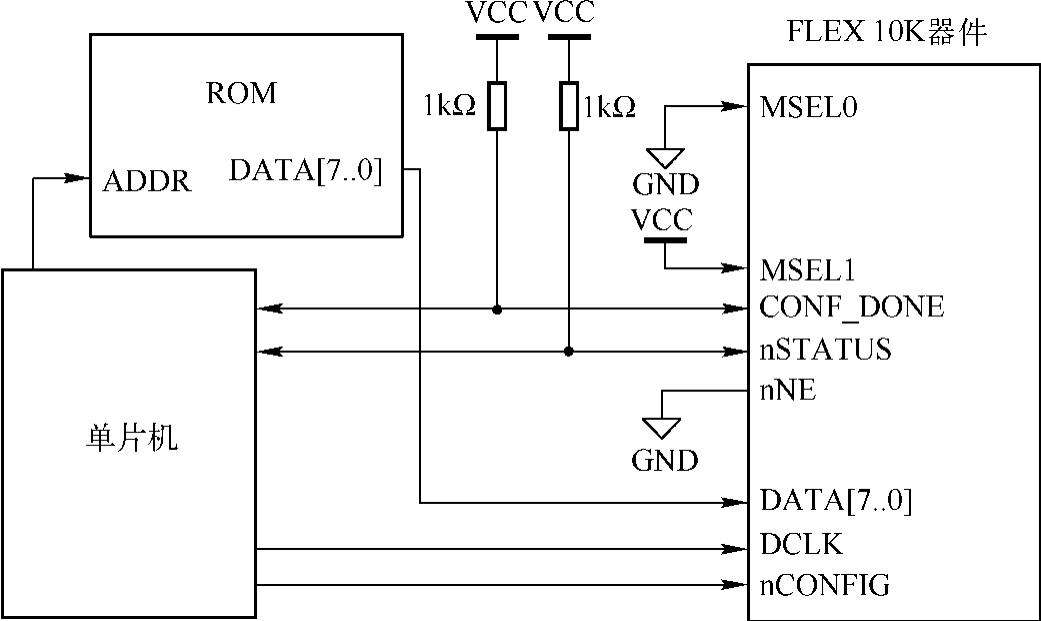

用单片机配置FPGA器件,关键在于产生合适的时序。由于篇幅限制,这里仅对两种模式进行介绍。图1-24所示的是单片机用PPS模式配置FPGA器件的电路。图中,单片机可以选用常见的单片机,如MCS-51系列、MCS-96系列、AVR系列等; ROM可以用EPROM或Flash ROM,配置的数据就存储在其中。单片机在这里只起产生配置时序的作用。

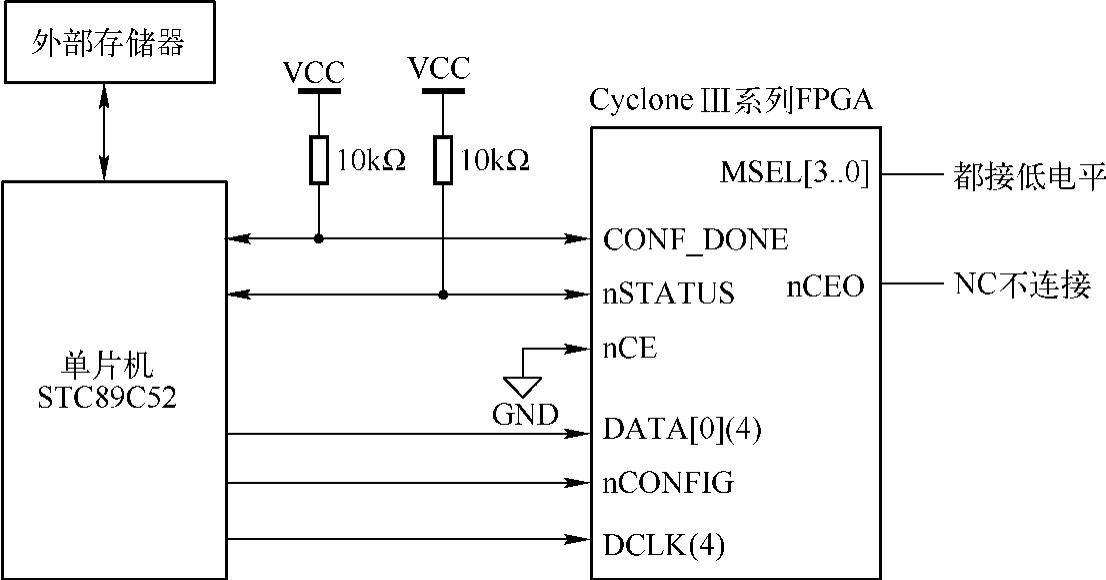

有时出于设计保密、减少芯片的使用数等考虑,对于配置器件容量不大的情况下,把配置数据也置于单片机的程序存储区中。图1-25所示的就是一个典型的应用示例。图中,单片机采用常见的STC89C52,FLEX10K的配置模式选为PS模式。由于STC89C52的程序存储器是内建于芯片的FlashROM,设计的保密性较好,还有很大的扩展余地。如果把图中的“其他功能模块”换成无线接收模块,还可以实现系统的无线升级。

利用单片机或CPLD对FPGA进行配置,除了可以取代昂贵的专用OTP配置ROM外,还有许多其他实际应用,如可对多家厂商的单片机进行仿真器设计、多功能虚拟仪器设计、多任务通信设备设计或EDA实验系统设计。其方法是,在图1-24中所示的ROM内按不同地址放置多个针对不同功能要求设计好的FPGA的配置文件,然后由单片机接收不同的命令,以选择不同的地址进行控制,从而使所需要的配置下载于FPGA中,这就是“多任务电路结构重配置”技术。这种设计方式可以极大地提高电路系统的硬件功能灵活性。因为从表面上看,同一电路系统没有发生任何外在结构上的改变,但通过来自外部不同的命令信号,系统内部将对应的配置信息加载于系统的FPGA中,电路系统的结构和功能将在瞬间发生巨大的改变,从而使单一电路系统具备许多不同电路结构的功能。

图1-24 单片机用PPS模式配置FPGA器件的电路

图1-25 使用STC89C52单片机进行配置

使用单片机进行配置时,也有一定的缺点:①速度慢,不适用于大规模FPGA和高可靠的应用;②容量小,单片机引脚少,不适用接大的ROM以存储较大的配置文件;③体积大,成本和功耗都不利于相关的设计。

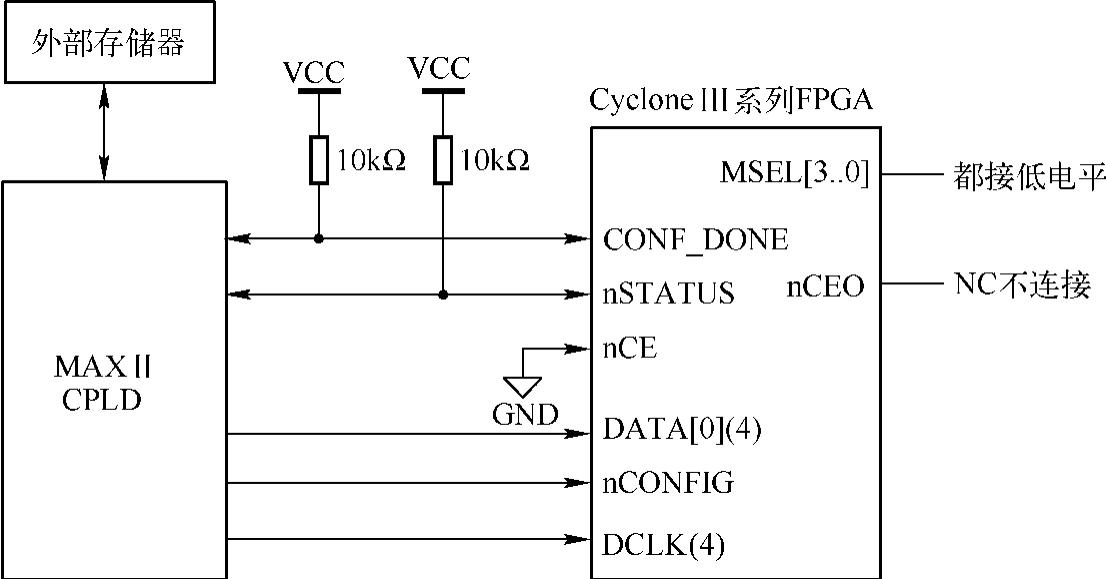

所以,如果将CPLD直接取代单片机将是一个较好的选择,原来单片机中的配置控制程序可以用状态机来取代,其电路如图1-26所示。

图1-26 用MAXⅡCPLD进行配置FPGA电路