作为IEEE标准硬件描述语言,利用VHDL进行系统行为级设计已成为FPGA和ASIC的设计主流。使用VHDL,不仅可以快速地描述和综合FPGA设计,还具有许多强大的性能特点。

FPGA数字系统可以使用不同复杂度(如系统级、电路板级、芯片级和门级)的电路网络在同一抽象程度上进行描述,有系统行为级、寄存器传输级(Register Transfer Level,RTL)和门电路级3种不同层次。

传统的PLD设计方式是设计者在CAD工作站上以基本的电路组件来组织,并构成一个完整的逻辑功能。这些最基本的电路组件如AND(逻辑“与门”)、OR(逻辑“或门”)或缓冲器在CAD工作站的屏幕中以线条和图案来表示,每个电路组件都必须清楚定义I/O信号和功能。在硬件描述语言中,这些所谓的电路符号(Symbol)并不存在,而是以Entity(俗称实体)的描述来进行定义。

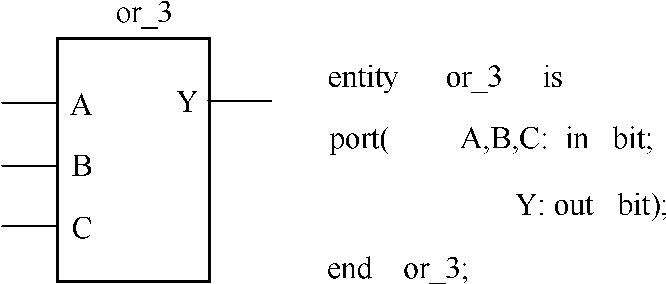

图2-1 3输入或门的电路符号和实体描述

图2-1所示为一个3输入或门的电路符号和它所对应的实体描述。实体是构成所有设计的基础,设计者以实体中的描述来定义一个设计中的所有I/O信号。在一个层次式设计(Hierarchical Design)中,TOP-Level设计整体是一个实体,而由此往下的每个层次线路的描述,均包含在各个不同的LOWERLevel的实体中。

在图2-1中,定义了3个输入A、B和C,并且这3个输入的取值对象只能是逻辑“0”(对应低电平)和“1”(对应高电平)这两种状态(bit是定义“0”和“1”两种取值的数据类型定义);定义了1个输出Y,Y同样只有“0”和“1”两种状态。

在实体这个阶段中,并未定义内部线路的功能。那么,如何来描述一个实体所含的功能呢?

在一个传统的层次式设计中,任一层次的Symbol,其功能是以深藏在它下面的实际线路(Schematic)来表示的,而完成此任务的是结构体(Architecture)。

在结构体中,有各式各样的语句(Statement),这些语句涵盖底层的门级(Gate-Level)、次低层的RTL级和顶层的行为级(Behavior-Level)描述,可以很完整地表现一个设计的所有功能。

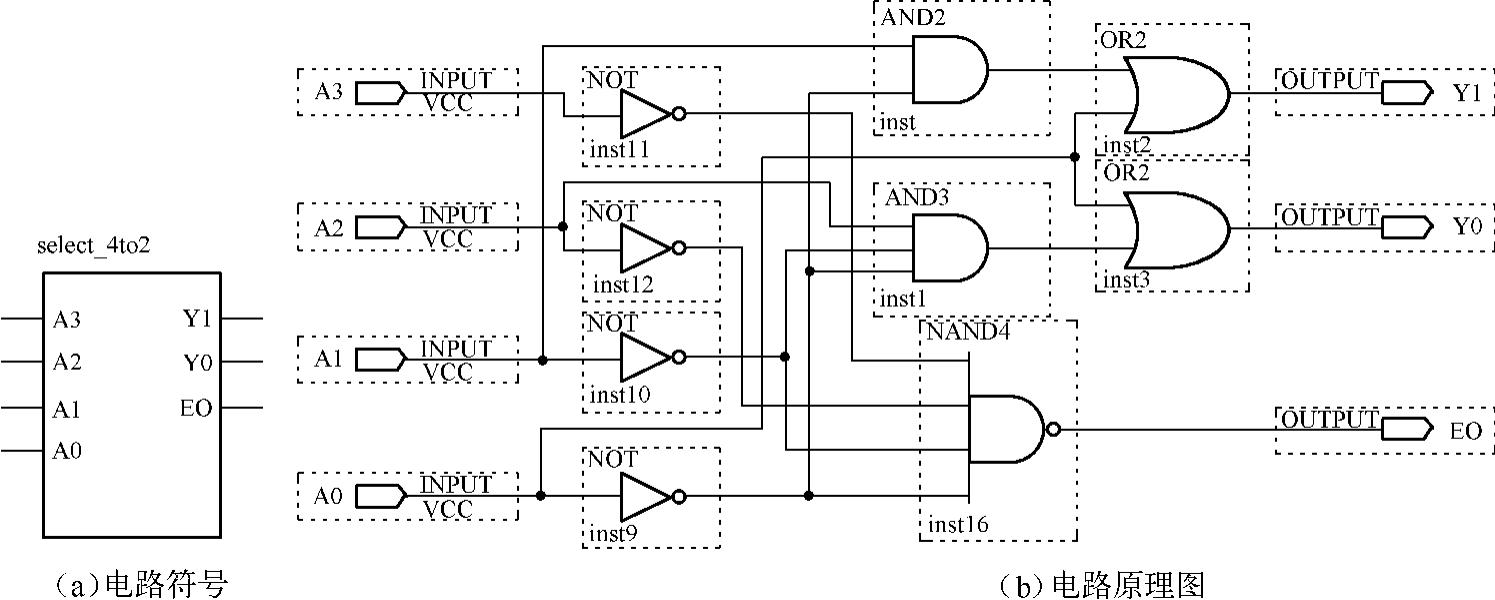

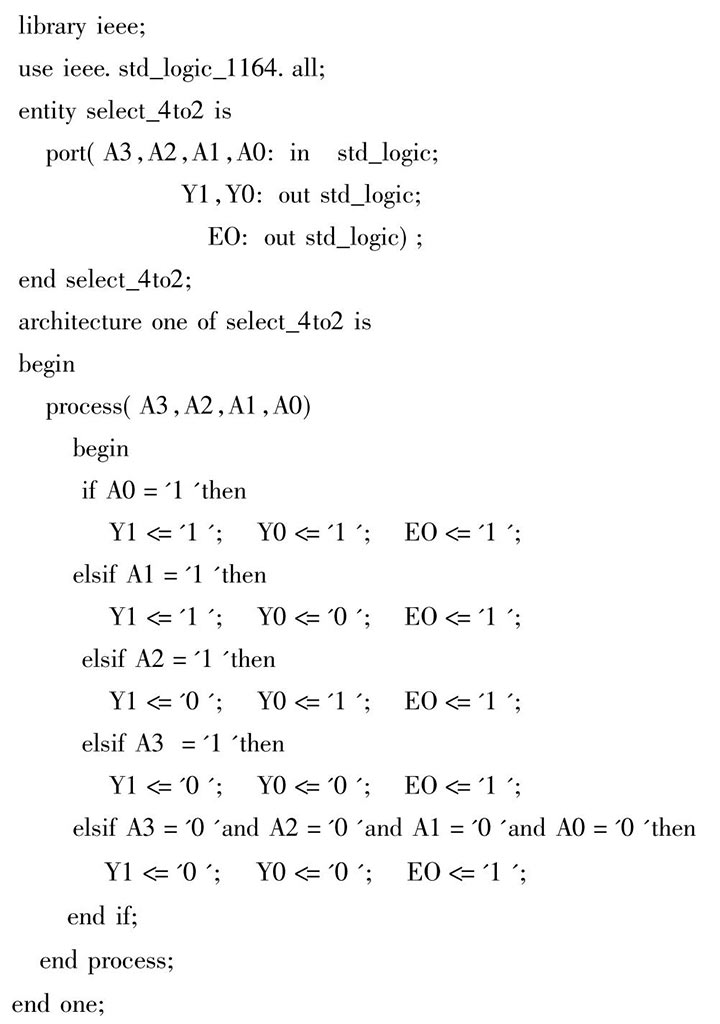

图2-2所示为4线-2线优先编码器的电路符号及电路原理图,从图中可以看出,它有4个输入端和3个输出端。

图2-2 4线-2线优先编码器的电路符号及电路原理图

4线-2线的VHDL如下所示,在该程序中,结构体使用了条件分支,根据A3~A0 这4个输入值的不同,使得Y0、Y1和EO输出相应的状态值。

基本上,在同一时间只有一个程序代码被执行。但在实际的FPGA硬件中,许多彼此不相关的信号变化或运算都可以并行进行,为了能充分表现硬件线路的所有特性,允许顺序(Sequential)和并行(Concurrent)两种不同的描述存在。描述硬件线路的方法不是唯一的,同样的线路往往有多种不同的表示方法,如何选择最有效的描述,这些均由设计者自行确定。

总的来说,基于EDA技术的FPGA设计是采用自顶向下(Top-Down)、由粗到细、逐步求精的设计方法。自顶向下是指将数字系统的整体逐步分解为各个子系统和模块,若子系统规模较大,则还需将子系统进一步分解为更小的子系统和模块,层层分解,直至整个系统中各子系统关系合理,并便于逻辑电路级的设计和实现为止。

采用自顶向下的设计方法时,高层设计用于功能和接口描述,说明模块的功能和接口,更详细的模块功能描述在下一设计层次说明,最底层的设计才涉及具体的寄存器和逻辑门电路等实现方式的描述。

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种标准的硬件描述语言,其中文含义为超高速集成电路硬件描述语言。

作为IEEE标准硬件描述语言,利用VHDL进行系统行为级设计已成为FPGA和ASIC的设计主流。在电子产业界,无论是ASIC设计人员,还是系统级设计人员,大都会通过学习VHDL来提高工作效率。由于VHDL所具有的通常性,它已成为可支持不同层次设计者所需求的标准语言。VHDL不仅可以快速地描述和综合FPGA设计,还具有如下一些特性。

【功能强大,灵活性强】VHDL具有功能强大的语言结构,可用简洁、明确的VHDL语言程序代码描述来进行复杂控制逻辑的设计。为了有效控制设计的实现,它还具有多层次的设计描述功能。此外,VHDL语言能够同时支持同步电路、异步电路和随机电路的设计实现,这是其他硬件描述语言无法比拟的。VHDL语言设计方法灵活多样,既支持自顶向下的设计方式,也支持自底向上的设计方法;既支持模块化设计方法,也支持层次化设计方法。

【具有强大的硬件描述能力】VHDL语言具有多层次的电路设计描述功能,既可描述系统级电路,也可以描述门级电路;描述方式既可以采用行为描述、寄存器传输描述或结构描述,也可以采用三者的混合描述方式。同时,VHDL语言也支持惯性延迟和传输延迟,这样可以准确地建立硬件电路的模型。VHDL语言的强大描述能力还体现在它具有丰富的数据类型。VHDL语言既支持标准定义的数据类型,也支持用户定义的数据类型,这样便会给硬件描述带来较大的自由度。

【不依赖于器件设计】VHDL允许设计人员生成一个设计,而并不需要首先选择一个用来实现设计的器件。对于同一个设计描述,可以采用多种不同的器件结构来实现其功能。若需对设计进行资源利用和性能方面的优化,也并不一定要求设计者非常熟悉该器件的结构。因此,设计者可以集中精力从事其本人的设计构思,当然,这并不是说设计者可以忽略电路结构。

【可移植性好】VHDL的可移植能力(Portability)允许设计者对需要综合的设计描述进行模拟。在综合前对一个数千门的设计描述进行模拟,这样可以节约设计时间。在对设计进行模拟时,若发现设计上的瑕疵,就能够在设计实现前给予纠正。因为VHDL是一个标准语言,故VHDL的设计描述可以被不同的工具所支持,可以从一个模拟工具移植到另一个模拟工具,从一个综合工具移植到另一个综合工具,从一个工作平台移植到另一个工作平台去执行。这意味着同一个VHDL设计描述可以在不同的设计项目中被采用。在某个EDA工具中构成的技术诀窍,在其他工具中同样可以被采用。

【具有性能评估能力】不依赖器件的设计(Device-Independent Design)和可移植能力允许设计者采用不同的器件结构和不同的综合工具来评估设计。在设计人员开始设计前,无须了解将采用何种器件。设计者可以进行一个完整的设计描述,并且对其进行综合,生成选定的器件结构的逻辑功能,然后评估结果,选用最适合设计人员设计需求的器件。为了衡量综合的质量,同样可利用不同的综合工具所得到的综合结果来进行分析、评估。

【易于共享和复用】VHDL语言采用基于库(Library)的设计方法。在设计过程中,设计人员可以建立各种可再次利用的模块,一个大规模的硬件电路的设计不可能从门级电路开始逐步地进行设计,而是一些模块的累加。这些模块可以预先设计,或者使用以前设计中存档的模块,将这些模块存放在库中,就可以在以后的设计中复用。

【上市时间快、成本低】VHDL语言的设计将大大提高数字单片化设计的实现速度。VHDL语言使设计描述快捷、方便,促进设计的快速复制,简便易行。同时,多种综合工具支持这种形式的设计。作为一类强有力的现场集成设计方式,VHDL和可编程逻辑的组合将为设计者的产品上市带来创纪录的速度。