在VHDL语言中,包含了一系列的在系统描述时用来代表和存储数据的语言元素,我们称之为对象。常用基本数据对象包括信号(Signals)、常量(Constants)和变量(Variables)。每个对象在使用前,必须预先声明,并且指明对象所属的数据类型。每种类型的数据对象具有相应的值域和操作范围,因此,针对对象的操作必须严格限制在该类型的规定值域和操作范围内。

VHDL描述中,根据描述对象的不同,选择不同的数据对象与之对应,进行数据传递或存储。下面介绍信号、常量和变量声明的语法格式。

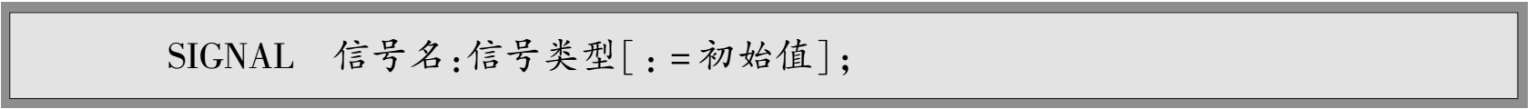

信号是VHDL语言中最常用到的对象。它描述了并行元素(如元件、进程等)间的连接关系,是对电子电路内部硬件连接的抽象。信号声明的语法格式如下:

SIGNAL为信号声明的关键字,一次可以声明一个或多个信号;信号名为设计者指定的合法标识符(见2.6.2节说明);信号类型为信号所采用的数据类型;方括号“[]”内为可选内容,用于为信号赋初始值,该值只在行为仿真时调用,在综合时被忽略。

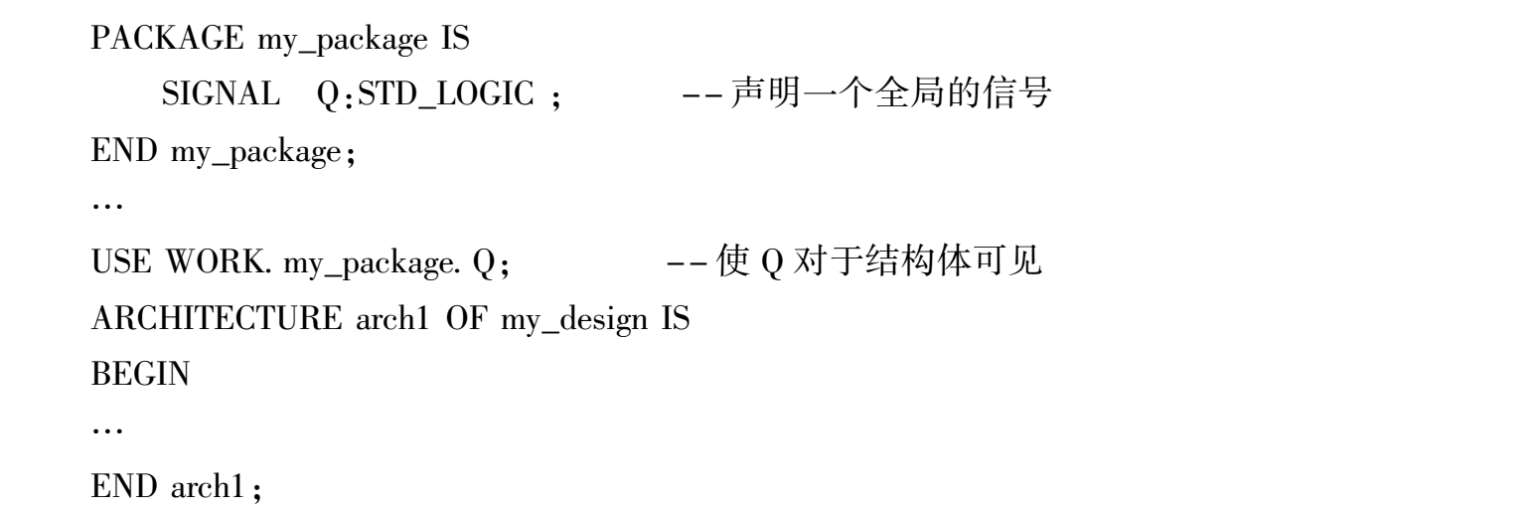

信号声明可以出现在实体声明部分、结构体声明部分和程序包声明部分。信号的作用范围遵循可视性原则,即在结构体内声明的信号,在该结构体内任何部分都是可见的,可以被引用,但在该结构体外就不能使用;在实体内声明的信号,可以被该实体对应的任何结构体使用;若要使一个信号在多个设计实体内可用,则必须将其信号声明语句放在实体外部的程序包声明处,也称全局信号(Global Signal)。如下面例程所示:

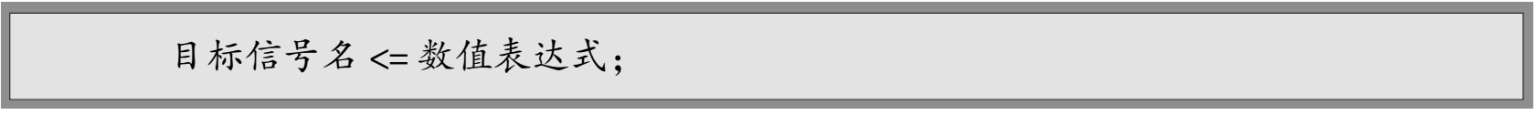

信号的赋值符号是“<=”,在结构体描述中对信号赋值的语句如下:

例如:

Q<='1';

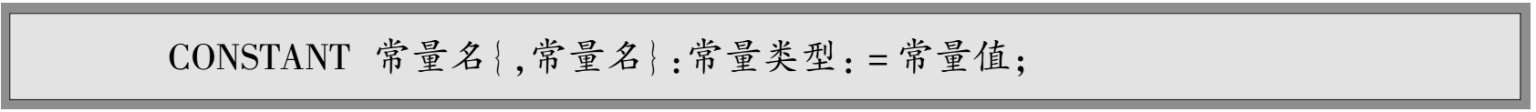

常量是指对一个对象赋予固定值,该值在此后综合仿真过程中不再改变。常量的使用增强了设计描述的可读性,且使设计模块更容易更新。例如,将位矢量的宽度定义为一个常量,只要修改这个常量就能改变宽度,从而改变逻辑部件的结构。常量声明的语法格式如下:

CONSTANT为常量声明的关键字,可以一次声明一个或多个常量;常量名由设计者指定;“{}”内是可重复或可选项;常量类型即常量所使用的数据类型;“:=”为常量赋值符号,用于为常量赋值。

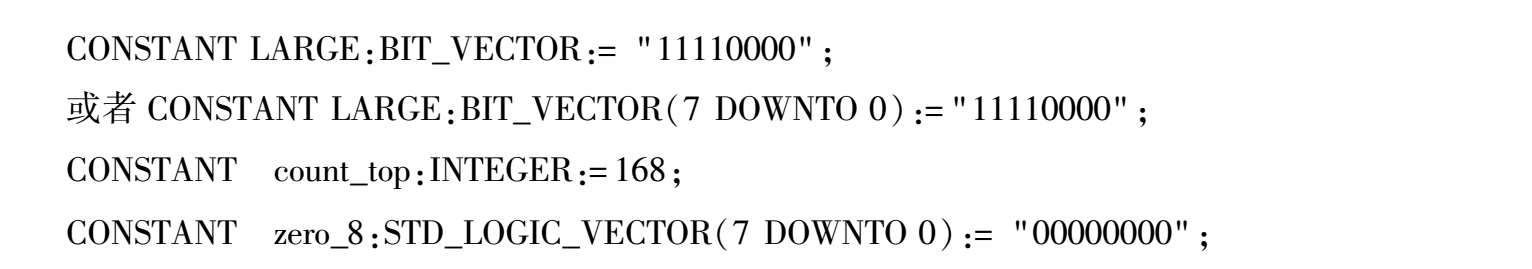

例如:

常量声明可以出现在任何声明区域内,如实体声明、结构体声明、程序包声明、进程、块和子程序的声明区域等。如果要使一个常量成为全局常量,在整个设计实体内可见,就需要将常量声明放在外部程序包声明处。常量的使用范围取决于它被定义的位置。在程序包中定义的常量具有最大的全局化特征,可以用在调用此程序包的所有设计实体中;定义在实体中的常量,可使用在这个实体对应的所有结构体中;定义在设计实体内部某一结构体中的常量,只能用于此结构体;定义在结构体某一单元内的常量,如进程内,则只能用于本进程中。

常量的作用是使程序易于阅读和修改。例如,在一个数据线宽度为8位的逻辑部件中用一个数值为8的常量bus_width来声明端口和信号的宽度限定,则在以后的移植或更改时,只需对bus_width常量定义的数值8进行更改,而对涉及的端口和信号则不需任何改动。

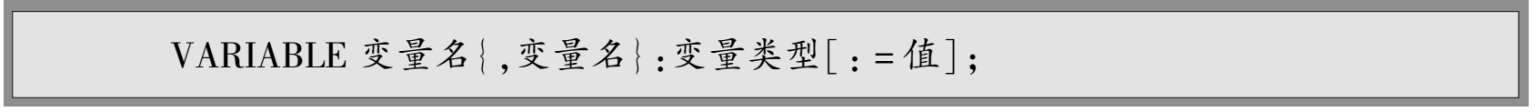

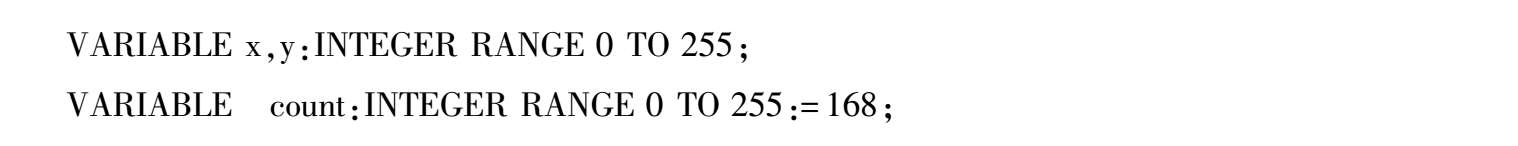

变量用来在顺序执行的VHDL语句间传递中间值。变量只能出现在进程(Processes)语句、过程(Procedures)语句和函数(Functions)语句中。变量只能是局部的,在该函数(或进程、过程)范围内有效。仿真过程中,对变量的赋值可以立即生效,这点与信号不同。变量声明的语法格式如下:

VARIABLE为变量声明的关键字,可以一次声明一个或多个变量;变量名由设计者指定;“{}”内是可重复或可选项;变量类型即变量所使用的数据类型;“[]”内为可选内容,用于为变量赋初值。

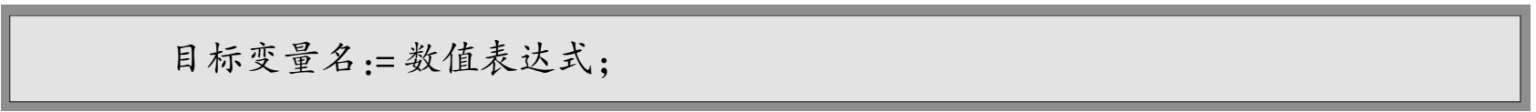

在程序中,变量赋值的语法格式如下:

例如:

变量初值只在行为仿真中有效,综合适配时将略去所有的初始值。

变量作为局部量,其使用范围仅限于进程或子程序中。变量不能将它所承载的信息带出对它做出定义的当前设计单元。因此当不同进程间需要数据传递时,需要通过信号进行。

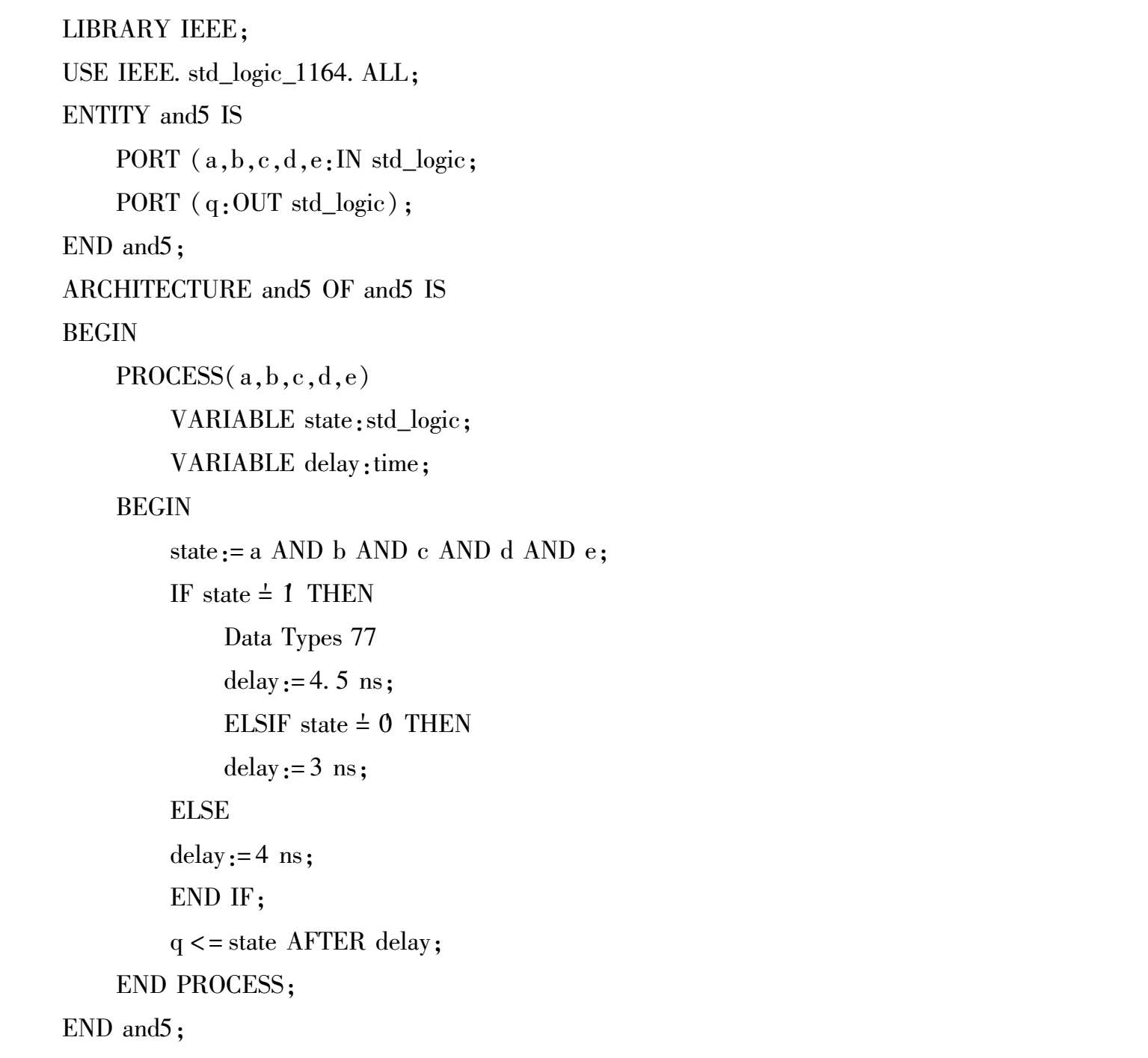

本例为5输入与门,在进程的声明部分,包含了两个变量声明:变量state和变量delay。变量state用来暂存输入量的与逻辑值,变量delay用来暂存在处理输出时用到的延时量,这两个变量都非静态值,因为它们的值取决于输入量a、b、c、d、e的值。信号也可以用于暂存数据,但基于以下原因,在这里不采用信号。

因为变量是立即赋值的,用在这里更加有效,而信号赋值需要条件启动。

变量更加节约存储单元,而信号需要更多存储单元。

在本例中,若要使用信号,还需要引入wait语句以保证信号赋值同步。

前述三种数据对象具有各自的适用范围和作用。这里做以简单对比分析。

☺ 从硬件电路系统来看,常量相当于电路中的恒定电平,如VCC或GND节点;而信号和变量则相当于组合电路中门与门见的连接线及连接线上的信号值。

☺ 从行为仿真和VHDL语句的功能上看,信号和变量的区别主要表现在接受和保持信息的方式、信息保持和传递区域大小上。例如,信号可以设置延时量,而变量不能;

变量只能作为局部信息的载体,而信号可以作为模块间的信息载体。通常,变量的设置只是一种过渡,最后的信息传输和模块间的通信都靠信号来完成。

从综合后的硬件电路来看,信号一般会对应更多的硬件结构。

许多情况下,信号和变量并没有什么区别。例如,满足一定条件的进程中,综合后它们都能引入寄存器。这时它们都具有能够接受赋值这一特性,而综合器并不理会它们在接受赋值时存在的延时特性。

虽然VHDL仿真器允许变量和信号赋初值,但在实际应用中,VHDL综合器并不会把这些信息综合进去。因为在CPLD/FPGA芯片上电后,并不能确保其初始状态的取向。因此,对于时序仿真来说,设置的初始值在综合时是没有作用的。