5.2 CORDIC循环和非循环结构硬件实现原理

5.2 CORDIC循环和非循环结构硬件实现原理

下面将介绍在Xilinx FPGA芯片上使用Xilinx的System Generator工具实现CORDIC算法的原理。理想的CORDIC结构取决于其在应用中的速度和面积均衡。在FPGA中实现CODIC的方法有:①循环结构;②非循环结构;③非循环流水线结构。

本节将介绍CORDIC循环结构的原理及实现方法。

1.循环结构的原理

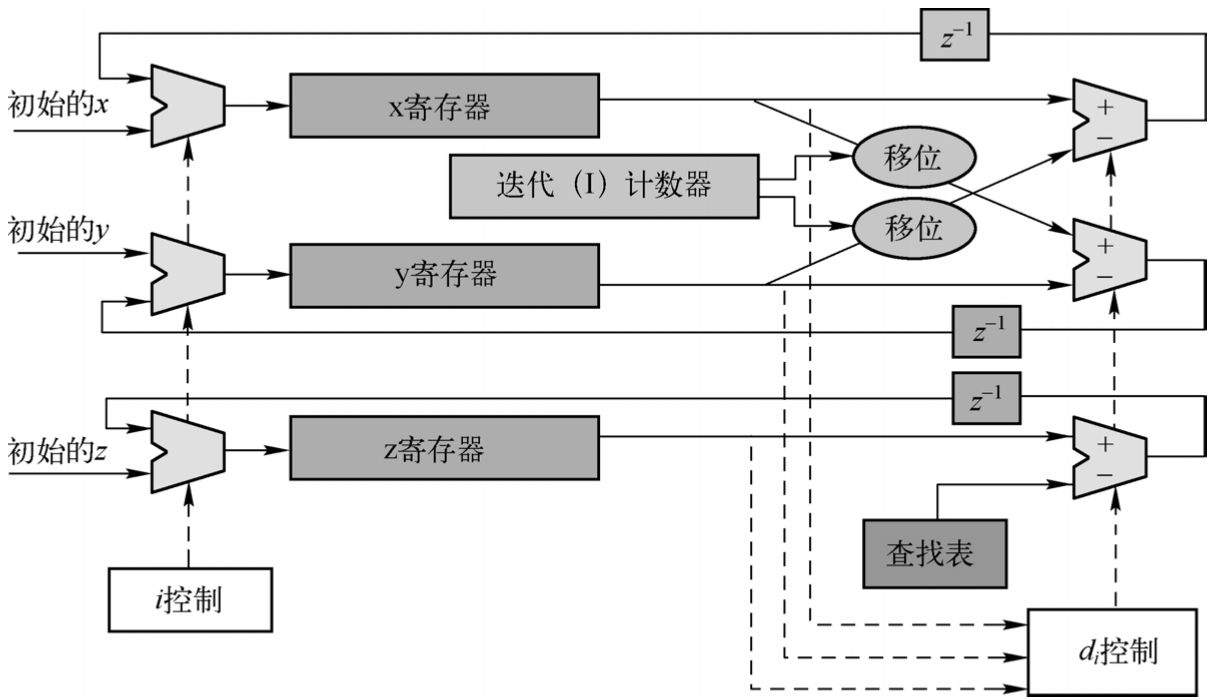

在循环的方式中,所有的迭代均在一个单元内完成,这种实现方式的结构如图5.9所示。

图5.9 循环方式实现的结构

这种结构带有反馈。在这个结构中,移位寄存器的实现是一个难点。在非循环方式的结构中使用的是固定结构的移位寄存器,能够使用布线资源来建立。而循环方式的结构要求一个可变位数的移位寄存器,每个单元乘以2 -i ,表示移位i个比特位。单个的单元必须能够提供所有的i值,可以使用桶型移位寄存器来实现这种可变移位寄存器。

2.移位寄存器的设计

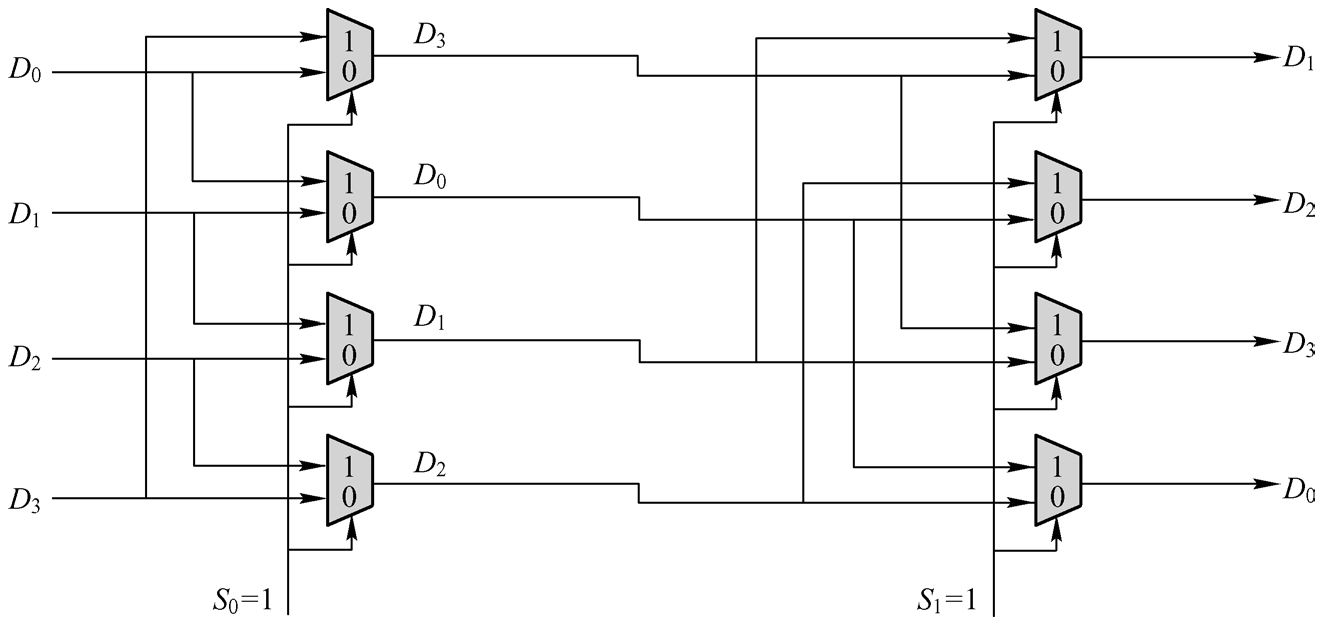

通过多路复用器,可以构成桶型移位寄存器。一个4位的桶型移位寄存器的结构如图5.10所示。

图5.10 4位的桶型移位寄存器的结构

(1)S 0 控制桶型移位寄存器的第一列:①当S 0 =0时,输入直接连接到输出;②当S 0 =1时,移动一位,输入D 0 D 1 D 2 D 3 ,输出D 3 D 0 D 1 D 2 。

(2)S 1 控制桶型移位寄存器的第二列:①当S 1 =0时,输入直接到输出;②当S 0 =1时,移动二位,输入D 3 D 0 D 1 D 2 ,输出D 1 D 2 D 3 D 0 。

这个结构非常灵活,可根据需要进行扩展。如果要求使用8位的桶型移位寄存器结构,则需要额外的列,即向下扩展该阵列。

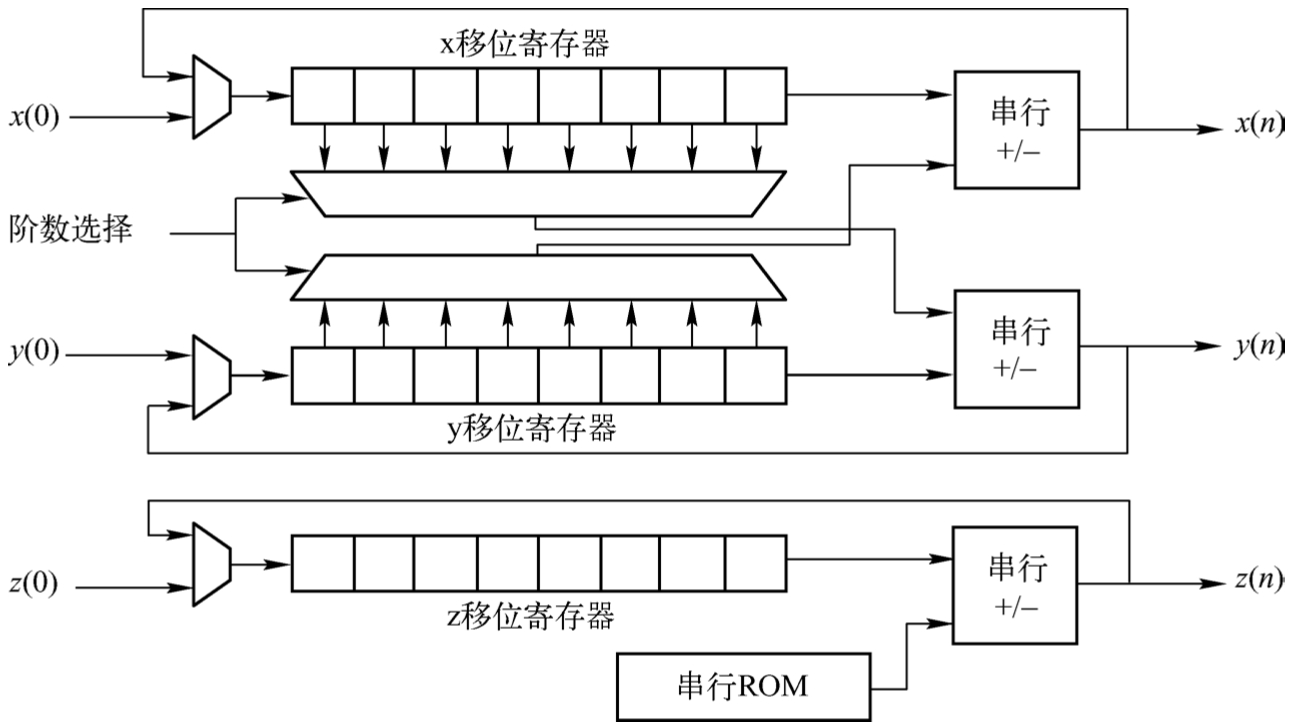

3.迭代位-串行移位寄存器

迭代位-串行移位寄存器的结构如图5.11所示,该结构包含:①3个位串行加法器/减法器;②3个移位寄存器;③一个串行ROM(用于存放旋转角度);④2个复用器(用于实现可变量移位)。

图5.11 迭代位-串行移位寄存器的结构

在该设计中,每个移位寄存器必须具有与字宽相等的长度。因此,每次迭代都需要该逻辑电路运行w次(w为字的宽度)。

由于首先将初始值x(0)、y(0)和z(0)加载到相关的移位寄存器中,因此通过加法器或者减法器右移数据,并且将数据返回到移位寄存器的最左端。在该迭代结构中,通过2个复用器实现变量移位器。在每个迭代的开始阶段,将两个复用器设置为从移位寄存器中读取合适的抽头数据。因此,来自每个复用器的数据被传送到了合适的加法器/减法器。在每次迭代的开始,从x、y和z寄存器中读出符号,用于给加法器设置正确的操作模式。在最后一次迭代的过程中,可以直接从加法器/减法器中读取结果。

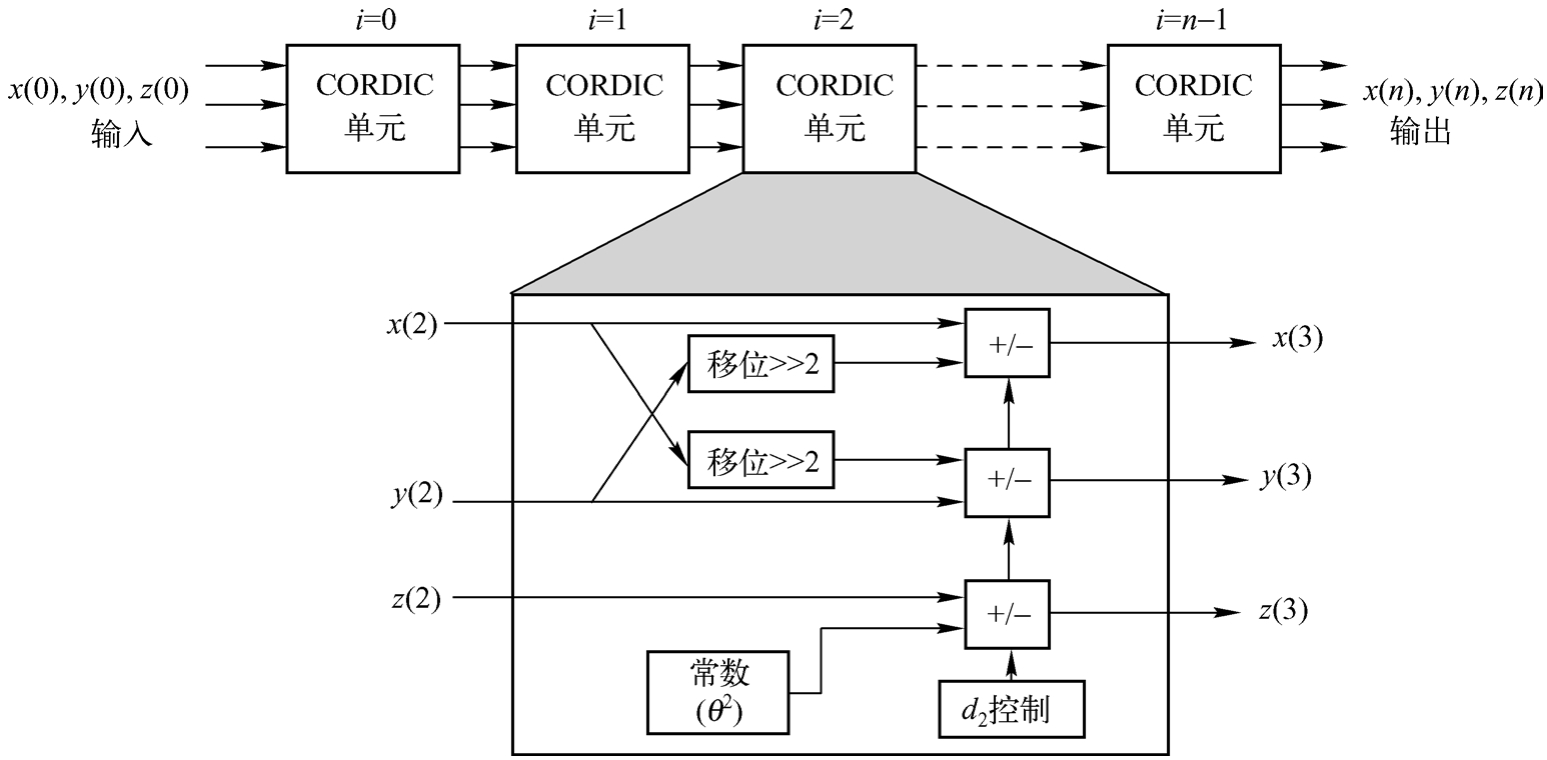

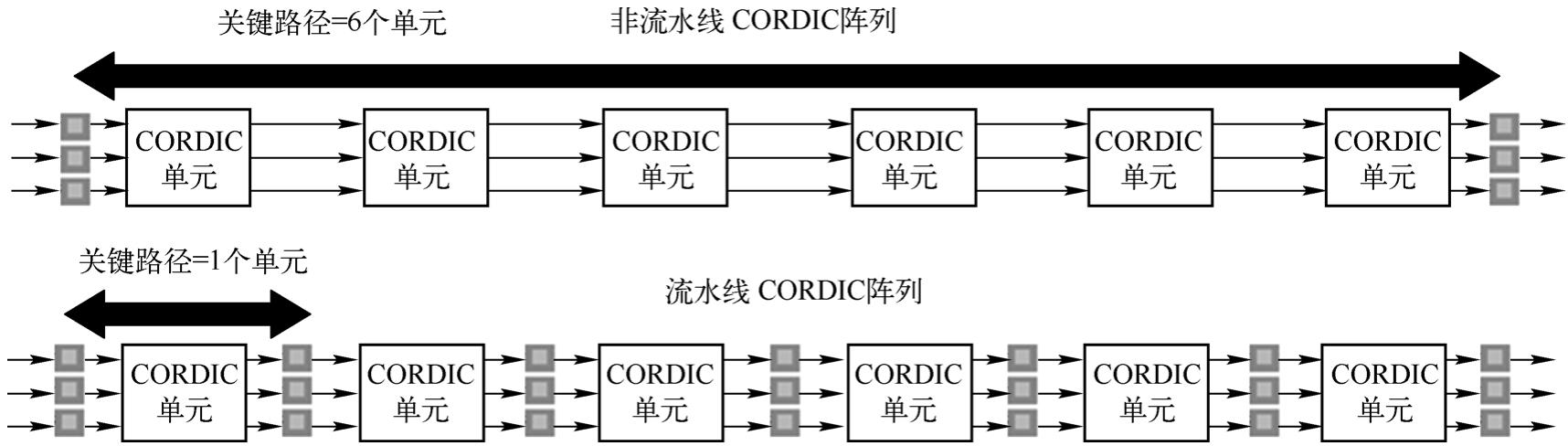

在CORDIC的非循环结构中使用一个阵列单元实现CODIC算法,如图5.12所示。该算法中的每一次迭代各自使用一个单元。

图5.12 CORDIC的非循环结构

CORDIC的非循环流水线结构是通过使用重定时来提高系统效率的,如图5.13所示。当在图5.12的每个CORDIC单元之间插入流水线寄存器时,可以显著降低关键路径的长度。

图5.13中,由于在6个CORDIC单元之间的每个计算单元中均插入了流水线寄存器,从而使得关键路径长度减少为1。

在流水线中插入寄存器的优势在于,显著降低了延迟,并且提高了整个系统的工作速度。

图5.13 CORDIC的非循环流水线结构