3.4 整数乘法运算的HDL描述

3.4 整数乘法运算的HDL描述

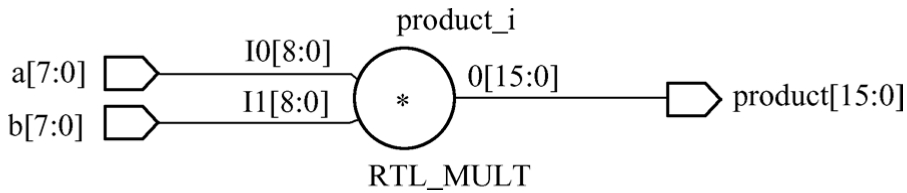

本节将使用VHDL和Verilog HDL语言实现有符号整数和无符号整数的乘法运算。整数乘法运算块的符号如图3.7所示。

图3.7 整数乘法运算块的符号

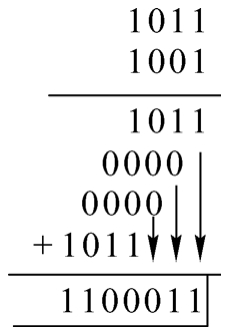

4位无符号整数(1011) 2 =(11) 10 和(1001) 2 =(9) 10 乘法运算的实现原理如图3.8所示。本质上,乘法运算就是加法运算和移位操作的组合。本节将使用HDL语言描述无符号整数的乘法运算。

图3.8 4位无符号整数(1011) 2 =(11) 10 和(1001) 2 =(9) 10 乘法运算的实现原理

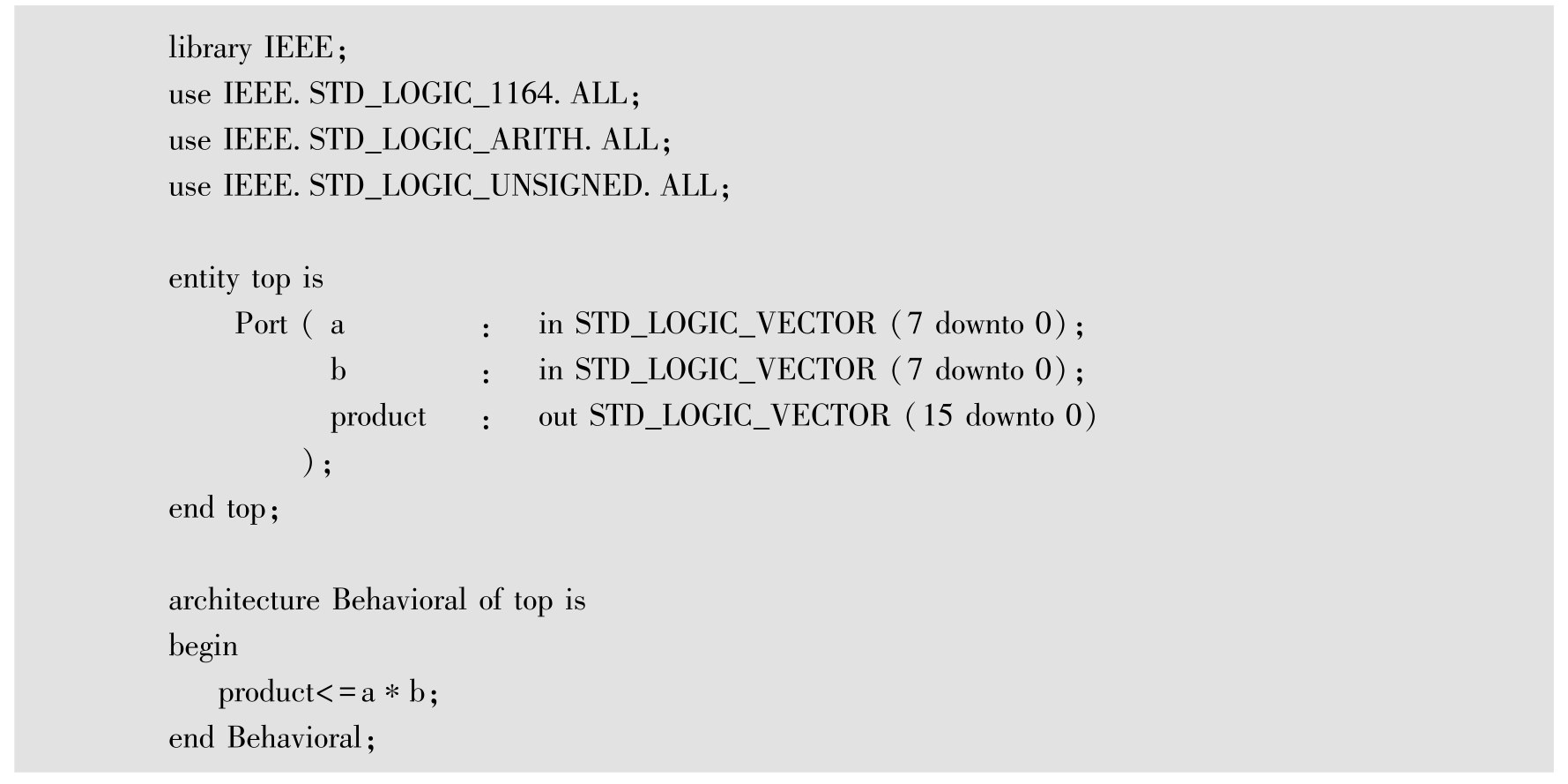

1.无符号整数乘法运算的VHDL描述

无符号整数乘法运算的VHDL描述如代码清单3-9所示。

代码清单3-9 无符号整数乘法运算的VHDL描述

注 :读者可以定位到本书所提供资料的\fpga_dsp_example\integer_mul_vhdl\unsigned_mul路径中,打开该设计。

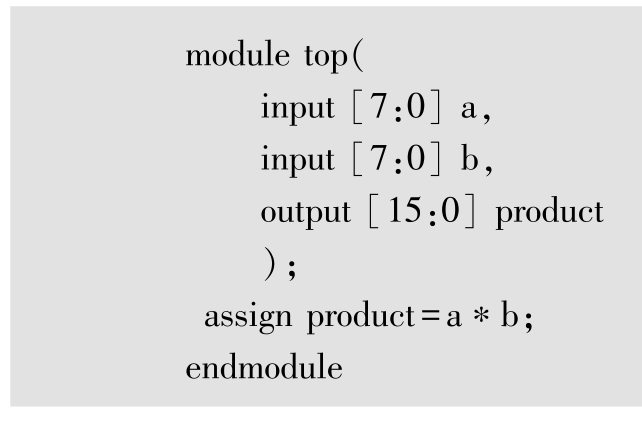

2.无符号整数乘法运算的Verilog HDL描述

无符号整数乘法运算的Verilog HDL描述如代码清单3-10所示。

代码清单3-10 无符号整数乘法运算的Verilog HDL描述

注 :读者可以定位到本书所提供资料的\fpga_dsp_example\integer_mul_verilog\unsigned_mul路径中,打开该设计。

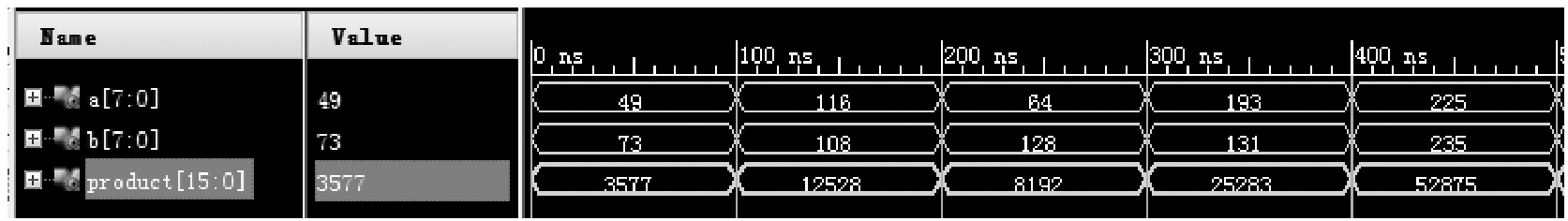

无符号整数乘法运算的仿真结果如图3.9所示。

图3.9 无符号整数乘法运算的仿真结果

思考与练习3-9 :对无符号整数乘法运算的仿真结果进行分析。

思考与练习3-10 :使用HDL语言描述无符号整数乘法运算的优势体现在哪些方面?

对于有符号整数的乘法而言,情况比较复杂,下面分别进行讨论。

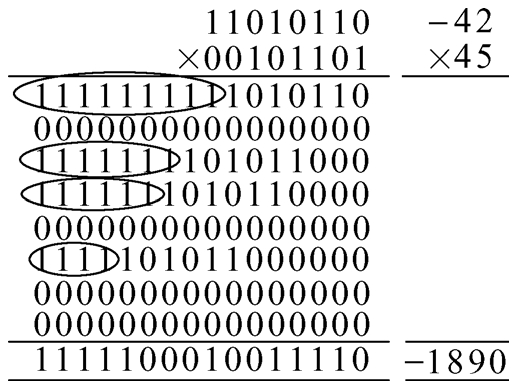

1.对于操作数为一个正数和一个负数的相乘

操作数为一个正数和一个负数的乘法运算如图3.10所示,只需要进行符号扩展。

图3.10 操作数为一个正数和一个负数的乘法运算

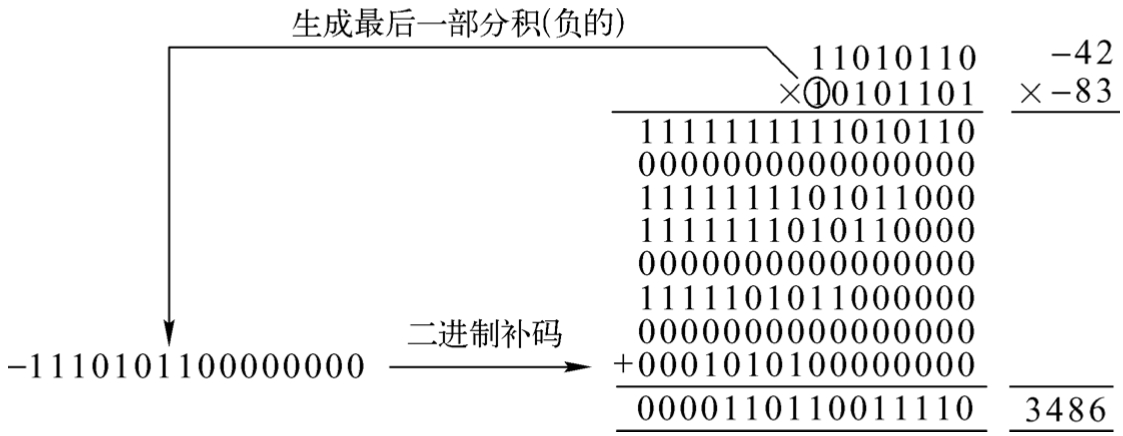

2.对于操作数均为两个负数的相乘

操作数为两个负数的乘法运算如图3.11所示。从图3.11中可知,减去最后一部分积。具体实现时,可以将最后一部分积转成补码,然后进行相加运算。

图3.11 操作数为两个负数的乘法运算

注 :(1)很明显,两个操作数都为负数时,本质上它等效于两个无符号整数的乘法运算。

(2)在使用HDL描述有符号整数的乘法运算时并不需要考虑上面的实现细节。

本节将使用HDL语言描述有符号整数乘法运算的实现过程。

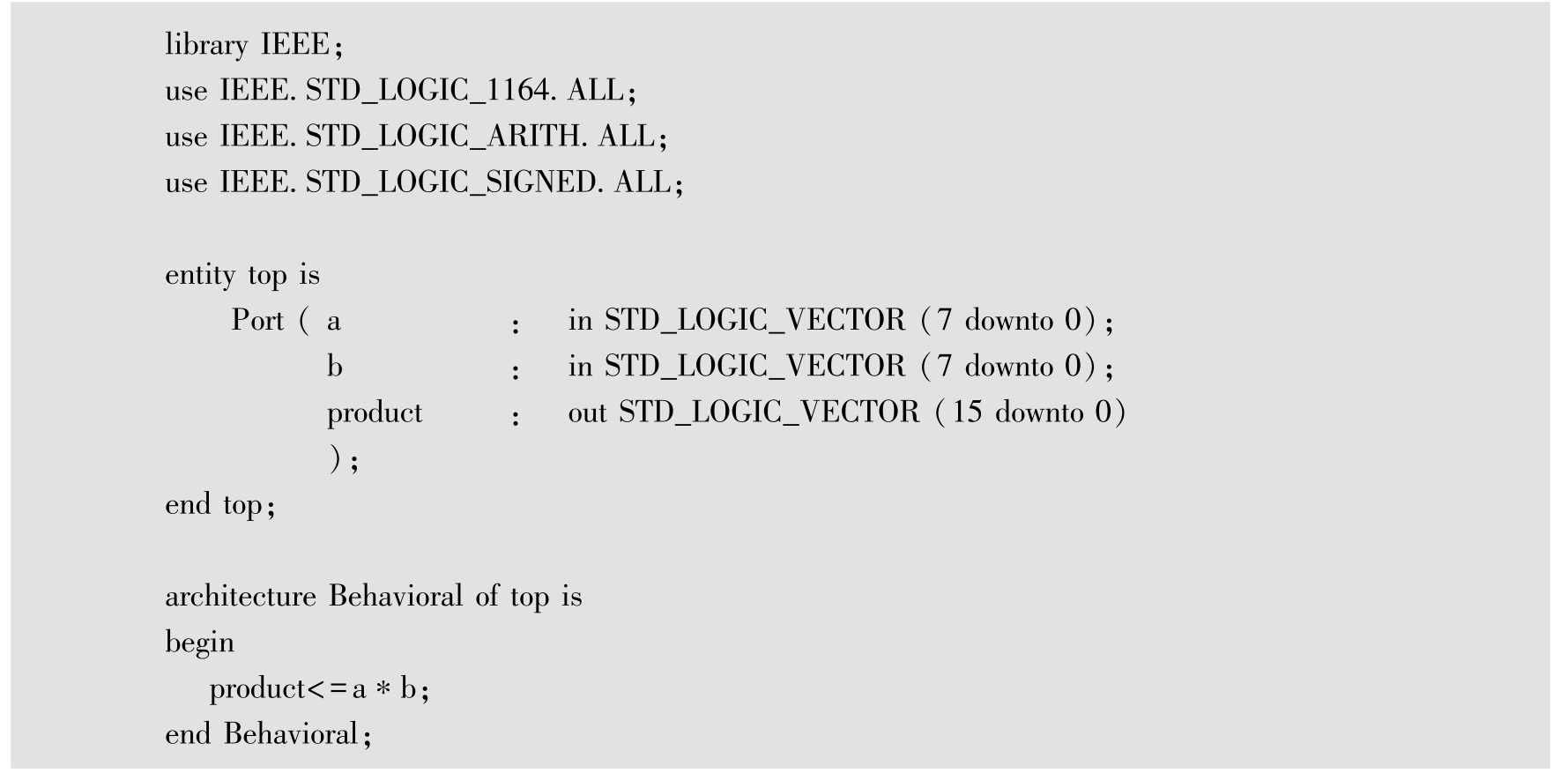

1.有符号整数乘法运算的VHDL描述

有符号整数乘法运算的VHDL描述如代码清单3-11所示。

代码清单3-11 有符号整数乘法运算的VHDL描述

注 :读者可以定位到本书所提供资料的\fpga_dsp_example\integer_mul_vhdl\signed_mul路径中,打开该设计。

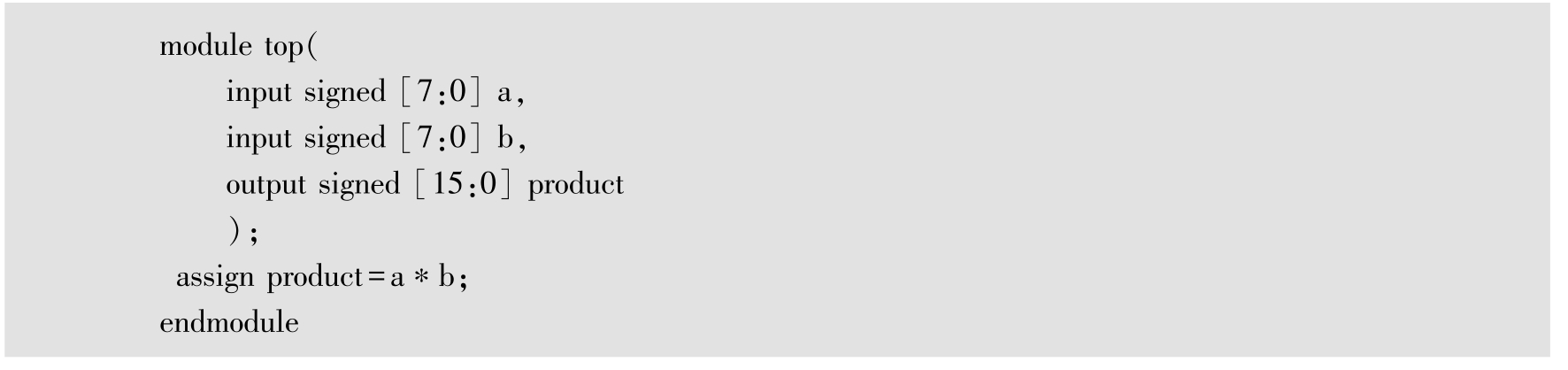

2.有符号整数乘法运算的Verilog HDL描述

有符号整数乘法运算的Verilog HDL描述如代码清单3-12所示。

代码清单3-12 有符号整数乘法运算的Verilog HDL描述

注 :读者可以定位到本书所提供资料的\fpga_dsp_example\integer_mul_verilog\signed_mul路径中,打开该设计。

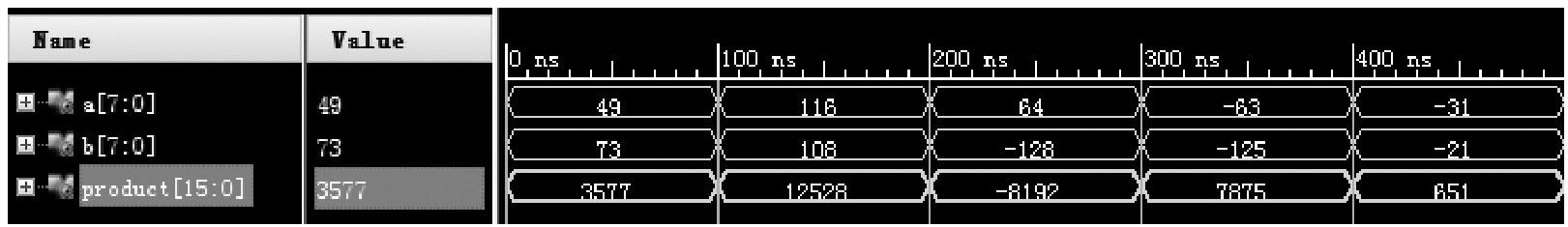

有符号整数乘法运算的仿真结果如图3.12所示。

图3.12 有符号整数乘法运算的仿真结果

思考与练习3-11 :对有符号整数乘法运算的仿真结果进行分析。

思考与练习3-12 :使用HDL语言描述有符号整数乘法运算的优势体现在哪些方面?